10-1

Semiconductor

August 1997

HI20206

Triple 8-Bit, 35 MSPS, RGB,

3-Channel D/A Converter

Features

∑ Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . Triple 8-Bit

∑ Maximum Conversion Speed . . . . . . . . . . . . . . . 35MHz

∑ RGB 3-Channel Input/Output

∑ Differential Linearity Error . . . . . . . . . . . . . . .

±

1

/

2

LSB

∑ Digital Input Voltage . . . . . . . . . . . . . . . . . . . .TTL Level

∑ Output Voltage Full-Scale . . . . . . . . . . . . . . 1V

P-P

(Typ)

∑ Low Power Consumption . . . . . . . . . . . . . 360mW (Typ)

∑ +5V Single Power Supply

∑ Direct Replacement for Sony CX20206

Applications

∑ Digital TV

∑ Graphics Display

∑ High Resolution Color Graphics

∑ Video Reconstruction

∑ Instrumentation

∑ Image Processing

∑ I/Q Modulation

Description

The HI20206 is a triple 8-bit, high-speed, bipolar D/A

converter designed for video band use. It has three sepa-

rate, 8-bit pixel inputs, one each for red, green, and blue

video data. A single 5.0V power supply and pixel clock input

is all that is required to make the device operational. A bias

voltage generator is internal. For lower CMOS power

consumption, refer to the HI1178.

Pinout

HI20206 (PDIP)

TOP VIEW

Ordering Information

PART NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

HI20206JCP

-20 to 75

42 Ld PDIP

E42.6B-S

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

R5

R6

R7

R8

G1

G2

G3

G4

G5

G6

G7

G8

B1

B2

B3

B4

B5

B6

B7

B8

30

42

41

40

39

38

37

36

35

34

33

32

31

29

28

27

26

25

24

23

R4

R3

R2

R1

NC

DGND

NC

ROUT

NC

GOUT

NC

BOUT

NC

AV

CC

NC

V

SET

V

REF

AGND

NC

NC

21

CLK

22

DV

CC

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

©

Harris Corporation 1997

File Number

4111.1

NOT RECOMMENDED FOR NEW DESIGNS

See HI1178

10-4

28

NC

No Connect.

29

AV

CC

Analog V

CC

.

30

NC

Vacant pin but connect to AV

CC

(Note 1).

31

BOUT

Analog Output pin for BLUE.

32

NC

Vacant pin but connect to AV

CC

(Note 1).

33

GOUT

Analog Output pin for GREEN.

34

NC

Vacant pin but connect to AV

CC

(Note 1).

35

ROUT

Analog Output pin for RED.

36

NC

Vacant pin but connect to AV

CC

(Note 1).

37

DGND

Digital GND.

38

NC

No Connect.

NOTE:

1. Pins 30, 32, 34 and 36 are vacant, but in order to reduce interference between the individual RGB outputs, connect them to AV

CC

.

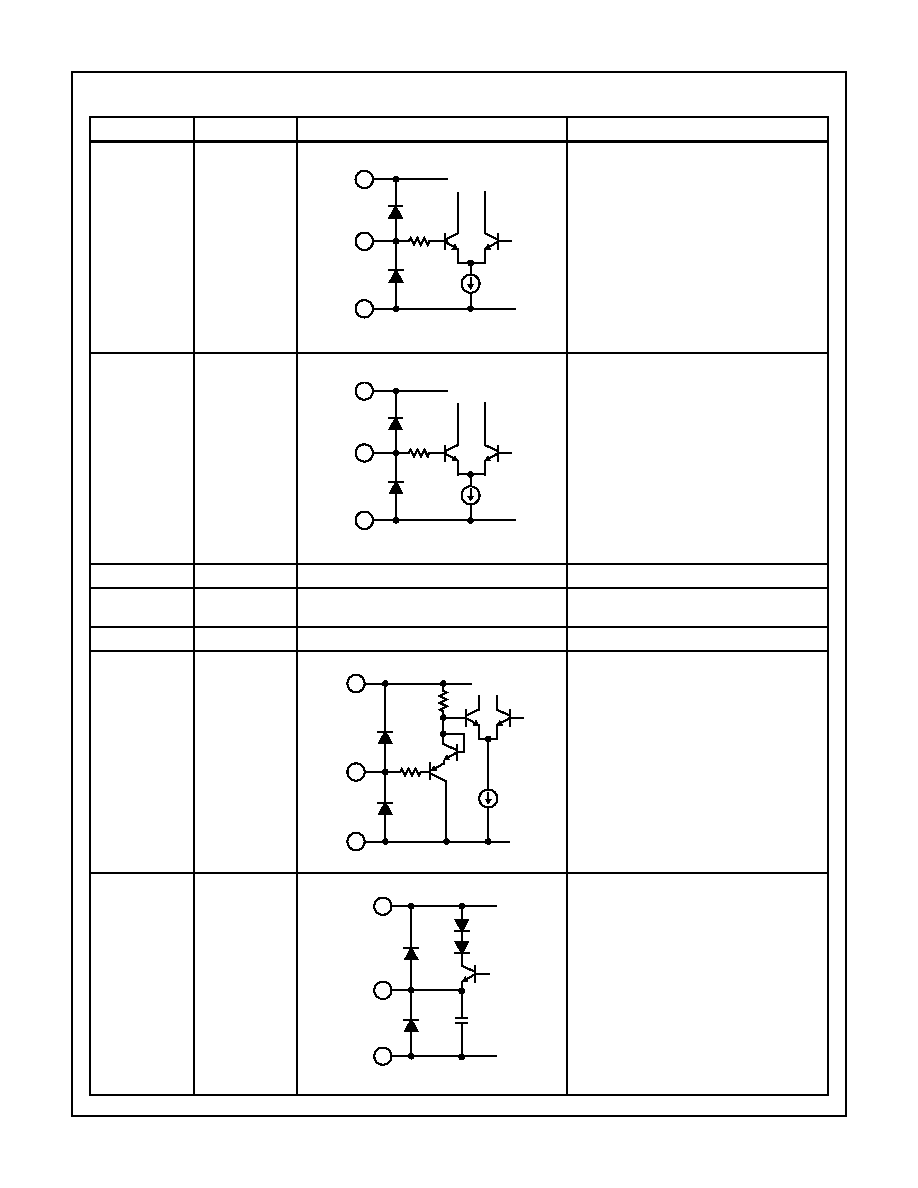

Pin Descriptions

(Continued)

PIN NO.

SYMBOL

EQUIVALENT CIRCUIT

DESCRIPTION

29

31

25

AGND

AV

CC

R

O

29

33

25

AGND

AV

CC

R

O

29

35

25

AGND

AV

CC

R

O

HI20206

10-5

Absolute Maximum Ratings

Thermal Information

Supply Voltage (V

CC

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0V to 7V

Input Voltage (Digital) (V

I

, V

CLK

) . . . . . . . . . . . . . . . . . -0.3V to V

CC

Output Voltage (Analog) (V

SET

) . . . . . . . . . . . . . . V

CC

-2.1V to V

CC

Output Current

Analog (I

OUT

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -3mA to 10mA

V

REF

Pin (I

REF

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . -5mA to 0mA

Supply Voltage Range (Typ) . . . . . . . . . . . . . . . . . . . . . . . 5V to 10V

Recommended Operating Conditions

Supply Voltage

AV

CC

, DV

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

AV

CC

-DV

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.2V to 0.2V

AGND-DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05V to 0.05V

Digital Input Voltage

H Level (V

IH

, V

CLKH

) . . . . . . . . . . . . . . . . . . . . . . . .2.0V to DV

CC

L Level (V

IL

, V

CLKL

) . . . . . . . . . . . . . . . . . . . . . . . . DGND to 0.8V

V

SET

Input Voltage (V

SET

). . . . . . . . . . . . . . . . . . . . . . .0.7V to 0.9V

V

REF

Pin Current (I

REF

). . . . . . . . . . . . . . . . . . . . . . -3mA to -0.4mA

Clock Pulse Width

t

PW1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15ns

t

PW0

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10ns

Temperature Range (T

OPR

) . . . . . . . . . . . . . . . . . . . . -40

o

C to 85

o

C

Thermal Resistance (Typical, Note 2)

JA

(

o

C/W)

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

70

Maximum Storage Temperature Range (T

STG

) . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

2.

JA

is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

T

A

= 25

o

C, AV

CC

= DV

CC

= 5V, AGND = DGND = 0V

PARAMETER

SYMBOL

TEST

CONDITIONS

MIN

TYP

MAX

UNITS

Resolution

RSL

-

8

-

Bit

Monotonic

MNT

-

Guarantee

-

-

Differential Linearity Error

DLE

V

SET

- AGND = 0.8V,

R

L

> 10k

-0.5

-

0.5

LSB

Integral Linearity Error

ILE

-0.4

-

0.4

% of Full

Scale

Maximum Conversion Speed

f

MAX

V

SET

- AGND = 0.8V,

R

L

> 10k

, C

L

< 20pF

35

-

-

MHz

Full Scale Output Voltage (Note 3)

V

OFS

0.85

1.0

1.15

V

P-P

RGB Output Voltage Full Scale Ratio (Note 4)

FSR

0

4

8

%

Output Zero Offset Voltage

V

OFFSET

-40

-6

0

mV

Output Resistance

R

O

270

340

420

Dissipation Current

I

D

V

SET

- AGND = 0.8V,

R

L

> 10k

, I

REF

= -400

µ

A

54

72

90

mA

Digital Data Input

Current

H Level

Upper 2 Bits

I

IH(U)

V

I

= DV

CC

-

1.2

20

µ

A

Lower 6 Bits

I

IH(L)

-

0.6

10

µ

A

L Level

Upper 2 Bits

I

IL(U)

V

I

= DGND

-10

0

10

µ

A

Lower 6 Bits

I

IL(U)

-10

0

10

µ

A

Clock Input Current

H Level

I

CLKH

V

CLK

= DV

CC

-

3

30

µ

A

L Level

I

CLKL

V

CLK

= DGND

-10

0

10

µ

A

V

SET

Input Current

I

SET

V

SET

- AGND = 0.8V

-5

-0.3

0

µ

A

Internal Reference Voltage

V

REF

I

REF

= -400

µ

A

1.08

1.20

1.32

V

Set-Up Time

t

S

12

-

-

ns

Hold Time

t

H

3

-

-

ns

Crosstalk Among R, G and B

CT

D/A OUT: 1V

P-P

, R

L

>10k

,

C

L

<20pF, f

DATA

= 7MHz,

f

CLK

= 14MHz, See Figure 5

-

-40

-33

dB

HI20206