10-1

Æ

January 1998

HI2309

Triple 10-Bit, 50 MSPS,

3-Channel D/A Converter

Features

∑ Resolution . . . . . . . . . . . . . . . . . . . . . . . . . .Triple 10-Bit

∑ Maximum Conversion Speed . . . . . . . . . . . . . . . 50MHz

∑ RGB 3-Channel Input/Output

∑ Differential Linearity Error . . . . . . . . . . . . . . .

±0.5 LSB

∑ Low Power Consumption . . . . . . . . . . . . . . . . . . 200mW

(200

Load for 2V

P-P

Output)

∑ Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . +5V Single

∑ Low Glitch

∑ Direct Replacement for Sony CXD2309

Applications

∑ Digital TV

∑ Graphics Display

∑ High Resolution Color Graphics

∑ Video Reconstruction

∑ Instrumentation

∑ Image Processing

∑ I/Q Modulation

Description

The HI2309 is a triple 10-bit, high-speed, CMOS D/A

converter designed for video band use. It has three sepa-

rate, 10-bit, pixel inputs, one each for red, green, and blue

video data. A single 5.0V power supply and pixel clock input

is all that is required to make the device operational. A bias

voltage generator is internal. Each channel clock input can

be controlled individually, or connected together as one. The

HI2309 also has BLANK video control signal.

Pinout

HI2309 (MQFP)

TOP VIEW

Ordering Information

PART

NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

HI2309JCQ

-20 to 75

48 Ld MQFP

Q48.12x12-S

1

2

3

4

5

6

7

8

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

9

10

11

12

13 14 15 16

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

I

REF

VB

DV

SS

BCK

GCK

RCK

B9

B8

B7

B6

B5

B4

(LSB) R0

R1

R2

R3

R4

R7

R8

R9

G0

(LSB) G1

R5

R6

DV

DD

AV

SS

BO

AV

SS

GO

RO

AV

DD

AV

DD

AV

DD

VG

V

RE

F

AV

SS

G2

G3

G4

G5

G6

G7

G8

G9

B0

(

L

S

B

)

B1

B2

B3

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

|

Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

File Number

4118.2

NOT

REC

OMM

END

ED F

OR N

EW D

ESIG

NS

See

HI30

50

or co

ntac

t our

Tec

hnic

al Su

ppor

t Cen

ter a

t

1-88

8-INT

ERS

IL or

www

.inte

rsil.c

om/t

sc

10-3

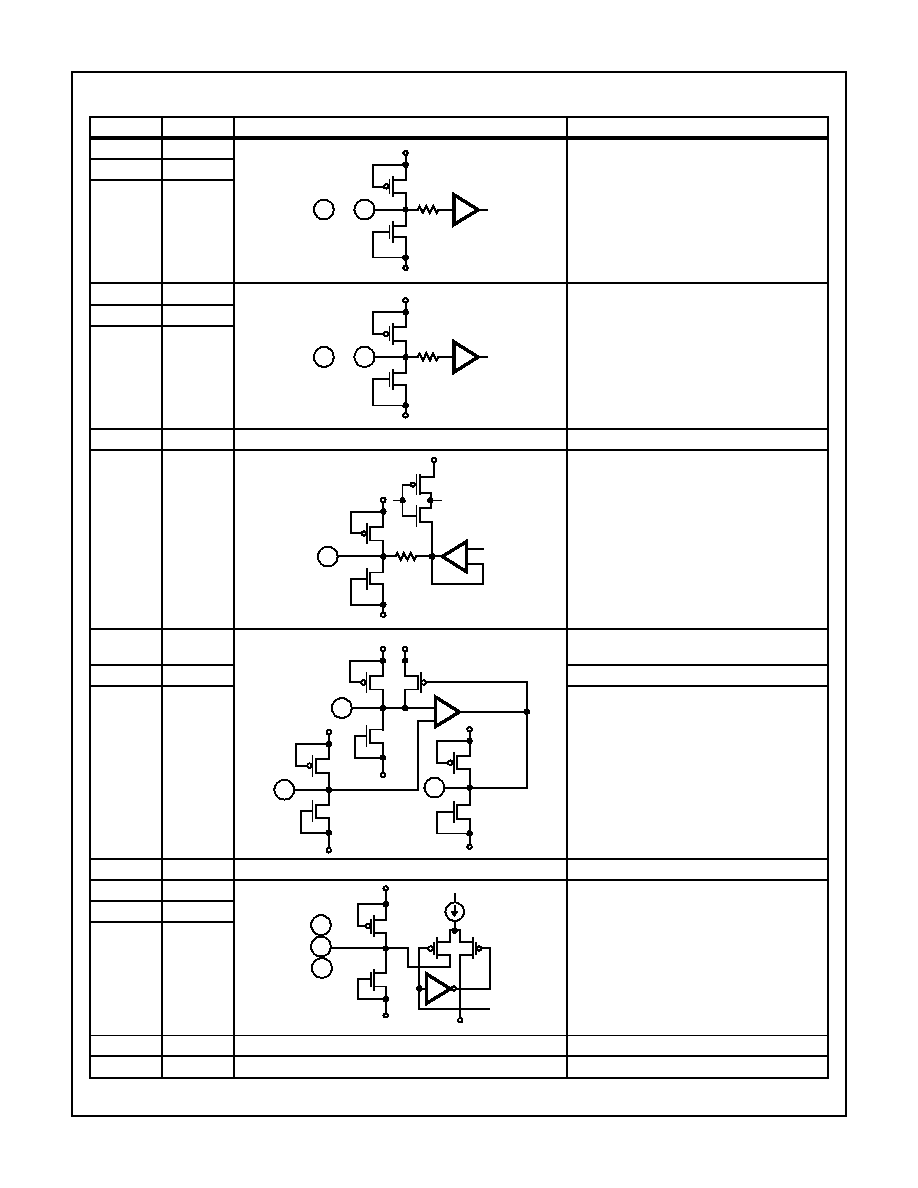

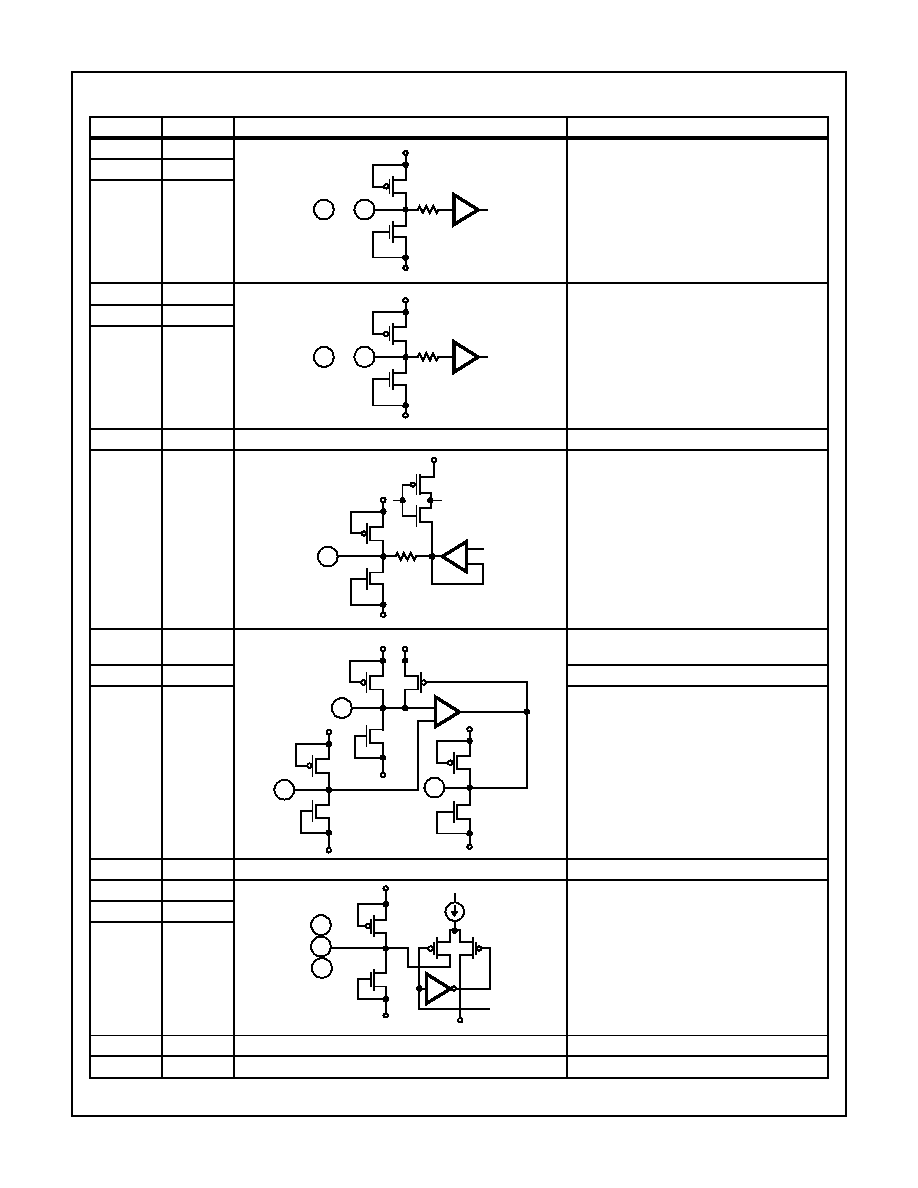

Pin Descriptions

PIN NO.

SYMBOL

EQUIVALENT CIRCUIT

DESCRIPTION

1 to 10

R0 to R9

Digital Input.

11 to 20

G0 to G9

21 to 30

B0 to B9

31

RCLK

Clock pin.

32

GCLK

33

BCLK

34

DV

SS

Digital GND.

35

VB

Connect an approximately 0.1

µF capacitor.

36

I

REF

Connect a "16R" resistor which is 16 times the

output resistance "R".

37

V

REF

Sets an output full scale value.

38

VG

Connect an approximately 0.1

µF capacitor.

39 to 41

AV

DD

Analog V

DD

.

42

RO

Current Output. Output can be obtained by

connecting a resistor (200

typical).

44

GO

46

BO

43, 45, 47

AV

DD

Analog GND.

47, 48

DV

DD

Digital V

DD

.

30

1

DV

DD

DV

SS

TO

33

31

DV

DD

DV

SS

TO

35

DV

DD

DV

SS

-

+

DV

DD

AV

DD

-

+

AV

DD

36

AV

DD

AV

DD

37

AV

SS

AV

DD

38

AV

SS

42

44

46

AV

SS

AV

DD

AV

SS

HI2309

10-4

Absolute Maximum Ratings

T

A

= 25

o

C

Thermal Information

Supply Voltage (V

DD

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V

Input Voltage (V

IN

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

DD

to V

SS

Output Current (I

OUT

) . . . . . . . . . . . . . . . . . . . . . . . . .0mA to 15mA

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . -55

o

C 150

o

C

Operating Conditions

Supply Voltage

AV

DD

, AV

SS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.75V to 5.25V

DV

DD

, DV

SS

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.75V to 5.25V

Reference Input Voltage (V

REF

) . . . . . . . . . . . . . . . . . .0.5V to 2.0V

Clock Pulse Width

t

PW1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10ns (Min)

t

PW0

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10ns (Min)

Temperature Range (T

OPR

). . . . . . . . . . . . . . . . . . . . -20

o

C to 75

o

C

Thermal Resistance (Typical, Note 1)

JA

(

o

C/W)

MQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . .

94

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . . -65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300

o

C

(Lead Tips Only)

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

f

CLK

= 50MHz, V

DD

= 5V, R = 200

, V

REF

= 2.0V, T

A

= 25

o

C

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

Resolution

n

-

10

-

Bit

Maximum Conversion Speed

f

MAX

50

-

-

MHz

Linearity Error

E

L

-2.0

-

2.0

LSB

Differential Linearity Error

E

D

-0.5

-

0.5

LSB

Output Full Scale Voltage

V

FS

1.8

1.92

2.0

V

Output Full Scale Current

I

FS

9.0

9.6

10

mA

Output Offset Voltage

V

OS

-

-

1

mV

Supply Current

I

DD

-

40

50

mA

Digital Input Current

High Level

I

IH

-

-

5

µA

Low Level

I

IL

-5

-

-

µA

Digital Input Voltage

High Level

V

IH

DV

DD

= 4.75 to 5.25V

2.15

-

-

V

Low Level

V

IL

DV

DD

- 4.75 to 5.25V

-

-

0.85

V

Precision Guaranteed Output Voltage Range

V

OC

1.8

1.92

2.0

V

Setup Time

t

S

6

-

-

ns

Hold Time

t

H

3

-

-

ns

Propagation Delay Time

t

PD

-

14

-

ns

Glitch Energy

GE

For R

OUT

= 100

, 1V

P-P

Output

-

50

-

pV/s

Cross Talk

CT

For 10MHz Sine Wave Output

40

42

-

dB

SNR

SNR

For 1MHz Sine Wave Output

50

55

-

dB

NOTE:

2. Output full scale ratio =

.

Full scale voltage for each channel

Average of full scale voltage for each channel

------------------------------------------------------------------------------------------------------------------------- 1

≠

x 100%

HI2309