GM71C4403C

1,048,576 WORDS x 4BIT

CMOS DYNAMIC RAM

Description

The GM71C4403C is the new generation dynamic

RAM organized 1,048,576 words x 4 bit.

GM71C4403C has realized higher density, higher

performance and various functions by utilizing

advanced CMOS process technology. The

GM71C4403C offers Extended Data Out (EDO)

Mode as a high speed access Mode. Multiplexed

address inputs permit the GM71C4403C to be

packaged in a standard 300mil 20(26) pin plastic

SOJ , and standard 300mil 20(26) pin plastic TSOP

II. The package size provides high system bit

densities and is compatible with widely available

automated testing and insertion equipment. System

oriented features include single power supply of

5V+/-10% tolerance, direct interfacing capability

with high performance logic families such as

Schottky TTL.

Features

* 1,048,576 Words x 4 Bit Organization

* Extended Data Out Mode Capability

* Single Power Supply (5V+/-10%)

* Fast Access Time & Cycle Time

* Low Power

Active : 605/550/495mW (MAX)

Standby : 5.5mW (CMOS level : MAX)

* RAS Only Refresh, CAS before RAS Refresh,

Hidden Refresh Capability

* All inputs and outputs TTL Compatible

*1024 Refresh Cycles/16ms

1

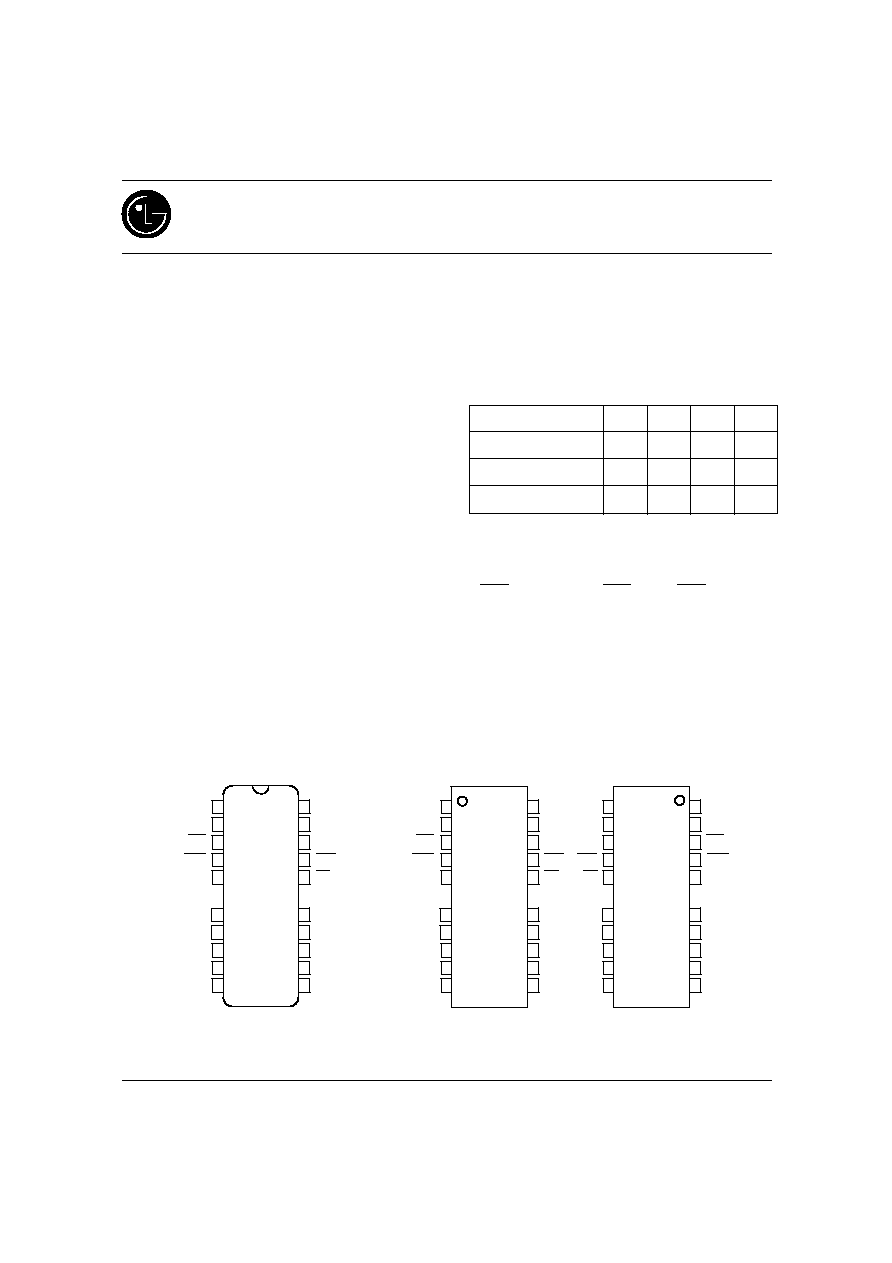

Pin Configuration

LG Semicon Co.,Ltd.

1

2

3

4

5

16

17

18

19

20

6

7

8

9

10

11

12

13

14

15

1

2

3

4

5

16

17

18

19

20

6

7

8

9

10

11

12

13

14

15

I/O1

I/O2

WE

RAS

A9

A0

A1

A2

A3

V

CC

V

SS

I/O4

I/O3

CAS

OE

A8

A7

A6

A5

A4

V

SS

I/O4

I/O3

CAS

OE

A8

A7

A6

A5

A4

I/O1

I/O2

WE

RAS

A9

A0

A1

A2

A3

V

CC

20 (26) TSOP II

(Top View)

1

2

3

4

5

16

17

18

19

20

I/O1

I/O2

WE

RAS

A9

A0

A1

A2

A3

V

CC

6

7

8

9

10

11

12

13

14

15

V

SS

I/O4

I/O3

CAS

OE

A8

A7

A6

A5

A4

20 (26) SOJ

(Top View)

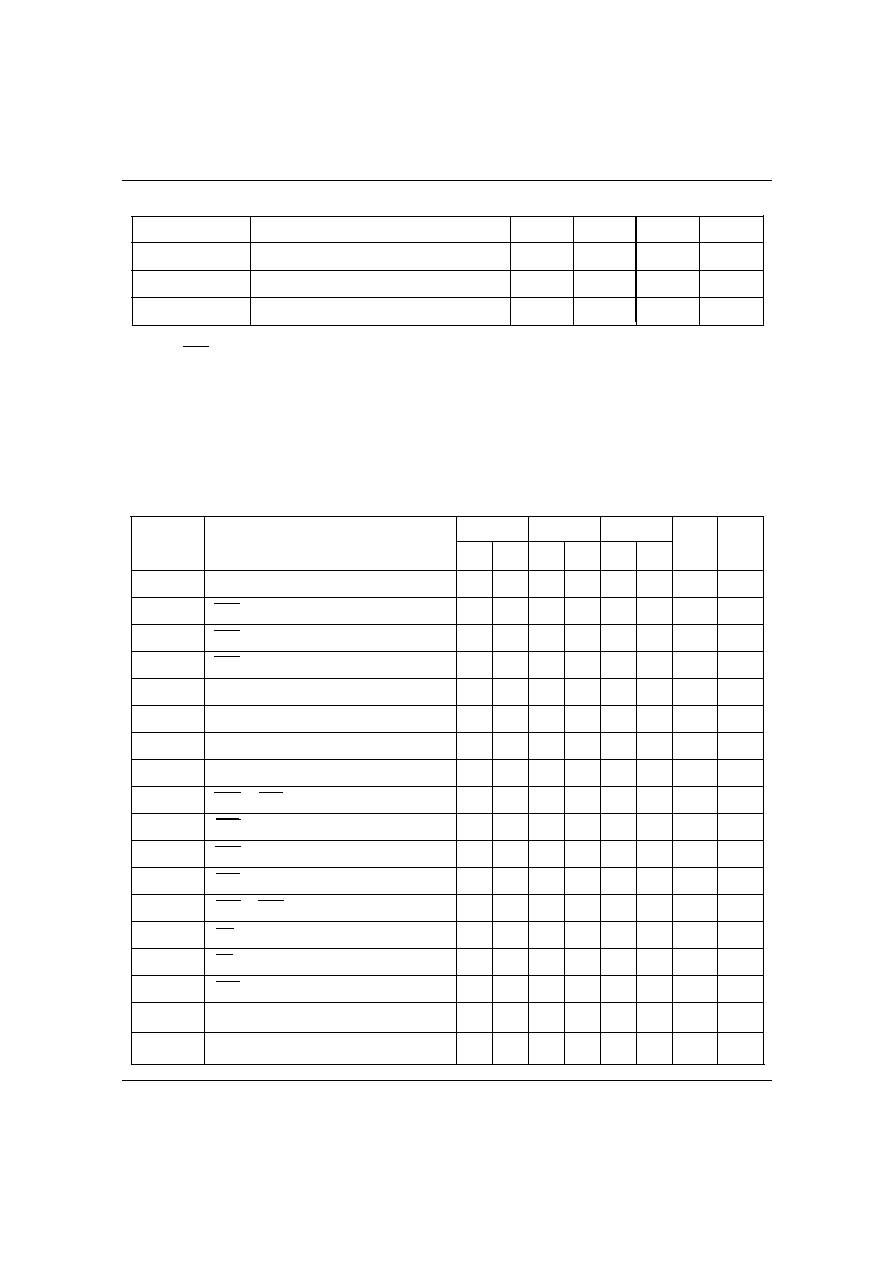

NORMAL TYPE

REVERSE TYPE

GM71C4403C-60

GM71C4403C-70

GM71C4403C-80

t

RAC

t

CAC

t

RC

t

HPC

60

70

80

15

18

20

104

124

144

25

30

35

(Unit: ns)

LG Semicon

GM71C4403C

2

Pin Description

Pin

Function

Pin

Function

A0-A9

A0-A9

I/O1-I/O4

RAS

CAS

WE

OE

V

CC

V

SS

Address Inputs

Refresh Address Inputs

Data Input / Data Output

Row Address Strobe

Column Address Strobe

Read/Write Enable

Output Enable

Power (+5V)

Ground

Ordering Information

Type No.

Access Time

Package

GM71C4403CJ-60

GM71C4403CJ-70

GM71C4403CJ-80

300 Mil, 20 (26) Pin

Plastic SOJ

Absolute Maximum Ratings*

Symbol

Parameter

Rating

Unit

T

A

T

STG

V

IN

/V

OUT

V

CC

I

OUT

0 ~ 70

-55 ~ 125

-1.0 ~ 7.0

-1.0 ~ 7.0

50

Ambient Temperature under Bias

Storage Temperature (Plastic)

Voltage on any Pin Relative to V

SS

Voltage on V

CC

Relative to V

SS

Short Circuit Output Current

C

C

V

V

mA

P

D

1.0

Power Dissipation

W

*Note: Operation at or above Absolute Maximum Ratings can adversely affect device reliability.

Recommended DC Operating Conditions (All Voltage referenced to Vss, T

A

= 0 ~ 70C)

Symbol

Parameter

Unit

V

CC

V

IH

V

IL

Supply Voltage

Input High Voltage

Input Low Voltage

V

V

V

Max

5.5

6.5

0.8

Typ

5.0

-

-

Min

4.5

2.4

-1.0

60ns

70ns

80ns

300 Mil, 20 (26) Pin

Plastic TSOP II

(Normal Type)

GM71C4403CT-60

GM71C4403CT-70

GM71C4403CT-80

300 Mil, 20 (26) Pin

Plastic TSOP II

(Reverse Type)

GM71C4403CR-60

GM71C4403CR-70

GM71C4403CR-80

60ns

70ns

80ns

60ns

70ns

80ns

LG Semicon

GM71C4403C

3

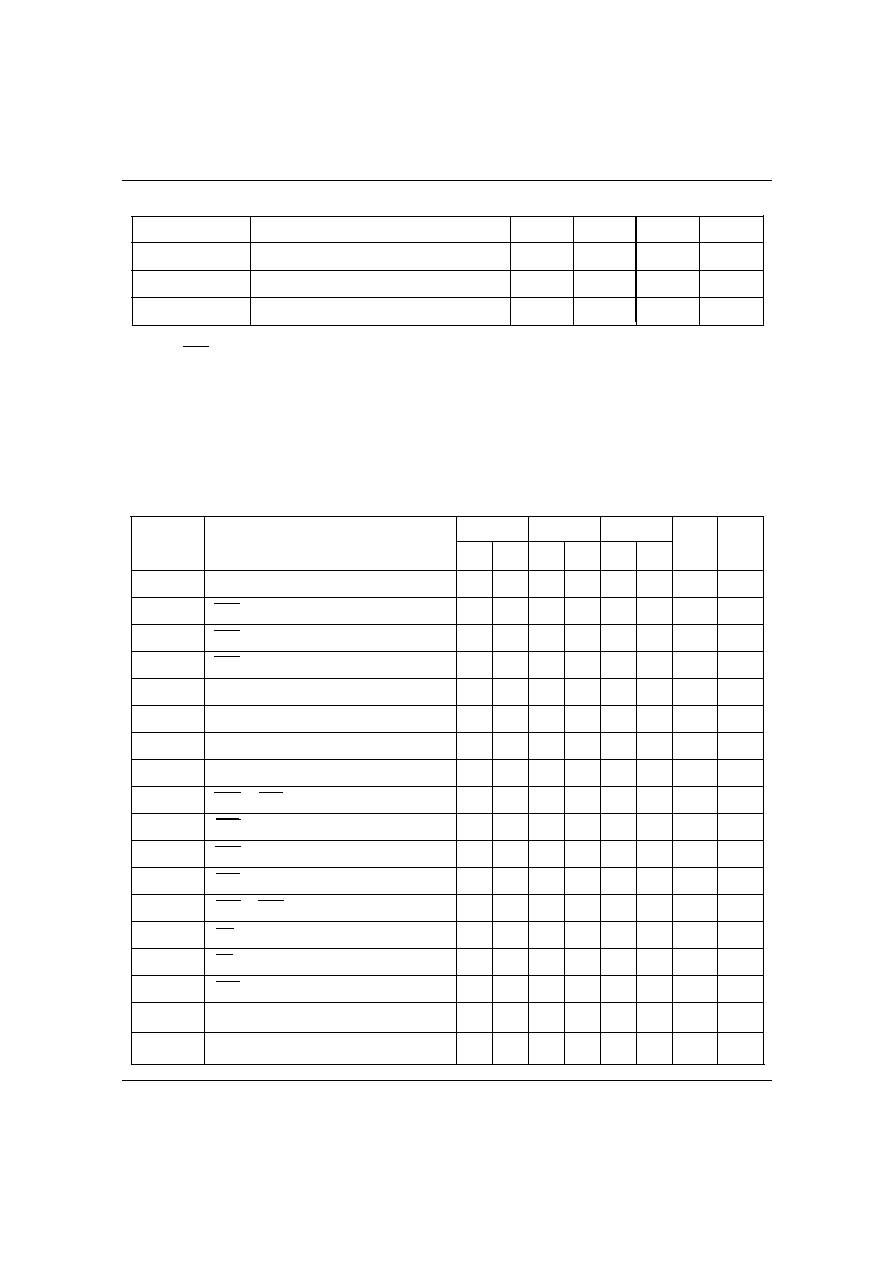

DC Electrical Characteristics (V

CC

= 5V+/-10%, T

A

= 0 ~ 70C)

Note: 1. I

CC

depends on output load condition when the device is selected. I

CC

(max) is specified at the

output open condition.

2. Address can be changed once or less while RAS = V

IL

.

3. Address can be changed once or less while CAS = V

IH

.

Symbol

Parameter

Note

V

OH

V

OL

Output Level

Output "H" Level Voltage (I

OUT

= -5mA)

Unit

V

V

Max

V

CC

0.4

Min

2.4

0

Output Level

Output "L" Level Voltage (I

OUT

= 4.2mA)

I

CC1

mA

110

-

Operating Current

Average Power Supply Operating Current

(RAS, CAS, Address Cycling: t

RC

= t

RC

min)

60ns

70ns

80ns

100

90

-

-

1, 2

I

CC2

mA

Standby Current (TTL)

Power Supply Standby Current

(RAS, CAS= V

IH

, D

OUT

= High-Z)

2

-

I

CC3

mA

2

I

CC4

mA

1, 3

110

-

60ns

70ns

80ns

100

90

-

-

130

-

60ns

70ns

80ns

120

110

-

-

I

CC5

mA

1

-

I

CC6

mA

CAS-before-RAS Refresh Current

(t

RC

= t

RC

min)

110

-

60ns

70ns

80ns

100

90

-

-

I

CC8

mA

Standby Current RAS = V

IH

CAS = V

IL

D

OUT

= Enable

5

-

1

I

I(L)

uA

10

-10

I

O(L)

uA

10

-10

Input Leakage Current

Any Input (0V<=V

IN

<=7V)

Output Leakage Current

(D

OUT

is Disabled, 0V<=V

OUT

<=7V)

RAS-Only Refresh Current

Average Power Supply Current

RAS-Only Refresh Mode

(RAS Cycling, CAS = V

IH

, t

RC

= t

RC

min)

Extended Data Out Page Mode Current

Average Power Supply Current

Extended Data Out Mode

(RAS = V

IL

, CAS, Address Cycling: t

HPC

= t

HPC

min)

Standby Current (CMOS)

Power Supply Standby Current

(RAS, CAS= V

IH

, WE, OE, Address and D

IN

=V

IH

or V

IL

,

D

OUT

=High-Z)

LG Semicon

GM71C4403C

4

Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

Symbol

Parameter

Note

Max

Unit

Min

Max

Min

Max

Min

t

RC

Random Read or Write Cycle Time

104

-

124

-

144

-

ns

t

RP

RAS Precharge Time

40

-

50

-

60

-

ns

t

RAS

RAS Pulse Width

60

10,000

70

10,000

80

10,000

ns

t

CAS

CAS Pulse Width

10

10,000

10,000

10,000

ns

13

15

t

ASR

Row Address Set-up Time

0

-

-

-

ns

0

0

t

RAH

Row Address Hold Time

10

-

-

-

ns

10

t

ASC

Column Address Set-up Time

0

-

-

-

ns

0

0

t

CAH

Column Address Hold Time

10

-

-

-

ns

13

15

t

RCD

RAS to CAS Delay Time

20

45

52

60

ns

20

20

8

t

RAD

RAS to Column Address Delay Time

15

30

35

40

ns

15

15

9

t

RSH

RAS Hold Time

15

-

-

-

ns

18

20

t

CSH

CAS Hold Time

48

-

-

-

ns

58

68

t

CRP

CAS to RAS Precharge Time

10

-

-

-

ns

10

10

t

T

Transition Time (Rise and Fall)

2

50

50

50

ns

2

2

7

t

REF

Refresh Period

-

16

16

16

ms

-

-

Capacitance (V

CC

= 5V+/-10%, T

A

= 25C)

Symbol

Parameter

Note

C

I1

C

I2

C

I/O

�

Input Capacitance (Address)

Input Capacitance (Clocks)

Data Input/Output Capacitance (Data-In/Out)

1

1

1, 2

Unit

��

��

��

Max

5

7

7

Min

-

-

-

Note: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. CAS = V

IH

to disable D

OUT

.

AC Characteristics (V

CC

= 5V+/-10%, T

A

= 0 ~ 70C, Notes 1, 14, 15, 16)

t

ODD

OE to D

IN

Delay Time

15

-

-

-

ns

18

20

t

DZO

OE Delay Time from D

IN

0

-

-

-

ns

0

0

t

DZC

CAS Set-up Time from D

IN

0

-

-

-

ns

0

0

GM71C4403

C-60

GM71C4403

C-70

GM71C4403

C-80

Test Conditions

Input level : V

IL

=0V, V

IH

=3.0V

Input rise and fall times: 2ns

Input timing reference levels: V

IL

=0.8V, V

IH

=2.4V

Output timing reference levels: V

OL

=0.8V, V

OH

=2.0V

Output load : 1 TTL gate + C

L

(100��)

(Including scope and jig)

10

19

20

22

LG Semicon

GM71C4403C

5

Read Cycle

Symbol

Parameter

Note

Max

Unit

Min

Max

Min

Max

Min

t

RAC

Access Time from RAS

-

60

-

70

-

80

ns

t

CAC

Access Time from CAS

-

15

-

18

-

20

ns

t

AA

Access Time from Address

-

30

-

35

-

40

ns

t

RCS

Read Command Setup Time

0

-

0

-

0

-

ns

t

RCH

Read Command Hold Time to CAS

0

-

-

-

ns

0

0

t

RRH

Read Command Hold Time to RAS

0

-

-

-

ns

0

0

t

RAL

Column Address to RAS Lead Time

30

-

-

-

ns

35

40

2,3,17

3, 4, 13,

17

t

OFF

Output Buffer Turn-off Time

15

15

15

ns

6,21

t

OAC

Access Time from OE

-

15

-

18

-

20

ns

3,17

t

OEZ

Output Buffer Turn-off Time to OE

15

15

15

ns

6

t

CDD

CAS to D

IN

Delay Time

-

-

-

ns

15

18

20

GM71C4403

C-60

GM71C4403

C-70

GM71C4403

C-80

t

OEP

OE Pulse width

-

-

-

ns

15

18

20

t

CAL

Column Address to CAS Lead Time

18

-

-

-

ns

23

28

t

RDD

RAS to D

IN

Delay Time

-

-

-

ns

15

18

20

t

WDD

WE to D

IN

Delay Time

-

-

-

ns

15

18

20

t

OFR

Output Buffer Turn-off Time to RAS

15

15

-

ns

6,21

t

WEZ

Output Buffer Turn-off Time to WE

15

15

-

15

15

ns

6

t

OH

Output Data Hold Time

5

-

5

-

5

-

ns

t

OHR

Output Data Hold Time form RAS

5

-

5

-

5

-

ns

t

RCHR

Read Command Hold Time from

RAS

60

-

70

-

80

-

ns

3, 5, 13,

17

18

18

-

-

-

-

-

-

-

-

-

-