1421fc.pm6

1

LTC1421/LTC1421-2.5

Hot Swap Controller

s

Allows Safe Board Insertion and Removal from a

Live Backplane

s

System Reset and Power Good Control Outputs

s

Programmable Electronic Circuit Breaker

s

User Programmable Supply Voltage Power-Up Rate

s

High Side Driver for Two External N-Channels

s

Controls Supply Voltages from 3V to 12V

s

Connection Inputs Detect Board Insertion or Removal

s

Undervoltage Lockout

s

Power-On Reset Input

s

Hot Board Insertion

s

Electronic Circuit Breaker

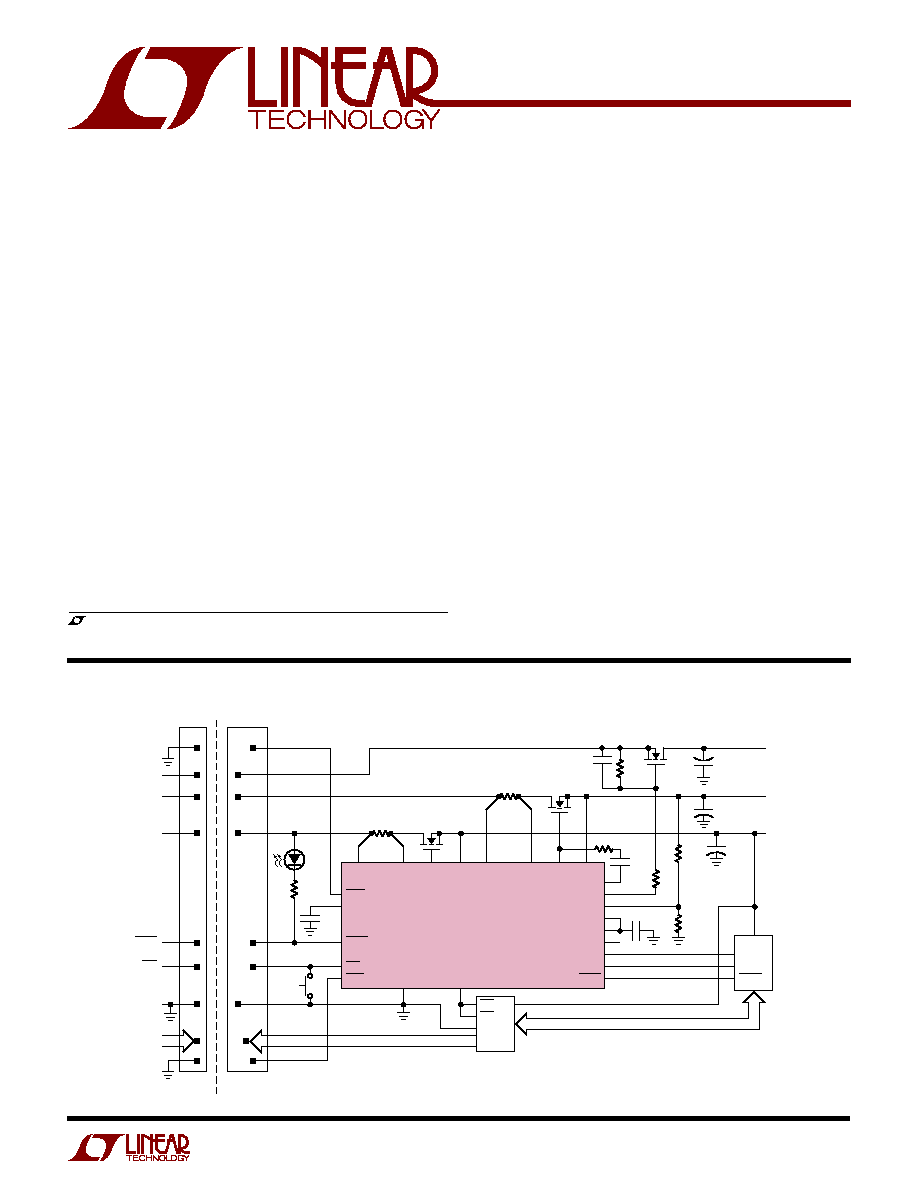

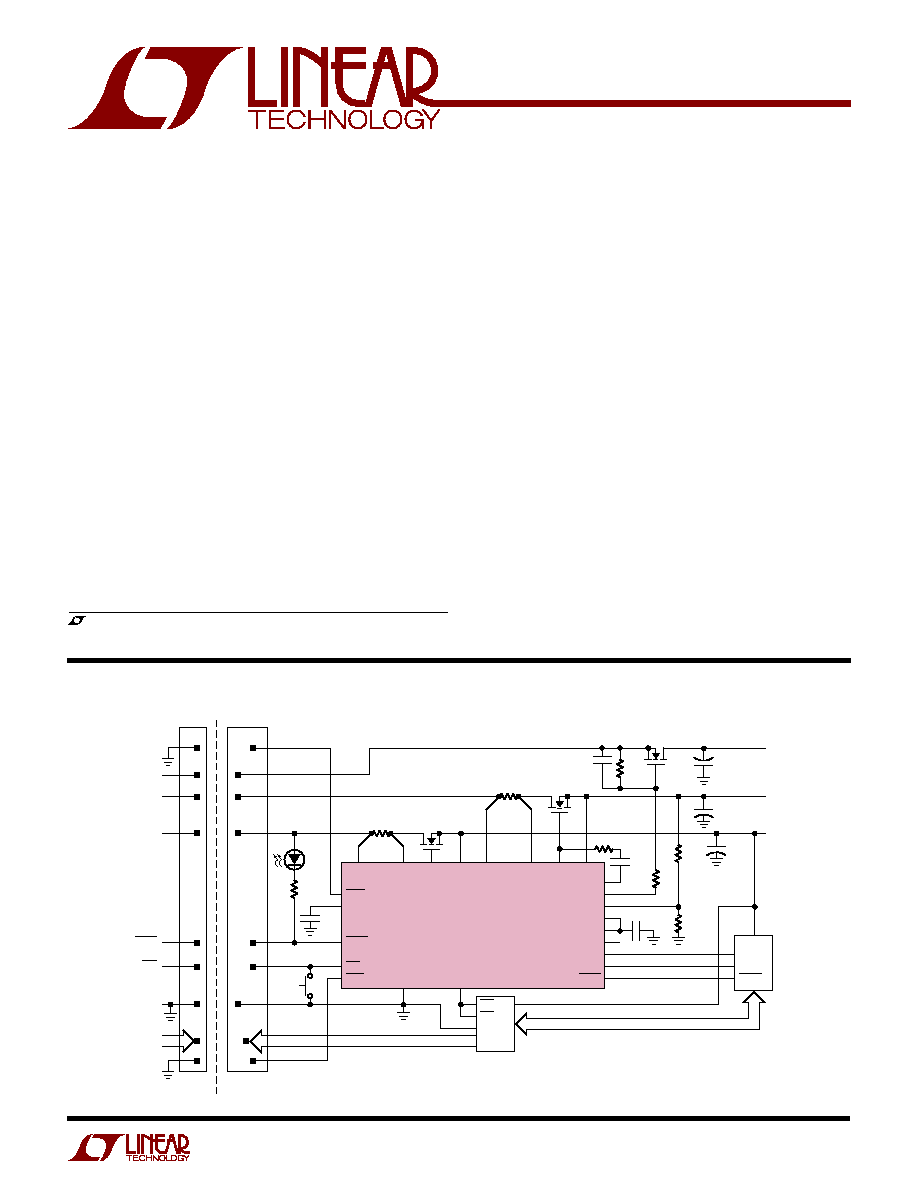

The LTC

®

1421/LTC1421-2.5 are Hot Swap

TM

controllers

that allow a board to be safely inserted and removed from a

live backplane. Using external N-channel pass transistors,

the board supply voltages can be ramped up at a program-

mable rate. Two high side switch drivers control the N-

channel gates for supply voltages ranging from 3V to 12V.

A programmable electronic circuit breaker protects against

shorts. Warning signals indicate that the circuit breaker

has tripped, a power failure has occurred or that the switch

drivers are turned off. The reset output can be used to

generate a system reset when the power cycles or a fault

occurs. The two connect inputs can be used with stag-

gered connector pins to indicate board insertion or re-

moval. The power-on reset input can be used to cycle the

board power or clear the circuit breaker.

The trip point of the ground sense comparator is set at

0.1V for LTC1421 and 2.5V for LTC1421-2.5.

The LTC1421/LTC1421-2.5 are available in 24-pin SO and

SSOP packages.

10

9

14

13

8

11

15

6

7

RAMP

CPON

COMP

COMP

+

REF

FB

COMPOUT

PWRGD

RESET

2

24

4

3

1

CON2

AUXV

CC

FAULT

POR

CON1

V

CCLO

SETLO GATELO V

OUTLO

LTC1421

GND

DISABLE

V

CCHI

SETHI GATEHI V

OUTHI

16

C2

0.1

µ

F

C1

1

µ

F

R5

16k

5%

Q1

MTB50N06E

R1

0.005

17

18

19

20

21

22

5

12

23

R3

1k

STAGGERED CONNECTOR

D1

R6

20k

1%

R4

20k

5%

R7

7.15k

1%

Q2

1/2 Si4936DY

Q3

1/2 Si4936DY

C3

0.47

µ

F

R2

0.025

+

C

LOAD

C

LOAD

C

LOAD

V

EE

12V

1A

V

DD

12V

1A

V

CC

5V

5A

+

+

I/O

I/O

RESET

BEA

BEB

GND

1

13

12

µ

P

QS3384

QuickSwitch

®

QuickSwitch IS A REGISTERED TRADEMARK

OF QUALITY SEMICONDUCTOR CORPORATION.

1421 TA01

DATA BUS

PC BOARD

BACKPLANE

DATA

BUS

GND

POR

FAULT

V

CC

V

DD

V

EE

V

CC

1

µ

F

4

3

2

1

4

3

2

1

10k

, LTC and LT are registered trademarks of Linear Technology Corporation.

Hot Swap is a trademark of Linear Technology Corporation.

DESCRIPTIO

U

FEATURES

APPLICATIO S

U

TYPICAL APPLICATIO

U

2

LTC1421/LTC1421-2.5

ABSOLUTE

M

AXI

M

U

M

RATINGS

W

W

W

U

W

U

U

PACKAGE/ORDER I FOR ATIO

Consult factory for parts specified with wider operating temperature ranges.

(Note 1)

Supply Voltage (V

CCLO

,

V

CCHI

, AUXV

CC

) .............. 13.2V

Input Voltage (Analog Pins) ..... 0.3V to (V

CCHI

+ 0.3V)

Input Voltage (Digital Pins) ................... 0.3V to 13.2V

Output Voltage (Digital Pins) .. 0.3V to (V

CCLO

+ 0.3V)

Output Voltage (CPON) ......... 13.2V to (V

CCLO

+ 0.3V)

Output Voltage (V

OUTLO

, V

OUTHI

) ........... 0.3V to 13.2V

Output Voltage (GATELO, GATEHI) ........... 0.3V to 20V

Operating Temperature Range

LTC1421C ............................................... 0

°

C to 70

°

C

LTC1421I ........................................... 40

°

C to 85

°

C

Storage Temperature Range ................ 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec)................. 300

°

C

ORDER PART

NUMBER

T

JMAX

= 125

°

C,

JA

= 100

°

C/W (G)

T

JMAX

= 125

°

C,

JA

= 85

°

C/W (SW)

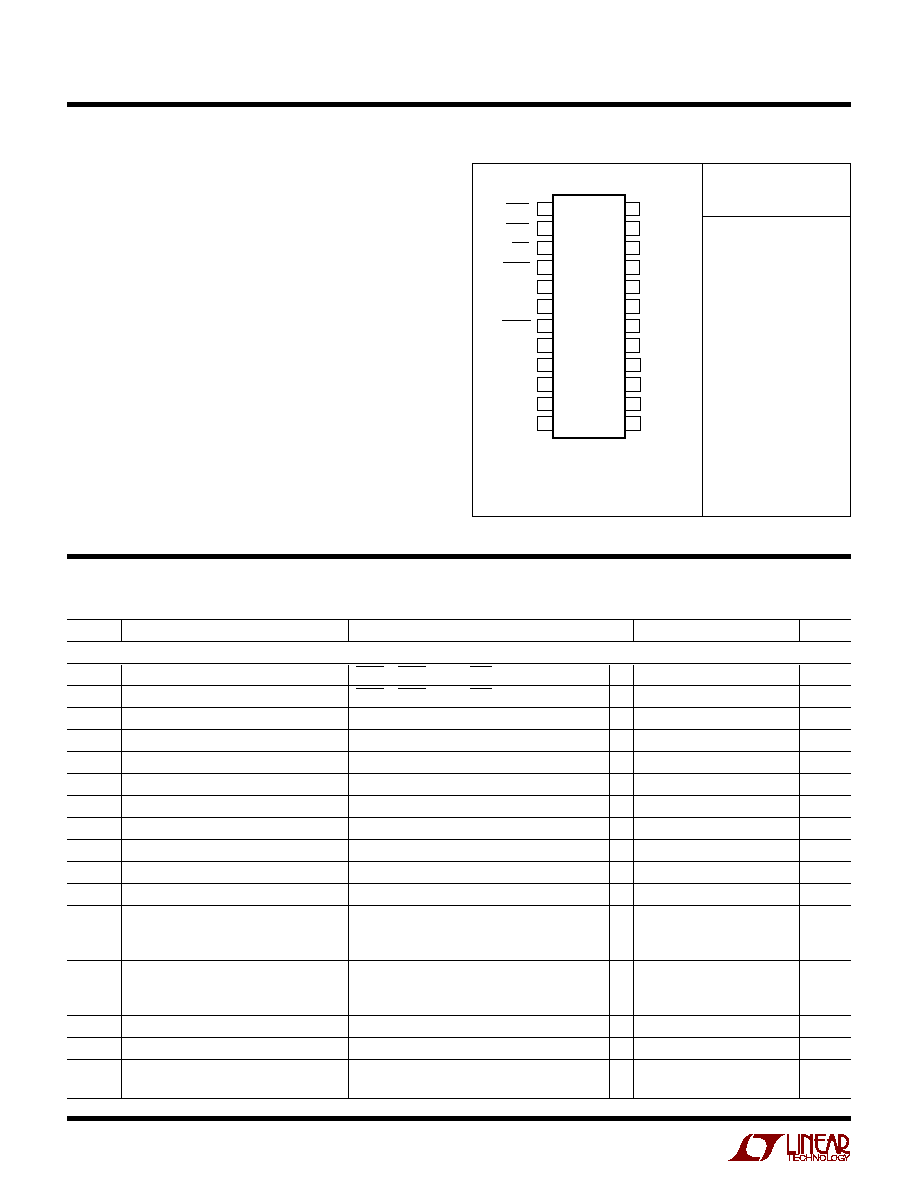

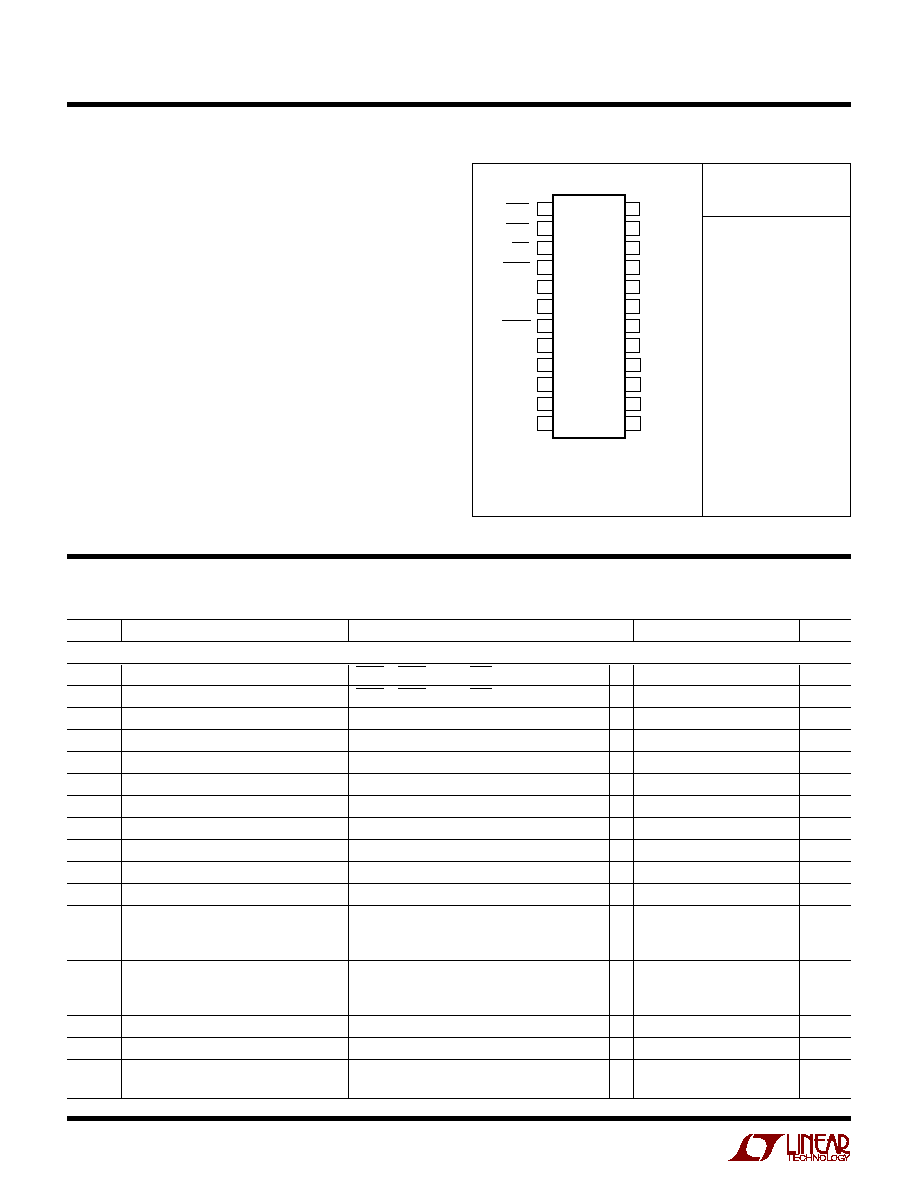

1

2

3

4

5

6

7

8

9

10

11

12

TOP VIEW

SW PACKAGE

24-LEAD PLASTIC SO

G PACKAGE

24-LEAD PLASTIC SSOP

24

23

22

21

20

19

18

17

16

15

14

13

CON1

CON2

POR

FAULT

DISABLE

PWRGD

RESET

REF

CPON

RAMP

FB

GND

AUXV

CC

V

CCLO

SETLO

GATELO

V

OUTLO

V

CCHI

SETHI

GATEHI

V

OUTHI

COMPOUT

COMP

COMP

+

ELECTRICAL CHARACTERISTICS

The

q

denotes specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

°

C. V

CCHI

= 12V, V

CCLO

= 5V unless otherwise noted (Note 2).

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

DC Characteristics

I

CCLO

V

CCLO

Supply Current

CON1 = CON2 = GND, POR = V

CCLO

q

1.5

3

mA

I

CCHI

V

CCHI

Supply Current

CON1 = CON2 = GND, POR = V

CCLO

q

0.6

1

mA

V

LKO

Undervoltage Lockout

V

CCLO

and V

CCHI

2.28

2.45

2.60

V

V

LKH

Undervoltage Lockout Hysteresis

V

CCLO

and V

CCHI

100

mV

V

REF

Reference Output Voltage

No Load

q

1.220

1.232

1.244

V

V

LNR

Reference Line Regulation

3V

V

CCLO

12V, No Load

q

4

8

mV

V

LDR

Reference Load Regulation

I

O

=

0mA to 5mA, Sourcing Only

q

1

3

mV

I

RSC

Reference Short-Circuit Current

V

REF

= 0V

45

mA

V

COF

Comparator Offset Voltage

0V

V

CM

(V

CCLO

-

1.3V)

q

±

10

mV

V

CPSR

Comparator Power Supply Rejection

0V

V

CM

(V

CCLO

-

1.3V), 3V

V

CCLO

12V

q

1

mV/V

V

CHST

Comparator Hysteresis

0V

V

CM

(V

CCLO

-

1.3V)

7

mV

V

RST

Reset Voltage Threshold (V

OUTLO

)

FB = V

OUTLO

q

2.80

2.90

3.00

V

FB = Floating

q

4.50

4.65

4.75

V

FB = GND

q

5.75

5.88

6.01

V

V

RHST

Reset Threshold Hysteresis (V

OUTLO

)

FB = V

OUTLO

7

mV

FB = Floating

12

mV

FB = GND

15

mV

R

FB

FB Pin Input Resistance

0V

V

FB

V

CCLO

95

k

V

CB

Circuit Breaker Trip Voltage

V

CB

= (V

CCLO

V

SETLO

) or V

CB

= (V

CCHI

V

SETHI

)

q

40

50

60

mV

V

TRIP

Output Voltage for Re-Power-Up

LTC1421 (Note 3)

0.1

V

LTC1421-2.5 (Note 4)

2.5

V

LTC1421CG

LTC1421CSW

LTC1421CG-2.5

LTC1421CSW-2.5

LTC1421IG

LTC1421ISW

LTC1421IG-2.5

LTC1421ISW-2.5

3

LTC1421/LTC1421-2.5

Note 3: After power-on reset, the V

OUTLO

and V

OUTHI

have to drop below the

V

TRIP

point before the charge pump is restarted.

Note 4: After power-on reset, the V

OUTLO

has to drop below the V

TRIP

point

before the charge pump is restarted.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are reference to ground unless otherwise

specified.

ELECTRICAL CHARACTERISTICS

The

q

denotes specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25

°

C. V

CCHI

= 12V, V

CCLO

= 5V unless otherwise noted (Note 2).

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

I

RAMP

RAMP Pin Output Current

Charge Pump On, V

RAMP

=

0.4V

q

11

17

23

µ

A

I

CP

Charge Pump Output Current

Charge Pump On, GATEHI = 0V

600

µ

A

GATELO = 0V

300

µ

A

V

GATEHI

GATEHI N-Channel Gate Drive

V

GATEHI

-

V

OUTHI

6

16

V

V

GATELO

GATELO N-Channel Gate Drive

V

GATELO

-

V

OUTLO

10

16

V

V

AUXVCC

Auxiliary V

CC

Output Voltage

V

CCLO

= 5V, Unloaded

4.5

V

V

IL

Input Low Voltage

CON1, CON2, POR

q

0.8

V

V

IH

Input High Voltage

CON1, CON2, POR

q

2

V

I

IN

Input Current

CON1, CON2, POR = GND

q

30

60

90

µ

A

V

OL

Output Low Voltage

RESET, COMPOUT, PWRGD, DISABLE, FAULT,

q

0.4

V

I

O

= 3mA

CPON, I

O

= 3mA

q

1.45

V

V

OH

Output High Voltage

DISABLE, I

O

= 3mA

q

4

V

CPON, I

O

= 1mA

q

3.4

V

I

PU

Logic Output Pull-Up Current

RESET, PWRGD, FAULT = GND

15

µ

A

AC CHARACTERISTICS

t

1

CON1 or CON2

to CPON

Figure 1, C

L

= 15pF

q

15

20

30

ms

t

2

PWRGD

to RESET

Figure 1, R

L

= 10k to V

CCLO

, C

L

= 15pF

160

200

240

ms

q

140

200

280

ms

t

3

PWRGD

to DISABLE

Figure 1, C

L

= 15pF

160

200

240

ms

q

140

200

280

ms

t

4

POR

to CPON

Figure 1, C

L

= 15pF

q

15

20

30

ms

t

5

PWRGD

to RESET

Figure 1, R

L

= 10k to V

CCLO

, C

L

= 15pF

32

µ

s

t

6

POR

to CPON

Figure 1, C

L

= 15pF

50

ns

t

7

CON1 or CON2

to CPON

Figure 1, C

L

= 15pF

50

ns

t

9

Short-Circuit Detect

to FAULT

Figure 1, R

L

= 10k to V

CCLO

, C

L

= 15pF

20

µ

s

V

CCLO

SETLO = 0mV to 100mV

t

10

Short-Circuit Detect

to CPON

Figure 2, C

L

= 15pF

20

µ

s

V

CCLO

SETLO = 0mV to 100mV

t

11

POR

to FAULT

Figure 2, R

L

= 10k to V

CCLO

, C

L

= 15pF

20

ns

t

CHL

Comparator High to Low

COMP

= 1.232V, 10mV Overdrive

q

0.25

0.5

µ

s

R

L

= 10k to V

CCLO

, C

L

= 15pF

t

CLH

Comparator Low to High

COMP

= 1.232V, 10mV Overdrive

q

1

1.5

µ

s

R

L

= 10k to V

CCLO

, C

L

= 15pF

4

LTC1421/LTC1421-2.5

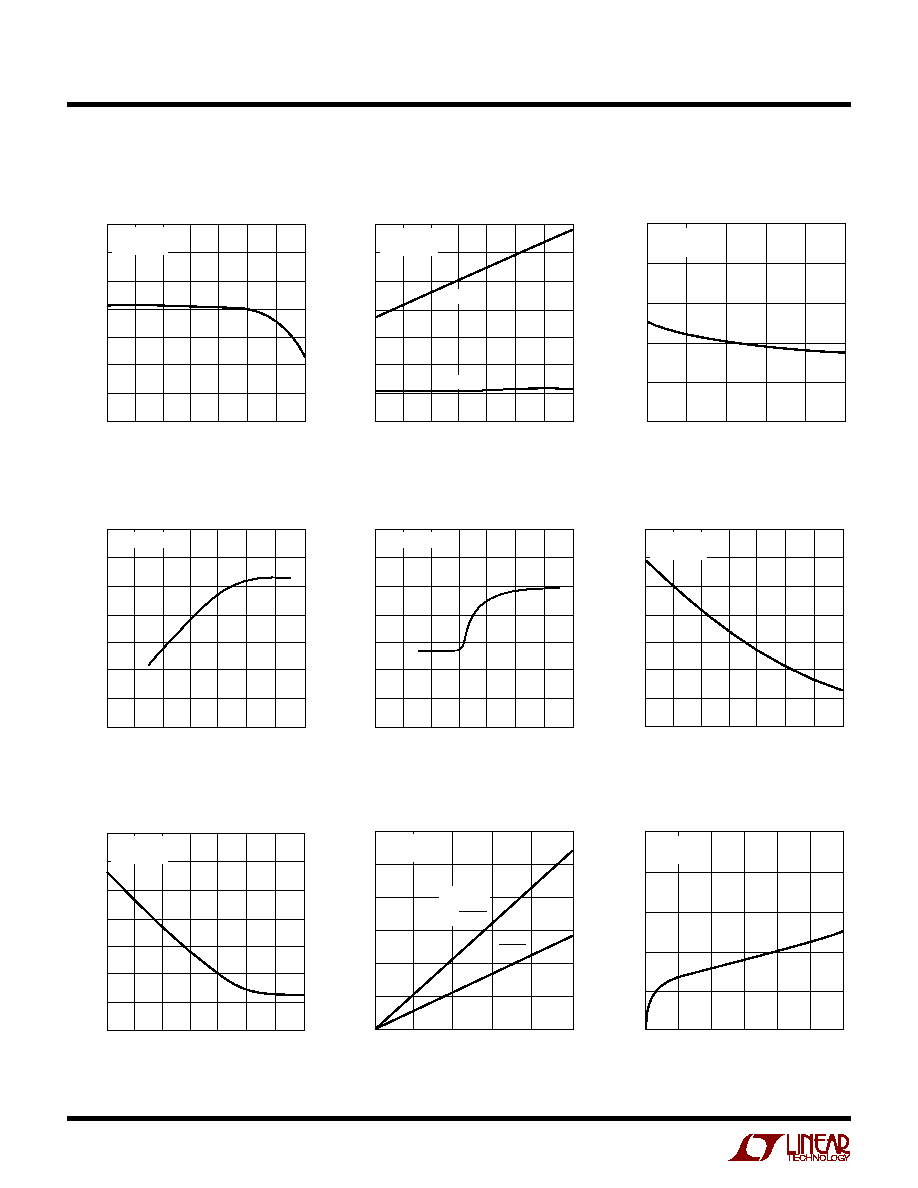

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

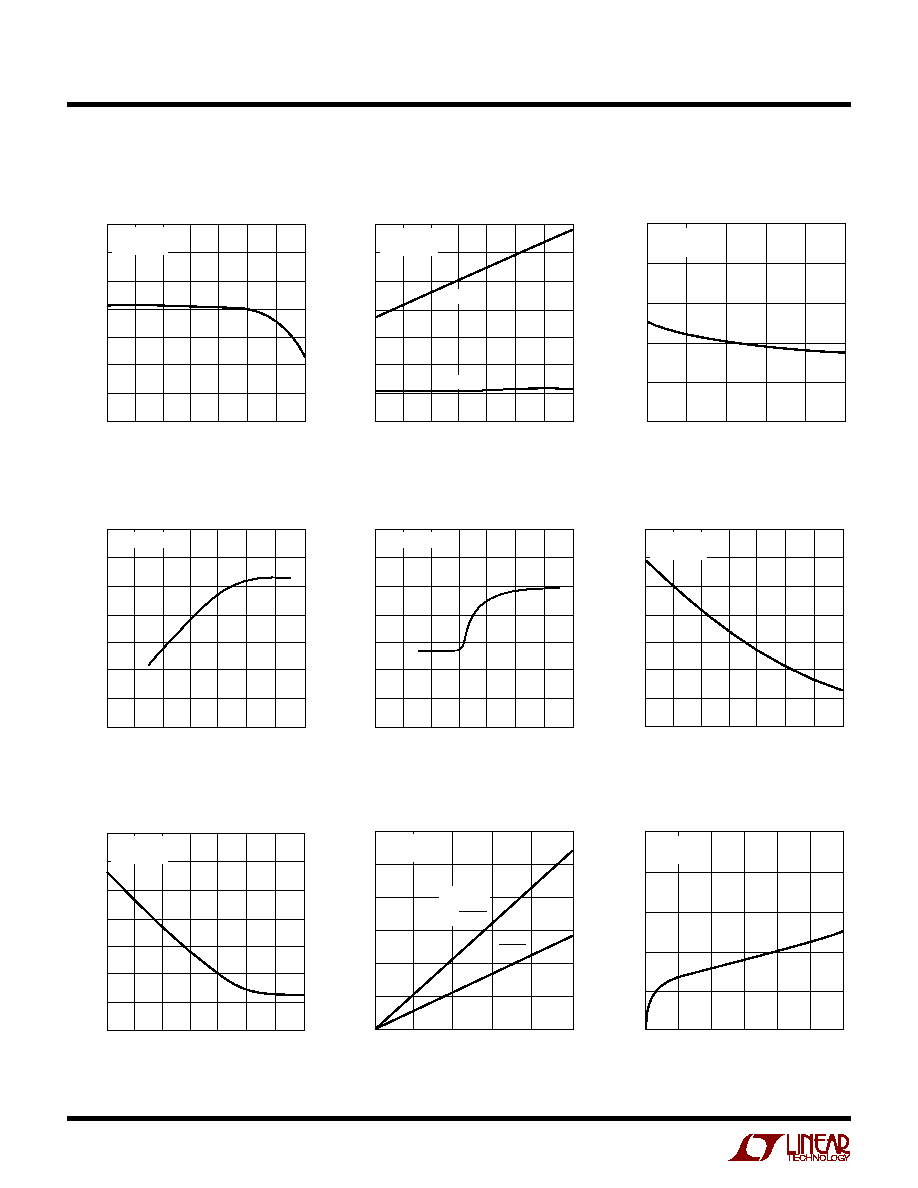

TEMPERATURE (

°

C)

50

1.232

1.234

1.238

25

75

1421 G01

1.230

1.228

25

0

50

100

125

1.226

1.224

1.236

REFERENCE VOLTAGE (V)

V

CCLO

= 5V

V

CCHI

= 12V

Reference Voltage vs

Temperature

SOURCE CURRENT (mA)

0

REFERENCE VOLTAGE (V)

1.235

1.240

1.245

8

1421 G03

1.230

1.225

1.220

2

4

6

10

V

CCLO

= 5V

V

CCHI

= 12V

Reference Voltage

vs Source Current

Gate Voltage vs Temperature

TEMPERATURE (

°

C)

50

21

22

24

25

75

1421 G02

20

19

25

0

50

100

125

18

17

23

GATE VOLTAGE (V)

V

CCLO

= 5V

V

CCHI

= 12V

GATEHI

GATELO

GATELO Voltage vs V

CCLO

Voltage

V

CCLO

VOLTAGE (V)

0

20

22

26

6

10

1421 G04

18

16

2

4

8

12

14

14

12

24

GATELO VOLTAGE (V)

V

CCHI

= 12V

GATEHI Voltage vs V

CCHI

Voltage

V

CCHI

VOLTAGE (V)

0

20

22

26

6

10

1421 G05

18

16

2

4

8

12

14

14

12

24

GATEHI VOLTAGE (V)

V

CCLO

= 5V

I

CCLO

Supply Current

vs Temperature

TEMPERATURE (

°

C)

50

1400

25

75

1421 G06

1300

25

0

50

100

125

1200

1500

I

CCLO

SUPPLY CURRENT (

µ

A)

V

CCLO

= 5V

V

CCHI

= 12V

V

OL

vs I

SINK

CPON Voltage vs Sink Current

(Charge Pump Off)

I

CCHI

Supply Current

vs Temperature

TEMPERATURE (

°

C)

50

540

25

75

1421 G07

530

25

0

50

100

125

520

550

545

535

525

555

I

CCHI

SUPPLY CURRENT (

µ

A)

V

CCLO

= 5V

V

CCHI

= 12V

SINK CURRENT (mA)

0

0

VOLTAGE (mV)

100

200

300

400

500

FAULT

600

2

4

6

8

1421 G08

10

V

CCLO

= 5V

V

CCHI

= 12V

COMPOUT

PWRGD

RESET

SINK CURRENT (mA)

0

0

CPON VOLTAGE (V)

0.5

1.0

1.5

2.0

2.5

0.5

1.0

1.5

2.0

1421 G09

2.5

3.0

V

CCLO

= 5V

V

CCHI

= 12V

5

LTC1421/LTC1421-2.5

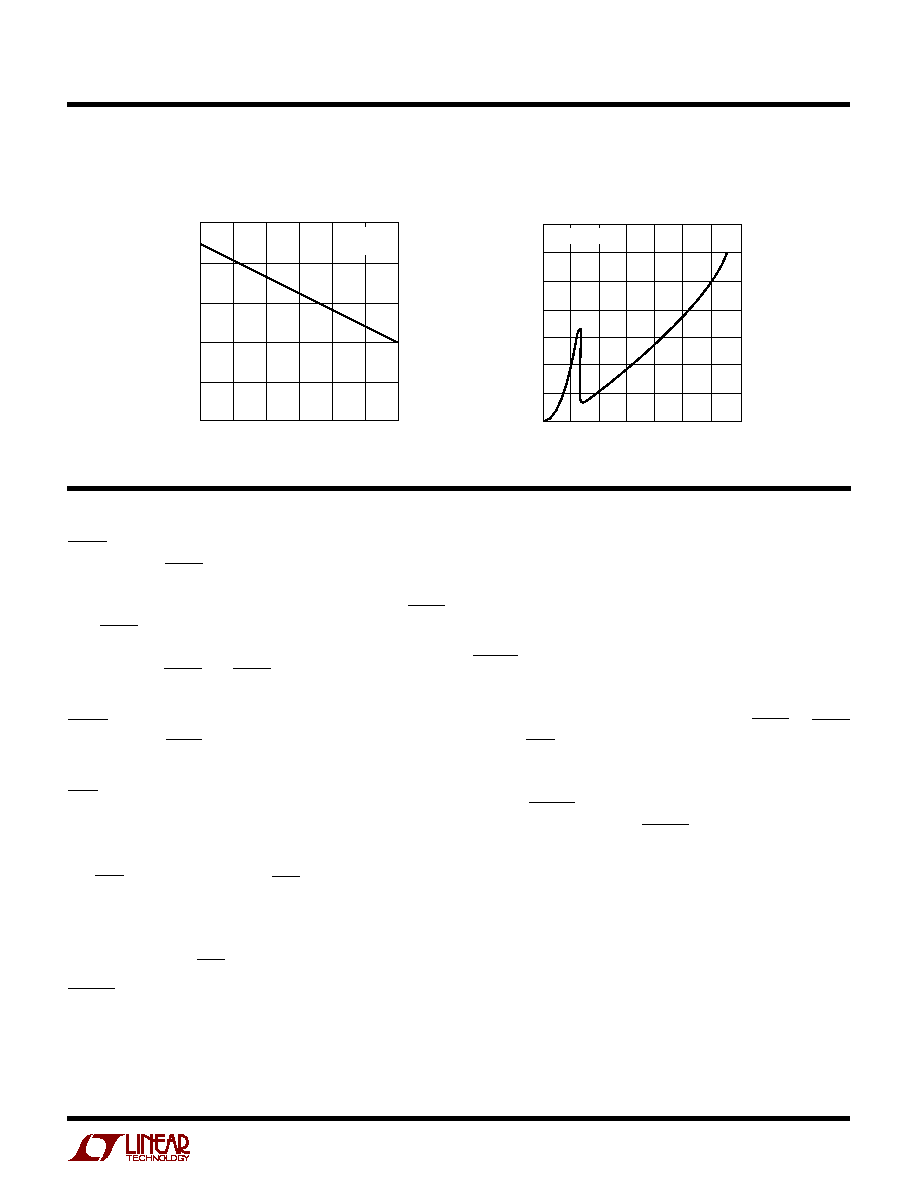

TYPICAL PERFOR

M

A

N

CE CHARACTERISTICS

U

W

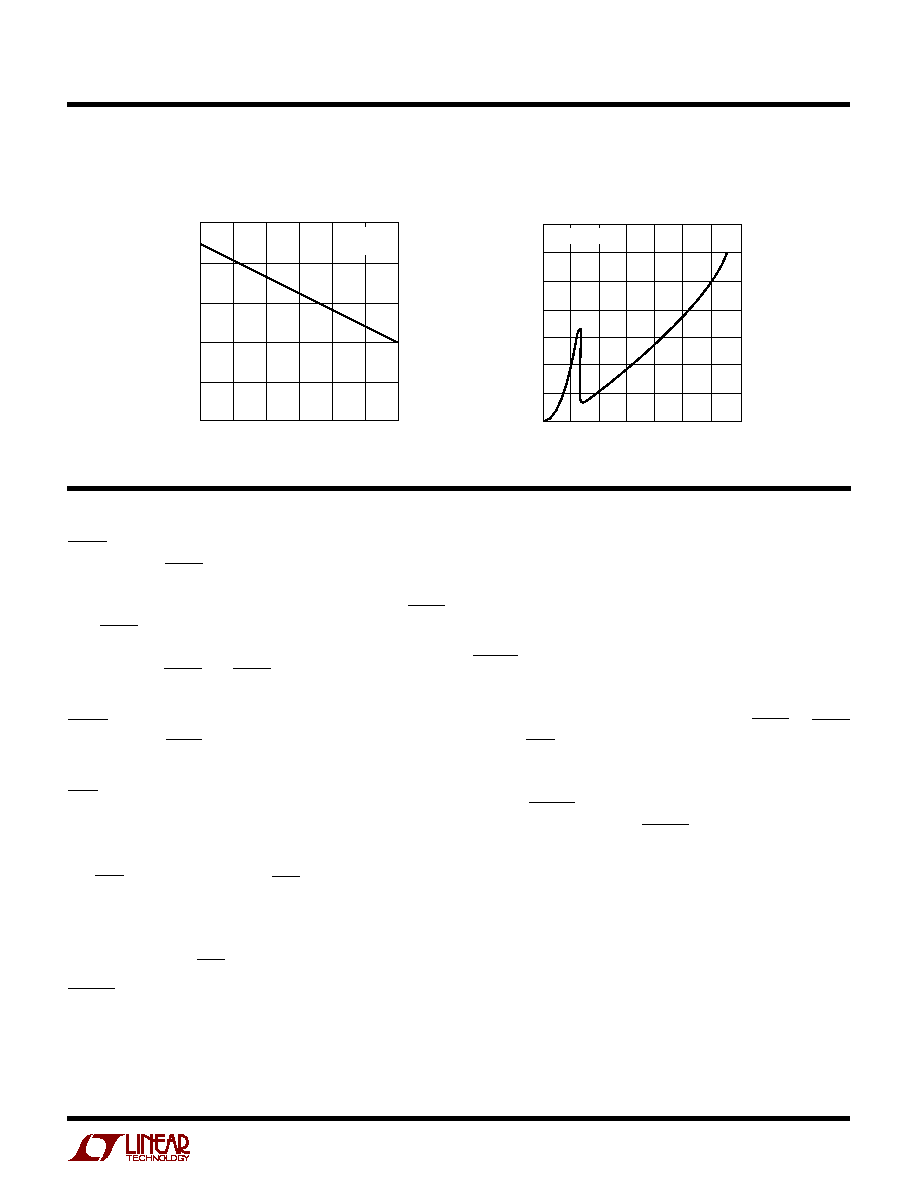

CPON Voltage vs Source Current

(Charge Pump On)

SOURCE CURRENT (mA)

0

0

CPON VOLTAGE (V)

1

2

3

4

5

0.5

1.0

1.5

2.0

1421 G10

2.5

3.0

V

CCLO

= 5V

V

CCHI

= 12V

I

CCLO

Supply Current

vs V

CCLO

Voltage

V

CCLO

VOLTAGE (V)

0

4

5

7

6

10

1421 G11

3

2

2

4

8

12

14

1

0

6

I

CCLO

SUPPLY CURRENT (mA)

V

CCHI

= 12V

PI

N

FU

N

CTIO

N

S

U

U

U

CON1 (Pin 1): TTL Level Input with a Pull-Up to V

CCLO

.

Together with CON2, it is used to indicate board connec-

tion. The pin must be tied to ground on the host side of the

connector. When using staggered connector pins, CON1

and CON2 must be the shortest and must be placed at

opposite corners of the connector. Board insertion is

assumed after CON1 and CON2 are both held low for 20ms

after power-up.

CON2 (Pin 2): TTL Level Input with a Pull-Up to V

CCLO

.

Together with CON1 it is used to indicate board connec-

tion.

POR (Pin 3): TTL Level Input with a Pull-Up to V

CCLO

.

When the pin is pulled low for at least 20ms, a hard reset

is generated. Both V

OUTLO

and V

OUTHI

will turn off at a

controlled rate. A power-up sequence will not start until

the POR pin is pulled high. If POR is pulled high before

V

OUTLO

and V

OUTHI

are fully discharged, a power-up

sequence will not begin until the voltage at V

OUTLO

and

V

OUTHI

are below V

TRIP

. The electronic circuit breaker will

be reset by pulling POR low.

FAULT (Pin 4): Open Drain Output to GND with a Weak

Pull-Up to V

CCLO

. The pin is pulled low when an overcur-

rent fault is detected at V

OUTLO

or V

OUTHI

.

DISABLE (Pin 5): CMOS Output. The signal is used to

disable the board's data bus during insertion or removal.

PWRGD (Pin 6): Open Drain Output to GND with a Weak

Pull-Up to V

CCLO

. The pin is pulled low immediately after

V

OUTLO

falls below its reset threshold voltage. The pin is

pulled high immediately after V

OUTLO

rises above its reset

threshold voltage.

RESET (Pin 7): Open Drain Output to GND with a Weak

Pull-Up to V

CCLO

. The pin is pulled low when a reset

condition is detected. A reset will be generated when any

of the following conditions are met: Either CON1 or CON2

is high, POR is pulled low, V

CCLO

or V

CCHI

are below their

respective undervoltage lockout thresholds, PWRGD goes

low or an overcurrent fault is detected at V

OUTLO

or

V

OUTHI

. RESET will go high 200ms after PWRGD goes

high. On power failure, RESET will go low 32

µ

s after

PWRGD goes low.

REF (Pin 8): The Reference Voltage Output. V

OUT

= 1.232V

±

1%. The reference can source up to 5mA of current. A

1

µ

F bypass capacitor is recommended.

CPON (Pin 9): CMOS Output That Can Be Pulled Below

Ground. CPON is pulled high when the internal charge

pumps for GATELO and GATEHI are turned on. CPON is

pulled low when the charge pumps are turned off. The pin

can be used to control an external MOSFET for a 5V to

12V supply.