| ÐлекÑÑоннÑй компоненÑ: LTC1873 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1

LTC1873

Dual 550kHz Synchronous

2-Phase Switching Regulator

Controller with 5-Bit VID

The LTC

®

1873 is a dual switching regulator controller opti-

mized for high efficiency with low input voltages. It includes

two complete, on-chip, independent switching regulator con-

trollers. Each is designed to drive a pair of external

N-channel MOSFETs in a voltage mode feedback, synchro-

nous buck configuration. The LTC1873 includes digital out-

put voltage adjustment on side 1 that conforms to the Intel

Desktop VID specification. A constant-frequency, true PWM

design minimizes external component size and cost and

optimizes load transient performance. The synchronous buck

architecture automatically shifts to discontinuous and then to

Burst Mode

TM

operation as the output load decreases, ensur-

ing maximum efficiency over a wide range of load currents.

The LTC1873 features an onboard reference trimmed to 1%

and delivers better than 1.5% regulation at the converter

outputs over all combinations of line, load and temperature.

Each channel can be enabled independently; with both chan-

nels disabled, the LTC1873 shuts down and supply current

drops below 100

µ

A.

s

Two Independent PWM Controllers in One Package

s

Side 1 Output Is Compliant with Intel

Desktop

VRM 8.4 Specifications (Includes 5-Bit VID DAC)

s

1.3V to 3.5V Output Voltage with 50mV/100mV Steps

s

Two Sides Run Out-of-Phase to Minimize C

IN

s

All N-Channel External MOSFET Architecture

s

No External Current Sense Resistors Required

s

Precison Internal 0.8V

±

1% Reference

s

550kHz Switching Frequency Minimizes External

Component Size

s

Very Fast Transient Response

s

Up to 25A Output Current per Channel

s

Low Shutdown Current: < 100

µ

A

s

Small 28-Pin SSOP Package

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode is a trademark of Linear Technology Corporation.

s

Microprocessor Core and I/O Supplies

s

Multiple Logic Supply Generator

s

High Efficiency Power Conversion

s

Chipset Power Supply

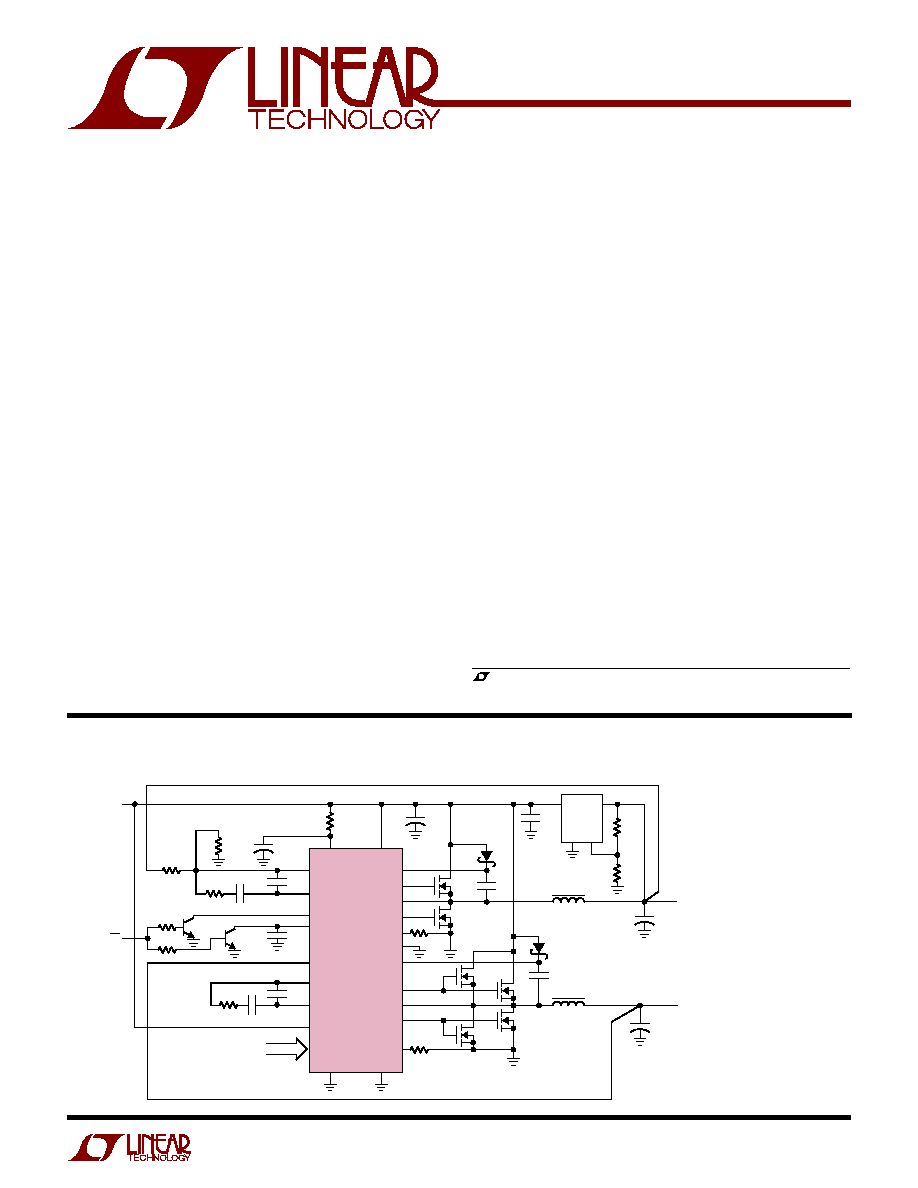

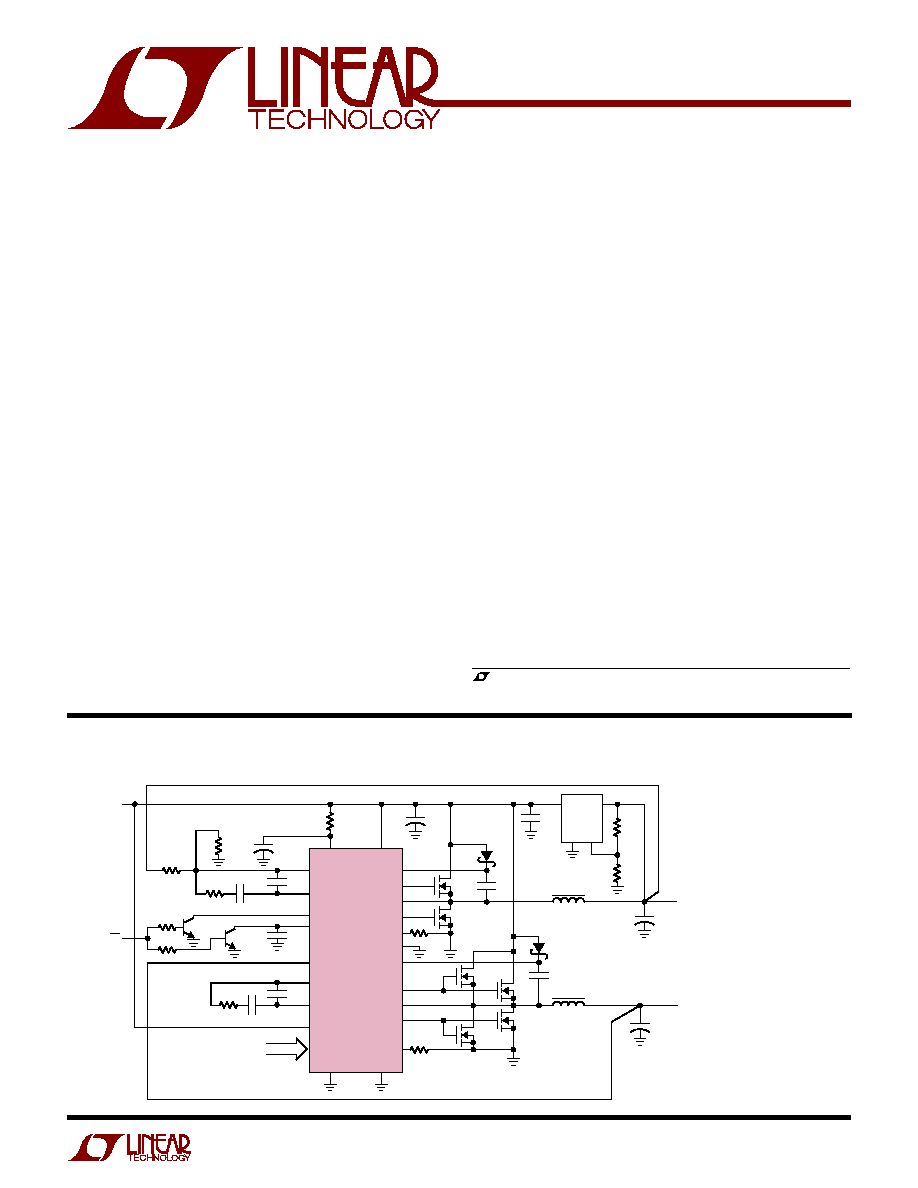

Low Cost Desktop CPU Supply with RDRAM Keepalive

+

FB2

COMP2

RUN/SS2

FB1

COMP1

FCB

VID4:0

BOOST2

TG2

SW2

BG2

I

MAX2

V

CC

PV

CC

SGND

PGND

LTC1873

4.75k

0.1%

0.1

µ

F

39pF

56pF

220pF

330pF

56k

QSS2

QSS1

C

IN

= SANYO 10MV1200GX (6 IN PARALLEL)

C

OUT1

= SANYO 6MV1500GX (8 IN PARALLEL)

C

OUT2

= SANYO 6MV1500GX (3 IN PARALLEL)

L1: 1

µ

H SUMIDA CEP125-1R0MC-H

L2: 2.2

µ

H COILTRONICS UP2B-2R2

QSS1, QSS2: MOTOROLA MMBT3904LT1

QT1A, QT1B, QB1A, QB1B: FAIRCHILD FDS6670A

QT2, QB2: 1/2 SILICONIX Si4966

4.5V TO 5.5V

STBY/ON

5-BIT VID

1k

68k

1k

10k

0.1%

47k

QT2

MBR0530T

1

µ

F

QB2

QT1A

QT1B

MBR0530T

1

µ

F

C

OUT1

1873 TA01

+

C

OUT2

+

10

µ

F

+

C

IN

1

µ

F

16.9k

0.1%

16.2k

0.1%

V

RDRAM

2.5V/7A

2.45V/100mA STANDBY

V

CORE

1.3V TO 3.5V

20A

10

L1

QB1A

QB1B

33k

FAULT

BOOST1

TG1

SW1

BG1

I

MAX1

L2

IN

OUT

GND

LT1761

ADJ

RUN/SS1

SENSE

DESCRIPTIO

U

FEATURES

APPLICATIO S

U

TYPICAL APPLICATIO

U

2

LTC1873

(Note 1)

Supply Voltage

V

CC ...........................................................................................

7V

BOOST

n ............................................................... 15V

BOOST

n SWn .................................................... 7V

Input Voltage

SW

n .......................................................... 1V to 8V

VID

n ....................................................... 0.3V to 7V

All Other Inputs ......................... 0.3V to V

CC

+ 0.3V

Peak Output Current < 10

µ

s

TG

n, BGn ............................................................... 5A

Operating Temperature Range

(Note 2) ............................................. 40

°

C to 85

°

C

Storage Temperature Range ................. 65

°

C to 150

°

C

Lead Temperature (Soldering, 10 sec).................. 300

°

C

ORDER PART

NUMBER

T

JMAX

= 125

°

C,

JA

= 55

°

C/ W

LTC1873EG

Consult factory for Industrial and Military grade parts.

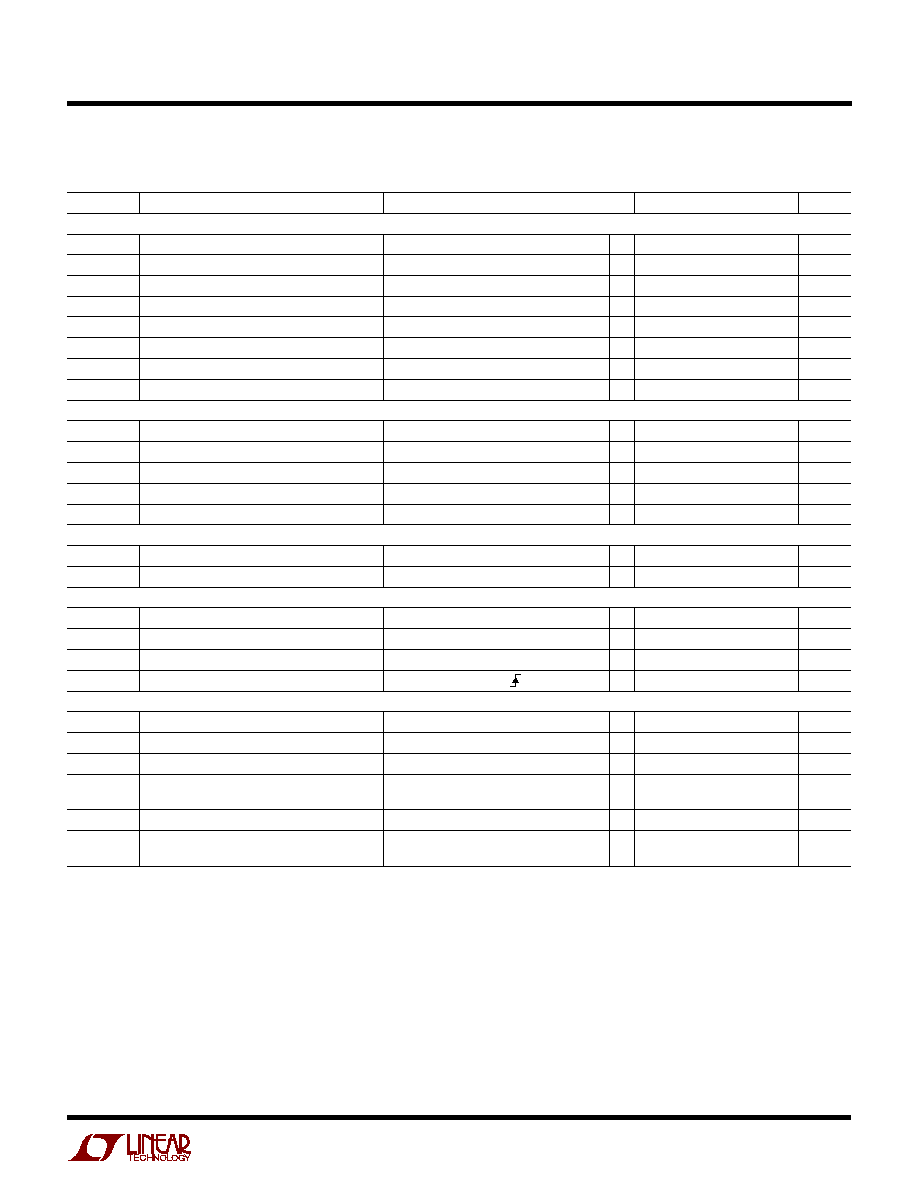

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Main Control Loop

V

CC

V

CC

Supply Voltage

q

3

7

V

PV

CC

PV

CC

Supply Voltage

(Note 3)

q

3

7

V

BV

CC

BOOST Pin Voltage

V

BOOST

V

SW

(Note 3)

q

2.7

7

V

I

CC

V

CC

Supply Current

Test Circuit 1

q

2.2

8

mA

RUN/SS1 = RUN/SS2 = 0V (Note 6)

q

30

100

µ

A

IPV

CC

PV

CC

Supply Current

Test Circuit 1 (Note 5)

q

2.2

6

mA

RUN/SS1 = RUN/SS2 = 0V (Note 6)

q

6

100

µ

A

I

BOOST

BOOST Pin Current

Test Circuit 1 (Note 5)

q

1.3

3

mA

RUN/SS1 = RUN/SS2 = 0V

q

0.1

10

µ

A

V

FB

Feedback Voltage

Test Circuit 1

q

0.790

0.800

0.810

V

V

FB

Feedback Voltage Line Regulation

V

CC

= 3V to 7V

q

±

0.005

±

0.05

%/V

I

FB

Feedback Current

FB2 Only (Note 7)

q

±

0.001

±

1

µ

A

V

FCB

FCB Threshold

q

0.75

0.8

0.85

V

V

FCB

FCB Feedback Hysteresis

20

mV

I

FCB

FCB Pin Current

q

±

0.001

±

1

µ

A

V

RUN

RUN/SS Pin RUN Threshold

q

0.45

0.55

0.65

V

I

SS

Soft Start Source Current

RUN/SS

n = 0V

1.5

3.5

5.5

µ

A

The

q

denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25

°

C.

V

CC

= 5V unless otherwise specified. (Note 4)

1

2

3

4

5

6

7

8

9

10

11

12

13

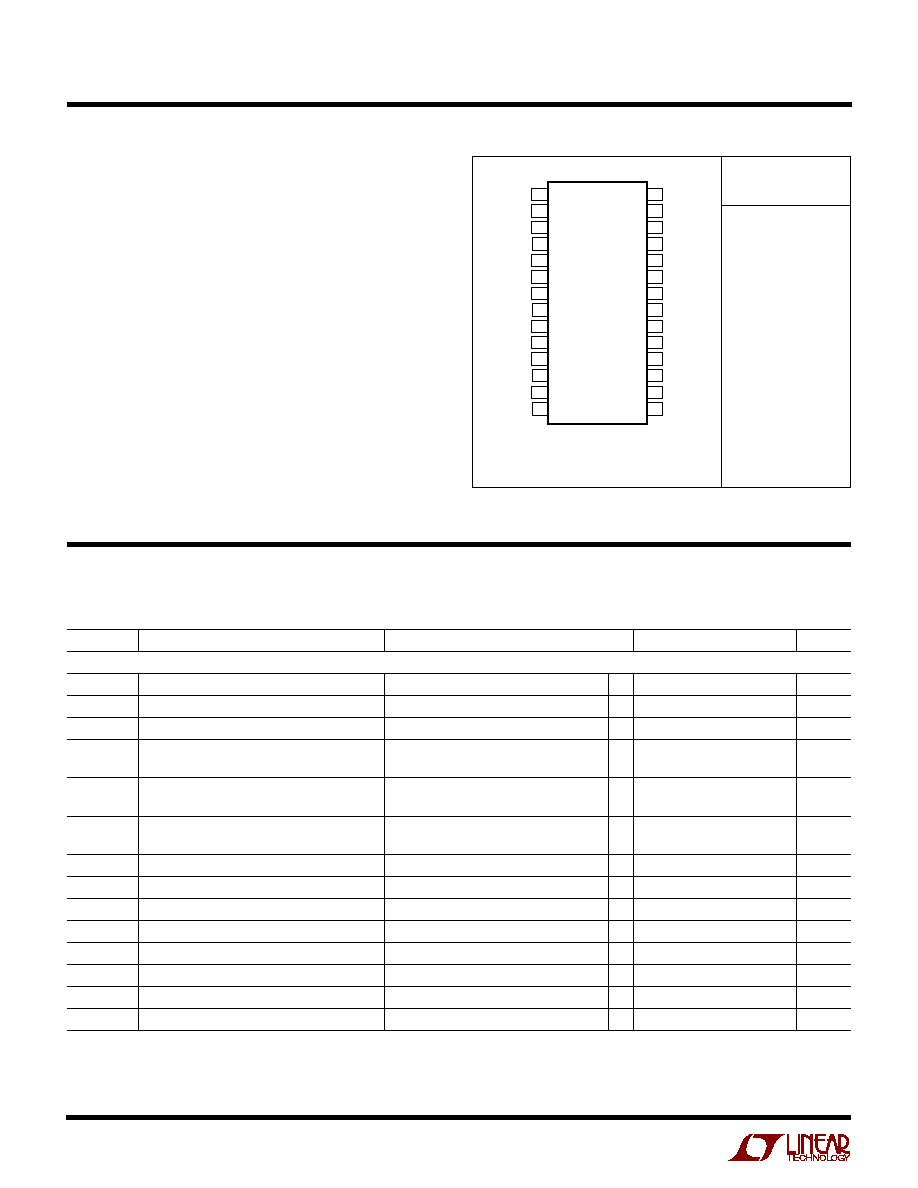

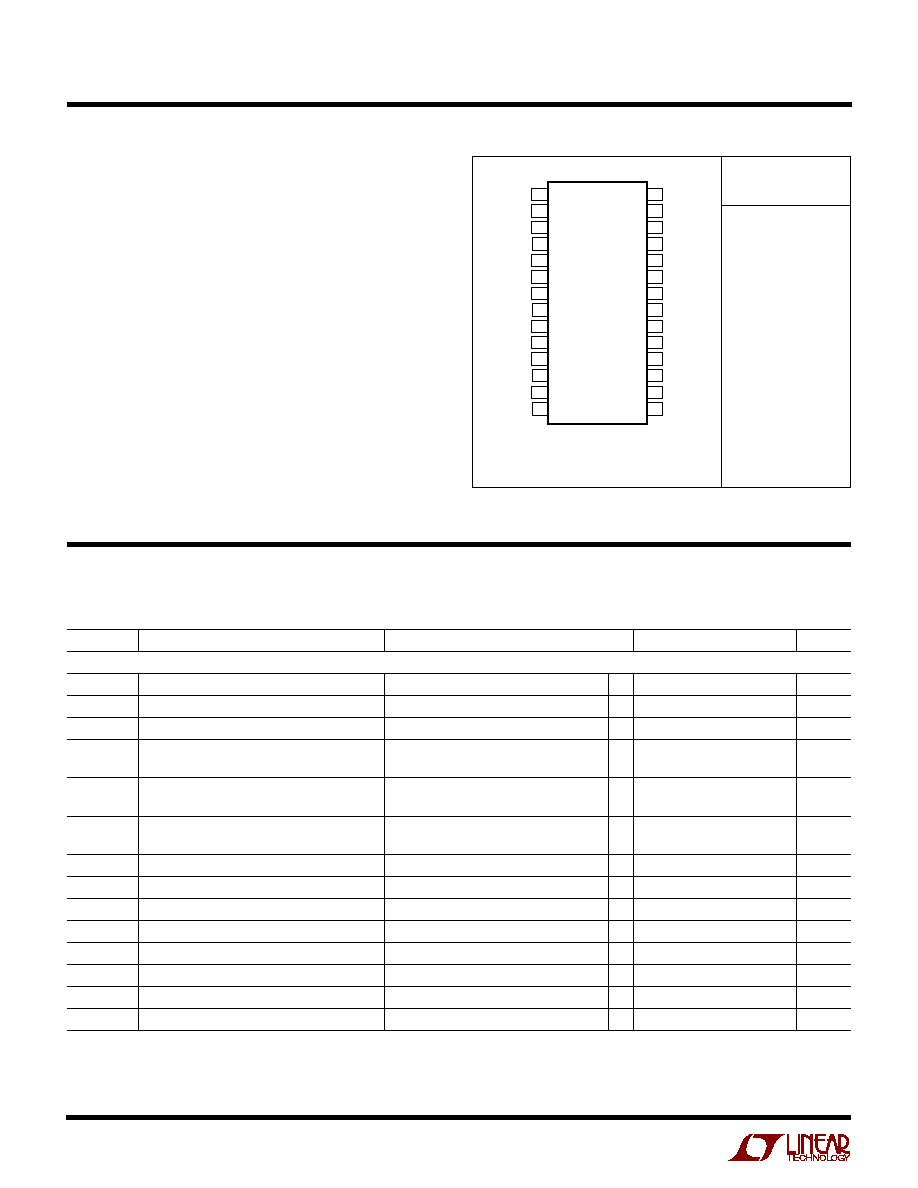

14

TOP VIEW

G PACKAGE

28-LEAD PLASTIC SSOP

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PV

CC

BOOST1

BG1

TG1

SW1

I

MAX1

FCB

RUN/SS1

COMP1

SGND

FB1

SENSE

VID0

VID1

I

MAX2

BOOST2

BG2

TG2

SW2

PGND

FAULT

RUN/SS2

COMP2

FB2

V

CC

VID4

VID3

VID2

ABSOLUTE AXI U RATI GS

W

W

W

U

PACKAGE/ORDER I FOR ATIO

U

U

W

ELECTRICAL CHARACTERISTICS

3

LTC1873

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The LTC1873 is guaranteed to meet performance specifications

from 0

°

C to 70

°

C. Specifications over the 40

°

C to 85

°

C operating

temperature range are assured by design, characterization and correlation

with statistical process controls.

Note 3: PV

CC

and BV

CC

(V

BOOST

V

SW

) must be greater than V

GS(ON)

of

the external MOSFETs used to ensure proper operation.

Note 4: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are referenced to ground unless otherwise

specified.

The

q

denotes specifications which apply over the full operating temperature range, otherwise specifications are TA = 25

°

C.

V

CC

= 5V unless otherwise specified. (Note 4)

Note 5: Supply current in normal operation is dominated by the current

needed to charge and discharge the external MOSFET gates. This current

will vary with supply voltage and the external MOSFETs used.

Note 6: Supply current in shutdown is dominated by external MOSFET

leakage and may be significantly higher than the quiescent current drawn

by the LTC1873, especially at elevated temperature.

Note 7: Feedback current at FB1 will be higher due to internal VID

resistors.

Note 8: Each built-in pull-up resistor attached to the VID inputs also has a

series diode connected to V

CC

to allow input voltages higher than the V

CC

supply without damage or clamping. (See Block Diagram.)

Note 9: Rise and fall times are measured at 20% to 80% levels. Delay and

nonoverlap times are measured using 50% levels.

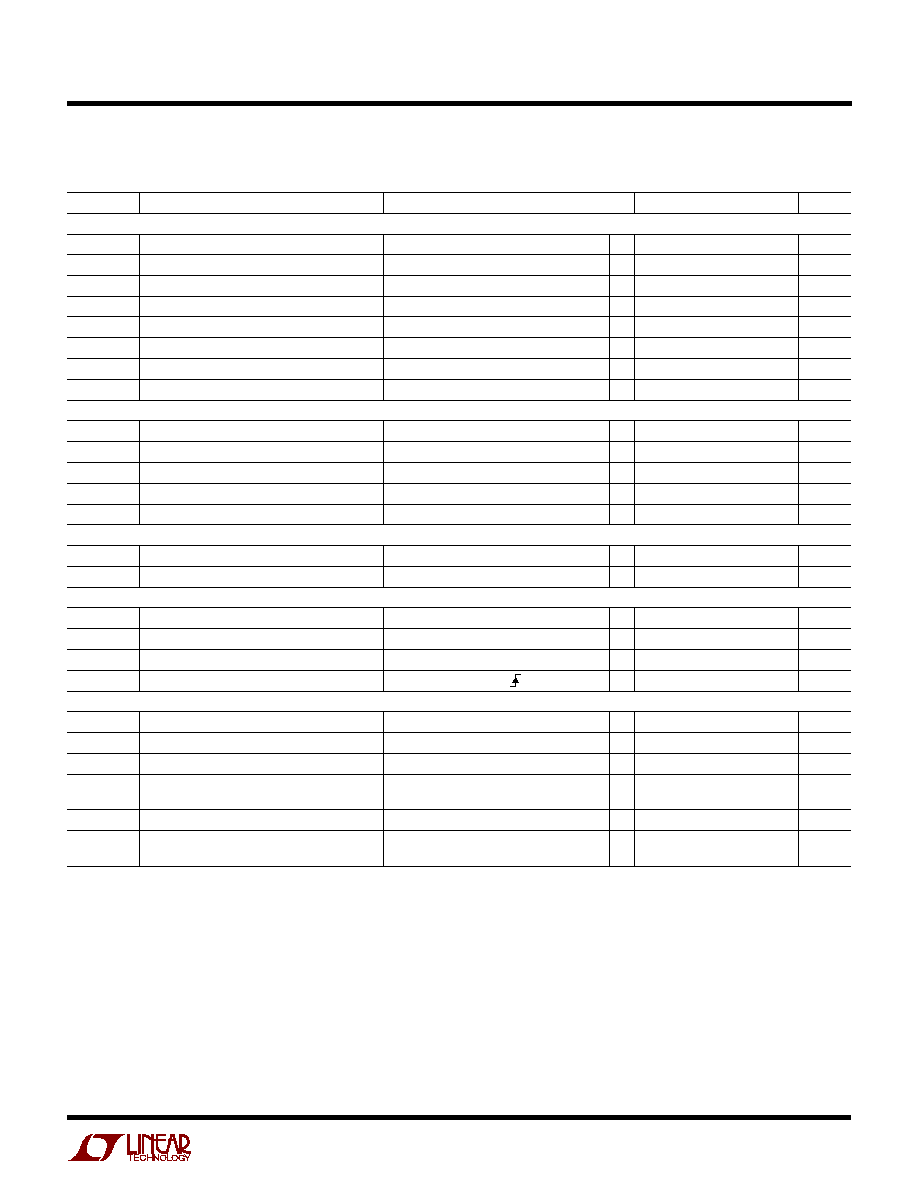

ELECTRICAL CHARACTERISTICS

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Switching Characteristics

V

OSC

Oscillator Amplitude

1

V

P-P

f

OSC

Oscillator Frequency

Test Circuit 1

q

475

550

750

kHz

OSC2

Controller 2 Oscillator Phase

Relative to Controller 1

180

DEG

DC

MIN1

Minimum Duty Cycle

V

FB

< V

MAX

q

7

10

%

DC

MIN2

Minimum Duty Cycle

V

FB

> V

MAX

q

0

%

DC

MAX

Maximum Duty Cycle

q

87

90

93

%

t

NOV

Driver Nonoverlap

Test Circuit 1 (Note 9)

q

40

100

ns

t

r

, t

f

Driver Rise/Fall Time

Test Circuit 1 (Note 9)

q

12

80

ns

Feedback Amplifier

A

VFB

FB DC Gain

q

74

85

dB

GBW

FB Gain Bandwidth

25

MHz

I

ERR

FB Sink/Source Current

COMP

N

Output

q

±

3

±

10

mA

V

MIN

MIN Comparator Threshold

q

760

785

mV

V

MAX

MAX Comparator Threshold

q

815

840

mV

Current Limit Loop

A

VILIM

I

LIM

Gain

40

dB

I

IMAX

I

MAX

Source Current

I

MAX

= 0V

q

7

10

14

µ

A

Status Outputs

V

FAULT

FAULT Trip Point

V

FB

Relative to Regulated V

OUT

q

+ 10

+ 15

+ 20

%

V

OLF

FAULT Output Low Voltage

I

FAULT

= 1mA

q

0.03

0.1

V

I

FAULT

FAULT Output Current

V

FAULT

= 0V

10

µ

A

t

FAULT

FAULT Delay Time

V

FB

> V

FAULT

to FAULT (Note 9)

25

µ

s

VID Inputs

R1

Resistance Between SENSE and FB1

Side 1 Only

20

k

V

OUT

Error %

Output Voltage Accuracy

Programmed from 1.3V to 3.5V

q

1.5

1.5

%

R

PULLUP

VID Input Pull-Up Resistance

V

DIODE

= 0.6V (Note 8)

40

k

VID

T

VID Input Voltage Threshold

V

IL

(2.7V

V

CC

5.5V)

0.4

V

V

IH

(2.7V

V

CC

5.5V)

1.6

V

I

VID-LEAK

VID Input Leakage Current

V

CC

< VID < 7V (Note 8)

0.01

±

1

µ

A

V

PULLUP

VID Pull-Up Voltage

V

CC

= 3.3V

2.8

V

V

CC

= 5V

4.5

V

4

LTC1873

10

µ

s/DIV

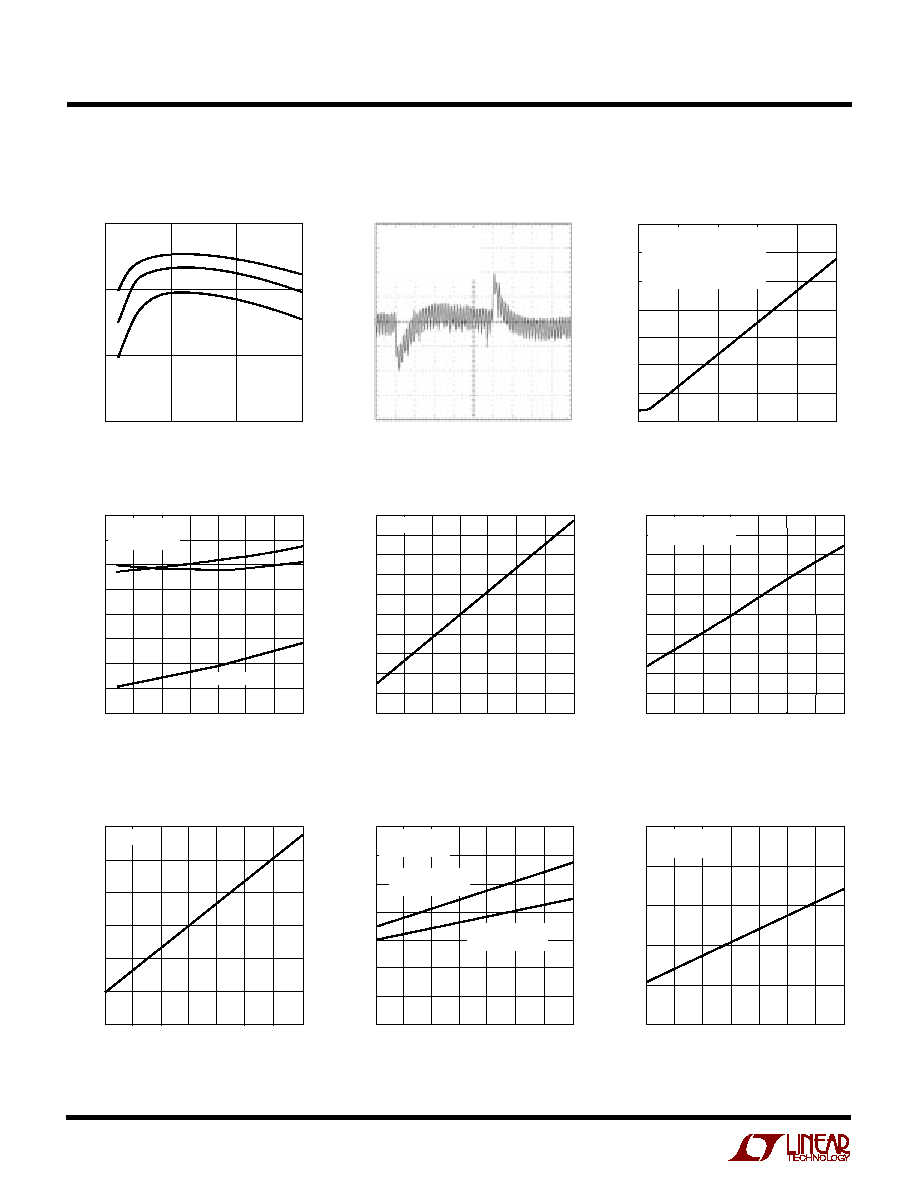

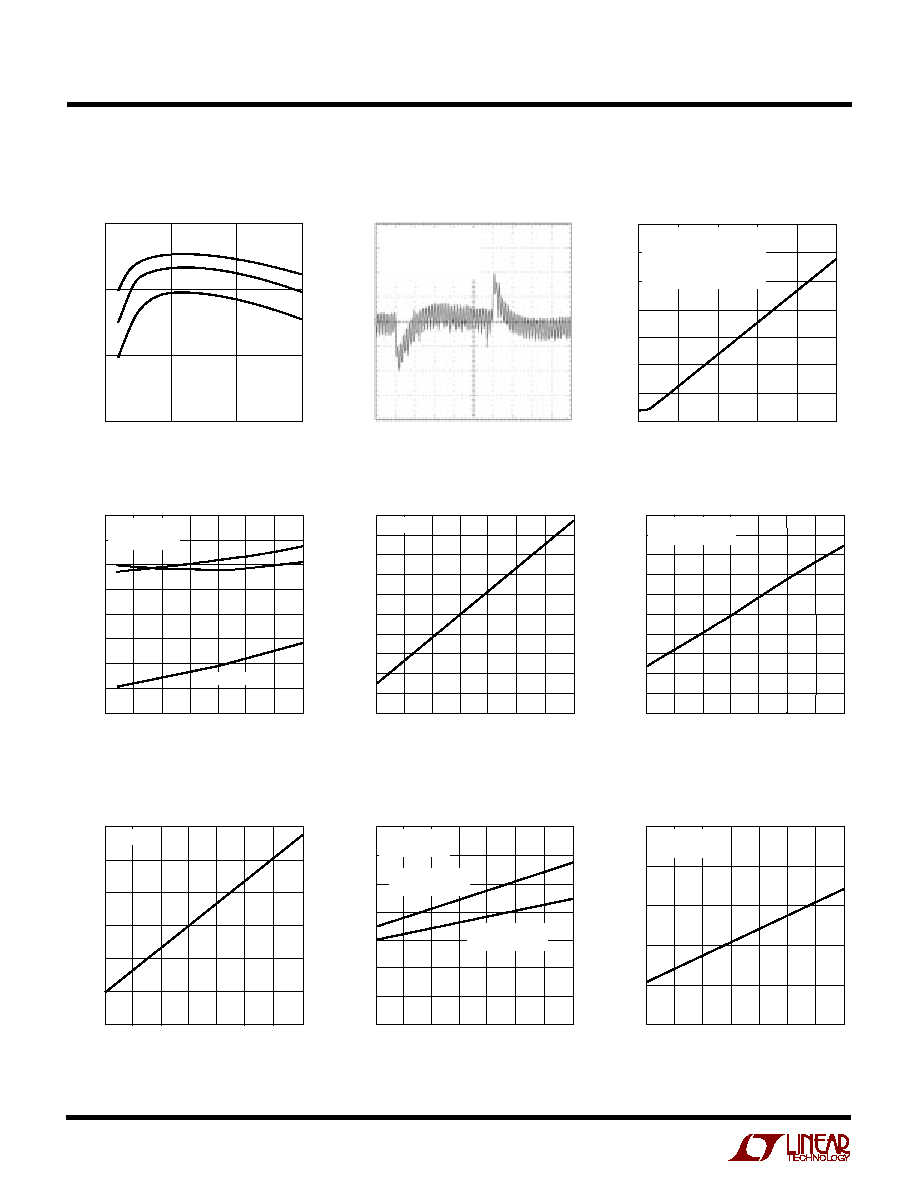

TYPICAL PERFOR A CE CHARACTERISTICS

U

W

Efficiency vs Load Current

TEMPERATURE (

°

C)

50

SUPPLY CURRENT (mA)

2.4

PV

CC

V

CC

25

1873 G04

1.8

1.4

25

0

50

1.2

1.0

2.6

2.2

2.0

1.6

75

100

125

BOOST1, BOOST2

TEST CIRCUIT 1

C

L

= 0pF

Transient Response

TEMPERATURE (

°

C)

50

2.5

FREQUENCY DRIFT (%)

2.0

1.0

0.5

0

2.5

1.0

0

50

75

1873 G05

1.5

1.5

2.0

0.5

25

25

100

125

V

CC

= 5V

TEMPERATURE (

°

C)

50

0.4

R

ON

(

)

0.5

0.7

0.8

0.9

1.4

1.1

0

50

75

1873 G06

0.6

1.2

1.3

1.0

25

25

100

125

V

PVCC

= 5V

V

BOOST

V

SW

= 5V

MOSFET Driver Supply Current

vs Gate Capacitance

Supply Current vs Temperature

Frequency Drift vs Temperature

Driver R

ON

vs Temperature

RUN/SS Source Current

vs Temperature

TEMPERATURE (

°

C)

50

SOURCE CURRENT (

µ

A)

4.0

4.5

5.0

25

75

1873 G07

3.5

3.0

25

0

50

100

125

2.5

2.0

V

CC

= 5V

Nonoverlap Time vs Temperature

Driver Rise/Fall vs Temperature

LOAD CURRENT (A)

0

70

EFFICIENCY (%)

80

90

100

5

10

1873 G01

15

V

IN

= 5V

V

OUT

= 3.3V

V

OUT

= 2.5V

V

OUT

= 1.6V

V

IN

= 5V

V

OUT

= 1.8V

I

LOAD

= 0A-10A-0A

±

2.2% MAX DEVIATION

1873 G02

GATE CAPACITANCE (pF)

0

25

30

35

6000

8000

1873 G03

20

15

2000

4000

10000

10

5

0

DRIVER SUPPLY CURRENT (mA)

TEST CIRCUIT 1

ONE DRIVER LOADED

MULTIPLY BY # OF ACTIVE

DRIVERS TO OBTAIN TOTAL

DRIVER SUPPLY CURRENT

TEMPERATURE (

°

C)

50

40

50

70

25

75

1873 G08

30

20

25

0

50

100

125

10

0

60

NONOVERLAP TIME (ns)

TEST CIRCUIT 1

C

L

= 2000pF

BG FALLING EDGE

TG RISING EDGE

TG FALLING EDGE

BG RISING EDGE

TEMPERATURE (

°

C)

50

25

12

RISE/FALL TIME (ns)

12

15

0

50

75

1873 G09

11

14

13

25

100

125

TEST CIRCUIT 1

C

L

= 2000pF

20mV/

DIV

5

LTC1873

FCB (Pin 7): Force Continuous Bar. The FCB pin forces

both converters to maintain continuous synchronous

operation regardless of load when the voltage at FCB

drops below 0.8V. FCB is normally tied to V

CC

. To force

continuous operation, tie FCB to SGND. FCB can also be

connected to a feedback resistor divider from a secondary

winding on one converter's inductor to generate a third

regulated output voltage. Do not leave FCB floating.

RUN/SS1 (Pin 8): Controller 1 Run/Soft-Start. Pulling

RUN/SS1 to SGND will disable controller 1 and turn off

both of its external MOSFET switches. Pulling both

RUN/SS pins down will shut down the entire LTC1873,

dropping the quiescent supply current below 50

µ

A. A

capacitor from RUN/SS1 to SGND will control the turn-on

time and rate of rise of the controller 1 output voltage at

power-up. An internal 3.5

µ

A current source pull-up at

RUN/SS1 pin sets the turn-on time at approximately

50ms/

µ

F.

COMP1 (Pin 9): Controller 1 Loop Compensation. The

COMP1 pin is connected directly to the output of the first

controller's error amplifier and the input to the PWM

comparator. An RC network is used at the COMP1 pin to

compensate the feedback loop for optimum transient

response.

SGND (Pin 10): Signal Ground. All internal low power

circuitry returns to the SGND pin. Connect to a low

impedance ground, separated from the PGND node. All

feedback, compensation and soft-start connections should

return to SGND. SGND and PGND should connect only at

a single point, near the PGND pin and the negative plate of

the C

IN

bypass capacitor.

FB1 (Pin 11): Controller 1 Feedback Input. The loop

compensation network for controller 1 should be con-

nected to FB1. FB1 is connected internally to the VID

resistor network to set the output voltage at side 1.

SENSE (Pin 12): Output Sense. Connect to V

OUT1

.

VID0 to VID4 (Pins 13 to 17): VID Programming Inputs.

These are logic inputs that set the output voltage at side 1

to a preprogrammed value (see Table 1). VID4 is the MSB,

VID0 is the LSB. The codes selected by the VID

n inputs

correspond to the Intel Desktop VID specification. Each

PV

CC

(Pin 1): Driver Power Supply Input. PV

CC

provides

power to the two BG

n output drivers. PV

CC

must be

connected to a voltage high enough to fully turn on the

external MOSFETs QB1 and QB2. PV

CC

should generally

be connected directly to V

IN

. PV

CC

requires at least a 1

µ

F

bypass capacitor directly to PGND.

BOOST1 (Pin 2): Controller 1 Top Gate Driver Supply. The

BOOST1 pin supplies power to the floating TG1 driver.

BOOST1 should be bypassed to SW1 with a 1

µ

F capacitor.

An additional Schottky diode from V

IN

to BOOST1 pin will

create a complete floating charge-pumped supply at

BOOST1. No other external supplies are required.

BG1 (Pin 3): Controller 1 Bottom Gate Drive. The BG1 pin

drives the gate of the bottom N-channel synchronous

switch MOSFET, QB1. BG1 is designed to drive up to

10,000pF of gate capacitance directly. If RUN/SS1 goes

low, BG1 will go low, turning off QB1. If FAULT mode is

tripped, BG1 will go high and stay high, keeping QB1 on

until the power is cycled.

TG1 (Pin 4): Controller 1 Top Gate Drive. The TG1 pin

drives the gate of the top N-channel MOSFET, QT1. The

TG1 driver draws power from the BOOST1 pin and returns

to the SW1 pin, providing true floating drive to QT1. TG1

is designed to drive up to 10,000pF of gate capacitance

directly. In shutdown or fault modes, TG1 will go low.

SW1 (Pin 5): Controller 1 Switching Node. SW1 should be

connected to the switching node of converter 1. The TG1

driver ground returns to SW1, providing floating gate

drive to the top N-channel MOSFET switch, QT1. The

voltage at SW1 is compared to I

MAX1

by the current limit

comparator while the bottom MOSFET, QB1, is on.

I

MAX1

(Pin 6): Controller 1 Current Limit Set. The I

MAX1

pin sets the current limit comparator threshold for

controller 1. If the voltage drop across the bottom MOSFET,

QB1, exceeds the magnitude of the voltage at I

MAX1

,

controller 1 will go into current limit. The I

MAX1

pin has an

internal 10

µ

A current source pull-up, allowing the current

threshold to be set with a single external resistor to PGND.

This current setting resistor should be Kelvin connected to

the source of QB1. See the Current Limit Programming

section for more information on choosing R

IMAX

.

U

U

U

PI FU CTIO S