22323f

LTC2232/LTC2233

1

22323f

FEATURES

DESCRIPTIO

U

APPLICATIO S

U

TYPICAL APPLICATIO

U

Sample Rate: 105Msps/80Msps

61dB SNR up to 140MHz Input

75dB SFDR up to 200MHz Input

775MHz Full Power Bandwidth S/H

Single 3.3V Supply

Low Power Dissipation: 475mW/366mW

Selectable Input Ranges: ±0.5V or ±1V

No Missing Codes

Optional Clock Duty Cycle Stabilizer

Shutdown and Nap Modes

Data Ready Output Clock

Pin Compatible Family

135Msps: LTC2224 (12-Bit), LTC2234 (10-Bit)

105Msps: LTC2222 (12-Bit), LTC2232 (10-Bit)

80Msps: LTC2223 (12-Bit), LTC2233 (10-Bit)

48-Pin 7mm x 7mm QFN Package

10-Bit,105Msps/

80Msps ADCs

The LTC

®

2232 and LTC2233 are 105Msps/80Msps, sam-

pling 10-bit A/D converters designed for digitizing high

frequency, wide dynamic range signals. The LTC2232/

LTC2233 are perfect for demanding communications

applications with AC performance that includes 61dB SNR

and 75dB spurious free dynamic range for signals

up to 200MHz. Ultralow jitter of 0.15ps

RMS

allows

undersampling of IF frequencies with excellent noise

performance.

DC specs include ±0.15LSB INL (typ), ±0.1LSB DNL (typ)

and ±0.8LSB INL, ±0.6LSB DNL over temperature. The

transition noise is a low 0.12LSB

RMS

.

A separate output power supply allows the outputs to drive

0.5V to 3.3V logic.

The ENC

+

and ENC

inputs may be driven differentially or

single ended with a sine wave, PECL, LVDS, TTL, or CMOS

inputs. An optional clock duty cycle stabilizer allows high

performance at full speed for a wide range of clock duty

cycles.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Wireless and Wired Broadband Communication

Cable Head-End Systems

Power Amplifier Linearization

Communications Test Equipment

+

INPUT

S/H

CORRECTION

LOGIC

OUTPUT

DRIVERS

10-BIT

PIPELINED

ADC CORE

CLOCK/DUTY

CYCLE

CONTROL

FLEXIBLE

REFERENCE

D9

·

·

·

D0

ENCODE INPUT

REFH

REFL

ANALOG

INPUT

22323 TA01

0.5V

TO 3.3V

OV

DD

OGND

V

DD

3.3V

INPUT FREQUENCY (MHz)

0

90

85

80

75

70

65

60

55

50

100

200

300

400

22323 TA01b

500

600

SFDR (dBFS)

4th OR HIGHER

2nd OR 3rd

SFDR vs Input Frequency

LTC2232/LTC2233

2

22323f

CO VERTER CHARACTERISTICS

U

Supply Voltage (V

DD

) ................................................. 4V

Digital Output Ground Voltage (OGND) ....... 0.3V to 1V

Analog Input Voltage (Note 3) ..... 0.3V to (V

DD

+ 0.3V)

Digital Input Voltage .................... 0.3V to (V

DD

+ 0.3V)

Digital Output Voltage ............... 0.3V to (OV

DD

+ 0.3V)

Power Dissipation ............................................ 1500mW

Operating Temperature Range

LTC2232C, LTC2233C ............................. 0°C to 70°C

LTC2232I, LTC2233I ...........................40°C to 85°C

Storage Temperature Range ..................65°C to 125°C

ORDER PART

NUMBER

UK PART

MARKING*

T

JMAX

= 125°C,

JA

= 29°C/W

LTC2232UK

LTC2232UK

LTC2233UK

LTC2233UK

LTC2232CUK

LTC2232IUK

LTC2233CUK

LTC2233IUK

ABSOLUTE AXI U

RATI GS

W

W

W

U

PACKAGE/ORDER I FOR ATIO

U

U

W

OV

DD

= V

DD

(Notes 1, 2)

The

denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at T

A

= 25°C. (Note 4)

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Resolution (No Missing Codes)

10

Bits

Integral Linearity Error (Note 5)

Differential Analog Input

0.8

±0.15

0.8

LSB

Differential Linearity Error

Differential Analog Input

0.6

±0.1

0.6

LSB

Integral Linearity Error (Note 5)

Single-Ended Analog Input

±0.5

LSB

Differential Linearity Error

Single-Ended Analog Input

±0.1

LSB

Offset Error (Note 6)

37

±5

37

mV

Gain Error

External Reference

2.5

±0.5

2.5

%FS

Offset Drift

±10

µV/C

Full-Scale Drift

Internal Reference

±30

ppm/C

External Reference

±15

ppm/C

Transition Noise

SENSE = 1V

0.12

LSB

RMS

*The temperature grade is identified by a label on the shipping container.

Consult LTC Marketing for parts specified with wider operating temperature ranges.

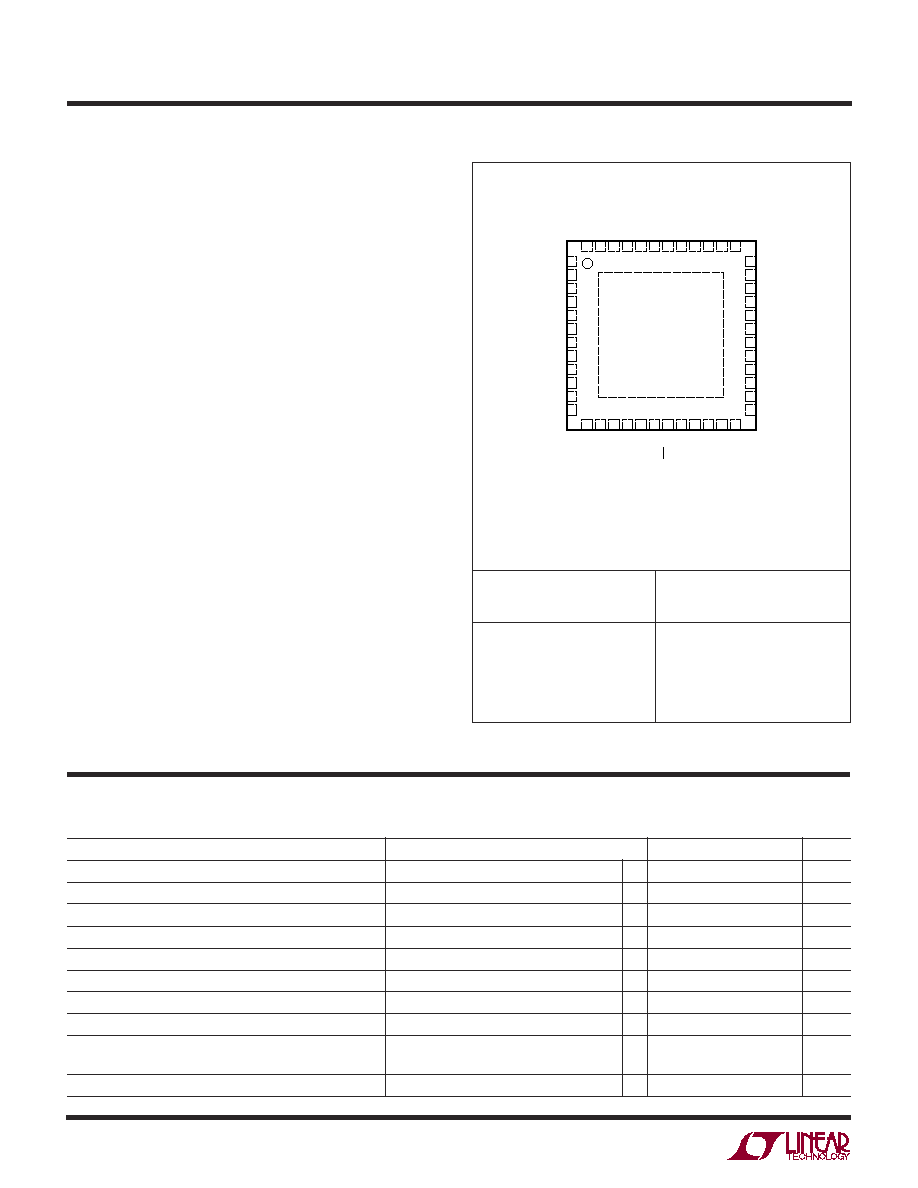

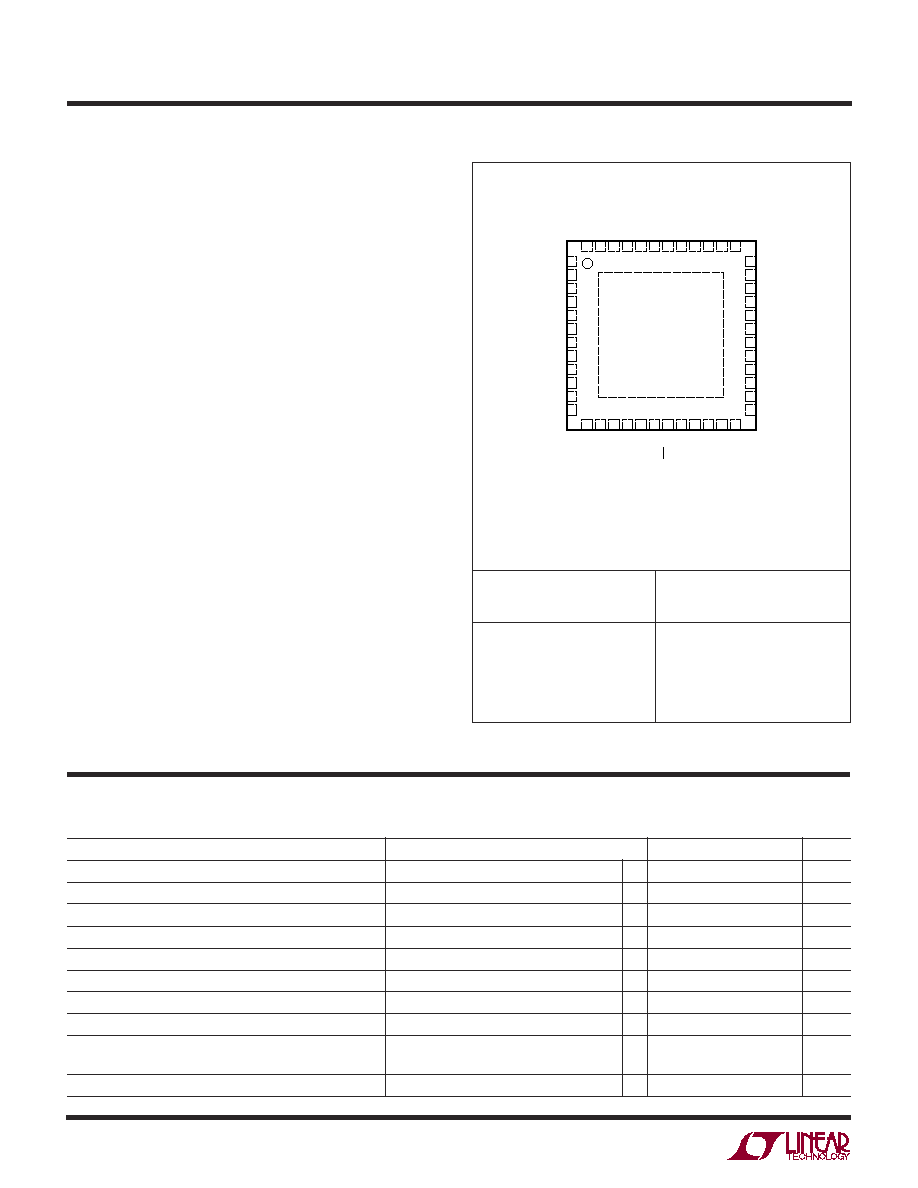

TOP VIEW

UK PACKAGE

48-LEAD (7mm × 7mm) PLASTIC QFN

EXPOSED PAD IS GND (PIN 49),

MUST BE SOLDERED TO PCB

A

IN

+

1

A

IN

2

REFHA 3

REFHA 4

REFLB

5

REFLB

6

REFHB 7

REFHB 8

REFLA 9

REFLA 10

V

DD

11

V

DD

12

36 D7

35 D6

34 D5

33 OV

DD

32 OGND

31 D4

30 D3

29 D2

28 OV

DD

27 OGND

26 D1

25 D0

49

48 GND

47 V

DD

46 V

DD

45 GND

44 V

CM

43 SENSE

42 MODE

41 OF

40 D9

39 D8

38 OGND

37 OV

DD

GND 13

V

DD

14

GND 15

ENC

+

16

ENC

17

SHDN

18

OE

19

CLOCKOUT

20

NC 21

OGND 22

OV

DD

23

NC 24

LTC2232/LTC2233

3

22323f

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

IN

Analog Input Range (A

IN

+

A

IN

)

3.1V < V

DD

< 3.5V

±0.5 to ±1

V

V

IN, CM

Analog Input Common Mode

Differential Input

1

1.6

1.9

V

I

IN

Analog Input Leakage Current

0 < A

IN

+

, A

IN

< V

DD

1

1

µA

I

SENSE

SENSE Input Leakage

0V < SENSE < 1V

1

1

µA

I

MODE

MODE Pin Pull-Down Current to GND

10

µA

Full Power Bandwidth

Figure 8 Test Circuit

775

MHz

t

AP

Sample and Hold Acquisition Delay Time

0

ns

t

JITTER

Sample and Hold Acquisition Delay Time Jitter

0.15

ps

RMS

CMRR

Analog Input Common Mode Rejection Ratio

80

dB

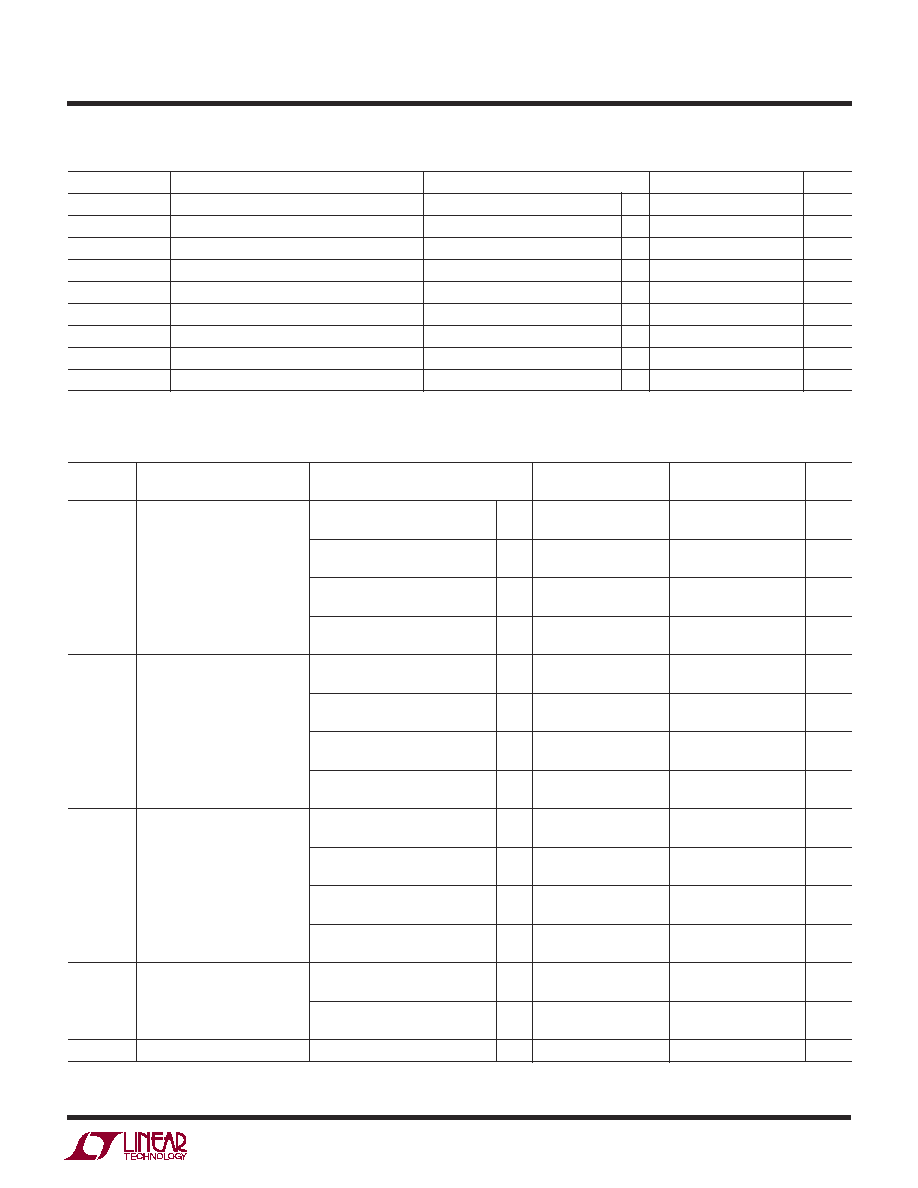

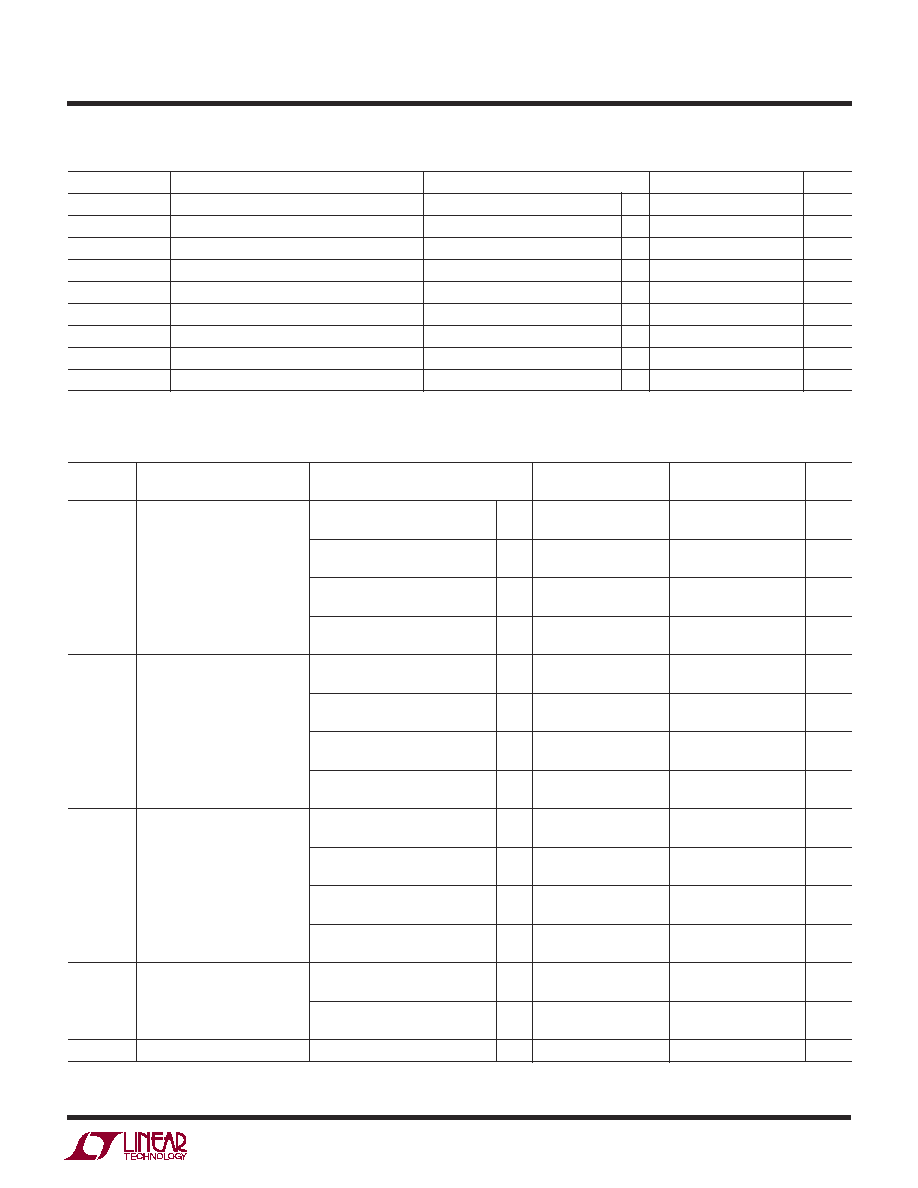

LTC2232

LTC2233

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

SNR

Signal-to-Noise Ratio

30MHz Input (1V Range)

59.8

59.9

dB

30MHz Input (2V Range)

60.4

61.3

60.4

61.3

dB

70MHz Input (1V Range)

59.8

59.8

dB

70MHz Input (2V Range)

61.2

61.3

dB

140MHz Input (1V Range)

59.8

59.8

dB

140MHz Input (2V Range)

61.2

61.2

dB

250MHz Input (1V Range)

59.6

59.7

dB

250MHz Input (2V Range)

61.1

61.2

dB

SFDR

Spurious Free Dynamic Range

30MHz Input (1V Range)

80

80

dB

30MHz Input (2V Range)

69

78

69

78

dB

70MHz Input (1V Range)

80

80

dB

70MHz Input (2V Range)

78

78

dB

140MHz Input (1V Range)

78

78

dB

140MHz Input (2V Range)

78

78

dB

250MHz Input (1V Range)

71

73

dB

250MHz Input (2V Range)

70

72

dB

SFDR

Spurious Free Dynamic Range

30MHz Input (1V Range)

86

86

dB

4th Harmonic or Higher

30MHz Input (2V Range)

86

86

dB

70MHz Input (1V Range)

86

86

dB

70MHz Input (2V Range)

86

86

dB

140MHz Input (1V Range)

86

86

dB

140MHz Input (2V Range)

86

86

dB

250MHz Input (1V Range)

86

86

dB

250MHz Input (2V Range)

86

86

dB

S/(N+D)

Signal-to-Noise Plus

30MHz Input (1V Range)

59.8

59.9

dB

Distortion Ratio

30MHz Input (2V Range)

60.2

61.3

60.2

61.3

dB

70MHz Input (1V Range)

59.8

59.8

dB

70MHz Input (2V Range)

61.2

61.2

dB

IMD

Intermodulation Distortion

f

IN1

= 138MHz, f

IN2

= 140MHz

81

81

dBc

A ALOG I PUT

U

U

DY

A

IC ACCURACY

U

W

The

denotes the specifications which apply over the full operating temperature range, otherwise

specifications are at T

A

= 25°C. (Note 4)

The

denotes the specifications which apply over the full operating temperature range,

otherwise specifications are at T

A

= 25°C. A

IN

= 1dBFS. (Note 4)

LTC2232/LTC2233

4

22323f

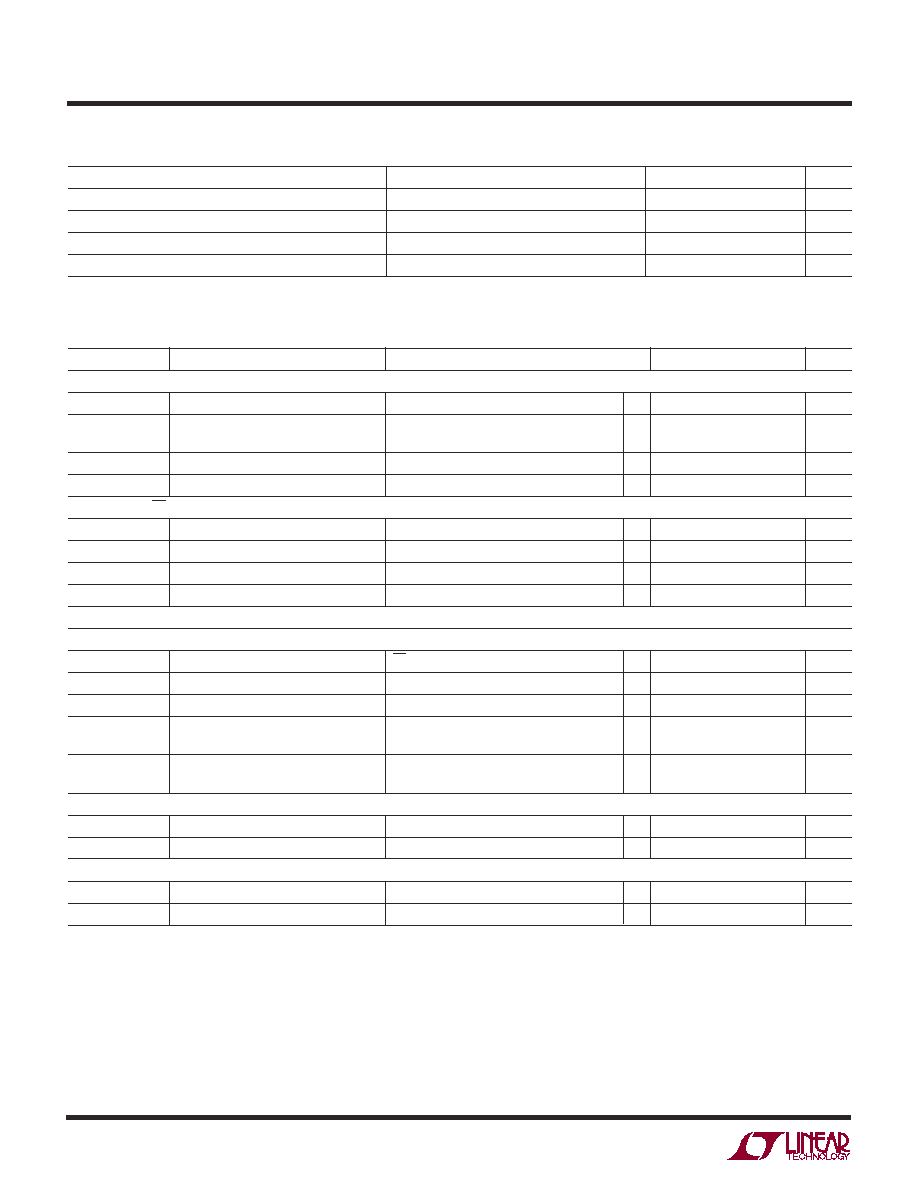

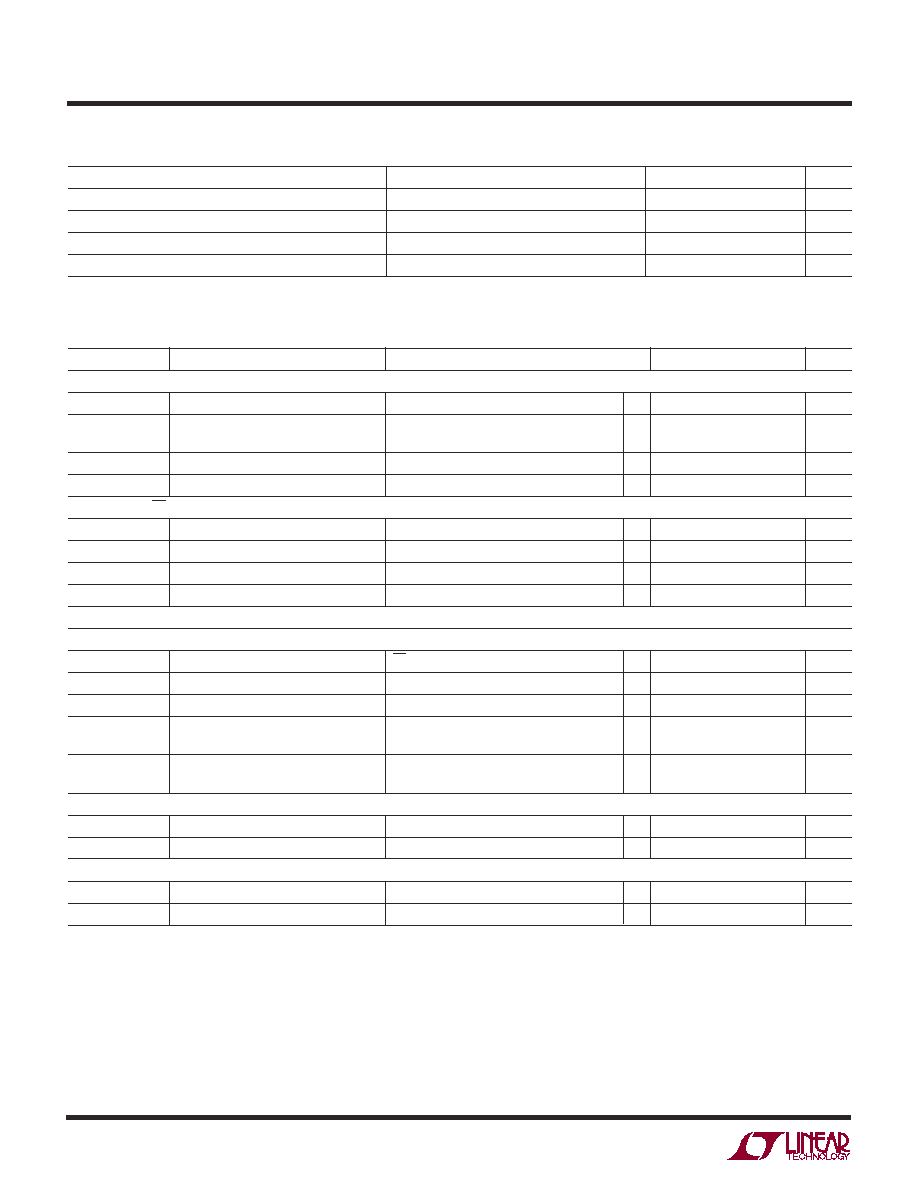

DIGITAL I PUTS A D DIGITAL OUTPUTS

U

U

The

denotes the specifications which apply over the

full operating temperature range, otherwise specifications are at T

A

= 25°C. (Note 4)

I TER AL REFERE CE CHARACTERISTICS

U

U

U

(Note 4)

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

V

CM

Output Voltage

I

OUT

= 0

1.570

1.600

1.630

V

V

CM

Output Tempco

±25

ppm/°C

V

CM

Line Regulation

3.1V < V

DD

< 3.5V

3

mV/V

V

CM

Output Resistance

1mA < I

OUT

< 1mA

4

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

ENCODE INPUTS (ENC

+

, ENC

)

V

ID

Differential Input Voltage

0.2

V

V

ICM

Common Mode Input Voltage

Internally Set

1.6

V

Externally Set (Note 7)

1.1

1.6

2.5

V

R

IN

Input Resistance

6

k

C

IN

Input Capacitance

(Note 7)

3

pF

LOGIC INPUTS (OE, SHDN)

V

IH

High Level Input Voltage

V

DD

= 3.3V

2

V

V

IL

Low Level Input Voltage

V

DD

= 3.3V

0.8

V

I

IN

Input Current

V

IN

= 0V to V

DD

10

10

µA

C

IN

Input Capacitance

(Note 7)

3

pF

LOGIC OUTPUTS

OV

DD

= 3.3V

C

OZ

Hi-Z Output Capacitance

OE = High (Note 7)

3

pF

I

SOURCE

Output Source Current

V

OUT

= 0V

50

mA

I

SINK

Output Sink Current

V

OUT

= 3.3V

50

mA

V

OH

High Level Output Voltage

I

O

= 10µA

3.295

V

I

O

= 200µA

3.1

3.29

V

V

OL

Low Level Output Voltage

I

O

= 10µA

0.005

V

I

O

= 1.6mA

0.09

0.4

V

OV

DD

= 2.5V

V

OH

High Level Output Voltage

I

O

= 200µA

2.49

V

V

OL

Low Level Output Voltage

I

O

= 1.6mA

0.09

V

OV

DD

= 1.8V

V

OH

High Level Output Voltage

I

O

= 200µA

1.79

V

V

OL

Low Level Output Voltage

I

O

= 1.6mA

0.09

V

LTC2232/LTC2233

5

22323f

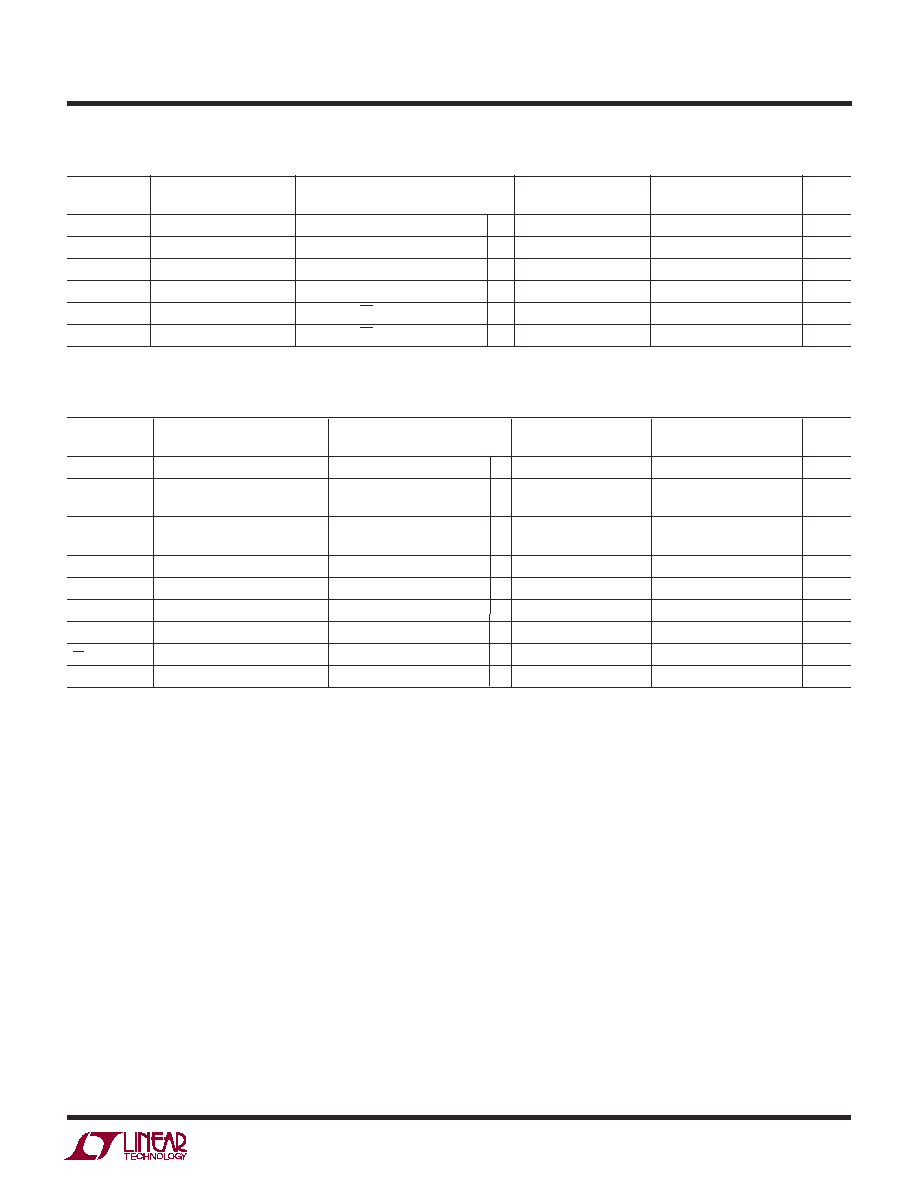

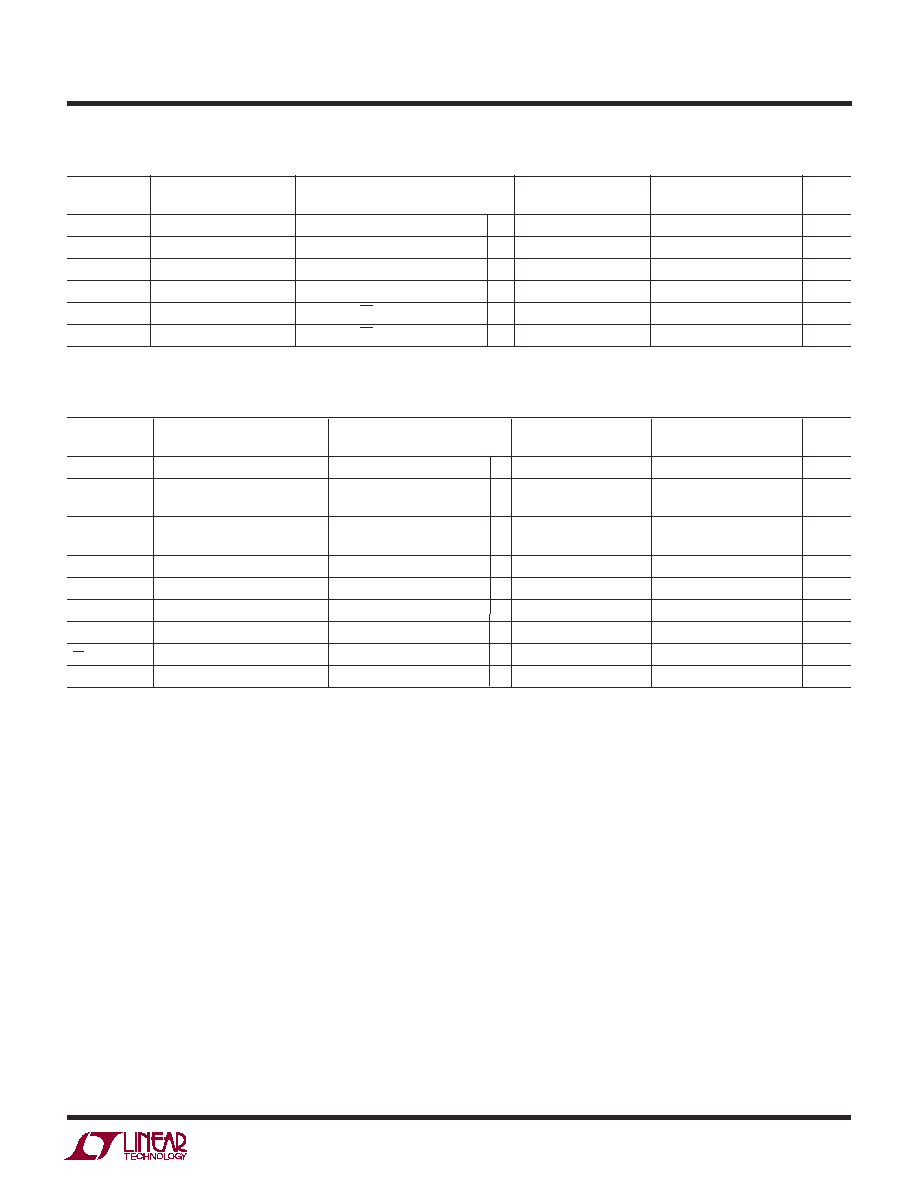

LTC2232

LTC2233

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

V

DD

Analog Supply Voltage

3.1

3.3

3.5

3.1

3.3

3.5

V

OV

DD

Output Supply Voltage

0.5

3.3

3.6

0.5

3.3

3.6

V

I

VDD

Analog Supply Current

144

162

111

123

mA

P

DISS

Power Dissipation

475

535

366

406

mW

P

SHDN

Shutdown Power

SHDN = H, OE = H, No CLK

2

2

mW

P

NAP

Nap Mode Power

SHDN = H, OE = L, No CLK

35

35

mW

LTC2232

LTC2233

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

MIN

TYP

MAX

UNITS

f

S

Sampling Frequency

1

105

1

80

MHz

t

L

ENC Low Time (Note 8)

Duty Cycle Stabilizer Off

4.5

4.76

500

5.9

6.25

500

ns

Duty Cycle Stabilizer On

3

4.76

500

3

6.25

500

ns

t

H

ENC High Time (Note 8)

Duty Cycle Stabilizer Off

4.5

4.76

500

5.9

6.25

500

ns

Duty Cycle Stabilizer On

3

4.76

500

3

6.25

500

ns

t

AP

Sample-and-Hold Aperture Delay

0

0

ns

t

D

ENC to DATA Delay

(Note 7)

1.3

2.1

4

1.3

2.1

4

ns

t

C

ENC to CLOCKOUT Delay

(Note 7)

1.3

2.1

4

1.3

2.1

4

ns

DATA to CLOCKOUT Skew

(t

C

- t

D

) (Note 7)

0.6

0

0.6

0.6

0

0.6

ns

t

OE

Output Enable Delay

(Note 7)

5

10

5

10

ns

Pipeline Latency

5

5

Cycles

POWER REQUIRE E TS

W

U

The

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at T

A

= 25°C. (Note 9)

TI I G CHARACTERISTICS

U

W

The

denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at T

A

= 25°C. (Note 4)

Note 1: Absolute Maximum Ratings are those values beyond which the life of

a device may be impaired.

Note 2: All voltage values are with respect to ground with GND and OGND

wired together (unless otherwise noted).

Note 3: When these pin voltages are taken below GND or above V

DD

, they will

be clamped by internal diodes. This product can handle input currents of

greater than 100mA below GND or above V

DD

without latchup.

Note 4: V

DD

= 3.3V, f

SAMPLE

= 105MHz (LTC2232) or 80MHz (LTC2233),

differential ENC

+

/ENC

= 2V

P-P

sine wave, input range = 2V

P-P

with differential

drive, unless otherwise noted.

Note 5: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual endpoints of the transfer curve. The

deviation is measured from the center of the quantization band.

Note 6: Offset error is the offset voltage measured from 0.5 LSB when the

output code flickers between 00 0000 0000 and 11 1111 1111 in 2's

complement output mode.

Note 7: Guaranteed by design, not subject to test.

Note 8: Recommended operating conditions.

Note 9: V

DD

= 3.3V, f

SAMPLE

= 105MHz (LTC2232) or 80MHz (LTC2233),

differential ENC

+

/ENC

= 2V

P-P

sine wave, input range = 1V

P-P

with differential

drive.