| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LF3324 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DEVICES INCORPORATED

LF3324

24Mbit Frame Buffer / FIFO

Preliminary Datasheet

LOGIC Devices Incorporated

September 14, 2005 LDS.3324 E

Video Imaging Product

LF3324s may be Cascaded for depth and

width, supporting HDTV, Multiframe SDTV,

and other high resolution formats

∑ Seamless address space is maintained

with up to 8 cascaded devices

Built-in ITU-R BT.656 TRS detection and

Synchronization

Set & Clear Read/Write Pointer Control Pins

Choice of Control Interfaces:

∑ Two-wire Serial Microprocessor Interface

∑ Parallel Microprocessor Interface

Input Enable Control (Write Mask) for freeze-

frame applications

Output Enable Control (Data Skipping)

JTAG Boundary Scan - IEEE 1149.1

172 ball LBGA package

1.8V Internal Core Power Supply

3.3V I/O Supply

DTV/HDTV Video Stream Buffer

Frame Synchronization

CCTV Security Camera Systems

Time Base Correction (TBC)

Freeze-Frame Buffer

Regional Read/Write for Picture-in-Picture (PIP)

Field-Based or Frame-Based Comb Filtering

Video Capture & Editing Systems

Deep Data Buffering

Video Special Effects (Rotation, Zoom)

Test Pattern Generation

Motion Detection or Frame-to-Frame Correlation

24,883,200-bit Frame Memory

74.25 Mhz Data Rate

May be Organized Into the Following Configurations:

∑ 3,110,400 x 8-bit

∑ 2,488,320 x 10-bit

∑ 2,073,600 x 12-bit

Operating Modes:

∑ Random Access with Burst Control

∑ FIFO

∑ Synchronous Shift Register

Near-Full/Empty Flags With Programmable

Thresholds

Flexible Pointer Manipulation

∑ Write and Read Pointers may be independently

jumped to arbitrary address locations

∑ Write or Read Pointers can be manipulated in real-

time based on external 24bit address

Features

Applications

NOTE: This Preliminary Datasheet references LF3324BGC Engineering Samples

with an E marking under the part designation.

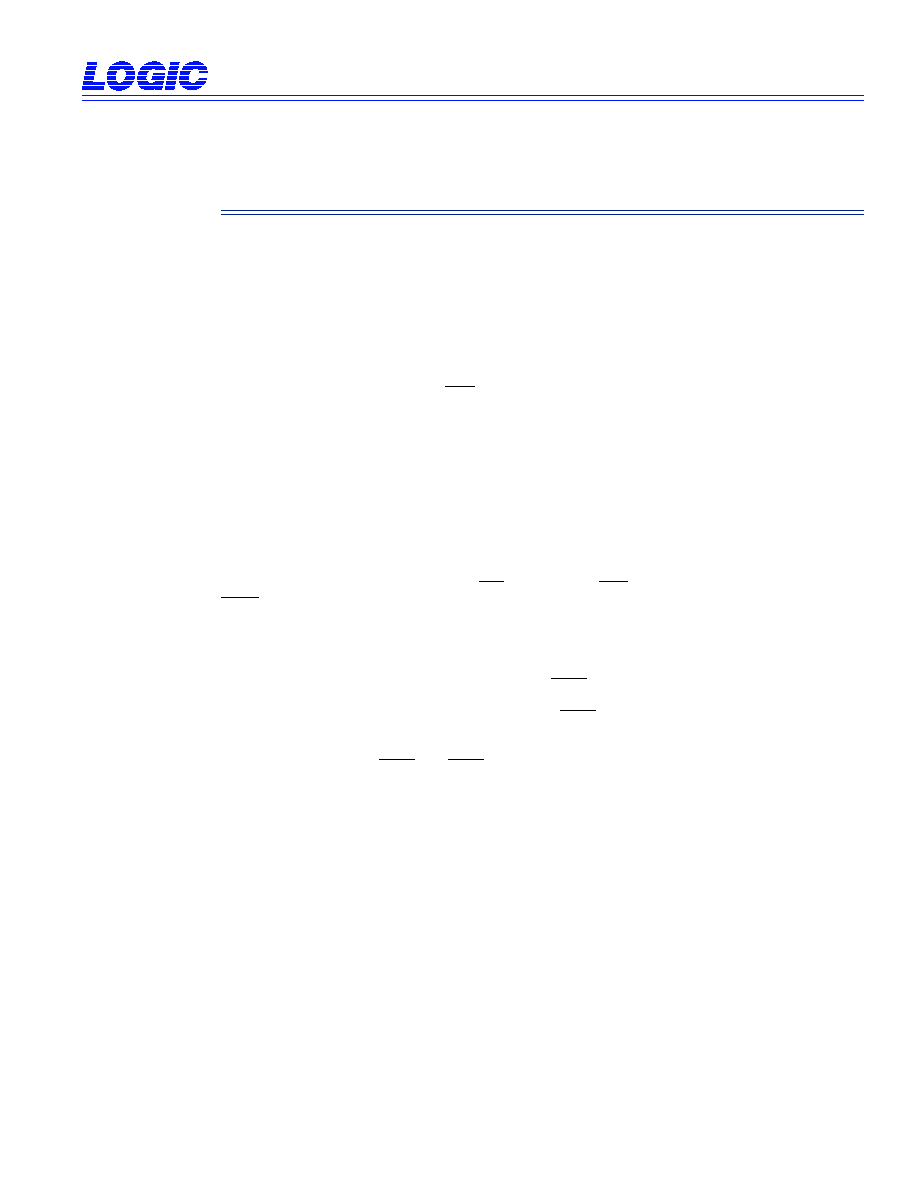

MEMORY

24Mbit

JTAG

PARALLEL

INTERFACE

WRITE

POINTER

RANDOM ACCESS

ADDRESSING

FLAGS

INPUT

DATA

PORT

OUTPUT

DATA

PORTS

WEN

REN

WSET

RSET

IEN

MARK

TDI

TDO

TRST

TMS

TCLK

(x8, x10, x12)

TWO-WIRE SERIAL

INTERFACE

INPUT

CONTROL

OUTPUT

CONTROL

WCLK

WCLR

RCLK

RCLR

PE

PF

COLLIDE

SDA SCL

(x8, x10, x12)

PCE

1

PWE

PRE

PADDR

PDATA

D[11:0]

Q[11:0]

8

6

LOAD

PROGRAM

.

.

ADDR[23:0]

24

PCE

0

READ

POINTER

WADDRSEL

RADDRSEL

OE

DEVICES INCORPORATED

LF3324

24Mbit Frame Buffer / FIFO

Preliminary Datasheet

LOGIC Devices Incorporated

2

September 14, 2005 LDS.3324 E

Video Imaging Product

The LF3324 is a 24 Mbit memory device that handles 8, 10, or 12bit data. The input data port may be

clocked asynchronously to the output ports. Since reads are non-destructive, a given data value, once

written into the memory core, may be read as many times as desired. A user requiring more storage can

cascade up to eight LF3324s into a larger array.

A great deal of memory addressing flexibility is offered with the LF3324. Both Burst Mode and Random

Access addressing is possible. In addition to simple clearing of the Write and Read pointers, either pointer

may be set/jumped to any location within the entire address space. Real-time random-access Writing or

Reading is also supported through an external address port.

The device is controlled by sixteen instruction words of eight bits each, which may be programmed or

verified via standard I

2

C 2-wire serial or parallel microprocessor interfaces.

The OPMODE configuration register selects one of the chip's operating modes, each of which has versatile

submode options:

- FIFO With Asynchronous I/O

- Synchronous Shift Register (Single Clock; User-set Latency)

- Random Access With Burst Address

LF3324 Overview

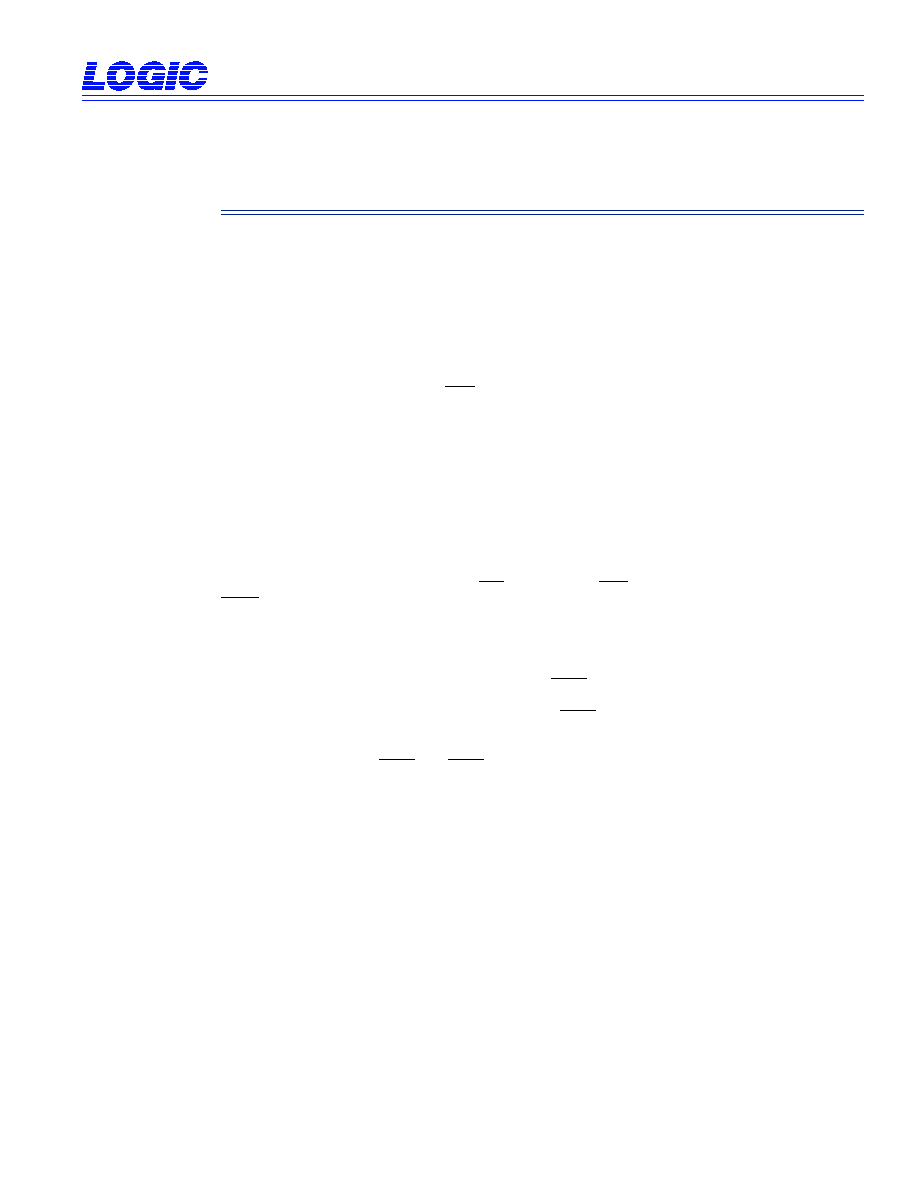

Figure 1. LF3324 Functional Block Diagram

MEMORY CELL ARRAY

D[11:0]

12

Q[11:0]

12

PE

PF

FLAG

GENERATOR

OE

2,073,600 x 12-bit

2,488,320 x 10-bit

3,110,400 x 8-bit

READ

CONTROL

READ

CONTROL A

RCLK

REN

RSET

RCLR

COLLIDE

MARK

WRITE

CONTROL A

WSET

WCLR

WEN

WCLK

WIEN

MASTER

CONTROL

I C

2

SCL

SDA

PROGRAM

CHIP_ADDR

6-0

7

PDATA

8

PADDR

6

PCE

1

PCE

0

PRE

PWE

WRITE ADDRESS

READ ADDRESS

MEMORY CELL ARRAY

D[11:0]

12

Q[11:0]

12

OE

2,073,600 x 12-bit

2,488,320 x 10-bit

3,110,400 x 8-bit

ADDRESS

CONTROL

READ

CONTROL

RCLK

REN

RSET

RCLR

24

WRITE

CONTROL A

WSET

WCLR

WEN

WCLK

MARK

WIEN

MASTER

CONTROL

I C

2

SCL

SDA

PROGRAM

CHIP_ADDR

6-0

7

PDATA

8

PADDR

6

PCE

1

PCE

0

PRE

PWE

24

ADDR[23:0]

WRITE ADDRESS

READ ADDRESS

RADDRSEL

WADDRSEL

DEVICES INCORPORATED

LF3324

24Mbit Frame Buffer / FIFO

Preliminary Datasheet

LOGIC Devices Incorporated

3

September 14, 2005 LDS.3324 E

Video Imaging Product

Figure 2. Single Channel FIFO Mode Functional Block Diagram

Figure 3. Random Access Mode Functional Block Diagram

DEVICES INCORPORATED

LF3324

24Mbit Frame Buffer / FIFO

Preliminary Datasheet

LOGIC Devices Incorporated

4

September 14, 2005 LDS.3324 E

Video Imaging Product

Asynchronous FIFO mode (OPMODE = 3)

In OPMODE 3, the LF3324 is configured as asynchronous First-In-First-Out 24Mbit memory, with indepen-

dent read and write clocks to allow for asynchronous operation. This mode is ideal for buffering or burst

data applications. Arbitrary write/read pointer jumping is supported in all FIFO modes. In this mode the

device can re-time a data stream according to a read sync signal (RSET or RCLR) and either ITU-R656

Timing Reference Signals (TRS) embedded within the incoming (video) data or the falling edge of a write

sync signal applied to WCLR, WSET, or MARK.

The input (write) and output (read) clocks need not be synchronous with one another, although the memory

core may fill or empty if they differ in average frequency. After it "fills," the LF3324 continues writing and

the oldest data gets written over. If the memory core "empties" (and neither the read nor write pointer

have been set or cleared during run-time) the read pointer stops incrementing, and the device re-reads the

last written sample until more data is written. In either case, when the read and write addresses are the

same, the COLLIDE flag will go high, to alert the host. The almost-full (PF) and almost-empty (PE) flags

provide advance warning of these conditions whenever user-selected "fullness" or "emptiness" thresholds,

expressed in approximate eightieths of the memory core size, are exceeded. For example, if the 1/80 and

79/80 thresholds are enabled, flag PE will go HIGH whenever the read pointer lags behind the write pointer

by less than 1/80 of the memory space, and flag PF will go HIGH whenever the read pointer leads the

write pointer by this amount. (Calculations are performed modulo the total address space.) The data input

and output are sequential and the timing between write and read sync signals dynamically determines the

effective delay (depth) of the FIFO.

The "stop reading when empty" FIFO-mode behavior can be avoided by making sure LOAD is HIGH and

issuing any write or read pointer SET or CLEAR command at any time. This effectively gets the device out

of this "read-pointer-halting" mode from that point onwards, but invalidates the flags. Random Access Mode

allows free manipulation of the r/w pointers, and never halts the read pointer without being commanded

to do so using REN. Since Random Access mode naturally increments the r/w pointers sequentially, like

in FIFO mode, it may be a better mode to use if complex pointer manipulation of a single-channel of

memory is desired.

Synchronous shift register mode (OPMODE = 0)

In OPMODE 0, the LF3324 becomes a shift register with programmable total latency up to 2

24

-8 clock

cycles. Writes and reads occur simultaneously, hence synchronous operation.

In OPMODE 0, the user provides a single clock for both the input and output clocks and specifies a desired

input-to-output data path latency, configuration register "WADDR" via the control interface. WCLK and RCLK

must be tied together, as should WEN and REN. When activated, WADDR will begin to countdown, and

once expired, will allow the inputs to begin to appear on the outputs. In OPMODE 0, WADDR countdown

can be activated in two ways. The first occurs when the first enable is brought LOW after the LOAD

signal has been set HIGH after MPU programming. The second is by bringing LOAD HIGH once MPU

programming complete, after the enables have been brought LOW.

Random Access Mode (OPMODE = 1)

Random Access mode is a FIFO mode, with the capability of either full-time write or read pointer Random

Accessability. This mode also supports write and read pointer jumps to arbitrary locations throughout

the address space. Unlike Asynchronous FIFO mode, Random Access mode does not disable memory

reads when the read pointer catches up to the write pointer. Write pointer manipulation can be done

Operating Modes

DEVICES INCORPORATED

LF3324

24Mbit Frame Buffer / FIFO

Preliminary Datasheet

LOGIC Devices Incorporated

5

September 14, 2005 LDS.3324 E

Video Imaging Product

through setting (jumping) the write pointer to the 24bit address via the ADDR[23:0] port or to the WADDR

configuration register. Read pointer manipulation can be done through setting (jumping) the write pointer

to the 24bit address via the ADDR[23:0] port or to the RADDR configuration register. Periodic write and

read pointer jumping can be accomplished by supplying an address through either the ADDR[23:0] external

address or the WADDR/RADDR instruction registers. Continuous random access can only be accomplished

through the use of the ADDR[23:0] ports. When the write/read pointers are not being set to an address,

they increment sequentially in burst mode.

In Random Access Mode, when WADRSEL = 1 and RADRSEL = 0 the write pointer is set to the address

supplied by the ADDR[23:0] ports when WSET is brought LOW. In other words, on each active write clock

cycle (rising edge of WCLK for which WEN was LOW two rising edges of WCLK previously), the user

directs the write pointer to any desired memory location, using what are otherwise the second channel

data input and output ports. In this application, ADDR[23:12] denotes the vertical (row) component,

and ADDR[11:0], the horizontal (column) component, of a Cartesian set. Setting the configuration

register ROW_LENGTH to the frame's line (row) length internally defines the Cartesian coordinates. Also,

ADDR[23:0] can also represent a single 24-bit linear address. The user governs the mapping of (ADDR)

to the internal memory space by setting the parameter ROW_LENGTH such that the internal ADDRESS

= ADDR[23-12] * ROW_LENGTH + ADDR[11-0]. A ROW_LENGTH setting of 0 is interpreted as 4096,

such that ADDRESS = a 24-bit concatenation of {ADDR} for this particular value. For a standard D1 video

application with 1716 samples per line, the user would set ROW_LENGTH to 1716 decimal = 6B4 hex.

Offset circuitry within the LF3324 permits the user to cascade several chips in parallel and to use them

collectively as a single large memory with a seamless address space. Data are read out sequentially by

rising edges of RCLK, under the control of REN (read enable), RSET (read pointer force to constant), and

RCLR (read pointer clear to 0). Holding WSET LOW keeps the device continuously in random access

write mode. Releasing WSET to its HIGH state causes the chip to continue to write sequentially from

the last-loaded address.

In Random Access Mode, when RADRSEL = 1, WADRSEL = 0, MARK_SEL = 1, the read pointer is set

to the address supplied by the ADDR[23:0] ports when RSET is brought LOW. As mentioned above,

ADDR[23:12] represents the upper bits or the vertical (row) address, whereas ADDR[11:0] represents the

lower bits or the horizontal (column) address. Releasing RSET HIGH causes the read address pointer to

increment from its last assigned location to the next sequential address.

It is important to note that WSET and RSET can be programmed to be level or negative-edge triggered.

An edge sensitive "SET" command is useful for using SYNC signals to reset FIFO pointers. Level sensitive

"SET" commands allow full-time Random Access capability.

Operating Modes