| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LMU8UPC35 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DEVICES INCORPORATED

LMU08/8U

8 x 8-bit Parallel Multiplier

Multipliers

08/16/2000≠LDS.08/8U-R

1

u

u

u

u

u

20 ns Worst-Case Multiply Time

u

u

u

u

u Low Power CMOS Technology

u

u

u

u

u LMU08 Replaces TRW TMC208K

u

u

u

u

u LMU8U Replaces TRW TMC28KU

u

u

u

u

u Two's Complement (LMU08), or

Unsigned Operands (LMU8U)

u

u

u

u

u

Three-State Outputs

u

u

u

u

u Package Styles Available:

∑ 40-pin PDIP

∑ 44-pin PLCC, J-Lead

FEATURES

DESCRIPTION

LMU08/8U

8 x 8-bit Parallel Multiplier

DEVICES INCORPORATED

The LMU08 and LMU8U are high-

speed, low power 8-bit parallel

multipliers. They are pin-for-pin

equivalents with TRW

TMC208K

and

TMC28KU

type multipliers. Full

military ambient temperature range

operation is attained by the use of

advanced CMOS technology.

Both the LMU08 and the LMU8U

produce the 16-bit product of two

8-bit numbers. The LMU08 accepts

operands in two's complement format,

and produces a two's complement

result. The product is provided in two

halves with the sign bit replicated as

the most significant bit of both halves.

This facilitates use of the LMU08

product as a double precision operand

in 8-bit systems. The LMU8U oper-

ates on unsigned data, producing an

unsigned magnitude result.

Both the LMU08 and the LMU8U

feature independently controlled

registers for both inputs and the

product, which along with three-state

outputs allows easy interfacing with

microprocessor busses. Provision is

made in the LMU08 and LMU8U for

proper rounding of the product to

8-bit precision. The round input is

loaded at the rising edge of the logical

OR of CLK A and CLK B for the

LMU08. The LMU8U latches RND on

the rising edge of CLK A only. In

either case, a `1' is added in the most

significant position of the lower

product byte when RND is asserted.

Subsequent truncation of the least

significant product byte results in a

correctly rounded 8-bit result.

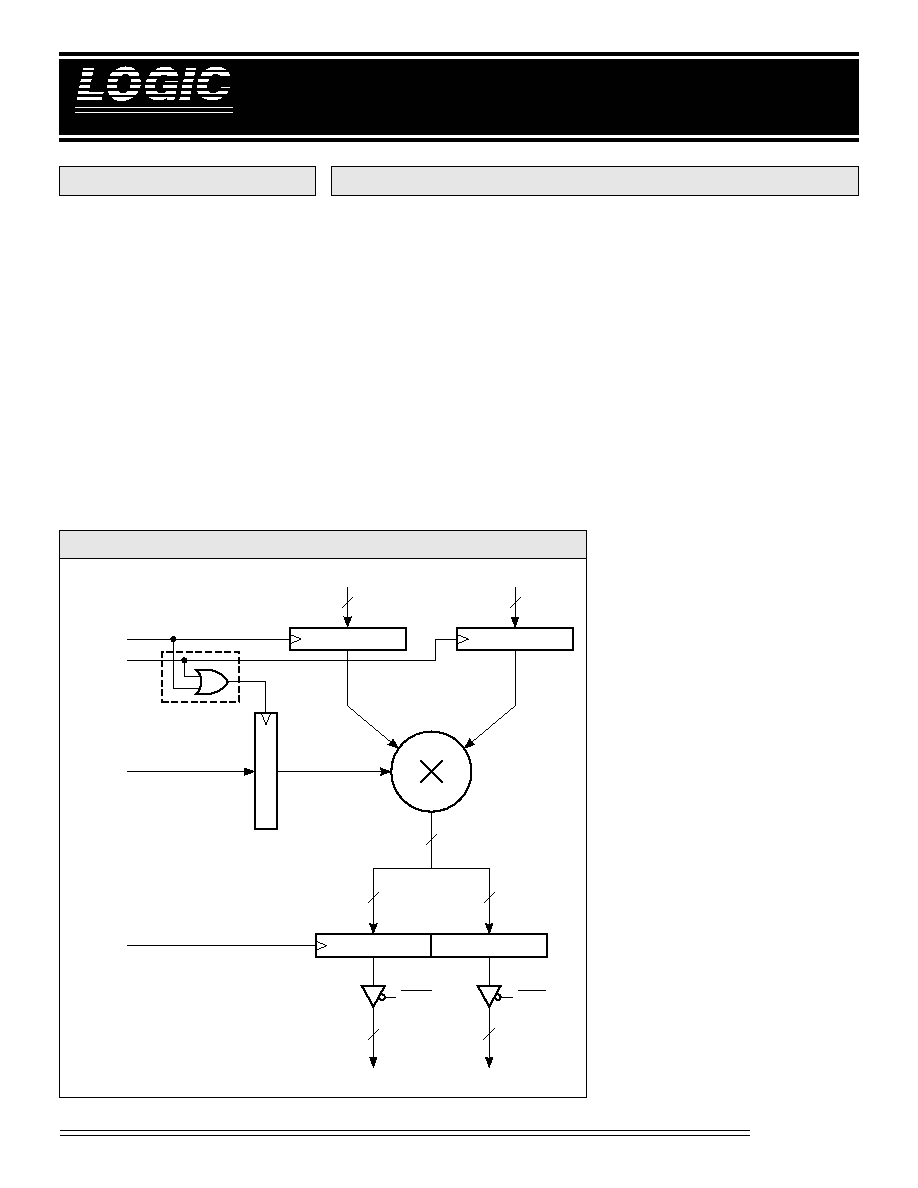

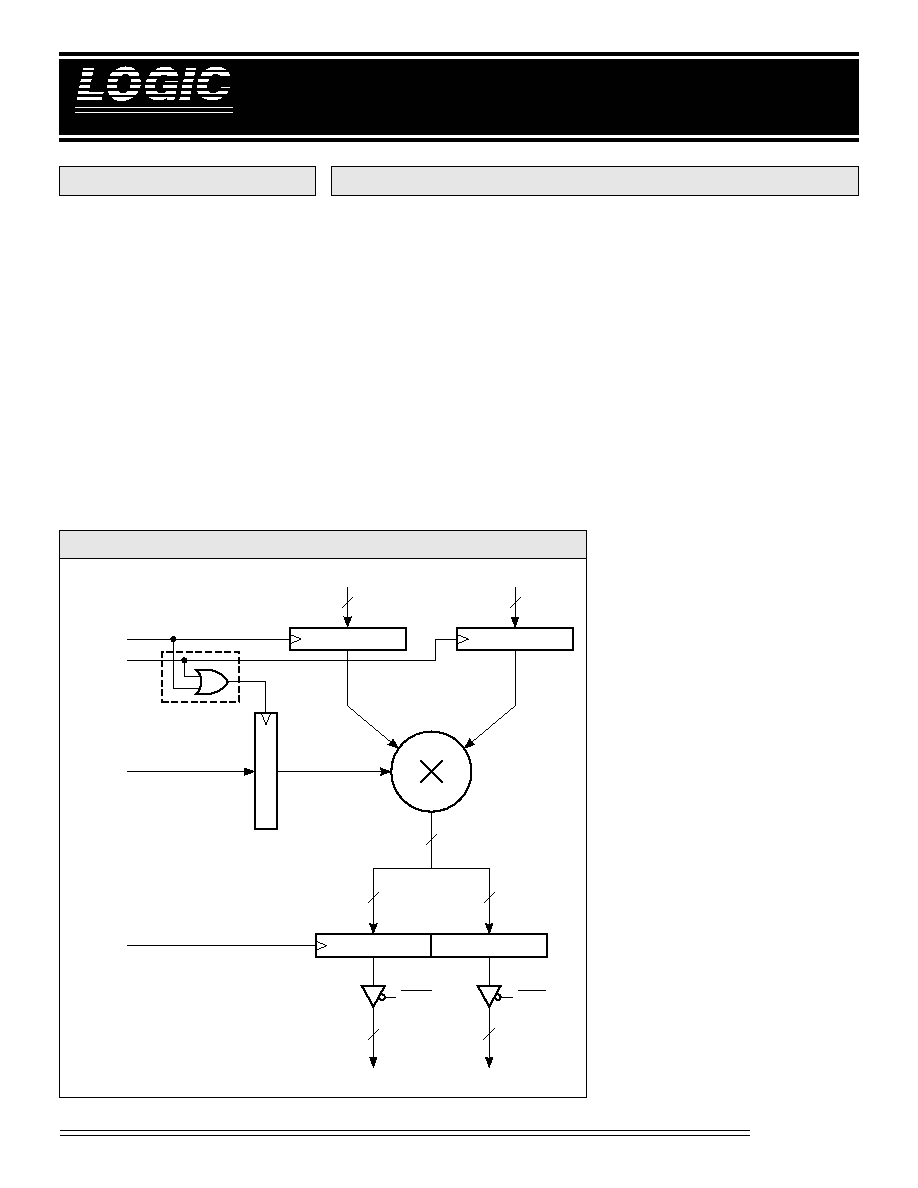

LMU08/8U B

LOCK

D

IAGRAM

REGISTER

CLK A

CLK B

RND

CLK R

LMU08 Only

8

8

16

8

8

OEM

R

7-0

A

7-0

R

15-8

A REGISTER

B REGISTER

B

7-0

RESULT

REGISTER

OEL

8

8

DEVICES INCORPORATED

LMU08/8U

8 x 8-bit Parallel Multiplier

Multipliers

08/16/2000≠LDS.08/8U-R

2

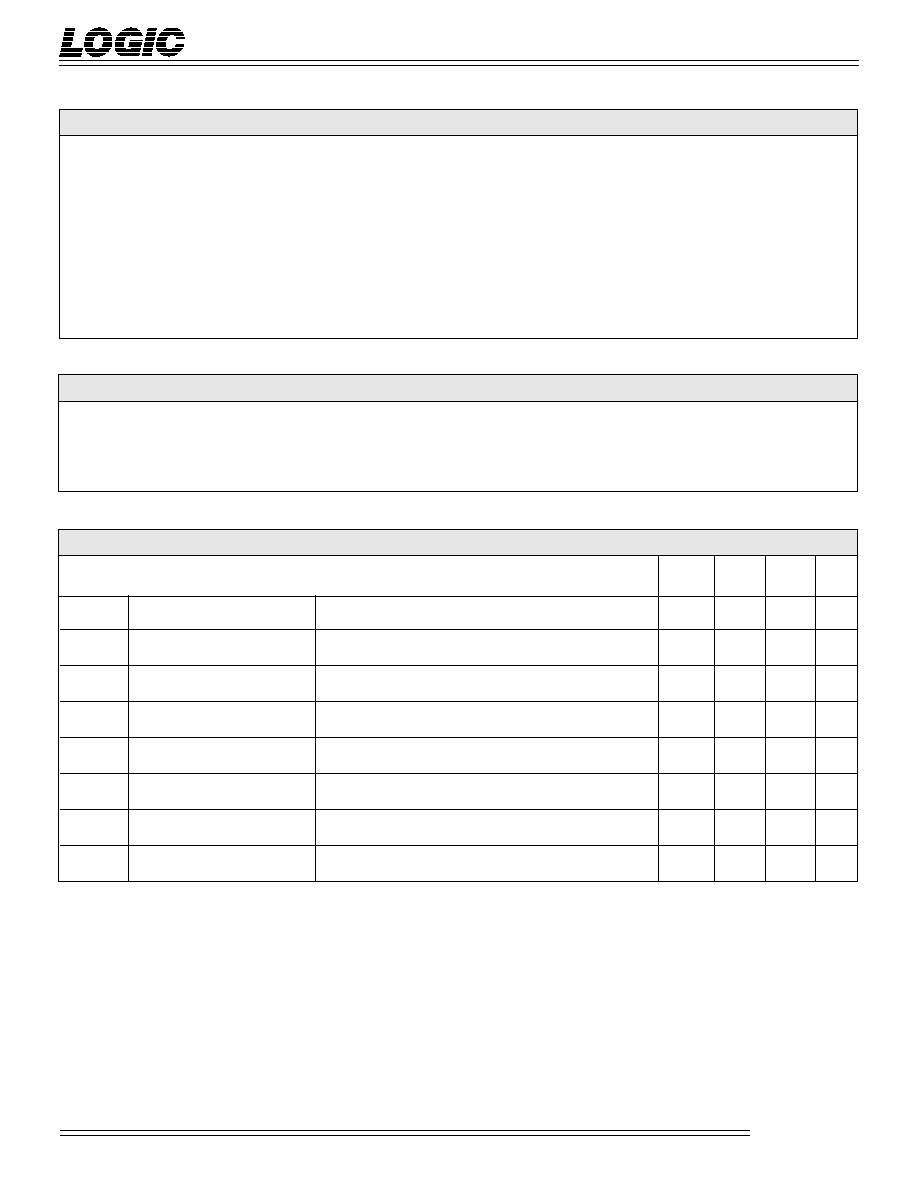

F

IGURE

1

A

.

I

NPUT

F

ORMATS

F

IGURE

1

B

.

O

UTPUT

F

ORMATS

15 14 13

10

9

8

≠2

0

(Sign)

2

≠1

2

≠2

2

≠5

2

≠6

2

≠7

7

6

5

2

1

0

≠2

0

(Sign)

2

≠8

2

≠9

2

≠12

2

≠13

2

≠14

LMU08 Fractional Two's Complement

15 14 13

10

9

8

≠2

14

(Sign)

2

13

2

12

2

9

2

8

2

7

7

6

5

2

1

0

≠2

14

(Sign)

2

6

2

5

2

2

2

1

2

0

LMU08 Integer Two's Complement

15 14 13

10

9

8

2

≠1

2

≠2

2

≠3

2

≠6

2

≠7

2

≠8

7

6

5

2

1

0

2

≠9

2

≠10

2

≠11

2

≠14

2

≠15

2

≠16

LMU8U Unsigned Fractional

15 14 13

10

9

8

2

15

2

14

2

13

2

10

2

9

2

8

7

6

5

2

1

0

2

7

2

6

2

5

2

2

2

1

2

0

LMU8U Unsigned Integer

MSP

LSP

7

6

5

2

1

0

≠2

0

(Sign)

2

≠1

2

≠2

2

≠5

2

≠6

2

≠7

7

6

5

2

1

0

≠2

0

(Sign)

2

≠1

2

≠2

2

≠5

2

≠6

2

≠7

LMU08 Fractional Two's Complement

7

6

5

2

1

0

≠2

7

(Sign)

2

6

2

5

2

2

2

1

2

0

7

6

5

2

1

0

≠2

7

(Sign)

2

6

2

5

2

2

2

1

2

0

LMU08 Integer Two's Complement

7

6

5

2

1

0

2

≠1

2

≠2

2

≠3

2

≠6

2

≠7

2

≠8

7

6

5

2

1

0

2

≠1

2

≠2

2

≠3

2

≠6

2

≠7

2

≠8

LMU8U Unsigned Fractional

7

6

5

2

1

0

2

7

2

6

2

5

2

2

2

1

2

0

7

6

5

2

1

0

2

7

2

6

2

5

2

2

2

1

2

0

LMU8U Unsigned Integer

A

IN

B

IN

DEVICES INCORPORATED

LMU08/8U

8 x 8-bit Parallel Multiplier

Multipliers

08/16/2000≠LDS.08/8U-R

3

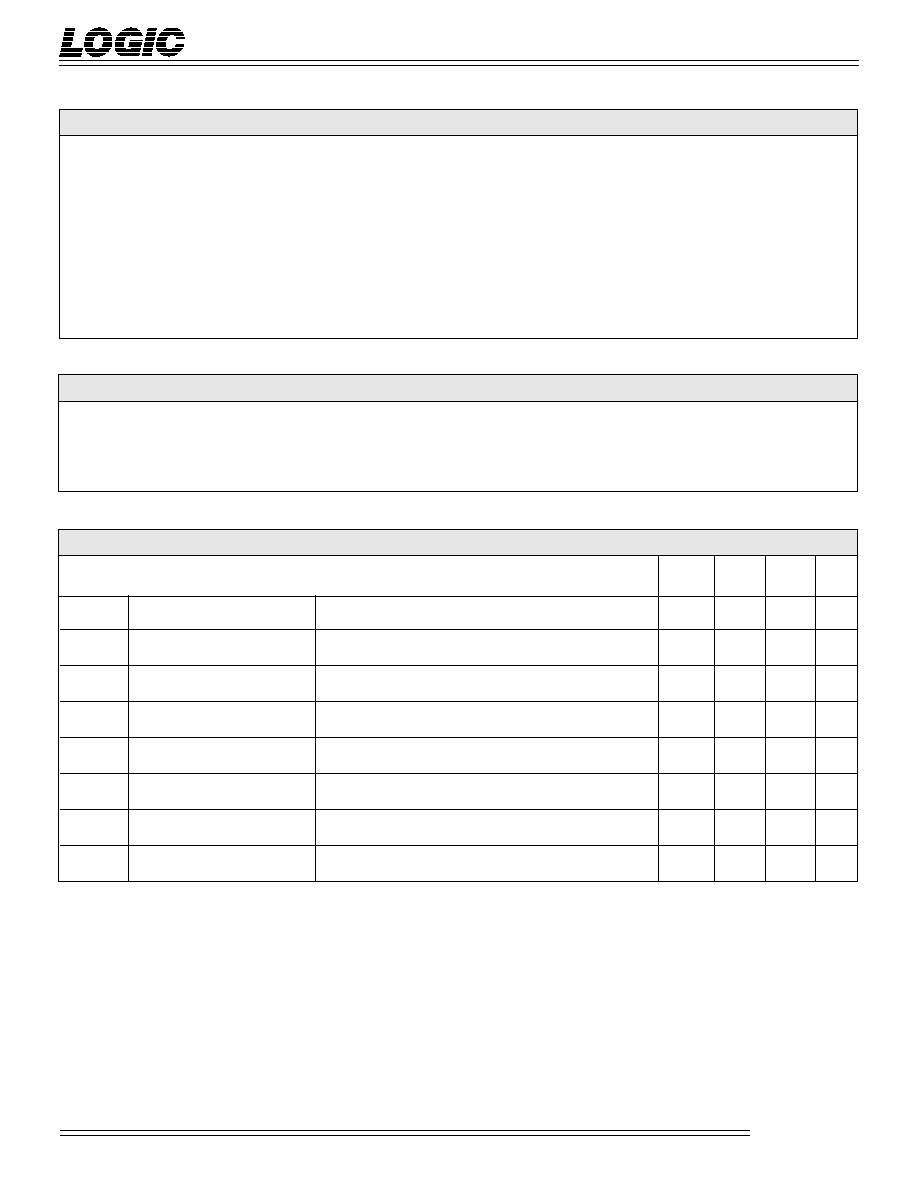

Storage temperature ........................................................................................................... ≠65∞C to +150∞C

Operating ambient temperature ........................................................................................... ≠55∞C to +125∞C

V

CC

supply voltage with respect to ground ............................................................................ ≠0.5 V to +7.0 V

Input signal with respect to ground ........................................................................................ ≠3.0 V to +7.0 V

Signal applied to high impedance output ............................................................................... ≠3.0 V to +7.0 V

Output current into low outputs ............................................................................................................. 25 mA

Latchup current ............................................................................................................................... > 400 mA

M

AXIMUM

R

ATINGS

Above which useful life may be impaired (Notes 1, 2, 3, 8)

O

PERATING

C

ONDITIONS

To meet specified electrical and switching characteristics

E

LECTRICAL

C

HARACTERISTICS

Over Operating Conditions (Note 4)

Mode

Temperature Range (Ambient)

Supply

Voltage

Active Operation, Commercial

0∞C to +70∞C

4.75 V

V

CC

5.25 V

Active Operation, Military

≠55∞C to +125∞C

4.50 V

V

CC

5.50 V

Symbol

Parameter

Test Condition

Min

Typ

Max

Unit

V

OH

Output High Voltage

V

CC

= Min., I

OH

= ≠2.0 mA

2.4

V

V

OL

Output Low Voltage

V

CC

= Min., I

OL

= 8.0 mA

0.5

V

V

IH

Input High Voltage

2.0

V

CC

V

V

IL

Input Low Voltage

(Note 3)

0.0

0.8

V

I

IX

Input Current

Ground

V

IN

V

CC

(Note 12)

±

20

µA

I

OZ

Output Leakage Current

Ground

V

OUT

V

CC

(Note 12)

±

20

µA

I

CC1

V

CC

Current, Dynamic

(Notes 5, 6)

8

24

mA

I

CC2

V

CC

Current, Quiescent

(Note 7)

1.0

mA

DEVICES INCORPORATED

LMU08/8U

8 x 8-bit Parallel Multiplier

Multipliers

08/16/2000≠LDS.08/8U-R

4

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

123456789012345678901234567890121234567890123

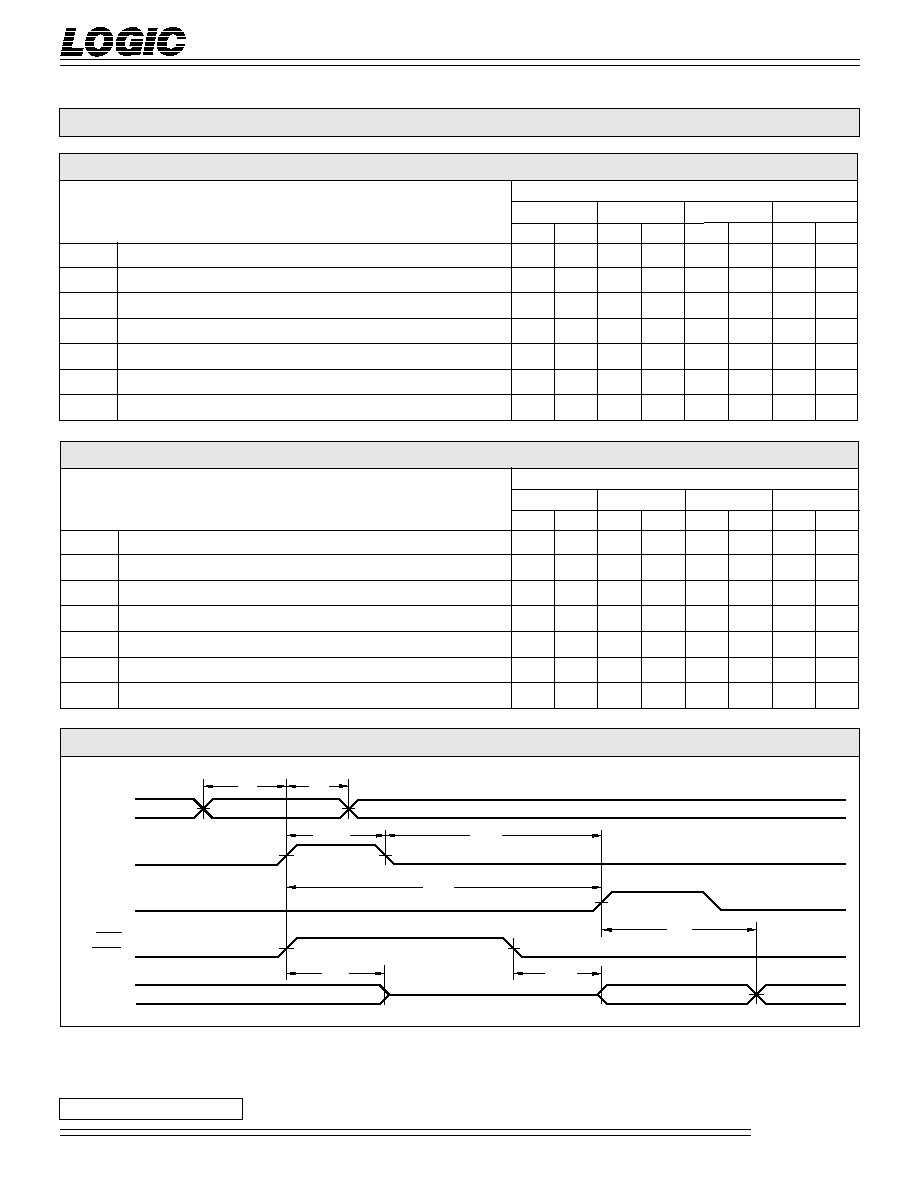

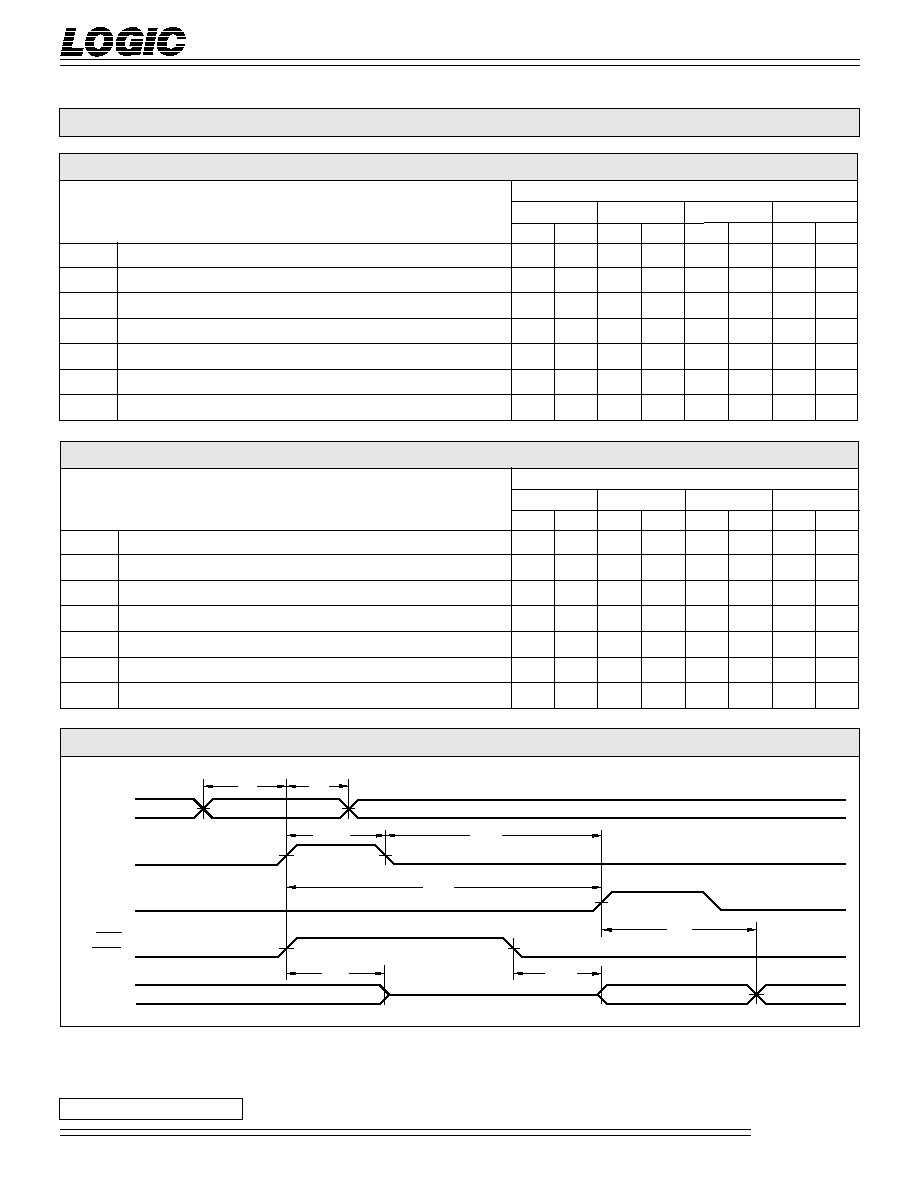

LMU08/8U≠

90*

60*

45*

25*

Symbol

Parameter

Min

Max

Min

Max

Min

Max

Min

Max

t

MC

Clocked Multiply Time

90

60

45

25

t

PW

Clock Pulse Width

25

20

15

10

t

S

Input Register Setup Time

20

15

15

15

t

H

Input Register Hold Time

5

2

2

2

t

D

Output Delay

35

22

22

20

t

ENA

Three-State Output Enable Delay

(Note 11)

35

24

24

20

t

DIS

Three-State Output Disable Delay

(Note 11)

35

22

22

20

M

ILITARY

O

PERATING

R

ANGE

(≠55∞C to +125∞C)

Notes 9, 10 (ns)

SWITCHING CHARACTERISTICS

LMU08/8U≠

70*

50

35

20*

Symbol

Parameter

Min

Max

Min

Max

Min

Max

Min

Max

t

MC

Clocked Multiply Time

70

50

35

20

t

PW

Clock Pulse Width

20

20

10

8

t

S

Input Register Setup Time

14

14

14

10

t

H

Input Register Hold Time

4

0

0

0

t

D

Output Delay

25

20

20

18

t

ENA

Three-State Output Enable Delay

(Note 11)

24

22

22

15

t

DIS

Three-State Output Disable Delay

(Note 11)

22

20

20

15

C

OMMERCIAL

O

PERATING

R

ANGE

(0∞C to +70∞C)

Notes 9, 10 (ns)

123456789012345678901234

123456789012345678901234

123456789012345678901234

123456789012345678901234

*D

ISCONTINUED

S

PEED

G

RADE

S

WITCHING

W

AVEFORMS

HIGH IMPEDANCE

INPUT

t

ENA

t

DIS

t

D

t

PW

t

MC

t

PW

t

H

t

S

CLK A

CLK B

CLK R

OEL

R

15-0

OEM

DEVICES INCORPORATED

LMU08/8U

8 x 8-bit Parallel Multiplier

Multipliers

08/16/2000≠LDS.08/8U-R

5

1. Maximum Ratings indicate stress

specifications only. Functional oper-

ation of these products at values beyond

those indicated in the Operating Condi-

tions table is not implied. Exposure to

maximum rating conditions for ex-

tended periods may affect reliability.

2. The products described by this spec-

ification include internal circuitry de-

signed to protect the chip from damag-

ing substrate injection currents and ac-

cumulations of static charge. Neverthe-

less, conventional precautions should

be observed during storage, handling,

and use of these circuits in order to

avoid exposure to excessive electrical

stress values.

3. This device provides hard clamping of

transient undershoot and overshoot. In-

put levels below ground or above V

CC

will be clamped beginning at ≠0.6 V and

V

CC

+ 0.6 V. The device can withstand

indefinite operation with inputs in the

range of ≠0.5 V to +7.0 V. Device opera-

tion will not be adversely affected, how-

ever, input current levels will be well in

excess of 100 mA.

4. Actual test conditions may vary from

those designated but operation is guar-

anteed as specified.

5. Supply current for a given applica-

tion can be accurately approximated by:

where

N = total number of device outputs

C = capacitive load per output

V = supply voltage

F = clock frequency

6. Tested with all outputs changing ev-

ery cycle and no load, at a 5 MHz clock

rate.

7. Tested with all inputs within 0.1 V of

V

CC

or Ground, no load.

8. These parameters are guaranteed

but not 100% tested.

NCV F

4

2

NOTES

9. AC specifications are tested with

input transition times less than 3 ns,

output reference levels of 1.5 V (except

t

DIS

test), and input levels of nominally

0 to 3.0 V. Output loading may be a

resistive divider which provides for

specified I

OH

and I

OL

at an output

voltage of V

OH

min and V

OL

max

respectively. Alternatively, a diode

bridge with upper and lower current

sources of I

OH

and I

OL

respectively,

and a balancing voltage of 1.5 V may be

used. Parasitic capacitance is 30 pF

minimum, and may be distributed.

This device has high-speed outputs ca-

pable of large instantaneous current

pulses and fast turn-on/turn-off times.

As a result, care must be exercised in the

testing of this device. The following

measures are recommended:

a. A 0.1 µF ceramic capacitor should be

installed between V

CC

and Ground

leads as close to the Device Under Test

(DUT) as possible. Similar capacitors

should be installed between device V

CC

and the tester common, and device

ground and tester common.

b. Ground and V

CC

supply planes

must be brought directly to the DUT

socket or contactor fingers.

c. Input voltages should be adjusted to

compensate for inductive ground and V

CC

noise to maintain required DUT input

levels relative to the DUT ground pin.

10. Each parameter is shown as a min-

imum or maximum value. Input re-

quirements are specified from the point

of view of the external system driving

the chip. Setup time, for example, is

specified as a minimum since the exter-

nal system must supply at least that

much time to meet the worst-case re-

quirements of all parts. Responses from

the internal circuitry are specified from

the point of view of the device. Output

delay, for example, is specified as a

maximum since worst-case operation of

any device always provides data within

that time.

11. For the t

ENA

test, the transition is

measured to the 1.5 V crossing point

with datasheet loads. For the t

DIS

test,

the transition is measured to the

±200mV level from the measured

steady-state output voltage with

±10mA loads. The balancing volt-

age, V

TH

, is set at 3.5 V for Z-to-0

and 0-to-Z tests, and set at 0 V for Z-

to-1 and 1-to-Z tests.

12. These parameters are only tested at

the high temperature extreme, which is

the worst case for leakage current.

S1

I

OH

I

OL

V

TH

C

L

DUT

OE

0.2 V

t

DIS

t

ENA

0.2 V

1.5 V

1.5 V

3.5V Vth

1

Z

0

Z

Z

1

Z

0

1.5 V

1.5 V

0V Vth

V

OL

*

V

OH

*

V

OL

*

V

OH

*

Measured V

OL

with I

OH

= ≠10mA and I

OL

= 10mA

Measured V

OH

with I

OH

= ≠10mA and I

OL

= 10mA

F

IGURE

B. T

HRESHOLD

L

EVELS

F

IGURE

A. O

UTPUT

L

OADING

C

IRCUIT