| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CW001105 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

DB08-000172-00

October 2001

1 of 32

Rev. A

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

CW001105

ARM966E-S

Microprocessor Core

Preliminary Datasheet

The CW001105 ARM966E-S core integrates the ARM9E-S 32-bit

processor, an instruction RAM, a data RAM, a write buffer, and an AHB

bus interface. The CW001105 supports both the 32-bit ARM and 16-bit

Thumb instruction sets, allowing you to trade off between high

performance and high code density. Additionally the CW001105 supports

the ARM9E instruction extensions. It provides an enhanced multiplier for

increased DSP performance. The CW001105 core is developed using

LSI Logic's G12

Æ

-p performance process.

Figure 1

CW001105 Block Diagram

AHB Bus

Interface Unit

and

Write Buffer

Instruction

SRAM

Dout

Addr

Din

Data

SRAM

Dout

Addr

Din

System

Control

Coprocessor

(CP15)

External

Coprocessor

Interface

IA

ARM9E-S

INSTR

RDATA

DA

WDATA

System

Controller

ETM

Interface

Core

2 of 32

CW001105 ARM966E-S Microprocessor Core

DB08-000172-00

October 2001 - Rev. A

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

The AHB bus interface eases connection to cached and SRAM-based

memory systems.

The CW001105 supports the ARM debug architecture and includes logic

to assist in both hardware and software debug. It supports non-stopping

hardware debug, which allows critical exception handlers to execute

while debugging the system. The CW001105 provides real-time trace

and supports external coprocessors.

Features

This section lists the key features of the CW001105 microprocessor core:

∑

ARM9E-S processor core

∑

Instruction and Data RAMs with independent sizes up to 512 Kbytes

∑

DMA Interface to Data RAM

∑

ARM Advanced High-performance Bus (AHB) interface unit with

Write Buffer

≠

16-word Write Buffer depth at up to four addresses

≠

Burst transfer generation

≠

Support for split transactions

∑

External coprocessor interface

∑

System controller arbitrates between instruction and data memories

and AHB

∑

Optional embedded trace module (ETM) provides real-time trace

capability

∑

G12-p performance process

∑

0.18-micron drawn gate length (0.13 effective channel length)

∑

System clock operates at 195 MHz tested under worst-case

conditions, 1.62 V, 115 ∞C

CW001105 ARM966E-S Microprocessor Core

3 of 32

DB08-000172-00

October 2001 - Rev. A

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

Functional Description

This section briefly describes the main functional blocks of the

CW001105.

ARM9E-S Processor Core

The ARM9E-S processor core has a Harvard bus architecture with

separate instruction and data interfaces. This design allows concurrent

instruction and data accesses, and greatly reduces the cycles per

instruction of the processor. For optimal performance, single cycle

memory accesses for both interfaces are required, although the core can

be stalled for non-sequential accesses, or slower memory systems.

The processor is implemented using a five-stage pipeline:

∑

Instruction Fetch (F)

∑

Instruction Decode (D)

∑

Execute (E)

∑

Data Memory Access (M)

∑

Register Write (W)

ARM implementations are fully interlocked, so that software functions

identically across different implementations without concern for pipeline

effects.

System Controller

The system controller oversees the interactions between the Instruction

RAM, Data RAM, and the Bus Interface Unit. It controls internal

arbitration between the blocks and stalls the appropriate blocks when

required.

CP15 System Control Coprocessor

The processor core uses a set of registers in the CP15 Coprocessor to

control the functionality of the RAMs and the Write Buffer. These

registers are accessed using the coprocessor instructions MCR and

MRC.

4 of 32

CW001105 ARM966E-S Microprocessor Core

DB08-000172-00

October 2001 - Rev. A

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

Address Decoders

The address decoders determine whether a memory request accesses

the internal RAM or the AHB interface. The address decoders provide a

hit/miss indication to the system controller, which then either stalls the

core if an AHB read or unbuffered write access is required or allows

execution to continue if the access hits the RAM or is a buffered write.

Instruction and Data RAMs

The CW001105 incorporates internal instruction and data memories to

allow high-speed operation without incurring the performance penalties

of accessing the system bus. Typically, the CW001105 offers lower power

solutions than cached alternatives because memory is segmented to

conserve power. The Instruction and Data RAMs each consist of blocks

of ASIC library compiled RAM. Logically, the RAM sizes can be of any

size up to 64 Mbytes, but the practical limit is approximately 512 Kbytes

for the G12 technology. The instruction and data memories can have

unique sizes.

DMA Interface

The Direct Memory Access (DMA) interface allows an external device

direct access to the CW001105 Data RAM. If a single-port Data RAM is

used, then the DMA interface stalls the CW001105 microprocessor core

during the DMA transfer. If a dual-port Data RAM is used, then the DMA

interface does not stall the CW001105 during the DMA transfer.

AHB Interface Unit and Write Buffer

The AHB (Advanced High-performance Bus) is a new generation of

AMBA bus, which meets the requirements of high-performance

synthesizable designs. The AHB Interface Unit arbitrates between the

external bus transaction sources within the CW001105. It stalls all other

accesses until the current request has been completed. The AHB

Interface Unit supports the following types of transactions: burst

transfers, split transactions, single-cycle bus master handovers, single

clock edge operations, and non-3-state implementations.

The Write Buffer is a 12-entry FIFO. It increases system performance.

CW001105 ARM966E-S Microprocessor Core

5 of 32

DB08-000172-00

October 2001 - Rev. A

Copyright © 2000, 2001 by LSI Logic Corporation. All rights reserved.

External Coprocessor Interface

The CW001105 supports the connection of coprocessors through the

external coprocessor interface. All types of ARM coprocessor instructions

are supported. Coprocessors determine the instructions they need to

execute using a pipeline follower in the coprocessor.

JTAG and Debug Port

The CW001105 debug interface is based on IEEE Std. 1149.1-1990. It

allows the processor core to be stopped on a given instruction fetch

(breakpoint), data access (watchpoint), or external debug request. The

JTAG-style serial interface allows instructions to be serially inserted into

the pipeline of the core without using the external data bus.

Embedded Trace Module Interface

This interface connects to an external Embedded Trace Module (ETM).

The ETM provides a high-speed port for tracing of the processor core in

real time.

Enhanced Instruction Set Summary

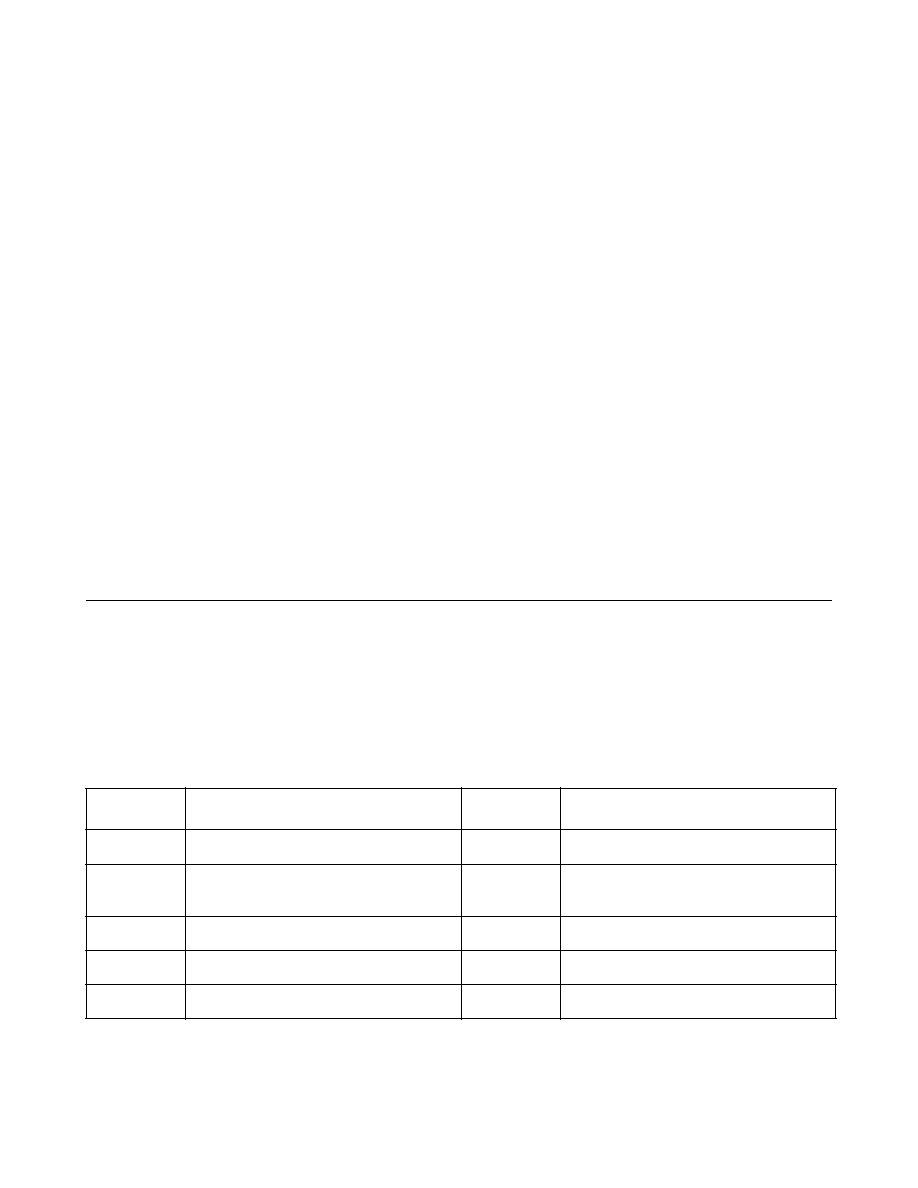

Table 1

lists the instruction enhancements made to the ARM9E-S

instruction set. The ARM9E extensions improve the ARM architecture's

performance in signal processing algorithms.

Table 1

ARM9E Instruction Set Summary

Instruction

Description

Instruction

Description

CLZ

Count Leading Zeros

QADD

Saturating Add

QDADD

Saturated Double Rn and Saturated

Add

QDSUB

Saturated Double Rn and Saturated

Subtract

QSUB

Saturating Subtract

SMLAxy

Signed Integer Multiply-Accumulate

SMLALxy

Signed Multiply-Accumulate

SMLAWy

Signed Integer Multiply-Accumulate

SMULxy

Signed Integer Multiply

SMULWy

Signed Integer Multiply