DB08-000215-04

January 2005

1 of 30

Version 2.0

Copyright © 2003, 2004, 2005 by LSI Logic Corporation. All rights reserved.

LSISAS1064 4-Port 3 Gbit/s

Serial Attached SCSI Controller

Datasheet

Version 2.0

The LSISAS1064 is a 4-port, 3.0 Gbit/s SAS/SATA controller that is

compliant with the Fusion-MPTTM architecture, provides a PCI-X

interface, and supports Integrated RAIDTM.

The LSISAS1064 controller brings 3.0 Gbit/s SAS performance to host

adapter, workstation, and server designs, making it easy to add a SAS

interface to any PCI or PCI-X

1

system. The LSISAS1064 integrates four

high-performance SAS/SATA phys and a 64-bit, 133 MHz PCI-X bus

master DMA core. Each of the four phys on the LSISAS1064 is capable

of 3.0 Gbit/s and 1.5 Gbit/s SAS link rates and 3.0 Gbit/s and 1.5 Gbit/s

SATA link rates. The LSISAS1064 supports the ANSI Serial Attached

SCSI Standard, Version 1.0. The controller also supports the Serial ATA

(SATA) protocol defined by the Serial ATA Specification, Version 1.0a.

Supporting both the SAS and SATA interfaces, the LSISAS1064 is a

versatile controller that provides the backbone of both server and high-

end workstation environments.

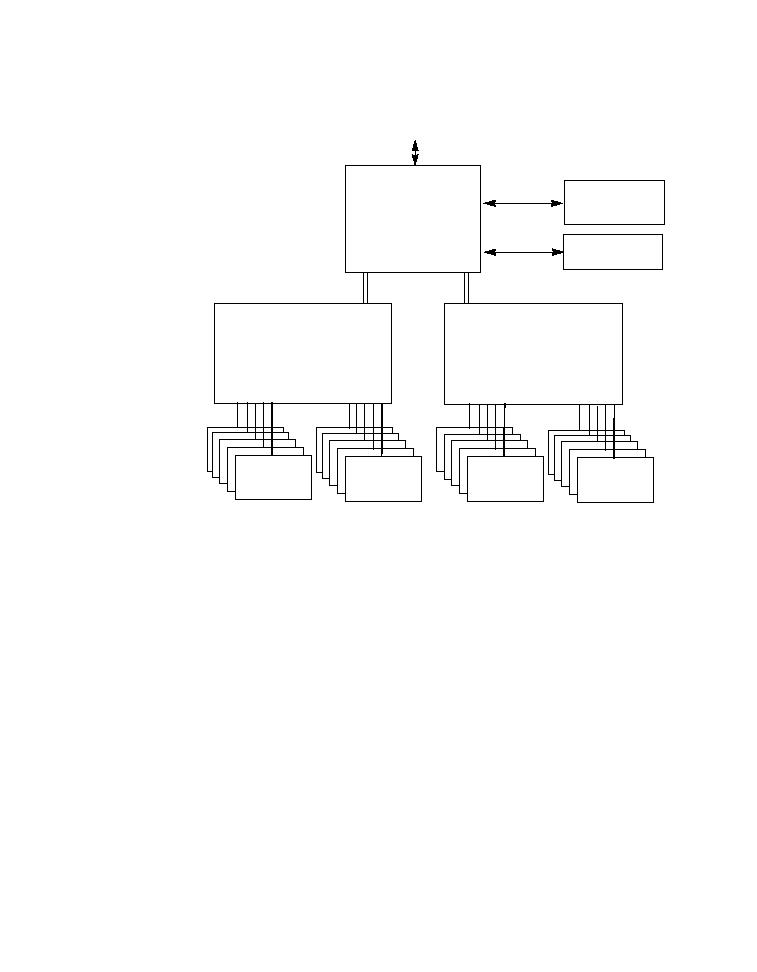

Figure 1

shows a direct-connect

configuration.

Figure 2

provides an example of the LSISAS1064

configured with an LSISASx12 expander.

Figure 1

LSISAS1064 Direct-Connect Example Application

1. In some instances, this manual references PCI-X explicitly. References to the PCI bus may

be inclusive of both the PCI specification and PCI-X addendum, or may only refer to the PCI

bus depending on the operating mode of the device.

Flash ROM/

LSISAS1064

64-Bit, 133 MHz

PCI-X

SAS/SATA Device

32-Bit Memory

Address/Data

Bus

PSBRAM/

Tx , Rx

I

2

C

SAS/SATA Device

Tx , Rx

SAS/SATA Device

Tx , Rx

SAS/SATA Device

Tx , Rx

PCI/PCI-X Interface

NVSRAM

Controller

I

2

C

Interface

2 of 30

LSISAS1064 4-Port 3 Gbit/s Serial Attached SCSI Controller

DB08-000215-04

January 2005 - Version 2.0 Copyright © 2003, 2004, 2005 by LSI Logic Corporation. All rights reserved.

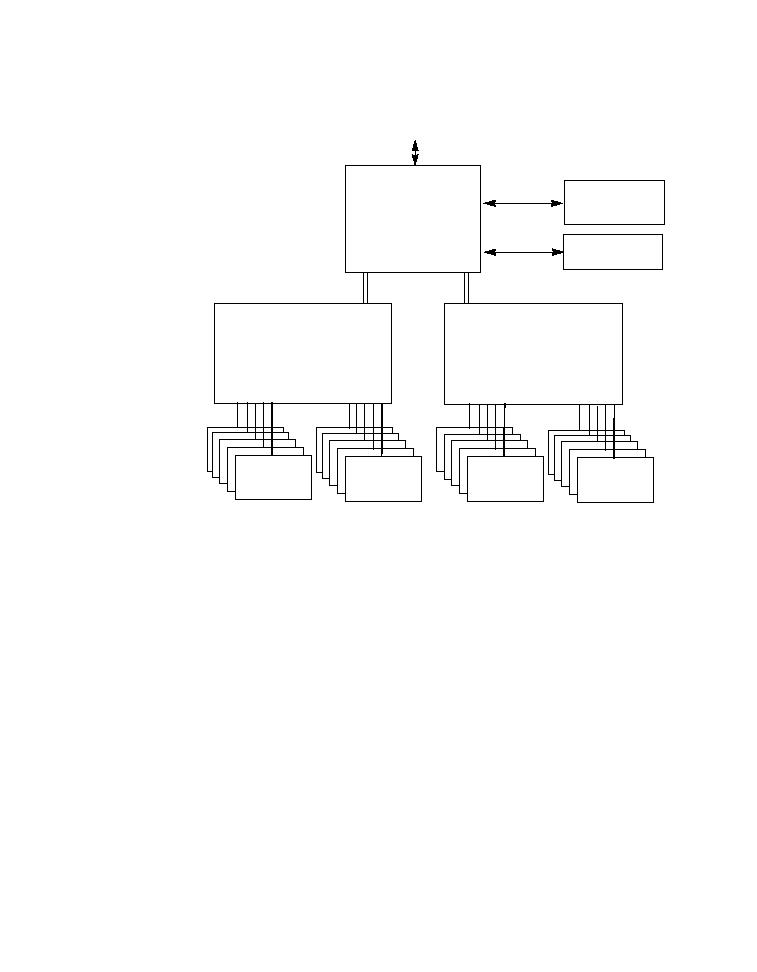

Figure 2

LSISAS1064 Controller and LSISASx12 Expander

Example Application

The SAS interface uses the proven SCSI data transfer command set to

ensure reliable data transfers while providing the connectivity and

flexibility of point-to-point serial data transfers. The SAS interface

provides improved performance, simplified cabling, smaller connectors,

lower pin count, and lower power requirements when compared to

parallel SCSI. SAS controllers leverage an electrical and physical

connection interface that is compatible with Serial ATA technology.

Each port on the LSISAS1064 supports SAS and SATA devices using the

SAS Serial SCSI Protocol (SSP), Serial Management Protocol (SMP),

Serial Tunneling Protocol (STP), and SATA. The SSP enables

communication with other SAS devices. SATA enables the LSISAS1064

to communicate with other SATA devices. The SMP communicates

topology management information directly with an attached SAS

expander device, such as the LSISASx12. STP enables the LSISAS1064

to communicate with a SATA device through an attached expander.

The LSISAS1064 supports a 133 MHz, 64-bit PCI-X bus. With the

exception that the PCI interface is not tolerant of 5 V PCI, the interface

LSISAS1064

LSISASx12

Flash ROM/

32-Bit Memory

Address/Data

Bus

PSBRAM/

I

2

C

NVSRAM

LSISASx12

SAS/SATA

Drives

PCI/PCI-X Interface

SAS/SATA

Drives

SAS/SATA

Drives

SAS/SATA

Drives

I

2

C

Interface

LSISAS1064 4-Port 3 Gbit/s Serial Attached SCSI Controller

3 of 30

DB08-000215-04

January 2005 - Version 2.0 Copyright © 2003, 2004, 2005 by LSI Logic Corporation. All rights reserved.

is backward compatible with all revisions of the PCI/PCI-X bus. The

LSISAS1064 supports PCI-X split completion cycles and 32-bit or 64-bit

data bursts with variable burst length. The LSISAS1064 supports the

PCI-X Addendum to the PCI Local Bus Specification, Revision 2.0, and

the PCI Local Buss Specification, Revision 3.0.

The LSISAS1064 supports the Integrated RAID solution, which is a

highly integrated, low-cost RAID implementation. It is designed for

systems requiring redundancy and high availability but not needing a full-

featured RAID implementation. The Integrated RAID solution includes

Integrated MirroringTM (IM) technology and Integrated StripingTM (IS)

technology. IM provides physical mirroring of up to eight physical drives.

IM requires a nonvolatile RAM (NVSRAM) to support write journaling. IS

enables data striping across up to eight physical drives. The Integrated

RAID solution is OS-independent, easy to install and configure, and does

not require a special driver. The runtime operation of the Integrated RAID

solution is transparent to the operating system. A single firmware build

supports all Integrated RAID capabilities. The LSISAS1064 also provides

Zero Channel RAID (ZCR) support.

The LSISAS1064 is based on the Fusion-MPT (Message Passing

Technology) architecture, which features a performance-based message

passing protocol that offloads the host CPU by completely managing all

I/Os and minimizes system bus overhead by coalescing interrupts. The

Fusion-MPT architecture requires only a thin, easy to develop device

driver that is independent of the I/O bus. LSI Logic provides this device

driver.

To meet its flexibility and data transfer requirements, the LSISAS1064

uses an ARM

Æ

926 processor. The ARM926 offers data cache and

instruction cache, which provide a significant performance increase.

LSI Logic manufactures the LSISAS1064 controller using the GflxTM

technology.

4 of 30

LSISAS1064 4-Port 3 Gbit/s Serial Attached SCSI Controller

DB08-000215-04

January 2005 - Version 2.0 Copyright © 2003, 2004, 2005 by LSI Logic Corporation. All rights reserved.

Features

This section provides a summary of the LSISAS1064 features and

benefits.

SAS Features

SAS features include:

∑

Provides four fully independent phys

∑

Supports 3.0 Gbit/s and 1.5 Gbit/s SAS data transfers for each phy

∑

Supports SSP to enable communication with other SAS devices

∑

Supports SMP to communicate topology management information

∑

Provides a serial, point-to-point, enterprise-level storage interface

∑

Simplifies cabling between devices

∑

Provides a scalable interface that supports up to 128 devices through

multiple expanders

∑

Supports wide ports consisting of two, three, or four phys

∑

Supports narrow ports consisting of a single phy

∑

Transfers data using SCSI information units

SATA and STP Features

SATA and STP features include:

∑

Supports SATA data transfers of 3.0 Gbits/s and 1.5 Gbits/s

∑

Supports STP data transfers of 3.0 Gbits/s and 1.5 Gbits/s

∑

Provides a serial, point-to-point storage interface

∑

Simplifies cabling between devices

∑

Eliminates the Master-Slave construction used in parallel ATA

∑

Allows addressing of multiple SATA targets through an expander

∑

Allows multiple initiators to address a single target (in a fail-over

configuration) through an expander

LSISAS1064 4-Port 3 Gbit/s Serial Attached SCSI Controller

5 of 30

DB08-000215-04

January 2005 - Version 2.0 Copyright © 2003, 2004, 2005 by LSI Logic Corporation. All rights reserved.

PCI Performance

PCI features of the LSISAS1064 include:

∑

Supports a 133 MHz, 64-bit PCI/PCI-X interface that does the

following:

≠

Operates up to 133 MHz PCI-X

≠

Operates at 33 MHz or 66 MHz PCI

≠

Supports 32-bit or 64-bit data transfers

≠

Supports 32-bit or 64-bit addressing through Dual Address

Cycles (DAC)

≠

Provides a theoretical 1066 Mbytes/s PCI bandwidth

≠

Supports 3.3 V PCI, and is not 5 V PCI tolerant

≠

Complies with the PCI Local Bus Specification, Revision 3.0

≠

Complies with the PCI-X Addendum to the PCI Local Bus

Specification, Revision 2.0

≠

Complies with the PCI Power Management Interface

Specification, Revision 1.2

≠

Complies with the PC2001 Specification

∑

Provides unequaled performance through the Fusion-MPT

architecture

∑

Provides high throughput and low CPU utilization to offload the host

processor

∑

Uses a dedicated ARM926 processor

∑

Presents a single electrical load to the PCI bus

∑

Reduces Interrupt Service Routine (ISR) overhead with interrupt

coalescing

∑

Supports Message Signaled Interrupts (MSI) and MSI-X

∑

Supports 32-bit or 64-bit data bursts with variable burst lengths

∑

Supports the PCI Cache Line Size register

∑

Supports the PCI Memory Write and Invalidate, Memory Read Line,

and Memory Read Multiple commands