F E A T U R E S

∑ 64-bit standard R4000 MIPS-III

architecture with integrated MIPS-III

FPU

∑ 240MHz (under worst case conditions)

∑ AMBA AHB Interface

∑ Harvard Cache Architecture

∑ Integrated 2 way set associative 16K

Instruction Cache and 16K write-back

or write-through Data Cache

∑ Bus Snooping enabling cache

coherency in a multi-processing

environment

∑ Compact EasyMACRO size:

12 square mm

- includes 16K instruction and 16K

Data Caches

∑ Integrated non-intrusive EJTAG Debug

with enhanced break functions and

Integrated PC Trace

∑ Low-operating voltage of 1.8V

∑ EasyMacro optimized for frequency

and area

∑ Designed for ease of rapid SoC

integration

∑ Fully supported by Industry Standard

Toolchains

I N T E G R A T E D M I N I R I S C

Æ

M I P S M I C R O P R O C E S S O R C O R E

O V E R V I E W

The EZ4030 extends the LSI Logic MIPS MiniRISC

Æ

family with a high per-

formance 64-bit microprocessor. The EZ4030 EasyMACRO

TM

is an optimized

implementation of a synthesizeable core that operates at up to 240MHz under

worst case conditions. With its high integer and floating point performance,

compact area, and low power consumption rating, the EZ4030 is well prepared

to meet the embedded system designer's growing demand for high performance

64-bit applications.

The EZ4030 EasyMACRO physical implementation facilitates the re-use of the

core in customers' designs. System designers do not need detailed knowledge of

the core for use in a system-on-a-chip design. Optimized for size and frequency,

the core is a highly integrated solution that is comprised of the MiniRISC

EZ4030 64-bit CPU and CPU sub-system. Specifically designed using industry-

standard, third-party EDA tools (including simulation, synthesis, static timing

analysis and ATPG), the EZ4030 further enhances LSI Logic's MIPS-based

embedded processor line. The EZ4030 EasyMACRO core is designed for rapid

system-on-a-chip ASIC integration through LSI Logic's CoreWare

Æ

design

methodology.

With an operating frequency of 240MHz, the EZ4030 is ideally suited for

performance driven embedded applications such as digital consumer set-top

boxes, advanced networking systems, high-end printers and all-in-one office

systems, all of which require the performance provided by 64-bit processing.

EZ4030 240MHz 64-bit MIPS

Æ

Processor Core with integrated

FPU

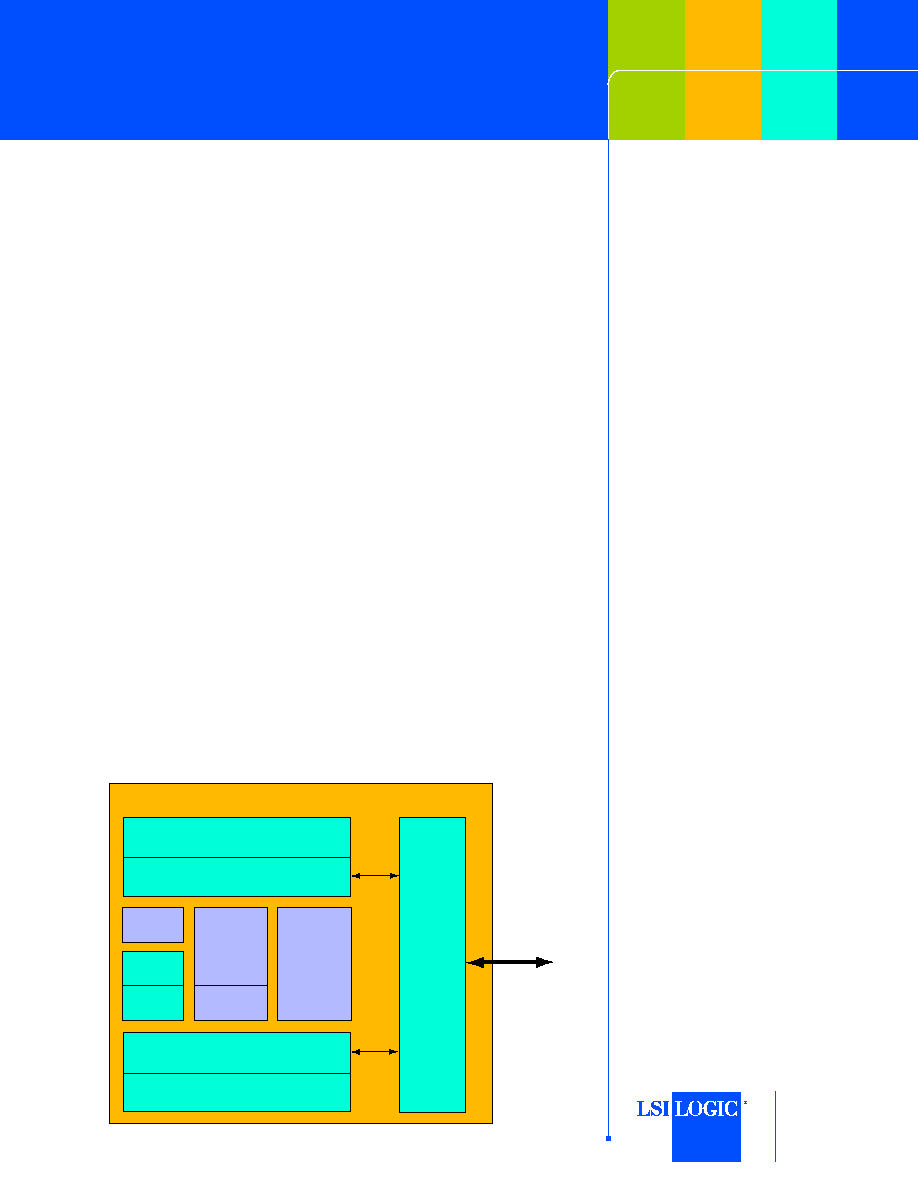

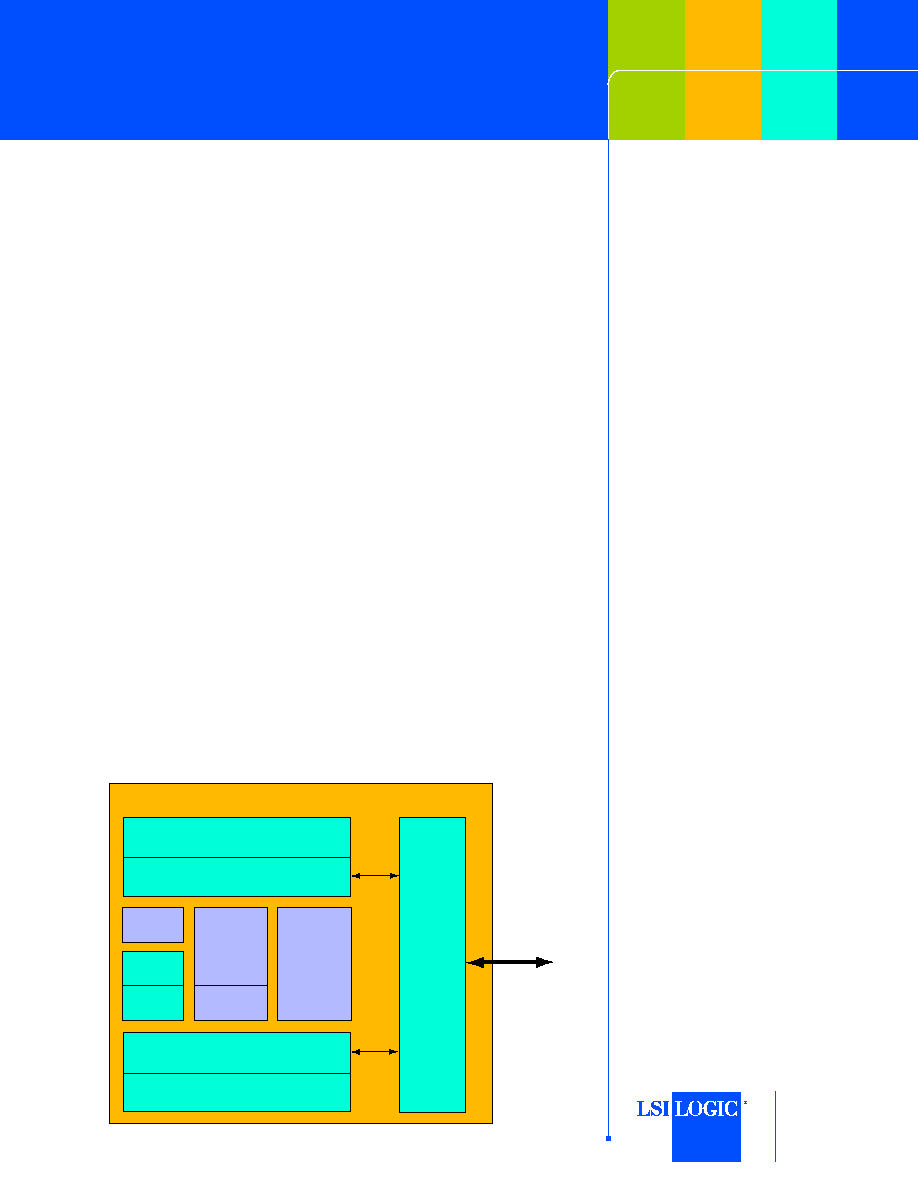

EZ4030 Block Diagram

AHB

EZ4030

Instruction Cache (16KB 2-way)

I-Cache Controller

Integer

Data Path

Module

CPU

Data Path

Control

Module

Bus

Interface

Unit

CPO

MMU

EJTAG

Interface

D-Cache Controller

Data Cache (16KB 2-way)

FPU

The

Communications

Company

TM

For more information please call:

LSI Logic Corporation

North American Headquarters

Milpitas, CA

Tel: 800 574 4286

LSI Logic Europe Ltd.

European Headquarters

United Kingdom

Tel: 44 1344 426544

Fax: 44 1344 481039

LSI Logic KK Headquarters

Tokyo, Japan

Tel: 81 3 5463 7165

Fax 81 3 5463 7820

LSI: Logic web site:

www.lsilogic.com

LSI Logic logo design, CoreWare, MiniRisc and

EasyMACRO are trademarks or registered trade-

marks of LSI Logic Corporation. MIPs, is a regis-

tered trademarks of MIPs Technologies Inc., used

under license. All other brand and product names

may be trademarks of their respective companies.

LSI Logic Corporation reserves the right to make

changes to any products and services herein at

any time without notice. LSI Logic does not assume

any responsibility or liability arising out of the

application or use of any product or service

described herein, except as expressly agreed to in

writing by LSI Logic; nor does the purchase, lease,

or use of a product or service from LSI Logic con-

vey a license under any patent rights, copyrights,

trademark rights, or any other of the intellectual

property rights of LSI Logic or of third parties.

Copyright ©2001 by LSI Logic Corporation.

All rights reserved.

1001.1k.SR.IK - Printed in USA

The

Communications

Company

TM

E Z 4 0 3 0 D E S C R I P T I O N

The EZ4030 EasyMACRO is an optimized implementation of a synthesize-

able core that operates at up to 240MHz under worst case conditions.

The EZ4030 core integrates a complete CPU and CPU subsystem. With its

high performance, compact area, and low power consumption rating, the

EZ4030 is well prepared to meet the SoC performance driven demands for

mid-to-high-end consumer set-top boxes, image processing, networking and

other applications requiring 64-bit performance. The CPU implements the

MIPS III integer and floating point instruction set. The CPU subsystem,

comprised of a floating point memory management unit, multiply-divide unit,

system-coprocessor, bus interface unit, separate 16K instruction and 16K data

caches, and on-chip non-intrusive EJTAG debug module, fits within the com-

pact 12-sq. mm EasyMACRO.

Improved embedded performance features of the EasyMACRO include

MAC instruction extensions and hardware prefetching. The memory manage-

ment unit, designed for Windows

Æ

CE compliance, includes dual 32 entry

TLBs, and supports variable page sizes ranging from 4K-16M. Offered with

an AMBA AHB interface, the EZ4030 Core connects to a vast amount of LSI

Logic and industry standard AMBA IP.

S U P P O R T P R O D U C T S

The EZ4030 MiniRISC MIPS core supports standard R4000 MIPS-III

instructions and leverages the widely available industry standard, low cost,

third-party tools developed in support of the MIPS architecture.

A complete evaluation and development kit is available for the EZ4030

EasyMACRO MIPS processor. The kit includes an EZ4030 development board,

an EJTAG probe, third-party tool chain, software examples and documentation.

C O R E W A R E D E S I G N P R O G R A M

As part of LSI Logic's extensive CoreWare IP library, the MiniRISC deliverables

include a Verilog-compatible RTL model, a system verification environment

(SVE), complete netlist, timing and example script files to accelerate customers'

ASIC SoC development using the EZ4030. The CoreWare design program

enables system-on-a-chip design integration, delivering unmatched market

advantages.

EZ4030 240MHz 64-bit MIPS Core