| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TH3122 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Pin Diagram

K-Bus Transceiver:

PNP-open emitter driver with slew rate control and current limita-

tion

BUS input voltage -24V ... 30V (independently of V

S

)

ISO 9141 and ODBII compliant

Possibility of BUS wake up

Operating voltage V

S

= 5.5 ... 16 V

Very low standby current consumption <100

µ

A

in normal mode (< 50

µ

A in sleep mode)

Linear low drop voltage regulator:

Output voltage 5V± 2%

Output current max. 100mA

Output current limitation

Overtemperature shutdown

Configurable reset time (15ms/100ms) and reset threshold voltage (3.15V / 4.65V)

Low voltage detection at VS

Wake-up by K-BUS traffic and start-up capable independent of EN voltage level

Universal comparator with an input voltage range ≠24V ... 30V

and digital output

Load dump protected (40V)

Part No.

Temperature Code

Package Code

TH3122

K ( -40∫C to 125∫C )

DF ( SOIC16, 300mil )

The TH3122 consists a low drop voltage regulator

5V/100mA and a K-Bus transceiver. The trans-

ceiver is suitable for K-Bus systems conform to

ISO 9141.

The combination of voltage regulator and bus

transceiver in combination with the monitoring

TH3122

1

EN

SENSE

GND

GND

VTR

GND

GND

RESET

BUS

SO

SI

SEN/STA

RxD

TxD

16

15

14

13

12

11

10

9

8

7

6

5

4

2

3

VS

VCC

SOIC16

Nov/02

Page 1

3901003122

Rev 003

functions make it possible to develop simple, but

powerful and cheap nodes in K-Bus systems.

The wide output current area and the configurable

reset time and reset voltage works together with

many different microcontrollers.

TH3122

K-Bus Transceiver with integrated Voltage Regulator

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Nov/02

Page 2

3901003122

Rev 003

Wake-up

pnp Control

slew rate

foldback

OSC

Over Temp

V

THSI_H

V

THSI_L

V

thH

V

thL

+5V

7.8V

6.8V

+5V

VS

EN

VTR

BUS

SI

SO

RxD

TxD

RESET

SENSE

VCC

Power Supply

+5V

Reset-Logic

VTR-Logic

Bus-Logic

SEN/STA

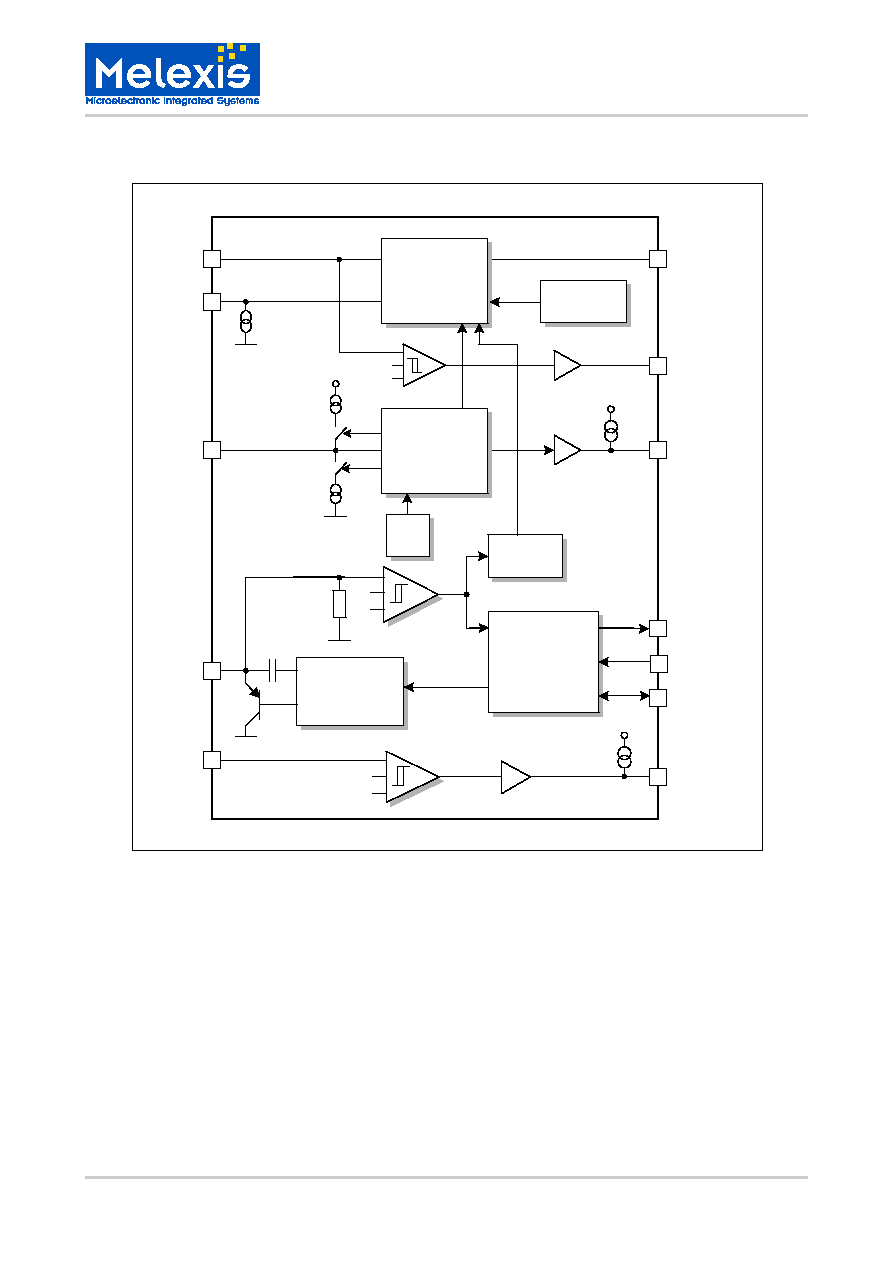

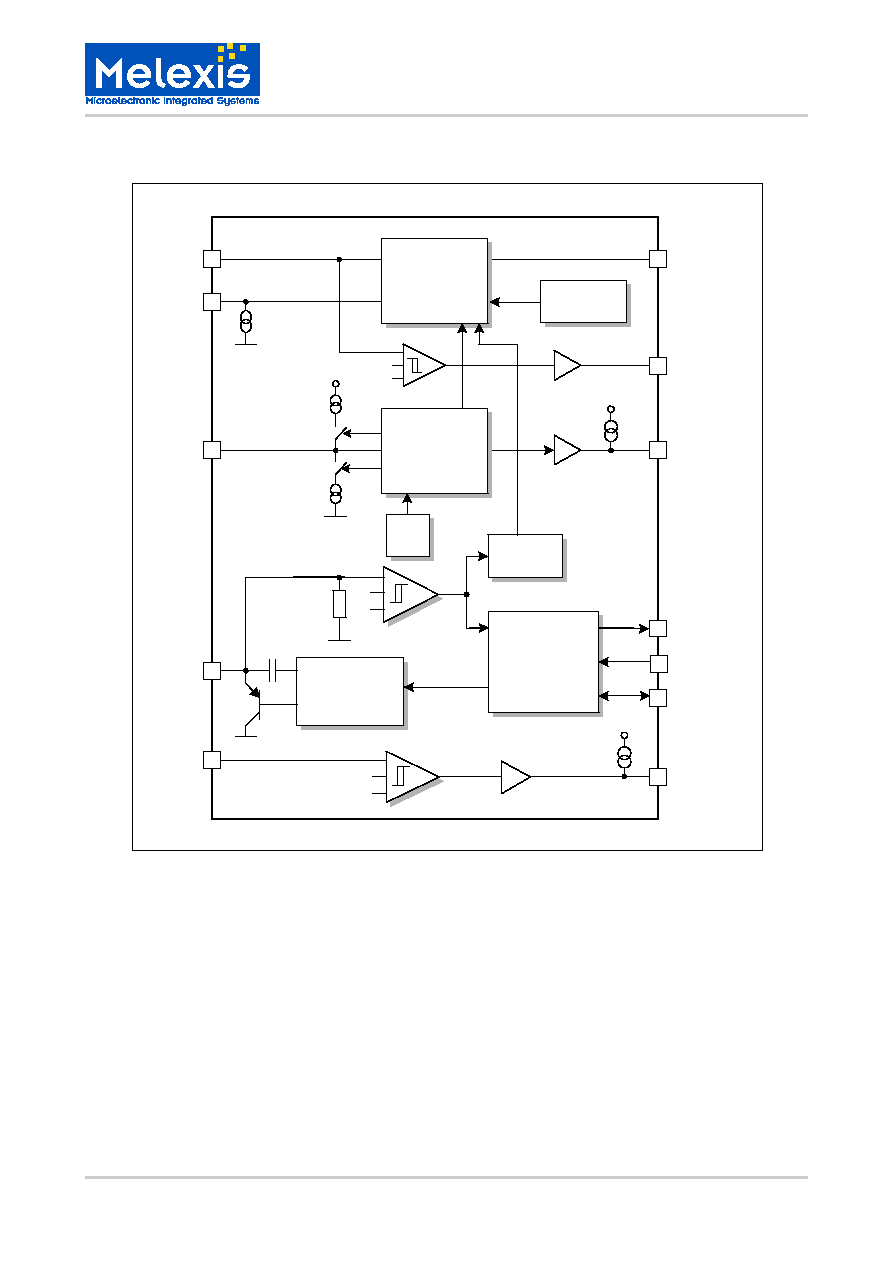

Figure 1 - Block Diagram

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Nov/02

Page 3

3901003122

Rev 003

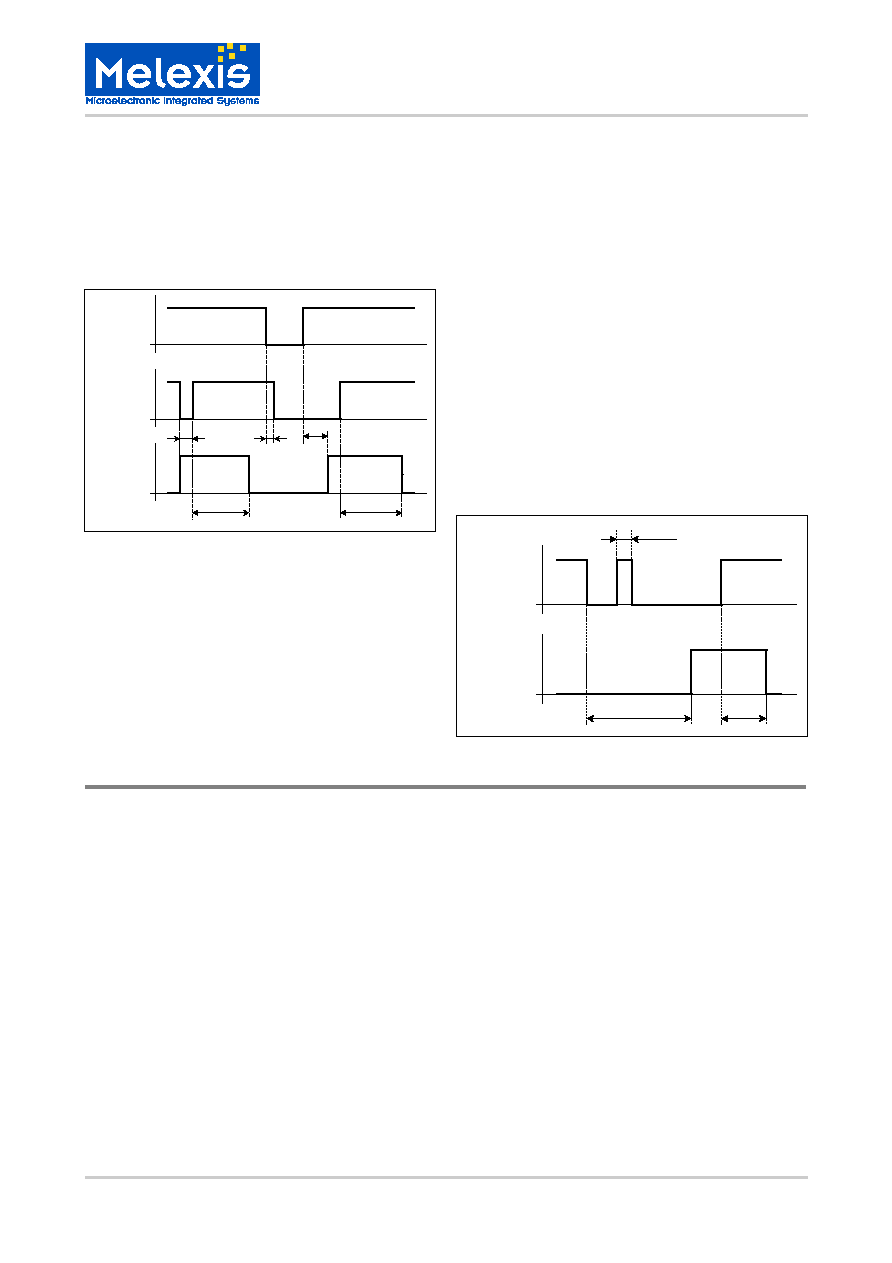

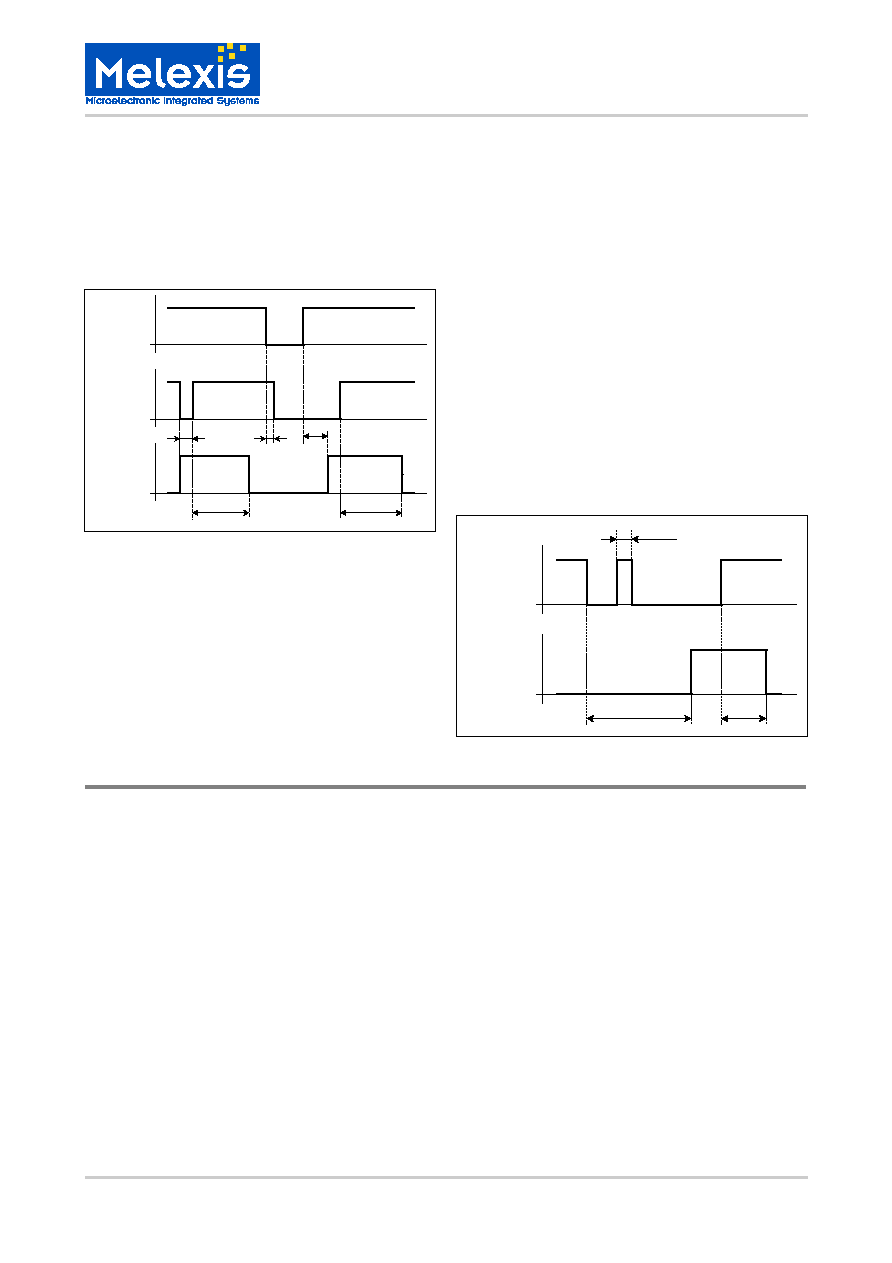

Figure 3 - Transmit Mode Pulse Diagram

Figure 4 - Receive Mode Pulse Diagram

BUS

RxD

t

debH

t

debL

< t

debH

< t

debL

The TH3122 consists a voltage regulator 5V/100mA and

a K-Bus transceiver, which is a bi-directional bus inter-

face device for data transfer between K-Bus and the K-

Bus protocol controller.

Also integrated into the transceiver are a voltage and

time controlled reset management, power down, wake

up function and a universal comparator for extended ap-

plications.

K-BUS Interface

The BUS Interface builds the connection between the

serial 5V bus line of the protocol controller and the 12V

K-Bus line.

The transceiver consists a pnp-driver with slew rate con-

trol and fold-back characteristic and consists as well in

the receiver a high voltage comparator followed by a de-

bouncing unit.

Transmit Mode

During the transmission the data at the pin TxD

will be

transferred to the pin BUS. To minimize the electromag-

netic emission of the bus line, the TH3122 has an inte-

grated slew rate control.

Receive Mode

The data at the pin BUS

will be transferred to the pin

RxD. Short spikes on the bus signal are suppressed by

the implemented debouncing circuit.

Figure 2 - Block Diagram K-Bus Transceiver

POR

VBAT

POR

VCC

Control-

logic

Bit-Compare

Constant-Low

VCC

ESD

ESD

VCC

OSC

Vref

Biasing

t

debBUS

pnp-

Control

- slew rate

- I

B

- foldback

V

thH

V

thL

RxD

TxD

SENSE

BUS

t

debWake

to W ake-up

Logic

SEN/STA

TxD

BUS

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Nov/02

Page 4

3901003122

Rev 003

Bit Compare

Are the signals at the pin TxD and the pin BUS

within a specified time t

bc

not identical, the

transmission will be interrupted.

If both signals at TxD and BUS are "High" within

the time t

ena

the transmission will be enabled. The

bit-compare-function is activ when the pin SEN/

STA is open (not overwritten).

Regulator

The TH3122 has an integrated linear regulator with an

output voltage of 5V ±

2% and an output current of max.

100mA. The regulator is switched on or off with a signal

on the EN pin or wake up with a BUS signal.

Initialization

The initialization is started if the power supply is switched

on, or after the temperature limitation has switched off

the regulator or in case of BUS traffic (wake up).

If the V

CC

voltage level is higher than V

RESEIN

, the reset

time t

RES

is started. This reset time is determined by the

Figure 5 - Bit Compare Pulse Diagram

TxD

BUS

t

ena

t < t

bc

SEN/STA

t

ena

t

bc

Using this pin as an input the transmission path

can be overwritten (independent of bit-compare

and constant-low function):

SEN/STA="0"

forcing the transmission path free

SEN/STA="1"

disable the transmission path

Constant Low Switch Off

A falling edge at pin TxD (from "1" to "0") starts the

internal constant low timer (SEN/STA open).

If the low level "0" is valid for the time t

low

the

transmission unit of the TH3122 will be disabled.

The receive unit is still active. A high level "1" at

TxD with a minimum pulse width of t

rec

reset the

constant low timer.

Transmitting is possible not until TxD and BUS is

High for the time t

ena

.

TxD

SEN/STA

t

low

t

ena

t < t

rec

Figure 6 - Constant Low Pulse Diagram

Linear Regulator and Controlling Functions

SEN/STA

The pin SEN/STA is bidirectional. Used as an

output the pin indicates whether the transmit-path

is enabled or disabled:

SEN/STA ="0"

transmission path is enabled

SEN/STA ="1"

transmission path is disabled

voltage level on the VTR pin (see table VTR Program-

ming). After t

RES

a rising edge on the RESET output is

generated (see figure 7 - Initialization).

The regulator is active and can only switched off with a

falling edge on EN. The regulator remain with EN=high in

active mode and therefore also the V

CC

voltage is active.

The input EN has an internal pull down resistor. If

EN=high, the internal pull down current is switched off to

minimize the quiescent current.

TH3122

K-Bus Transceiver with integrated Voltage Regulator

Nov/02

Page 5

3901003122

Rev 003

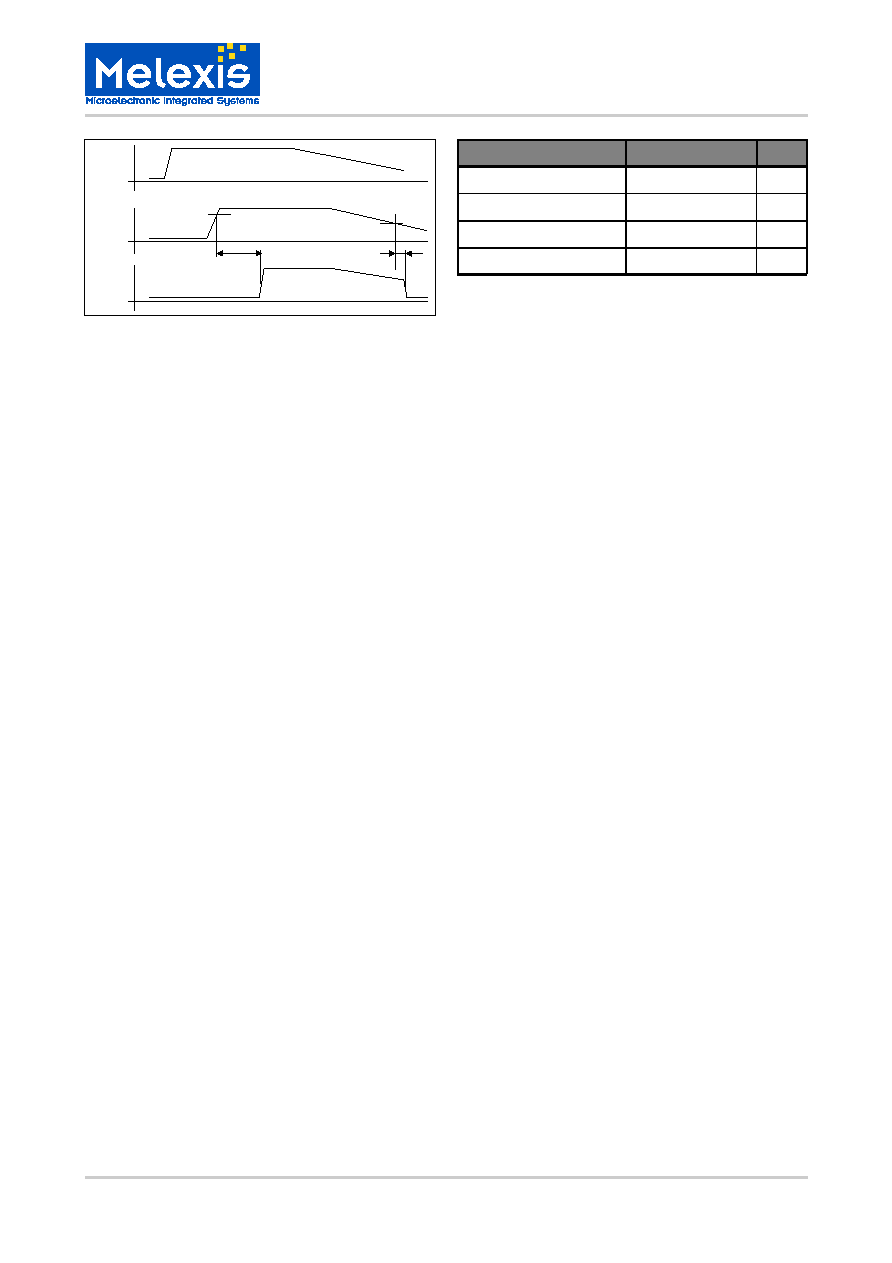

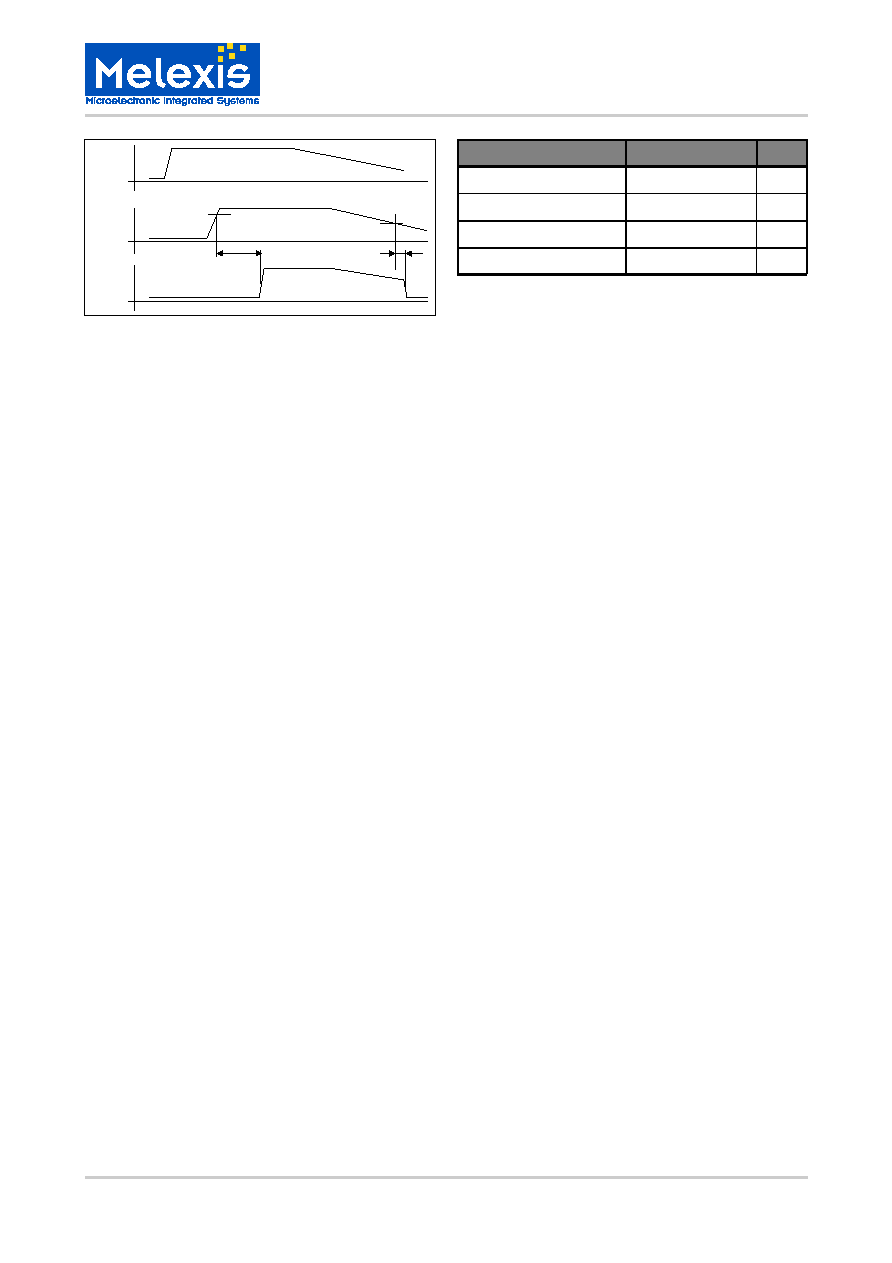

Figure 7 - Initialization

RESET Output

The RESET output is switched from low to high if V

S

is

switched on and V

CC

>V

RESEIN

after the time t

RES

.

If the voltage V

CC

drop below V

RES1

or V

RES2

then the RESET

output is switched from high to low after the time t

rr

has been

reached.

The voltage level for V

RES1

and V

RES2

and the corre-

sponding times t

RES

can be programmed via the ana-

logue input VTR.

Wake up with BUS traffic

If the regulator is put in standby mode it can be wake up

with the BUS interface. Every pulse on the BUS (high

pulse or low pulse) with a pulse width of min. 45

µ

s will

switch on the regulator.

After the BUS has wake up the regulator, it can only be

switched off with a high level followed by a low level on

the EN pin.

Reset Programming on VTR

With the VTR pin the reset switch off levels and delay

time can be programmed.

The voltage on VCC influences the reset function.

VTR-Programming

The voltage on VTR input is read out if the voltage at this

pin is higher than V

RESEIN

. This value defines the reset

switch off voltage V

RES

. With the next oscillator cycle it

switch on the pull up current source if VTR=low or the

pull down current source if VTR=high. The sources are

active for one oscillator cycle. The level changes during

this procedures on VTR, which depends on the external

pull up or pull down resistors control the reset time t

Res

Temperature Limitation

If the junction temperature 150∫C < T

j

< 170∫C the over

temperture recognition will be active and the regulator

voltage and the BUS driver will be switched off. After T

j

fall below 140∫C the TH3122 will be initialized, independ-

ently of the voltage levels on EN and BUS.

The function of the TH3122 is possible between T

Amax

and the switch off temperature, but small parameter dif-

ferences can appear.

Low Voltage Detection V

S

Low voltage on V

S

is monitored on SENSE output.

If V

S

has reached the level of V

S

=6.8V then the SENSE

output

generates

low

level.

The

normal

operating range is V

S

> 7.8V and the SENSE output gen-

erates a high level.

Universal Comparator

The TH3122 consist a universal comparator for general

use. The positive input of this comparator is connected to

the pin SI. The input voltage range of SI is 0V...V

S.

The

input voltage is compared with a fixed reference voltage

at high or low level and the comparator output SO drives

a 5V digital signal.

VS

VCC

t

Res

V

RESEIN

t

rr

V

RES1/2

RESET

VTR-Mode

V

RES

t

Res

VTR = GND

V

RES

= V

RES1

= 3.15V

100ms

VTR = VCC

V

RES

= V

RES2

= 4.65V

100ms

VTR with R

50k

to GND

V

RES

= V

RES1

= 3.15V

15ms

VTR with R

50k

to VCC

V

RES

= V

RES2

= 4.65V

15ms