| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MIC2186 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

July 2002

1

MIC2186

MIC2186

Micrel

MIC2186

Low Voltage PWM Control IC

Final Information

General Description

Micrel's MIC2186 is a high efficiency boost PWM control IC.

With its wide input voltage range of 2.9V to 14V, the MIC2186

can be used to efficiently boost voltages in 1- or 2-cell Li Ion

battery powered applications, as well as to boost voltages in

fixed 3.3V, 5V, or 12V systems. Its powerful 1.6

output

driver allows the MIC2186 to supply large output currents with

the selection of proper external MOSFETs.

The MIC2186 can be configured to operate at 100kHz,

200kHz, or 400kHz. With it's fixed frequency PWM architec-

ture, and easily synchronized drive, the MIC2186 is ideal for

noise-sensitive telecommunications applications.

MIC2186 also features a low current shutdown mode of

0.5

µ

A and programmable undervoltage lockout. A manually

selectable SKIP Mode allows high efficiencies in light load

situations.

The MIC2186 is available in 16 pin SOIC and QSOP package

options with an operating range from ≠40

∞

C to 125

∞

C.

Typical Application

VINA

Si4404DY

(x2)

4.5m

2.2

µ

H

MBR2535CT

C

IN

120

µ

F

20V

C

OUT

150

µ

F(x2)

20V

EN/UVLO

HIDC

FREQ/2

VDD

COMP

VREF

SKIP

SYNC

SS

MIC2186

SGND

VINP

FB

V

OUT

= 12V

OUTN

CSH

V

IN

= 3.3V

PGND

3

12

9

14

6

16

7

5

11

2

8

4

10

15

13

1

60

65

70

75

80

85

90

95

0

0.5

1

1.5

2

2.5

3

EFFICIENCY (%)

OUTPUT CURRENT (A)

12V Output Efficiency

V

IN

= 3.3V

Adjustable Output Boost Converter

Features

∑ Input voltage range: 2.9V to 14V

∑ 1.6

output driver

∑ Oscillator frequency of 100kHz/200kHz/400kHz

∑ Frequency sync to 600kHz

∑ Front edge blanking

∑ PWM Current Mode Control

∑ Selectable light load SKIP mode

∑ 600

µ

A quiescent current (SKIP-Mode)

∑ 0.5

µ

A shutdown current

∑ Cycle-by-Cycle current limiting

∑ Frequency foldback protection

∑ Adjustable under-voltage lockout

∑ Precision 1.245V reference output

∑ 16 pin SOIC and QSOP package options

∑ Selectable 50% maximum duty cycle for flyback applica-

tions

Applications

∑ DC power distribution systems

∑ Wireless Modems

∑ ADSL line cards

∑ SLIC power supplies

∑ 1-and 2-cell Li Ion battery operated equipment

Micrel, Inc. ∑ 1849 Fortune Drive ∑ San Jose, CA 95131 ∑ USA ∑ tel + 1 (408) 944-0800 ∑ fax + 1 (408) 944-0970 ∑ http://www.micrel.com

Ordering Information

Part Number

Frequency

Voltage

Ambient Temp. Range

Package

MIC2186BM

100kHz/200kHz/400kHz

Adj

≠40

∞

C to +125

∞

C

16-lead SOP

MIC2186BQS

100kHz/200kHz/400kHz

Adj

≠40

∞

C to +125

∞

C

16-lead QSOP

MIC2186

Micrel

MIC2186

2

July 2002

Pin Description

Pin Number

Pin Name

Pin Function

1

VINA

Input voltage to control circuitry (2.9V to 14V).

2

SKIP

SKIP (Input): Regulator operates in PWM mode (no pulse skipping) when

pin is pulled low, and skip mode when raised to Vdd. There is no automatic

switching between PWM and skip mode available on this device.

3

SS

Soft start reduces the inrush current and delays and slows the output voltage

rise time. A 5

µ

A current source will charge the capacitor up to Vdd.

4

COMP

Compensation (Output): Internal error amplifier output. Connect to a

capacitor or series RC network to compensate the regulator's control loop.

5

SGND

Small signal ground: must be routed separately from other grounds to the (-)

terminal of Cout.

6

FB

Feedback Input - regulates FB to 1.245V.

7

EN/UVLO

Enable/Undervoltage Lockout (input): A low level on this pin will power down

the device, reducing the quiescent current to under 0.5

µ

A. This pin has two

separate thresholds, below 1.5V the output switching is disabled, and below

0.9V the device is forced into a complete micropower shutdown. The 1.5V

threshold functions as an accurate undervoltage lockout (UVLO) with 135mV

hysteresis.

8

VREF

The 1.245V reference is available on this pin. A 0.1

µ

F capacitor should be

connected form this pin to SGnd.

9

CSH

The (+) input to the current limit comparator. A built in offset of 100mV

between CSH and SGnd in conjunction with the current sense resistor sets

the current limit threshold level. This is also the (+) input to the current

amplifier.

10

VDD

3V internal linear-regulator output. Vdd is also the supply voltage bus for the

chip. Bypass to SGND with 1

µ

F. Maximum source current is 0.5mA.

11

SYNC

Frequency Synchronization (Input): Connect an external clock signal to

synchronize the oscillator. Leading edge of signal above 1.5V starts switch-

ing cycle. Connect to SGND if not used.

12

PGND

MOSFET driver power ground, connects to the bottom of the current sense

resistor and the (≠) terminal of C

IN

.

13

HIDC

High Duty Cycle. Sets duty cycle and frequency along with Freq/2. Logic

HIGH sets 85% maximum duty cycle. Logic LOW sets 50% maximum duty

cycle. See applications section for more information.

14

OUTN

High current drive for N channel MOSFET. Voltage swing is from ground to

V

IN

. R

ON

is typically 1.6

.

15

FREQ/2

Sets duty cycle and frequency along with HiDC. See applications section for

more information.

16

VINP

Power input voltage to the gate drive circuitry (2.9V to 14V). This pin is

normally connected to the output voltage.

Pin Configuration

1

VINA

SKIP

SS

COMP

SGND

FB

EN/UVLO

VREF

16 VINP

FREQ/2

OUTN

HIDC

PGND

SYNC

VDD

CSH

15

14

13

12

11

10

9

2

3

4

5

6

7

8

16-pin Narrow Body SOP (M)

16-pin QSOP (QS)

July 2002

3

MIC2186

MIC2186

Micrel

Electrical Characteristics

V

IN

A = 5V, V

IN

P = V

OUT

= 12V, SKIP = 0V, FREQ/2 = 0V, HiDC = 3V, V

CSH

= 0V, T

J

= 25

∞

C, unless otherwise specified. Bold values

indicate ≠40

∞

C < T

J

< +125

∞

C.

Parameter

Condition

Min

Typ

Max

Units

Regulation

Feedback Voltage Reference

(

±

1%)

1.233

1.245

1.258

V

(

±

2%)

1.220

1.270

V

3V

V

IN

A

9V; 0mV

CSH

75mV; (

±

3%)

1.208

1.245

1.282

V

Feedback Bias Current

50

nA

Output Voltage Line Regulation

3V

V

IN

A

9V

+0.08

% / V

Output Voltage Load Regulation

0mV

CSH

75mV

≠1.2

%

Input & V

DD

Supply

V

IN

A Input Current, PWM mode

V

SKIP

= 0V

0.7

mA

V

IN

P Input Current, PWM mode

V

SKIP

= 0V (excluding external MOSFET gate current)

2.8

mA

V

IN

A Input Current, SKIP mode

V

SKIP

= 5V

0.6

mA

Shutdown Quiescent Current

VEN/UVLO = 0V; (I

VINA

+ I

VINP

)

0.5

5

µ

A

Digital Supply Voltage (VDD)

I

L

= 0

2.82

3.0

3.18

V

Digital Supply Load Regulation

I

L

= 0 to 0.5mA

0.03

V

Undervoltage Lockout

V

DD

upper threshold (turn on threshold)

2.9

2.75

V

V

DD

lower threshold (turn off threshold)

2.65

V

Reference Output (V

REF

)

Reference Voltage

(

±

1.5%)

1.226

1.245

1.264

V

(

±

2.5%)

1.213

1.276

V

Reference Voltage Line

5V < VinA < 9V

2

mV

Regulation

Reference Voltage Load

0 < I

REF

< 100

µ

A

1

mV

Regulation

Absolute Maximum Ratings (Note 1)

Supply Voltage (V

IN

A, V

IN

P) ......................................... 15V

Digital Supply Voltage (V

DD

) ........................................... 7V

SKIP Pin Voltage (V

SKIP

) ................................. ≠0.3V to 7V

Max Duty Cycle Pin Voltage (V

HIDC

) ................ ≠0.3V to 7V

Frequency Divider Pin Voltage (V

FREQ/2

) ........ ≠0.3V to 7V

Sync Pin Voltage (V

SYNC

) ................................ ≠0.3V to 7V

Comp Pin Voltage (V

COMP

) .............................. ≠0.3V to 3V

Feedback Pin Voltage (V

FB

) ............................ ≠0.3V to 3V

Enable Pin Voltage (V

EN/UVLO

) ...................... ≠0.3V to 15V

Current Sense Voltage (V

CSH

) ......................... ≠0.3V to 1V

Power Dissipation (P

D

)

16 lead SOP .............................. 400mW @ T

A

= 85

∞

C

16 lead QSOP ........................... 245mW @ T

A

= 85

∞

C

Ambient Storage Temp ............................ ≠65

∞

C to +150

∞

C

ESD Rating (Note 3)

Operating Ratings (Note 2)

Supply Voltage (V

IN

A, V

IN

P) ........................ +2.9V to +14V

Operating Ambient Temperature ......... ≠40

∞

C

T

A

+85

∞

C

Junction Temperature ....................... ≠40

∞

C

T

J

+125

∞

C

PackageThermal Resistance

JA

16-lead SOP ............................................... 100

∞

C/W

JA

16-lead QSOP ............................................. 163

∞

C/W

MIC2186

Micrel

MIC2186

4

July 2002

Parameter

Condition

Min

Typ

Max

Units

Enable/UVLO

Enable Input Threshold

0.6

0.9

1.2

V

UVLO Threshold

1.4

1.5

1.6

V

UVLO Hysteresis

140

mV

Enable Input Current

V

EN/UVLO

= 5V

0.2

5

µ

A

Soft Start

Soft Start Current

5

µ

A

Current Limit

Current Limit Threshold Voltage

(Voltage on CSH to trip current limit)

80

100

120

mV

Error Amplifier

Error Amplifier Gain

20

V/V

Current Amplifier

Current Amplifier Gain

3.7

V/V

SKIP Input

SKIP Threshold

0.6

1.4

2.2

V

SKIP Input Current

V

SKIP

= 3V

0.1

5

µ

A

HIDC Input

HIDC Threshold

0.6

1.4

2.2

V

Oscillator Section

Oscillator Frequency (f

O

)

360

400

440

kHz

Maximum Duty Cycle

V

FB

= 1.0V, V

HIDC

= 3V

85

%

V

FB

= 1.0V, V

HIDC

= 0V

50

Minimum On Time

V

FB

= 1.5V, V

HiDC

= 3V

180

ns

FREQ/2 Frequency (f

O

)

V

HiDC

= 3V, V

FREQ/2

= 3V

170

200

230

kHz

Frequency Foldback Threshold

Measured on FB

0.3

V

Frequency Foldback Frequency

V

HiDC

= 3V, V

FREQ/2

= 0V

90

kHz

SYNC Threshold Level

0.6

1.4

2.2

V

SYNC Input Current

0.1

5

µ

A

SYNC Minimum Pulse Width

200

ns

SYNC Capture Range

Note 4

f

O

+ 15 %

600

kHz

Gate Drivers

Rise/Fall Time

C

L

= 3300pF

50

ns

Output Driver Impedance

source; V

IN

P = 12V

1.8

4

sink; V

IN

P = 12V

1.6

3.5

source; V

IN

P =5V

2.6

sink; V

IN

P = 5V

2.4

Note 1.

Absolute maximum ratings indicate limits beyond which damage to the component may occur. Electrical specifications do not apply when

operating the device outside of its operating ratings. The maximum allowable power dissipation is a function of the maximum junction

temperature, T

J(max)

, the junction-to-ambient thermal resistance,

JA

, and the ambient temperature, T

A

.

Note 2.

The device is not guaranteed to function outside its operating rating.

Note 3.

Devices are ESD sensitive. Handling precautions recommended.

Note 4.

See application information for limitations on maximum operating frequency.

July 2002

5

MIC2186

MIC2186

Micrel

Typical Characteristics

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

-40 -20

0

20

40

60

80 100

I

Q(SKIP)

(mA)

TEMPERATURE (

∞

C)

Quiescent Current vs.

Temperature (SKIP Mode)

V

IN

A = 5V

DC

V

IN

P = 12V

DC

I

Q

= I

QVINA

+I

QVINP

3.35

3.4

3.45

3.5

3.55

3.6

3.65

-60 -40 -20 0

20 40 60 80 100

I

Q(PWM)

(mA)

TEMPERATURE (

∞

C)

Quiescent Current vs.

Temperature (PWM Mode)

V

IN

A = 5V

DC

V

IN

P = 12V

DC

I

Q

= I

QVINA

+I

QVINP

0

0.5

1

1.5

2

2.5

3

3.5

4

0

2

4

6

8

10 12 14 16

I

Q

(mA)

INPUT VOLTAGE (V

INA

)

Quiescent Current vs.

Input Voltage(PWM Mode)

400kHz

200kHz

100kHz

V

IN

P =12V

DC

I

Q

= I

QVINA

+I

QVINP

0

0.5

1

1.5

2

2.5

3

3.5

4

0

2

4

6

8

10 12 14 16

I

Q(PWM)

(mA)

INPUT VOLTAGE (V

INA

)

Quiescent Current vs.

Input Voltage (PWM Mode)

V

IN

P = 5V

V

IN

P = 9V

V

IN

P = 12V

I

Q

= I

QVINA

+ I

QVINP

f

S

= 400kHz

0.5

0.55

0.6

0.65

0.7

0.75

0.8

0.85

0.9

0

2

4

6

8

10 12 14 16

I

Q

(mA)

INPUT VOLTAGE (V

INA

)

Quiescent Current vs.

Input Voltage (SKIP Mode)

V

IN

P = 5V

DC

V

IN

P = 9V

DC

V

IN

P = 12V

DC

1.244

1.2442

1.2444

1.2446

1.2448

1.245

1.2452

0

2

4

6

8

10 12 14 16

REFERENCE VOLTAGE (V)

INPUT VOLTAGE (V

INA

)

Reference Voltage

vs. Input Voltage

V

IN

P = 12V

DC

1.2443

1.2444

1.2445

1.2446

1.2447

1.2448

1.2449

1.245

1.2451

0

20

40

60

80

100 120

REFERENCE VOLTAGE (V)

REFERENCE CURRENT (

µ

A)

Reference Voltage

vs. Reference Current

V

IN

P = 12V

DC

V

IN

A = 5V

DC

1.2436

1.2438

1.2440

1.2442

1.2444

1.2446

1.2448

1.2450

1.2452

1.2454

-40 -20

0

20

40

60

80 100

REFERENCE VOLTAGE (V)

TEMPERATURE (

∞

C)

Reference Voltage

vs. Temperature

V

IN

P = 12V

DC

V

IN

A = 5V

DC

2.80

2.85

2.90

2.95

3.00

3.05

3.10

0

2

4

6

8

10

12

14

VDD (V)

INPUT VOLTAGE (V

INA

)

VDD vs.

Input Voltage

V

IN

P = 12V

DC

2.995

3.000

3.005

3.010

3.015

3.020

3.025

3.030

3.035

0

0.2

0.4

0.6

0.8

1

1.2

VDD (V)

IVDD (mA)

VDD vs.

Load Current

V

IN

P = 12V

DC

V

IN

A = 5V

DC

2.94

2.96

2.98

3.00

3.02

3.04

3.06

3.08

-60 -40 -20 0

20 40 60 80 100

VDD (V)

TEMPERATURE (

∞

C)

VDD vs.

Temperature

V

IN

P = 12V

DC

V

IN

A = 5V

DC

0

50

100

150

200

250

300

0

2

4

6

8

10

12

14

IENABLE (

µ

A)

VENABLE (V)

Ienable vs.

Venable

V

IN

P = 12V

DC

V

IN

A = 5V

DC

85

∞

C

≠40

∞

C

20

∞

C

MIC2186

Micrel

MIC2186

6

July 2002

392

394

396

398

400

402

404

406

0

2

4

6

8

10

12

14

OSCILLATOR FREQUENCY (kHz)

INPUT VOLTAGE (V

INA

)

Oscillator Frequency

vs. Input Voltage

V

IN

P = 12V

DC

365

370

375

380

385

390

395

400

405

-50 -30 -10 10

30

50

70

90

OSCILLATOR FREQUENCY (kHz)

TEMPERATURE (

∞

C)

Oscillator Frequency

vs. Temperature

V

IN

P = 12V

DC

V

IN

A = 5V

DC

4.25

4.30

4.35

4.40

4.45

4.50

4.55

4.60

4.65

4.70

4.75

-50 -30 -10 10

30

50

70

90

SOFT START CURRENT (

µ

A)

TEMPERATURE (

∞

C)

Soft Start

vs. Temperature

V

IN

P = 12V

DC

V

IN

A = 5V

DC

0

10

20

30

40

50

60

70

80

90

100

0

2

4

6

8

10 12 14 16

OVERCURRENT THRESHOLD (mV)

VINA (V)

Overcurrent Threshold

vs. VINA

V

IN

P = 12V

DC

July 2002

7

MIC2186

MIC2186

Micrel

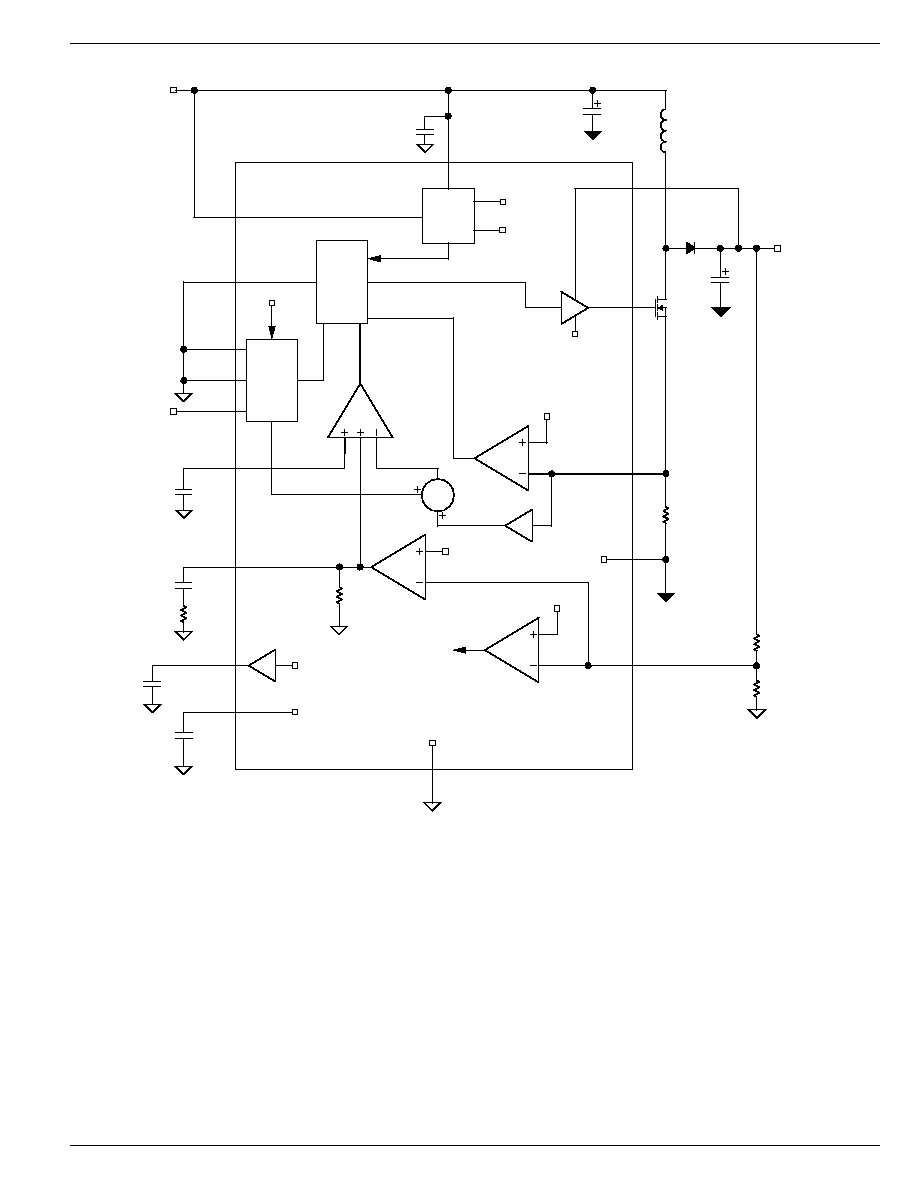

Functional Diagram

Osc

Error

Amplifier

0.1V

P

GND

D1

L1

C

IN

fs/4

V

IN

Control

Bias

PWM

Comparator

V

REF

V

REF

V

DD

S

GND

Overcurrent

Comparator

Frequency

Foldback

fs/4

Reset

Overcurrent Reset

Corrective

Ramp

On

Gain = 3.7

P

GND

12

CSH

9

OutN

14

V

IN

P

V

IN

A

16

1

V

fb

5

S

GND

6

V

DD

10

V

REF

8

COMP

4

Soft Start

3

HiDC

V

DD

13

Sync

11

Freq/2

15

SKIP

2

EN/UVLO

7

gm = 0.0002

Gain = 20

0.3V

100k

R2

R1

R

SENSE

C

OUT

V

OUT

P

GND

V

REF

C

DECOUP

V

DD

Figure 1. MIC2186 PWM Block Diagram

Functional Description

The MIC2186 is a BiCMOS, switched mode multi-topology

controller. It will operate most low side drive topologies

including boost, SEPIC, flyback and forward. The controller

has a low impedance driver capable of switching large N-

channel MOSFETs. It features multiple frequency and duty

cycle settings. Current mode control is used to achieve

superior transient line and load regulation. An internal correc-

tive ramp provides slope compensation for stable operation

above a 50% duty cycle. The controller is optimized for high

efficiency, high performance DC-DC converter applications.

Figure 1 shows a block diagram of the MIC2186 configured

as a PWM boost converter.

The switching cycle starts when OutN goes high and turns on

the low side, N-channel MOSFET, Q1. The Vgs of the

MOSFET is equal to V

IN

P. This forces current to ramp up in

the inductor. The inductor current flows through the current

sense resistor, Rsense. The voltage across the resistor is

amplified and combined with an internal ramp for stability.

This signal is compared with the error voltage signal from the

error amplifier. When the current signal equals the error

voltage signal, the low side MOSFET is turned off. The

inductor current then flows through the diode, D1, to the

output. The MOSFET remains off until the beginning of the

next switching cycle.

MIC2186

Micrel

MIC2186

8

July 2002

Control Loop

PWM and SKIP modes of operation

The MIC2186 can operate in either PWM (pulse width modu-

lated) or SKIP mode. The efficiency of the boost converter

can be improved at lower output loads by manually selecting

the skip mode of operation. The potential disadvantage of

skip mode is the variable switching frequency that accompa-

nies this mode of operation. The occurrence of switching

pulses depends on component values as well as line and load

conditions. PWM mode is the best choice of operation at

higher output loads. PWM mode has the advantages of lower

output ripple voltage and higher efficiencies at higher output

loads. Pulling the SKIP pin (pin 3) low will force the controller

to operate in PWM mode for all load conditions. Pulling the

SKIP pin high will force the controller to operate in SKIP

mode.

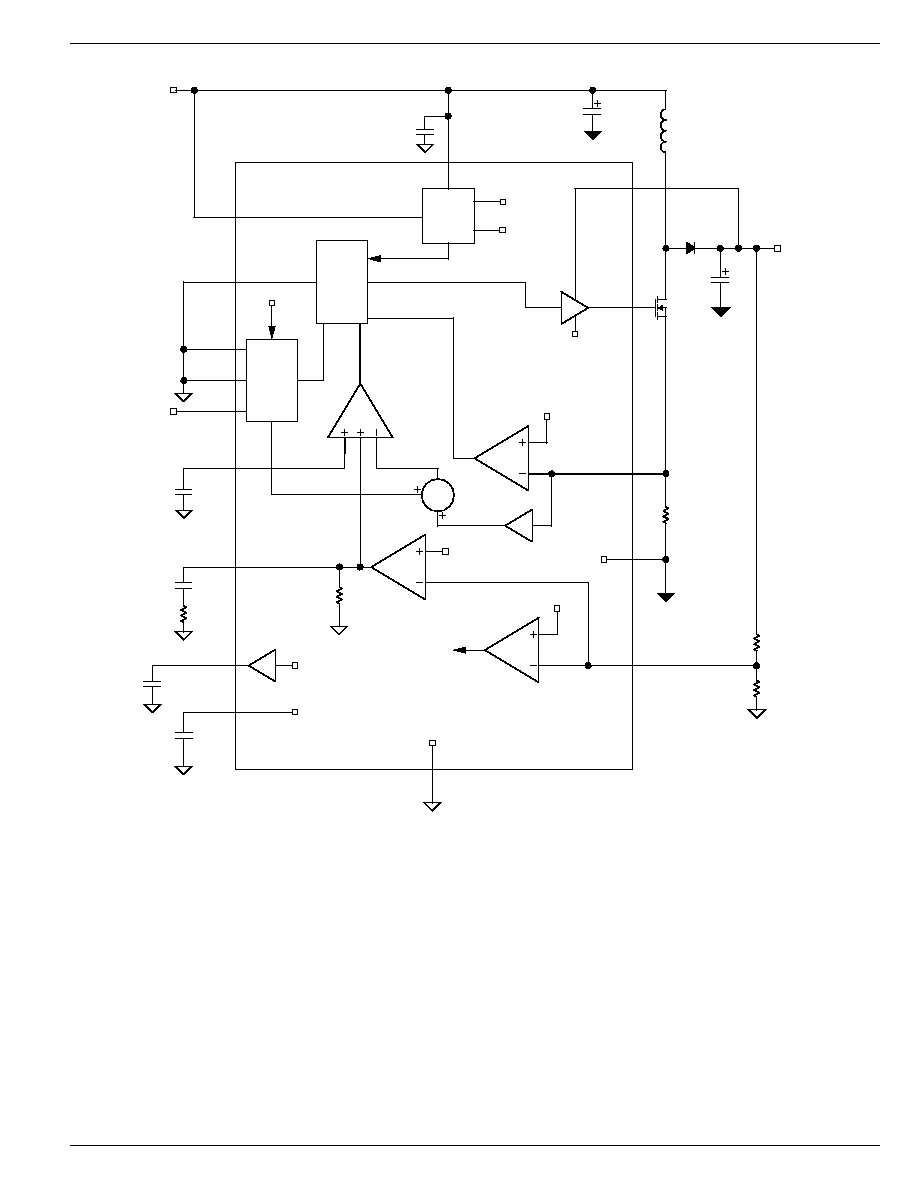

The description of the MIC2186 controller is broken

down into 6 basic functions.

∑ Control Loop

∑ PWM Operation

∑ SKIP Mode Operation

∑ Current Limit

∑ MOSFET gate drive

∑ Reference, enable & UVLO

∑ Oscillator & Sync

∑ Soft start

Osc

P

GND

D1

Q1

L1

V

IN

Control

Bias

V

REF

V

DD

S

GND

Skip Current

Limit Comparator

Hysteresis

Comparator

±

1%

F/2=H 2us off-time

F/2=L 1us off-time

Current

Reset

On

P

GND

12

CSH

9

OutN

14

V

IN

P

V

IN

A

16

1

V

fb

5

S

GND

6

V

DD

10

V

REF

8

COMP

4

Soft Start

3

HiDC

13

Sync

11

Freq/2

15

SKIP

2

EN/UVLO

7

50mV

V

DD

V

REF

1.245V

R2

R1

R

SENSE

C

OUT

V

OUT

P

GND

V

REF

C

DECOUP

C

IN

V

DD

Figure 2. MIC2186 SKIP Mode Block Diagram

July 2002

9

MIC2186

MIC2186

Micrel

SKIP Mode Operation

This control method is used to improve efficiency at low

output loads. A block diagram of the MIC2186 SKIP mode is

shown in Figure 2. The power drawn by the MIC2186 control

IC is (I

VIN

A ∑ V

IN

A )+ (I

VIN

P ∑ V

IN

P). The power dissipated by

the IC can be a significant portion of the total output power

during periods of low output current, which lowers the effi-

ciency of the power supply. In SKIP mode the MIC2186

lowers the IC supply current by turning off portions of the

control and drive circuitry when the IC is not switching. The

disadvantage of this method is greater output ripple and

variable switching frequency. The soft start, HiDC and Sync

pins have no effect when operating in SKIP mode.

In SKIP mode, switching starts when the feedback voltage

drops below the lower threshold level of the hysteresis

comparator. The OutN pin goes high, turning on the N-

channel MOSFET, Q1. Current ramps up in the inductor until

either the current limit comparator or the hysteretic voltage

comparator turns off Q1's gate drive. If the feedback voltage

exceeds the upper hysteretic threshold, Q1's gate drive is

terminated. However, if the voltage at the CSH pin exceeds

the SKIP mode current limit threshold, it terminates the gate

drive for that switching cycle. The gate drive remains off for

a constant period at the end of each switching cycle. This off

time period is typically 1

µ

s when the F/2 pin is low and 2

µ

s

when the F/2 pin is high. Figure 3 shows some typical SKIP

mode switching waveforms.

I

IND

@5A/div

MOSFET gate

drive @ 10V/div

Switch Node Voltage

(MOSFET Drain)

@10V/div

VOUT Ripple Voltage

@100mV/div

V

IN

= 3V

V

O

= 9V

I

O

= 0.6A

SKIP Mode Waveforms

TIME (10

µ

s/div)

Figure 3. SKIP Mode Waveform

The SKIP mode current threshold limits the peak inductor

current per cycle. Depending on the input, output and circuit

parameters, many switching cycles can occur before the

feedback voltage exceeds the upper hysteretic threshold.

Once the voltage on the feedback pin exceeds the upper

hysteretic threshold the gate drive is disabled. The output

load discharges the output capacitance causing Vout to

decrease until the feedback voltage drops below the lower

threshold voltage limit. The switching converter then turns the

gate drive back on. While the gate drive is disabled, the

MIC2186 draws less IC supply current then while it is switch-

ing, thereby improving efficiency at low output loads. Figure

4 shows the efficiency improvement at low output loads when

SKIP mode is selected.

0

10

20

30

40

50

60

70

80

0

0.05

0.1

0.15

0.2

0.25

EFFICIENCY (%)

INPUT CURRENT (A)

Low Current

Efficiency

SKIP Mode

PWM Mode

Figure 4.

The maximum peak inductor current depends on the skip

current limit threshold and the value of the current sense

resistor, Rsense. For a typical 50mV current limit threshold in

SKIP Mode, the peak inductor current is:

I

50mV

R

INDUCTOR_pk

SENSE

=

The maximum output current is SKIP mode depends on the

input conditions, output conditions and circuit component

values. Assuming a discontinuous mode where the inductor

current starts from zero at each cycle, the maximum output

current is calculated below:

I

2.5 10

L

fs

2 R

V

V

O(max)

3

SENSE

2

O

IN

=

◊

◊ ◊

◊

◊

- ◊

(

)

-

where:

Iomax is the maximum output current

Vo is the output voltage

Vin is the input voltage

L is the value of the boost inductor

fs is the switching frequency

is the efficiency of the boost converter

Rsense it the value of the current sense resistor

2.5∑10

-3

is a constant based on the SKIP mode

current threshold (50mV)

2

PWM Operation

Figure 5 shows typical waveforms for PWM mode of opera-

tion. The gate drive signal turns on the external MOSFET

which allows the inductor current to ramp up. When the

MOSFET turns off, the inductor forces the MOSFET drain

voltage to rise until the boost diode turns on and the voltage

is clamped at approximately the output voltage.

MIC2186

Micrel

MIC2186

10

July 2002

Conditions:

V

IN

= 3V

V

O

= 9V

I

O

= 0.6A

MOSFET gate

drive @ 10V/div

Switch Node Voltage

(MOSFET Drain)

@10V/div

VOUT Ripple Voltage

@50mV/div

Inductor Current @

1A/div

PWM Mode Waveforms

TIME (1

µ

s/div)

Figure 5 - PWM mode waveforms

The MIC2186 uses current mode control to improve output

regulation and simplify compensation of the control loop.

Current mode control senses both the output voltage (outer

loop) and the inductor current (inner loop). It uses the inductor

current and output voltage to determine the duty cycle (D) of

the buck converter. Sampling the inductor current effectively

removes the inductor from the control loop, which simplifies

compensation. A simplified current mode control diagram is

shown in Figure 6.

I_inductor

T

ON

T

PER

V

COMP

I_inductor

I_inductor

Gate Driver

I_inductor

Voltage

Divider

V

REF

V

IN

Gate Drive at OutN

Figure 6: PWM Control Loop

A block diagram of the MIC2186 PWM current mode control

loop is shown in Figure 1. The inductor current is sensed by

measuring the voltage across a resistor, Rsense. The current

sense amplifier buffers and amplifies this signal. A ramp is

added to this signal to provide slope compensation, which is

required in current mode control to prevent unstable opera-

tion at duty cycles greater than 50%.

A transconductance amplifier is used as an error amplifier,

which compares an attenuated output voltage with a refer-

ence voltage. The output of the error amplifier is compared to

the current sense waveform in the PWM block. When the

current signal rises above the error voltage, the comparator

turns off the low side drive. The error signal is brought out to

the COMP pin (pin 4) to provide access to the output of the

error amplifier. This allows the use of external components to

stabilize the voltage loop.

Current Sensing and Overcurrent Protection

The inductor current is sensed during the switch on time by

a current sense resistor located between the source of the

MOSFET and ground (Rsense in Figure 1). Exceeding the

current limit threshold will immediately terminate the gate

drive of the N-channel MOSFET, Q1. This forces the Q1 to

operate at a reduced duty cycle, which lowers the output

voltage. In a boost converter, the overcurrent limit will not

protect the power supply or load during a severe

overcurrent condition or short circuit condition. If the

output is short-circuited to ground, current will flow from the

input, through the inductor and output diode to ground. Only

the impedance of the source and components limits the

current.

The mode of operation (continuous or discontinuous), the

minimum input voltage, maximum output power and the

minimum value of the current limit threshold determine the

value of the current sense resistor. Discontinuous mode is

where all the energy in the inductor is delivered to the output

at each switching cycle. Continuous mode of operation

occurs when current always flows in the inductor, during both

the low-side MOSFET on and off times. The equations below

will help to determine the current sense resistor value for

each operating mode.

The critical value of output current in a boost converter is

calculated below. The operating mode is discontinuous if the

output current is below this value and is continuous if above

this value.

I

V

V

V

2

fs L

V

CRIT

IN

2

O

IN

O

2

=

◊

-

(

)

◊

◊ ◊ ◊

where:

is the efficiency of the boost converter

Vin is the minimum input voltage

L is the value of the boost inductor

Fs is the switching frequency

Vo is the output voltage

Maximum Peak Current in Discontinuous Mode:

The peak inductor current is:

I

2 I

V

V

L

fs

IND(pk)

O

O

IN

=

◊

◊

- ◊

(

)

◊

where:

Io is the maximum output current

Vo is the output voltage

Vin is the minimum input voltage

L is the value of the boost inductor

fs is the switching frequency

is the efficiency of the boost converter

The maximum value of current sense resistor is:

July 2002

11

MIC2186

MIC2186

Micrel

R

V

I

SENSE

SENSE

IND(pk)

=

where:

Vsense is the minimum current sense threshold

of the CSH pin

Maximum Peak Current in Continuous Mode:

The peak inductor current is equal to the average inductor

current plus one half of the peak to peak inductor current.

The peak inductor current is:

I

I

1

2

I

I

V

I

V

V

V

V

2

V

fs L

IND(pk)

IND(ave)

IND(pp)

IND(pk)

O

O

IN

L

O

IN

O

=

+ ◊

=

◊

◊

+

◊

-

◊

(

)

◊

◊ ◊

where:

Io is the maximum output current

Vo is the output voltage

Vin is the minimum input voltage

L is the value of the boost inductor

fs is the switching frequency

is the efficiency of the boost converter

VL is the voltage across the inductor

VL may be approximated as Vin for higher input voltage.

However, the voltage drop across the inductor winding resis-

tance and low side MOSFET on-resistance must be ac-

counted for at the lower input voltages that the MIC2186

operates at.

V

V

V

I

V

R

R

L

IN

O

O

IN

WINDING

DSON

=

-

◊

◊

◊

+

(

)

where:

Rwinding is the winding resistance of the inductor

Rdson is the on resistance of the low side switching

MOSFET

The maximum value of current sense resistor is:

R

V

I

SENSE

SENSE

IND(pk)

=

where:

V

SENSE

is the minimum current sense threshold

of the CSH pin

The current sense pin, CSH, is noise sensitive due to the low

signal level. The current sense voltage measurement is

referenced to the signal ground pin of the MIC2186. The

current sense resistor ground should be located close to the

IC ground. Make sure there are no high currents flowing in this

trace. The PCB trace between the high side of the current

sense resistor and the CHS pin should also be short and

routed close to the ground connection. The input to the

internal current sense amplifier has a 30nS dead time at the

beginning of each switching cycle. This dead time prevents

leading edge current spikes from prematurely terminating the

switching cycle. A small RC filter between the current sense

pin and current sense resistor may help to attenuate larger

switching spikes or high frequency switching noise. Adding

the filter slows down the current sense signal, which has the

effect of slightly raising the overcurrent limit threshold.

MOSFET Gate Drive

The MIC2186 converter drives a low side N-channel MOSFET.

The driver for the OutN pin has a 1.6

typical source and sink

impedance. The VinP pin is the supply pin for the gate drive

circuit. It typically connected to the output. The maximum

supply voltage to the VinP pin is 14V. If the output voltage is

greater than 14V or if it is desired to drive the MOSFET with

a voltage less than Vout, the VinP pin can be connected to the

input or to an separate supply voltage.

MOSFET Selection

In a boost converter, the Vds of the MOSFET is approxi-

mately equal to the output voltage. The maximum Vds rating

of the MOSFET must be high enough to allow for ringing and

spikes in addition to the output voltage.

The VinP pin supplies the N-channel gate drive voltage. The

Vgs threshold voltage of the N-channel MOSFET must be low

enough to operate at the minimum VinP voltage to guarantee

the boost converter will start up.

The maximum amout of MOSFET gate charge that can be

driven is limited by the power dissipation in the MIC2186. The

power dissipated by the gate drive circuitry is calculated

below:

P_gate_drive=Q_gate * VinP * fs

where:

Q_gate is the total gate charge of the external

MOSFET

The graph in Figure 7 shows the total gate charge which can

be driven by the MIC2186 over the input voltage range, for

different values of switching frequency. Higher gate charge

will slow down the turn-on and turn-off times of the MOSFET,

which increases switching losses.

0

20

40

60

80

100

120

140

160

180

200

220

0

2

4

6

8

10

12

14

MAXIMUM GATE CHARGE (nC)

V

IN

P (V)

Power Dissipation

vs. Frequency

200kHz

100kHz

400kHz

600kHz

500kHz

Figure 7 - MIC2186 freq vs pdiss

External Schottky Diode

In a boost converter topology, the boost diode, D1 must be

rated to handle the peak and average current. The average

current through the diode is equal to the average output

current of the boost converter. The peak current is calculated

in the current limit section of this specification.

MIC2186

Micrel

MIC2186

12

July 2002

The reverse voltage requirement of the diode is:

For the MIC2186, Schottky diodes are recommended when

they can be used. They have a lower forward voltage drop

than ultra-fast rectifier diodes, which lowers power dissipa-

tion and improves efficiency. They also do not have a recov-

ery time mechanism, which results in less ringing and noise

when the diode turns off. If the output voltage of the circuit

prevents the use of a Schottky diode, then only ultra-fast

recovery diodes should be used. Slower diodes will dissipate

more power in both the MOSFET and the diode. The will also

cause excessive ringing and noise when the diode turns off.

Reference, Enable and UVLO Circuits

The output drivers are enabled when the following conditions

are satisfied:

∑ The Vdd voltage (pin 10) is greater than its

undervoltage threshold.

∑ The voltage on the enable pin is greater than the

enable UVLO threshold.

The internal bias circuitry generates a 1.245V bandgap

reference for the voltage error amplifier and a 3V Vdd voltage

for the internal supply bus. The reference voltage in the

MIC2186 is buffered and brought out to pin 8. The Vref pin

must be bypassed to GND (pin 4) with a 0.1uf capacitor. The

Vdd pin must be decoupled to ground with a 1uf ceramic

capacitor.

The enable pin (pin 7) has two threshold levels, allowing the

MIC2186 to shut down in a micro-current mode, or turn off

output switching in standby mode. Below 0.9V, the device is

forced into a micro-power shutdown. If the enable pin is

between 0.9V and 1.5V the output gate drive is disabled but

the internal circuitry is powered on and the soft start pin

voltage is forced low. There is typically 135mV of hysteresis

below the 1.5V threshold to insure the part does not oscillate

on and off due to ripple voltage on the input. Raising the

enable voltage above the UVLO threshold of 1.5V enables

the output drivers and allows the soft start capacitor to

charge. The enable pin may be pulled up to VinA.

Oscillator & Sync

The internal oscillator is self-contained and requires no

external components. The HiDC and f/2 pins allow the user

to select from three different switching frequencies and two

maximum duty cycles. The chart in Table 1 shows the four

combinations that can be programmed along with the typical

minimum and maximum duty cycles.

n

i

p

2

/

F

l

e

v

e

L

C

D

i

H

l

e

v

e

L

g

n

i

h

c

t

i

w

S

y

c

n

e

u

q

e

r

F

m

u

m

i

x

a

M

e

l

c

y

C

y

t

u

D

l

a

c

i

p

y

T

m

u

m

i

n

i

M

e

l

c

y

C

y

t

u

D

T

F

F

O

n

i

e

d

o

M

p

i

k

S

0

1

z

H

k

0

0

4

%

5

8

%

7

s

µ

1

1

1

z

H

k

0

0

2

%

5

8

%

6

s

µ

2

0

0

z

H

k

0

0

2

%

0

5

%

4

s

µ

1

1

0

z

H

k

0

0

1

%

0

5

%

3

s

µ

2

Table 1

Minimum duty cycle becomes important in a boost converter

as the input voltage approaches the output voltage. At lower

duty cycles, the input voltage can be closer to the output

voltage without the output rising out of regulation.

A frequency foldback mode is enabled if the voltage on the

feedback pin (pin 6) is less than 0.3V. In frequency foldback

the oscillator frequency is reduced by approximately a factor

of 4. For the 400kHz setting, the oscillator runs at 100khz in

frequency foldback. For a 200kHz setting the oscillator runs

at approximately 50kHz and for a 100kHz setting, the oscil-

lator runs at approximately 25kHz.

The SYNC input (pin 11) allows the MIC2186 to synchronize

with an external CMOS or TTL clock signal. Depending on the

setting of the HiDC pin,the output frequency is either equal to

or 1/2 of the sync input frequency. If the HiDC level is low, the

output switching frequency is half the sync frequency. If the

HiDC level is high, the output switching frequency is equal to

the sync frequency.

The rising edge of the sync signal generates a reset signal in

the oscillator, which turns off the high-side gate drive output.

The low-side drive is turned on, restarting the switching cycle.

The sync signal is inhibited when the controller operates in

skip mode or frequency foldback. The sync signal frequency

must be greater than the maximum specified free running

frequency of the MIC2186. If the synchronizing frequency is

lower, double pulsing of the gate drive outputs will occur.

When not used, the sync pin must be connected to ground.

Table 2 shows the minimum recommended sync frequencies

for the different combinations of f/2 and HiDC inputs.

Figure 8a shows the timing between the external sync signal

(trace 2) and the low-side drive (trace 1) for a high level on the

HiDC pin. Figure 8b shows the timing between the external

sync signal (trace 2) and the low-side drive (trace 1) for a low

level on the HiDC pin. The sync frequency is twice the output

switching frequency.

n

i

p

2

/

F

l

e

v

e

L

C

D

i

H

l

e

v

e

L

g

n

i

t

a

l

l

i

c

s

O

f

l

e

S

y

c

n

e

u

q

e

r

F

m

u

m

i

n

i

M

d

e

d

n

e

m

m

o

c

e

R

y

c

n

e

u

q

e

r

F

c

n

y

S

y

c

n

e

u

q

e

r

F

t

u

p

n

I

c

n

y

S

f

S

y

c

n

e

u

q

e

r

f

g

n

i

h

c

t

i

w

s

t

u

p

t

u

o

=

f

C

N

Y

S

y

c

n

e

u

q

e

r

f

t

u

p

n

i

c

n

y

s

=

0

1

z

H

k

0

0

4

z

H

k

0

8

4

f

S

f

=

C

N

Y

S

1

1

z

H

k

0

0

2

z

H

k

0

5

2

f

S

f

=

C

N

Y

S

0

0

z

H

k

0

0

2

z

H

k

0

8

4

f

S

=

1

/

2

f

C

N

Y

S

1

0

z

H

k

0

0

1

z

H

k

0

5

2

f

S

=

1

/

2

f

C

N

Y

S

Table 2

July 2002

13

MIC2186

MIC2186

Micrel

MIC2186 Sync

Conditions:

HiDC = HIGH

F/2 = LOW

Gat Drive Output

(Pin 14)

Sync Input

(Pin 11)

Figure 8a.

MIC2186 Sync

Conditions:

HiDC = LOW

F/2 = LOW

Gat Drive Output

(Pin 14)

Sync Input

(Pin 11)

Figure 8b.

The maximum recommended output switching frequency is

600kHz. Synchronizing to higher frequencies may be pos-

sible, however there are some concerns. As the switching

frequency is increased, the switching period decreases. The

minimum on-time in the MIC2186 becomes a greater part of

the total switching period. This may prevent proper operation

as Vin approaches Vout and may also minimize the effective-

ness of the current limit circuitry. The maximum duty cycle

decreases as the sync frequency is increased. Figure 9

shows the relationship between the minimum/maximum duty

cycle and frequency.

40

45

50

55

60

65

70

75

80

85

250 300 350 400 450 500 550 600

MAXIMUM DUTY CYCLE (%)

SYNC FREQUENCY (kHz)

Max. Duty Cycle

vs. Frequency

HiDC=L

F/2=H

HiDC=L

F/2=L

HiDC=H

F/2=L

HiDC=H

F/2=H

Figure 9.

Soft start

Soft start reduces the power supply input surge current at

start up by limiting the output voltage risetime. Input surge

current occurs when the boost converter charges up the

output capacitance. Slowing the output risetime lowers the

input surge current. Soft start may also be used for power

supply sequencing. The soft start cannot control the initial

surge in current in a boost converter when Vin is applied. This

surge current is caused by the output capacitance charging

up to the input voltage. The current flows from the input

through the inductor and output diode to the output capaci-

tors.

The soft start voltage is applied directly to the PWM compara-

tor. A 5uA internal current source is used to charge up the soft

start capacitor. Either of 2 UVLO conditions will pull the soft

start capacitor low.

* When the Vdd voltage drops below its UVLO

threshold

* When the enable pin drops below its 1.5V UVLO

threshold

The part switches at a low duty cycle when the soft start pin

voltage zero. As the soft start voltage rises from 0V to 0.7V,

the duty cycle increases from the minimum duty cycle to the

operating duty cycle. The oscillator runs at the foldback

frequency until the feedback voltage rises above 0.3V. In a

boost converter the output voltage is equal to the input

voltage before the MIC2186 starts switching. If the ratio of

Vout/Vin is low, the voltage on the feedback pin will already

be greater than 0.3V and the converter begin switching at the

selected operating frequency.

The risetime of the output is dependent on the soft start

capacitor, output capacitance, input and output voltage and

load current. The scope photo in Figure 10 show the output

voltage and the soft start pin voltage at startup. The output

voltage is initially at the input voltage less a diode drop. After

the converter is enabled the output slowly rises due to the

minimum duty cycle of the controller. As the soft start voltage

increases, the output voltage rises in a controlled fashion until

the output voltage reaches the regulated value.

Soft Start

0V

Figure 10.

Voltage Setting Components

The MIC2186 requires two resistors to set the output voltage

as shown in figure 11

MIC2186

Micrel

MIC2186

14

July 2002

Pin

6

Voltage

Amplifier

V

REF

1.245V

MIC2186

R1

R2

Figure 11.

The output voltage is determined by the equation below.

V

V

1

R1

R2

O

REF

=

◊ +

Where: Vref for the MIC2186 is nominally 1.245V. Lower

values of resistance are preferred to prevent noise from

apprearing on the Vfb pin. A typically recommended value for

R1 is 10K.

Decoupling Capacitor Selection

The 1uf decoupling capacitor is used to stabilize the internal

regulator and minimize noise on the Vdd pin. Placement of

this capacitor is critical to the proper operation of the MIC2186.

It must be next to the Vdd and signal ground pins and routed

with wide etch. The capacitor should be a good quality

ceramic. Incorrect placement of the Vdd decoupling capaci-

tor will cause jitter and/or oscillations in the switching wave-

form as well as variations in the overcurrent limit.

A minimum 0.1uf ceramic capacitor is required to decouple

the Vin. The capacitor should be placed near the IC and

connected directly between pins 10 (Vcc) and 5 (SGND). A

0.1uf capacitor is required to decouple Vref. It should be

located near the Vref pin.

Efficiency calculation and considerations

Efficiency is the ratio of output power to input power. The

difference is dissipated as heat in the boost converter. The

significant contributors at light output loads are:

* The VinA pin supply current.

* The VinP pin supply current which includes the

current required to switch the external

MOSFETs

* Core losses in the inductor

To maximize efficiency at light loads:

* Use a low gate charge MOSFET or use the

smallest MOSFET, which is still adequate for the

maximum output current.

* Allow the MIC2186 to run in skip mode at lower

currents. If running in PWM mode, set the

MIC2186 to switch at a lower frequency.

* se a ferrite material for the inductor core, which

has less core loss than an MPP or iron power

core.

The significant contributors to power loss at higher output

loads are (in approximate order of magnitude):

* Resistive on-time losses in the MOSFET

* Switching transition losses in the MOSFET

* Inductor resistive losses

* Current sense resistor losses

* Output capacitor resistive losses (due to the

capacitor's ESR)

To minimize power loss under heavy loads:

* Use Logic level, low on resistance MOSFETs.

Multiplying the gate charge by the on resistance

gives a figure of merit, providing a good balance

between switching and resistive power dissipa-

tion.

* Slow transition times and oscillations on the

voltage and current waveforms dissipate more

power during the turn-on and turn-off of the low

side MOSFET. A clean layout will minimize

parasitic inductance and capacitance in the gate

drive and high current paths. This will allow the

fastest transition times and waveforms without

oscillations. Low gate charge MOSFETs will

switch faster than those with higher gate charge

specifications.

* For the same size inductor, a lower value will

have fewer turns and therefore, lower winding

resistance. However, using too small of a value

will increase the inductor current and therefore

require more output capacitors to filter the output

ripple.

* Lowering the current sense resistor value will

decrease the power dissipated in the resistor.

However, it will also increase the overcurrent

limit and may require larger MOSFETs and

inductor components to handle the higher

currents.

* Use low ESR output capacitors to minimize the

power dissipated in the capacitor's ESR.

July 2002

15

MIC2186

MIC2186

Micrel

Package Information

45

∞

0

∞

≠8

∞

0.244 (6.20)

0.228 (5.79)

0.394 (10.00)

0.386 (9.80)

SEATING

PLANE

0.020 (0.51)

REF

0.020 (0.51)

0.013 (0.33)

0.157 (3.99)

0.150 (3.81)

0.050 (1.27)

0.016 (0.40)

0.0648 (1.646)

0.0434 (1.102)

0.050 (1.27)

BSC

PIN 1

DIMENSIONS:

INCHES (MM)

0.0098 (0.249)

0.0040 (0.102)

16-Pin SOIC (M)

45

∞

0.2284 (5.801)

0.2240 (5.690)

SEATING

PLANE

0.009 (0.2286)

REF

0.012 (0.30)

0.008 (0.20)

0.157 (3.99)

0.150 (3.81)

0.050 (1.27)

0.016 (0.40)

0.0688 (1.748)

0.0532 (1.351)

0.196 (4.98)

0.189 (4.80)

0.025 (0.635)

BSC

PIN 1

DIMENSIONS:

INCHES (MM)

0.0098 (0.249)

0.0040 (0.102)

0.0098 (0.249)

0.0075 (0.190)

8

∞

0

∞

16-Pin QSOP (QS)

MIC2186

Micrel

MIC2186

16

July 2002

MICREL INC.

1849 FORTUNE DRIVE

SAN JOSE, CA 95131

USA

TEL

+ 1 (408) 944-0800

FAX

+ 1 (408) 944-0970

WEB

http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or

other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2001 Micrel Incorporated