| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ML6424 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

BLOCK DIAGRAM

1

February 1997

PRELIMINARY

ML6424

*

/ML6425

*

CCIR601 Video Lowpass Filter

with Optional Sinx/x Correction

GENERAL DESCRIPTION

The ML6424 is a monolithic BiCMOS Video Lowpass

Filter IC, incorporating a 5th order Elliptic (Cauer) lowpass

filter, a third order allpass filter, and a 75

coax cable

driver. The ML6425 additionally provides sinx/x amplitude

correction. These active lowpass filters are available with

a 2.75MHz (-2) or a 5.50MHz (-1) cutoff frequency.

The input signal can be either AC or DC coupled under

the control of the MODE pin. In the DC coupled case, a

control pin (RANGE) is provided to allow the inputs to

swing down to ground. Internal self clamping is provided

for AC coupled signals.

The ML6424 and ML6425 are powered by a single 5V

supply, and can drive 1V

PP

into 75

(0.5V to 1.5V), or

2V

PP

into 150

(0.5 to 2.5V). The maximum output swing

from 0.5V to 2.5V allows easy interface to the ML6400

family of A/D converters.

*Some packages Are Obsolete

FEATURES

s

External or internal input clamping with pulse output

for synchronous clamping of multiple filters

s

Frequency tunable with R

EXT

:

±

10%

s

±

0.25dB ripple

s

>40dB attenuation at f > 1.45 x f

C

(w/o sinx/x)

s

>35dB attenuation at f > 1.45 x f

C

(with sinx/x)

s

≠12dB attenuation at f = 1.23 x f

C

s

Group delay distortion:

±

20ns up to 0.9 x f

C

s

<1% peak overshoot and ringing on 2T test pulse

s

0.5% diff. gain and 0.5

diff. phase typical

s

THD <1% at 3.58 or 4.43MHz

s

Programmable input-output gain of 1x or 2x

s

5V

±

5% operation

+5V

V

CC

V

CC

V

CC

V

CC

GAIN

V

OUT

M

V

OUT

P

R

EXT

10k

1%

GND

GND

GND

V

IN

M

V

IN

P

MODE

PULSE

I/O

15

16

7

6

13

8

5

11

3

1

9

10

14

2

12

4

+

≠

+

≠

5TH ORDER

LOW PASS

INPUT

CLAMP

PULSE

CONTROL

3RD ORDER

ALL PASS

FILTER BIAS

RANGE

BUF

BUF

SINX/X

ML6424-1

ML6424-2

ML6425-1

ML6425-2

Bandwidth

5.50MHz

2.75MHz

5.50MHz

2.75MHz

Sinx/x

No

No

Yes

Yes

ML6424/ML6425

2

PIN CONFIGURATION

TOP VIEW

V

CC

GND

V

CC

PULSE I/O

V

CC

V

IN

P

V

IN

M

RANGE

V

OUT

M

V

OUT

P

GND

GAIN

MODE

V

CC

GND

R

EXT

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

Package: S16W

16-Pin SOIC

ML6424/ML6425

3

Pin #

Name

Description

1,3,

V

CC

Positive supply voltages

5,11

(4.75V to 5.25V).

2,10,

GND

Ground voltages.

14

4

PULSE I/O U/V clamp switch control input/output

pin. When MODE is low, U/V clamp

control pulse can be applied to this

input pin. When MODE is high, the

internal circuit generates a U/V clamp

control signal to produce an output

pulse at this pin. When MODE is

floating, do not apply any voltage to

this pin since it is internally tied low in

this case. (See table below)

6,7

V

IN

P,

Input to the filter. The input voltage for

V

IN

M

the filter is applied to V

IN

P pin with

respect to V

IN

M pin which is

grounded. (With no connection to

MODE pin, input signal range should

be from V

IN

= 0.5V to 1.5V when

RANGE = Low, V

IN

= 0V to 1V when

RANGE = High). There is a 100

µ

A

internal current source connected to

each of these inputs.

8

RANGE

Input signal range control when

MODE is floating. When RANGE is

low, the input signal range is 0.5V to

1.5V, when RANGE is tied high the

input signal range is 0V to 1V.

9

R

EXT

Precision resistor to ground that

defines the cutoff frequency of the

filter. (Typical value = 10k

)

10% change in R

EXT

produces a 10%

change in f

C

(Fig. 28).

PIN DESCRIPTION

Pin #

Name

Description

12

MODE

Input coupling mode control pin.

When MODE is low, U/V signal can

be applied through an external ac

coupling capacitor to V

IN

P. When

MODE is high, Y signal can be applied

through an external AC coupling

capacitor to V

IN

P. In this case, an

internal circuitry clamps the sinc tip of

the video input signal. When MODE is

set to mid supply or left floating, input

signal can be directly applied to the

input without an AC coupling capacitor.

13

GAIN

Three state gain control pin. GAIN tied

low sets the input amplifier gain to 3/4

(0.75) and the output amplifier gain to

4/3 (1.333). When GAIN is tied high,

the input amplifier gain is 3/2 (1.5) and

the output amplifier gain is 4/3. When

GAIN is set to mid supply or left to

float, the input amplifier gain is 3/4

and the output gain is 8/3 (2.666).

(See table below)

15,16

V

OUT

P,

The output from the filter is derived

V

OUT

M

from the V

OUT

P pin with respect to

the V

OUT

M pin which is grounded

typically. It can drive 1V

PP

/75

(0.5V

to 1.5V) or 2V

PP

/150

(0.5V to 2.5V).

If the ouput common-mode level

needs to be increased, it can be done

by raising the potential of V

OUT

M. In

this case, the output is measured from

V

OUT

P with respect to GND.

Gain Table

Pulse Mode Table

MODE

INPUT COUPLING

PULSE

Low

AC for U/V

Input

Float

DC

Internally biased

High

AC for Y

Output

GAIN INPUT INPUT

OUTPUT

OUTPUT OPTIMIZES

SELECT

BUFFER

BUFFER

GAIN

GAIN

Low

1V

PP

0.75

1.333

1V

PP

--

Float

1V

PP

0.75

2.666

2V

PP

Differential

Phase

& Gain

High

1V

PP

1.50

1.333

2V

PP

Noise

ML6424/ML6425

4

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, V

CC

= 4.75 to 5.25V, T

A

= Operating Temperature Range (Note 1).

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Supply Current

100

150

mA

Input Current (V

IN

P, V

IN

M)

Sourcing out of the device

80

100

120

µ

A

Input Current Matching

Between V

IN

P and V

IN

M (tied to GND)

3.0

5

%

Low Frequency Gain

V

IN

= 100mV

P≠P

@ 100kHz

≠0.2

0.0

0.2

dB

Passband Ripple

100Hz < f

IN

< f

C

≠0.25

0.25

dB

Differential Gain (RANGE = High)

V

IN

: 1.0V

±

0.5V, @ 3.58 or 4.43MHz

0.5

1

%

Differential Phase (RANGE = High)

V

IN

: 1.0V

±

0.5V, @ 3.58 or 4.43MHz

0.5

1

Degree

Dynamic Input Signal Range (MODE = Float) RANGE = Low

0.5

1.5

V

RANGE = High

0

1

V

Output Noise (GAIN = High)

Bw: 30MHz, ML6424-1

1.7

2.3

mV

RMS

Bw: 30MHz, ML6424-2

1.3

1.9

mV

RMS

Bw: 30MHz, ML6425-1

1.7

2.3

mV

RMS

Bw: 30MHz, ML6425-2

1.3

1.9

mV

RMS

Corner Frequency (f

C

) (

±

0.25dB)

ML6424-1 or ML6425-1

5.23

5.50

5.78

MHz

ML6424-2 or ML6424-2

2.61

2.75

2.89

MHz

Stopband Loss (ML6424-1, -2)

f

IN

> 1.45 x corner frequency

35

38

dB

Stopband Loss (ML6425-1, -2)

f

IN

> 1.45 x corner frequency

30

33

dB

Peak Overshoot and Ringing

2T, 0.7V

P≠P

pulse

1

%

Composite Chroma/Luma Delay

T

D

(subcarrier) ≠ T

D

(0); f

C

= 5.5MHz

20

ns

Output Short Circuit Current

V

OUT

P to GND while V

OUT

M = GND

45

mA

Load Capacitance

V

OUT

P to GND

35

pF

Logic Input Low (V

IL

)

RANGE

0.8

V

Logic Input High (V

IH

)

RANGE

V

CC

≠ 0.8

V

Logic Input Low (I

IL

)

V

IN

= GND

≠1

µA

Logic Input High (I

IL

)

V

IN

= V

CC

1

µA

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst case conditions.

Note 2: Digital Inputs: All inputs are high impedance 1

µ

A leakage, with MAX input voltage levels of 0.8V from each supply

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

DC Supply Voltage ........................................ ≠0.3V to 7V

Analog & Digital

Inputs/Outputs ................................. ≠0.3V to V

CC

+ 0.3V

Input current per pin .............................. ≠25mA to 25mA

Storage Temperature ................................ ≠65∞C to 150

C

Maximum Junction Temperature ............................ 150

C

OPERATING CONDITIONS

Operating temperature range ......................... 0∞C to 70

C

Operating supply range ....................................... 5V

±

5%

ML6424/ML6425

5

FUNCTIONAL DESCRIPTION

The ML6424 and ML6425 are monolithic CCIR601

continuous time video filters, designed for broadcast and

professional luminance and chrominance antialias and

reconstruction applications. They are fabricated using

Micro Linear's 1.5

µ

, 4 GHz BiCMOS process. The filter

incorporates an input amplifier, programmable gain of 1x

or 2x set by the GAIN pin, a fifth order lowpass filter, a

third order allpass filter, and an output amplifier capable

of driving 75

to ground. The ML6425 provides sinx/x

equalization.

The ML6424≠1 is intended for application as luminance

antialias processing, the ML6424≠2 for chrominance

antialias, the ML6425≠1 for luma reconstruction, and the

ML6425≠2 for chroma reconstruction.

Input signals can be applied either through an AC coupling

capacitor (MODE = High/Low) or directly to the input pin

(MODE = float). With MODE = High, Y-Channel signal

6

7

V

IN

M

ML6424-1

V

IN

P

12

MODE

+5V

Y

4

PULSE I/O

6

7

V

IN

M

ML6424-2

V

IN

P

12

MODE

U

4

PULSE I/O

6

7

V

IN

M

ML6424-2

V

IN

P

12

MODE

V

75

1

µ

F

1

µ

F

1

µ

F

75

75

4

PULSE I/O

can be applied to the input and the PULSE I/O pin

generates a clamping pulse for the U/V channel. When

MODE = Low, U/V channel signal can be applied to the

input. In this case, the PULSE I/O pin can take the pulse

signal generated from the PULSE I/O pin of the other chip

in the Y-channel. In the case of direct coupling, RANGE

should be adjusted according to the input signal range.

When RANGE is low, the input signal range is 0.5V to

1.5V. When the input signal goes down to 0V, RANGE

should be tied high. In this case, an offset is added to the

input so that the filter can process the 0V DC level.

The output amplifier is designed to drive up to 20mA peak

into a 75

load, or 17mA peak into a 150

load. Load

resistance less than 75

and/or output voltage above 1.5V

into 75

(2.5V into 150

) may cause signal distortion.

Good high frequency decoupling is required between

each power supply pin and ground, otherwise oscillations

and/or excessive crosstalk may occur.

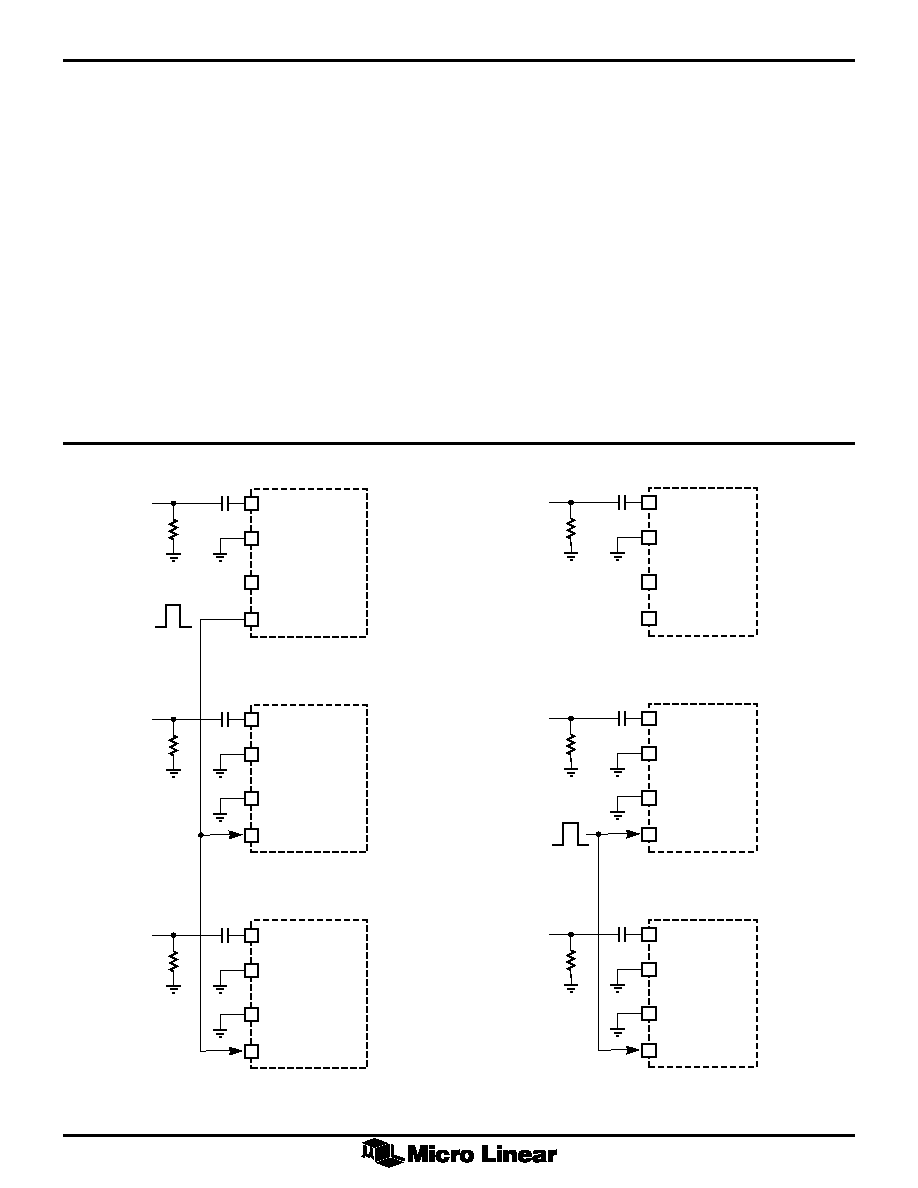

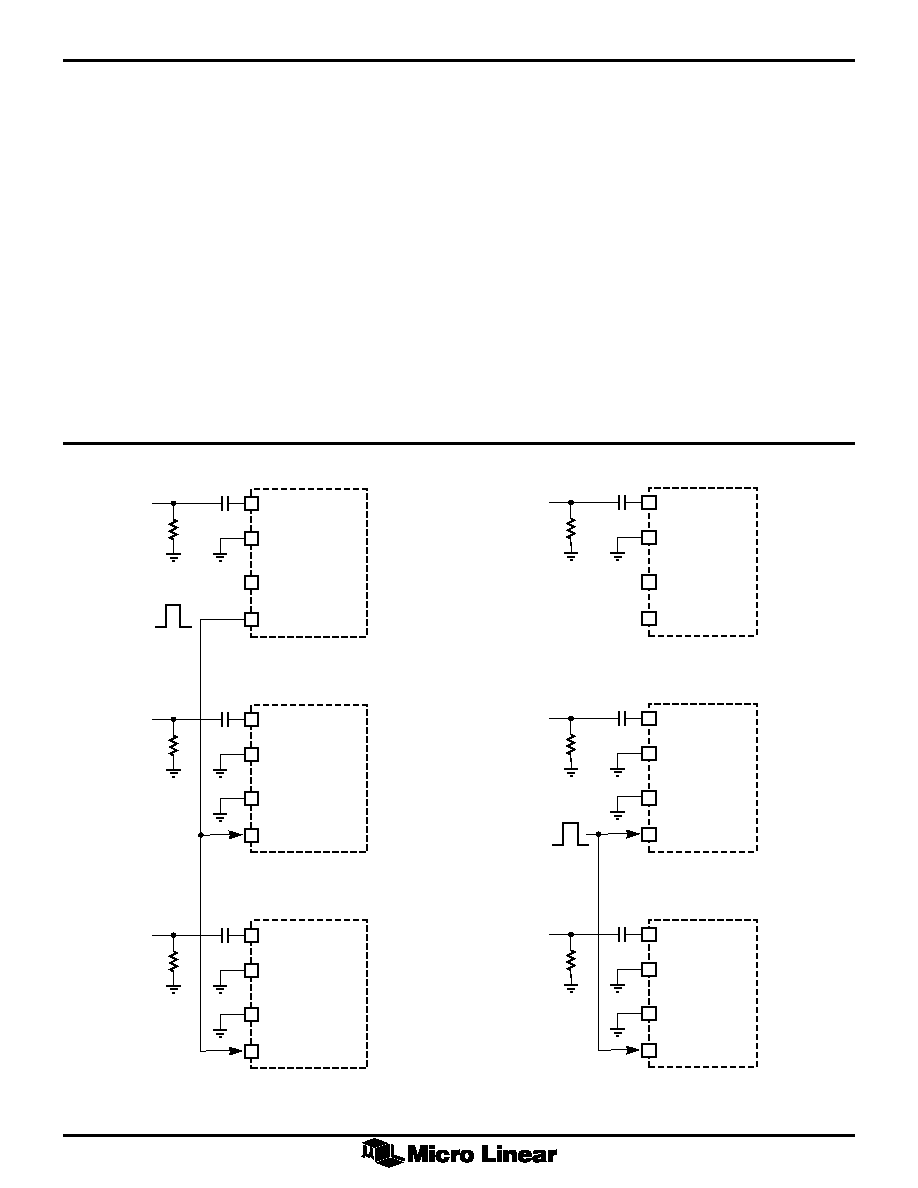

Figure 1. YUV Filter with Sync on Y Input

and Auto Clamp On

6

7

V

IN

M

ML6424-1

V

IN

P

12

MODE

+5V

Y

4

PULSE I/O

6

7

V

IN

M

ML6424-2

V

IN

P

12

MODE

U

4

PULSE I/O

6

7

V

IN

M

ML6424-2

V

IN

P

12

MODE

V

75

1

µ

F

1

µ

F

1

µ

F

75

75

4

PULSE I/O

Figure 2. YUV Filter with External Sync for U/V

ML6424/ML6425

6

6

7

V

IN

M

ML6424-1

V

IN

P

12

MODE

+5V

Y

4

PULSE I/O

6

7

V

IN

M

ML6424-2

V

IN

P

12

MODE

C

75

1

µ

F

1

µ

F

75

4

PULSE I/O

Figure 3. Y/C Filter

ML6424/ML6425

7

+10

0

≠10

≠20

≠30

≠40

≠50

≠60

≠70

≠80

≠90

AMPLITUDE (dB)

FREQUENCY (MHz)

0.1

1

10

50

+0.3

+0.2

+0.1

0.0

≠0.1

≠0.2

≠0.3

≠0.4

≠0.5

≠0.6

≠0.7

AMPLITUDE (dB)

FREQUENCY (Hz)

100k

3M

6M

380

360

340

320

300

280

GROUP

DELA

Y

(ns)

100k

3M

6M

FREQUENCY (Hz)

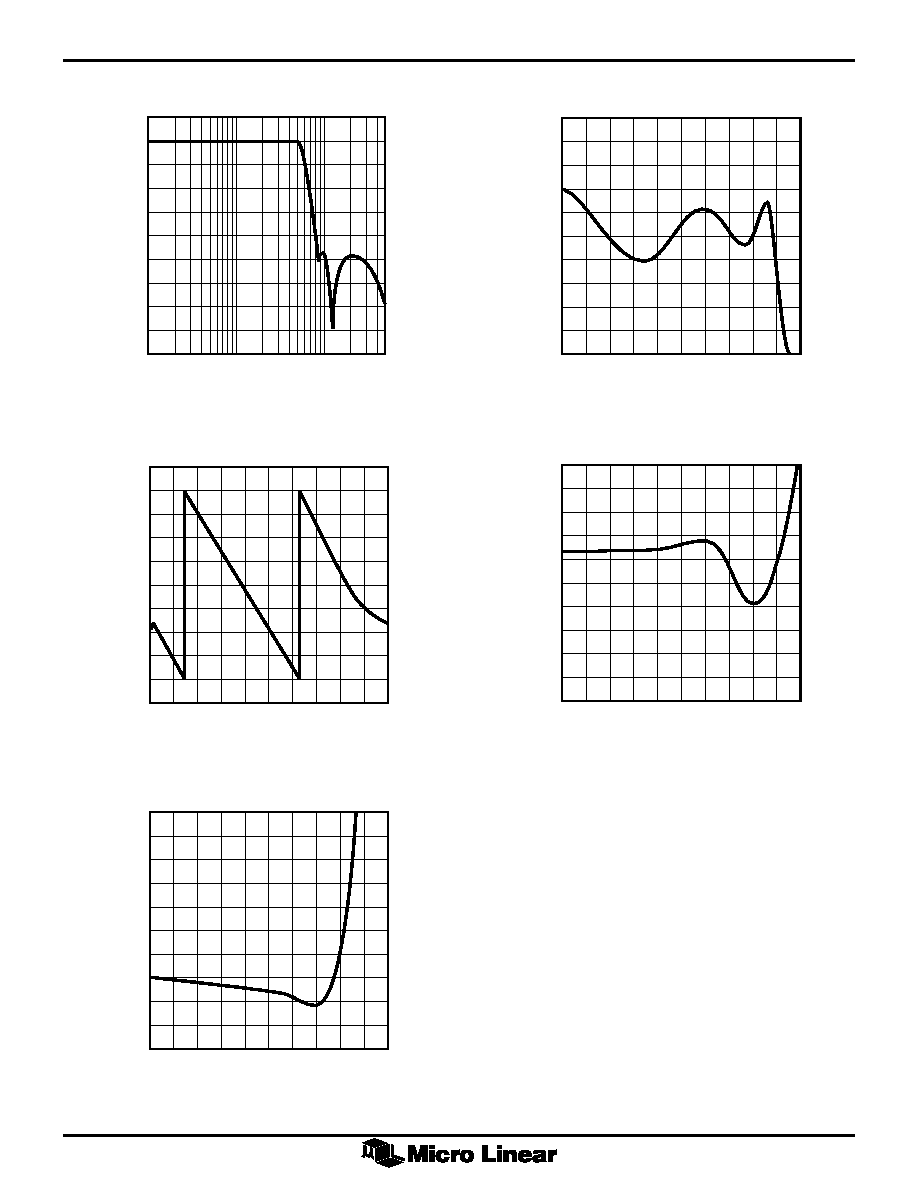

ML6424-1 RESPONSE CURVES

Figure 4. Amplitude vs Frequency

Figure 5. Amplitude vs Frequency

Figure 6. Phase vs Linear Frequency

Figure 7. Deviation from Linear Phase

Figure 8. Group Delay vs Frequency

PHASE (45∞/div)

FREQUENCY (Hz)

500k

5.5M

0∞

PHASE (10∞/div)

FREQUENCY (Hz)

500k

5.5M

0∞--

ML6424/ML6425

8

ML6424-2 RESPONSE CURVES

+10

0

≠10

≠20

≠30

≠40

≠50

≠60

≠70

≠80

≠90

AMPLITUDE (dB)

FREQUENCY (MHz)

0.1

1

10

30

Figure 9. Amplitude vs Frequency

+0.4

+0.3

+0.2

+0.1

0.0

≠0.1

≠0.2

≠0.3

≠0.4

≠0.5

≠0.6

AMPLITUDE (dB)

100k

1.5M

3M

FREQUENCY (Hz)

Figure 10. Amplitude vs Frequency

730

690

650

610

570

530

GROUP

DELA

Y

(ns)

100k

1.5M

3M

FREQUENCY (Hz)

Figure 13. Group Delay vs Frequency

Figure 12. Deviation from Linear Phase

PHASE (5∞/div)

FREQUENCY (Hz)

200k

2.2M

0∞

Figure 11. Phase vs Linear Frequency

PHASE (45∞/div)

FREQUENCY (Hz)

200k

2.2M

0∞

ML6424/ML6425

9

ML6425-1 RESPONSE CURVES

Figure 14. Amplitude vs Frequency

20

10

0

≠10

≠20

≠30

≠40

≠50

≠60

≠70

≠80

RELA

TIVE AMPLITUDE (dB)

FREQUENCY (Hz)

100k

1M

10M

Figure 15. Amplitude vs Frequency

+4dB

3.0

2.0

1.0

0

RELA

TIVE AMPLITUDE (dB)

FREQUENCY (MHz)

0.1

1

2

3

Figure 18. Group Delay vs Frequency

410

390

370

350

330

310

290

270

250

230

210

GROUP

DELA

Y

(ns)

100k

3.5M

6M

FREQUENCY (Hz)

Figure 17. Deviation from Linear Phase

PHASE (10∞/div)

FREQUENCY (Hz)

500k

5.5M

0∞

Figure 16. Phase vs Frequency

PHASE (45∞/div)

FREQUENCY (Hz)

500k

5.5M

0∞

ML6424/ML6425

10

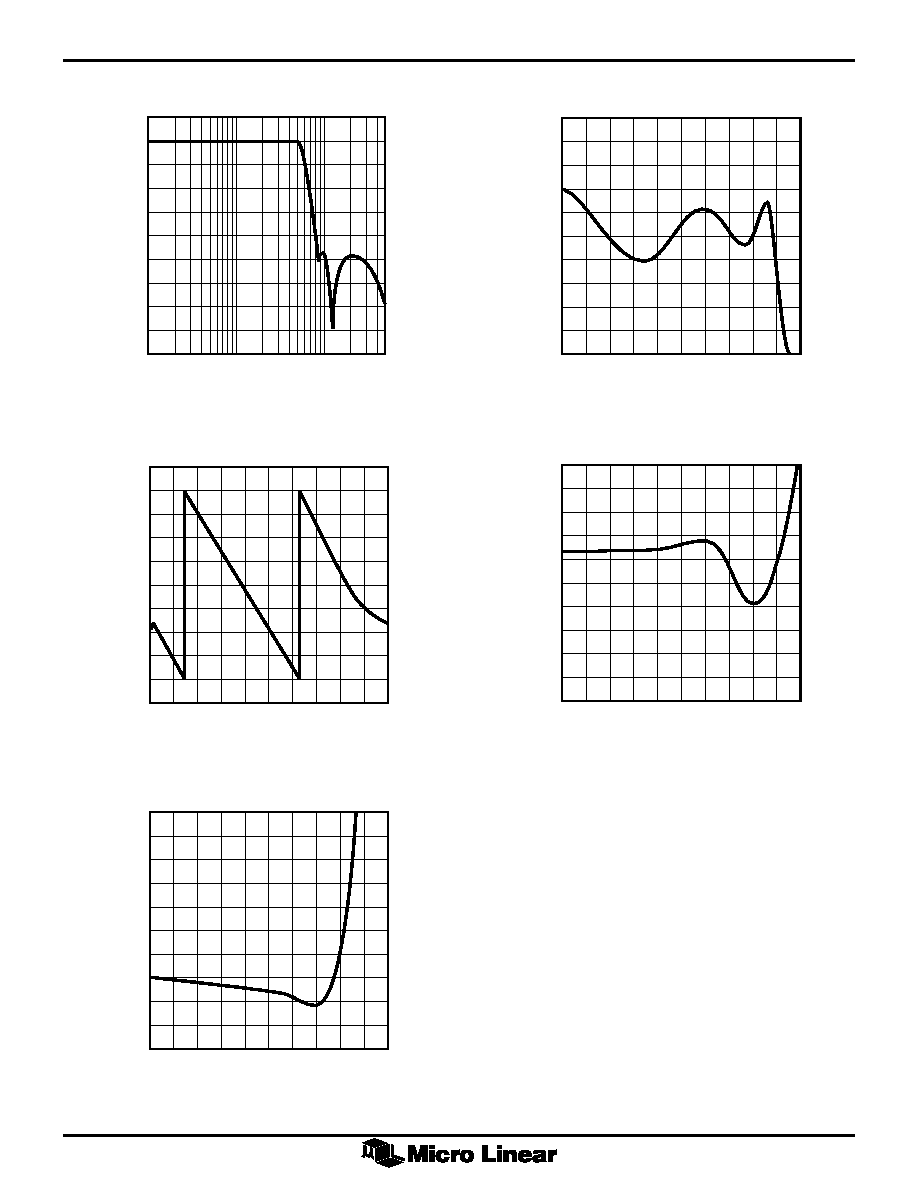

ML6425-2 RESPONSE CURVES

Figure 23. Group Delay vs Frequency

GROUP

DELA

Y

(20ns/div)

FREQUENCY (Hz)

100k

3.0M

630

Figure 22. Deviation from Linear vs Phase

PHASE (5∞/div)

FREQUENCY (Hz)

200k

2.2M

Figure 24. Frequency vs R

EXT

6

5

4

3

2

CUT OFF FREQUENCY

(Hz)

REXT (k)

8

9

10

12

11

ML6424/25-1

ML6424/25-2

Figure 19. Amplitude vs Frequency

100k

1M

10M

FREQUENCY (Hz)

20

10

0

≠10

≠20

≠30

≠40

≠50

≠60

≠70

≠80

RELA

TIVE AMPLITUDE (dB)

Figure 20. Amplitude vs Frequency

AMPLITUDE (dB)

FREQUENCY (Hz)

100k

6.0M

0

1

2

3

4

Figure 21. Phase vs Linear Frequency

PHASE (45∞/div)

FREQUENCY (Hz)

200k

2.2M

0∞

ML6424/ML6425

11

Figure 25. Transient Response

AMPLITUDE (0.5V/div

.)

TIME (500ns/div.)

INPUT FROM

DAC OUTPUT

FILTER

OUTPUT

ML6425-2 RESPONSE CURVES

ML6424/ML6425

12

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design.

Micro Linear does not assume any liability arising out of the application or use of any product described herein,

neither does it convey any license under its patent right nor the rights of others. The circuits contained in this

data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to

whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility

or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel

before deciding on a particular application.

DS6424_25-01

PHYSICAL DIMENSIONS

inches (millimeters)

ORDERING INFORMATION

PART NUMBER

FREQ

SIN X/X

TEMPERATURE RANGE

PACKAGE

ML6424-1

5.5

NO

0

C to 70

C

16-Pin SOIC (S16W)

(Obsolete)

ML6424-2

2.75

NO

0

C to 70

C

16-Pin SOIC (S16W)

ML6425-1

5.5

YES

0

C to 70

C

16-Pin SOIC (S16W)

(Obsolete)

ML6425-2

2.75

YES

0

C to 70

C

16-Pin SOIC (S16W)

2092 Concourse Drive

San Jose, CA 95131

Tel: 408/433-5200

Fax: 408/432-0295

SEATING PLANE

0.291 - 0.301

(7.39 - 7.65)

PIN 1 ID

0.398 - 0.412

(10.11 - 10.47)

0.400 - 0.414

(10.16 - 10.52)

0.012 - 0.020

(0.30 - 0.51)

0.050 BSC

(1.27 BSC)

0.022 - 0.042

(0.56 - 1.07)

0.095 - 0.107

(2.41 - 2.72)

0.005 - 0.013

(0.13 - 0.33)

0.090 - 0.094

(2.28 - 2.39)

16

0.009 - 0.013

(0.22 - 0.33)

0∫ - 8∫

1

0.024 - 0.034

(0.61 - 0.86)

(4 PLACES)

Package: S16W

16-Pin Wide SOIC

© Micro Linear 1997

is a registered trademark of Micro Linear Corporation

Products described herein may be covered by one or more of the following patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017;

5,559,470; 5,565,761, 5,594,376, 5,592,128. Other patents are pending.