| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ML6694CQ | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

May 1997

ML6694

*

100BASE-TX Physical Layer with 5-Bit Interface

1

GENERAL DESCRIPTION

The ML6694 is a high-speed physical layer transceiver

that provides a 5-bit (or symbol) interface to unshielded

twisted pair cable media. The ML6694 is well suited for

repeater applications using repeater controllers with the

5-bit interface. The ML6694 may also be used in FDDI-

over-copper applications.

The ML6694 integrates 125MHz clock recovery/

generation, receive adaptive equalization, baseline

wander correction and MLT-3/10BASE-T transmitter.

FEATURES

s

5-bit (or symbol) parallel interface

s

Compliant to IEEE 802.3u 100BASE-TX standard

s

Compliant to ANSI X3T12 TP-PMD (FDDI) standard

s

Single-jack 10BASE-T/100BASE-TX solution when used

with external 10Mbps PHY

s

125MHz receive clock recovery/generation

s

Baseline wander correction

s

Adaptive equalization and MLT-3 encoding/decoding

s

Supports full-duplex operation

BLOCK DIAGRAM

(PLCC Pin Configuration)

* Some Packages Are End Of Life As Of August 1, 2000

TXC

TPOUTP

TPOUTN

NRZ TO NRZI

AND

NRZI TO MLT-3

ENCODER

CLOCK AND DATA

RECOVERY

NRZI TO NRZ DECODER

RTSET

TSM4

10BTTXINN

TSM3

TSM2

TPINP

TPINN

CMREF

RGMSET

SDO

TSM1

TSM0

RXC

RSM4

RSM3

RSM2

RSM1

RSM0

10BTTXINP

PWRDN

LPBK

SEL10/

100

CLOCK SYTHESIZER

CONTROL LOGIC

EQUALIZER

BLW CORRECTION

MLT-3 DECODER

LOOPBACK MUX

SERIALIZER

DESERIALIZER

100BASE-TX/10BASE-T

TWISTED PAIR DRIVER

44

41

40

34

33

31

38

37

39

30

24

7

42

25

2

3

4

5

6

16

8

9

11

13

15

ML6694

2

PIN CONFIGURATION

ML6694

44-Pin PLCC (Q44)

CMREF

TPINP

TPINN

AVCC2

AGND2

TPOUTP

TPOUTN

AGND3

RTSET

RGMSET

NC

PWRDN

RSM4

RSM3

DGND1

RSM2

DVCC1

RSM1

DGND2

RSM0

RXC

DGND3

18

19

20

21

22

TSM0

TSM1

TSM2

TSM3

TSM4

AGND1

TXC

AVCC1

LPBK

10BTTXINP

10BTTXINN

DVCC2

DGND4A

DGND4B

DGND4C

DVCC5

DGND5

SDO

SEL10/100

NC

NC

AVCC3

23

24

7

8

9

10

11

12

13

14

15

16

17

6

5

4

3

2

39

38

37

36

35

34

33

32

31

30

29

1

44

25

43

26

42

27

41

28

40

CMREF

TPINP

TPINN

AVCC2

AGND2

TPOUTP

TPOUTN

AGND3

RTSET

RGMSET

NC

PWRDN

RSM4

RSM3

DGND1

RSM2

DVCC1

RSM1

DGND2

RSM0

RXC

DGND3

12

13

14

15

16

TSM0

TSM1

TSM2

TSM3

TSM4

AGND1

TXC

AVCC1

LPBK

10BTTXINP

10BTTXINN

DVCC2

DGND4A

DGND4B

DGND4C

DVCC5

DGND5

SDO

SEL10/100

NC

NC

AVCC3

17

18

1

2

3

4

5

6

7

8

9

10

11

44

43

42

41

40

33

32

31

30

29

28

27

26

25

24

23

39

38

19

37

20

36

21

35

22

34

ML6694

44-Pin TQFP (H44-10)

ML6694

3

PIN DESCRIPTION

(Pin numbers for TQFP package in parentheses)

PIN

NAME

DESCRIPTION

1

(39)

AGND1

Analog ground.

2-6

(40-44)

TSM<4:0>

Transmit data TTL inputs. TSM<4:0> inputs accept TX data symbols. Data

appearing at TSM<4:0> are clocked into the ML6694 on the rising edge of TXC.

7

(1)

PWRDN

Device power down input. A low signal powers down all ciruits of the ML6694, and

dissipates less than 20mA.

8,9,

(2, 3,

RSM<4:0>

Receive data TTL outputs. RSM<4:0> outputs may be sampled synchronously with

11,13, 5, 7, 9)

RXC's rising edge.

15

10

(4)

DGND1

Digital ground.

12

(6)

DVCC1

Digital +5V power supply.

14

(8)

DGND2

Digital ground.

16

(10)

RXC

Recovered receive symbol clock TTL output. This 25MHz clock is phase-aligned

with the internal 125MHz bit clock recovered from the signal received at TPINP/N

when data is present. Receive data at RSM<4:0> change on the falling edges and

should be sampled on the rising edges of this clock. RXC is phase aligned to TXC

when 100BASE-TX signal is not present at TPINP/N

17

(11)

DGND3

Digital ground.

18

(12)

DVCC2

Digital +5V power supply.

19

(13)

DGND4A

Digital ground.

20

(14)

DGND4B

Digital ground.

21

(15)

DGND4C

Digital ground.

22

(16)

DVCC5

Digital +5V power supply.

23

(17)

DGND5

Digital ground.

24

(18)

SD0

Signal detect TTL output. A high output level indicates 100BASE-TX activity at

TPINP/N with an amplitude exceeding the preset threshold. The signal detect

function is active only in 100Mbps mode, that is when the pin SEL10/

100 is low.

25

(19)

SEL10/

100

Speed select TTL input. Driving this pin high disables 100BASE-TX transmit and

receive functions, and enables the 10BASE-T transmit path from 10BTTXINP/N to

TPOUTP/N. A low signal on SEL10/

100 disables the 10BTTXINP/N inputs and enables

100BASE-TX operation.

28

(22)

AVCC3

Analog positive power supply.

30

(24)

RGMSET

Equalizer bias resistor input. An external 9.53k

, 1% resistor connected between

RGMSET and AGND3 sets internal time constants controlling the receive equalizer

transfer function.

31

(25)

RTSET

Transmit level bias resistor input. An external 2.49k

, 1% resistor connected

between RTSET and AGND3 sets a precision constant bias current for the twisted

pair transmit level.

32

(26)

AGND3

Analog ground.

33,34 (27,28)

TPOUTN/P

Transmit twisted pair outputs. This differential current output pair drives MLT-3

waveforms into the network coupling transformer in 100BASE-TX mode, and

10BASE-T or FLP waveforms in 10BASE-T mode.

35

(29)

AGND2

Analog ground.

36

(30)

AVCC2

Analog +5V power supply.

37,38 (31, 32)

TPINN/P

Receive twisted pair inputs. This differential input pair receives 100BASE-TX signals

from the network.

ML6694

4

PIN DESCRIPTION

(Continued)

PIN

NAME

DESCRIPTION

39

(33)

CMREF

Receiver common-mode reference output. This pin provides a common-mode bias

point for the twisted-pair media line receiver. A typical value for CMREF is

(VCC≠1.26)V.

40,41 (34,35)

10BTTXINN/P 10BASE-T transmit waveform inputs. The ML6694 presents a linear copy of the input

at 10BTTXINN/P to the TPOUTN/P outputs when the ML6694 functions in 10BASE-T

mode. Signals presented to these pins must be centered at V

CC

/2 with a single ended

amplitude of

±

0.25V.

42

(36)

LPBK

Loopback TTL input pin. Tying this pin to ground places the part in loopback mode;

data at RSM<4:0> are serialized, MLT-3 encoded, equalized then sent to the receive

PLL for clock recovery and sent to the RSM<4:0> outputs. Floating this pin or tying it

to V

CC

places the part in its normal mode of operation.

43

(37)

AVCC1

Analog +5V power supply.

44

(38)

TXC

Transmit clock TTL input. This 25MHz clock is the frequency reference for the

internal transmit PLL clock multiplier. This pin should be driven by an external

25MHz clock at TTL or CMOS levels.

ML6694

5

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

V

CC

Supply Voltage Range .................... GND ≠0.3V to 6V

Input Voltage Range

Digital Inputs ....................... GND ≠0.3V to V

CC

+ 0.3V

TPINP, TPINN, 10BTTXINN,

10BTTXINP ...................... GND ≠0.3V to V

CC

+ 0.3V

Output Current

TPOUTP, TPOUTN .............................................. 60mA

All other outputs .................................................. 10mA

Junction Temperature .............................................. 150

∞

C

Storage Temperature ................................ ≠65

∞

C to 150

∞

C

Lead Temperature (Soldering, 10 sec) ...................... 260

∞

C

OPERATING CONDITIONS

V

CC

Supply Voltage ............................................. 5V

±

5%

All V

CC

supply pins

must be within 0.1V of each other.

All GND pins

must be within 0.1V of each other.

T

A

, Ambient temperature ................................ 0

∞

C to 70

∞

C

RGMSET ...................................................... 9.53k

±

1%

RTSET .......................................................... 2.49k

±

1%

Receive transformer insertion loss ........................ <≠0.5dB

DC ELECTRICAL CHARACTERISTICS

Over full range of operating conditions unless otherwise specified (Note 1)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

TTL Inputs (TSM<4:0>, TXC, SEL10/

100, PWRDN, LPBK)

V

IL

Input Low Voltage

I

IL

= ≠400

µ

A

0.8

V

V

IH

Input High Voltage

I

IH

= 100

µ

A

2.0

V

I

IL

Input Low Current

V

IN

= 0.4V

≠200

µ

A

I

IH

Input High Current

V

IN

= 2.7V

100

µ

A

TTL Outputs (RSM<4:0>, RXC, SDO)

V

OL

Output Low Voltage

I

OL

= 4mA

0.4

V

V

OH

Output High Voltage

I

OH

= ≠4mA

2.4

V

Receiver

V

ICM

TPINP/N Input Common-Mode

100

Termination across TPINP/N

V

CC

≠ 1.26

V

Voltage

V

ID

TPINP-TPINN Differential Input

≠3.0

3.0

V

Voltage Range

R

IDR

TPINP-TPINN Differential

10.0k

Input Resistance

I

ICM

TPINP/N Common-Mode Input

+10

µ

A

Current

I

RGM

RGMSET Input Current

RGMSET = 9.53k

130

µ

A

I

RT

RTSET Input Current

RTSET = 2.49k

500

µ

A

Transmitter

I

TD100

TPOUTP/N 100BASE-TX Mode

Note 2, 3

±

19

±

21

mA

Differential Output Current

I

TD10

TPOUTP/N 10BASE-T

±

55

±

60

±

65

mA

Mode Differential Output Current

I

TOFF

TPOUTP/N Off-State Output

R

L

= 200, 1%

0

1.5

mA

I

TXI

TPOUTP/N Differential Output

Current Imbalance

R

L

= 200, 1%

500

µ

A

ML6694

6

DC ELECTRICAL CHARACTERISTICS

(Continued)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Transmitter (Continued)

X

ERR

TPOUTP/N Differential Output

V

OUT

= V

CC

; Note 3

≠5.0

+5.0

%

Current Error

X

CMP100

TPOUTP/N 100BASE-X Output

V

OUT

= V

CC

±

2.2V; referred to

Current Compliance Error

I

OUT

at V

CC

≠2.0

+2.0

%

V

OCM10

TPOUTP/N 10BASE-T Output

I

TD10

remains within specified

V

CC

≠ 2.7

V

CC

+ 2.7

V

Voltage Compliance Range

values

V

ICM10

10BTTXNN/P Input

V

CC

/2

≠ 0.3

V

CC

/2

+ 0.3

V

Common-Mode Voltage Range

Power Supply Current

I

CC100

Supply Current 100BASE-TX

Current into all V

CC

pins,

195

260

mA

Operation, Transmitting

V

CC

= 5.25V

I

CC10

Supply Current 10BASE-T Mode

90

110

mA

I

CCOFF

Supply Current

PWRDN

20

mA

Power Down Mode

AC ELECTRICAL CHARACTERISTICS

Over full range of operating conditions unless otherwise specified

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Transmitter (Note 4)

t

TR/F

TPOUTP-TPOUTN Differential

Notes 5, 6; for any legal

3.0

5.0

ns

Rise/Fall Time

code sequence

t

TM

TPOUTP-TPOUTN Differential

Notes 5, 6; for any legal

≠0.5

0.5

ns

Rise/Fall Time Mismatch

code sequence

t

TDC

TPOUTP-TPOUTN Differential

Notes 4, 6

≠0.5

0.5

ns

Output Duty Cycle Distortion

t

TJT

TPOUTP-TPOUTN Differential

Note 6

300

1400

ps

Output Peak-to-Peak Jitter

X

OST

TPOUTP-TPOUTN Differential

Notes 6, 7

5

%

Output Voltage Overshoot

t

TXP

Transmit Bit Delay

Note 8

10.5

Bit Times

t

RXDC

Receive Bit Delay

Note 9

15.5

Bit Times

ML6694

7

AC ELECTRICAL CHARACTERISTICS

(Continued)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

MII (Media-Independent Interface)

X

BTOL

TX Output Clock Frequency

25MHz frequency

≠100

+100

ppm

Tolerance

t

TPWH

TXC pulse width HIGH

14

ns

t

TPWL

TXC pulse width LOW

14

ns

t

RPWH

RXC pulse width HIGH

14

ns

t

RPWL

RXC pulse width LOW

14

ns

t

TPS

Setup time, TSM<4:0> Data Valid

12

ns

to TXC Rising Edge (1.4V point)

t

TPH

Hold Time, TSM<4:0> Data

3

ns

Valid After TXC Rising Edge

(1.4V point)

t

RCS

Time that RSM<4:0> Data are

10

ns

Valid Before RXC Rising Edge

(1.4V point)

t

RCH

Time that RSM<4:0> Data are

10

ns

Valid After RXC Rising Edge

(1.4V point)

t

RPCR

RXC 10% ≠ 90% Rise Time

6

ns

t

RPCF

RXC 90%-10% Fall Time

6

ns

Note 1.

Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2.

Measured using the test circuit shown in Fig. 1, under the following conditions:

R

LP

= 200

, R

LS

= 49.9

, R

TSET

= 2.49k

.

All resistors are 1% tolerance.

Note 3.

Output current amplitude is I

OUT

= 40

1.25V/RTSET.

Note 4.

Measured relative to ideal negative and positive signal 50% points, using the four successive MLT-3 transitions for the 01010101 bit sequence.

Note 5.

Time difference between 10% and 90% levels of the transition from the baseline voltage (nominally zero) to either the positive or negative peak signal voltage. The

times specified here correlate to the transition times defined in the ANSI X3T9.5 TP-PMD Rev 2.0 working draft, section 9.1.6, which include the effects of the

external network coupling transformer and EMI/RFI emissions filter.

Note 6.

Differential test load is shown in fig. 1 (see note 3).

Note 7.

Defined as the percentage excursion of the differential signal transition beyond its final adjusted value during the symbol interval following the transition. The

adjusted value is obtained by doing a straight line best-fit to an output waveform containing 14 bit-times of no transition preceded by a transition from zero to

either a positive or negative signal peak; the adjusted value is the point at which the straight line fit meets the rising or falling signal edge.

Note 8.

Symbol /J/ at TSM <4:0> sampled by TXC to first bit of /J/ at MDI.

Note 9.

First bit of /J/ at MDI to first rising edge of RXC after the last part of the /J/ appears at RSM <4:0>.

R

LS

49.9

R

LP

200

V

CC

R

LP

200

2:1

R

LS

49.9

TPOUTP

TPOUTN

1

2

Figure 1. Test Circuit

ML6694

8

TXC

TSM<4:0>

t

TPS

t

TPH

t

TPWH

t

TPWL

RXC

RSM<4:0>

t

RCS

t

RCM

t

TPWH

t

TPWL

t

RPCR

t

RPCF

Figure 2.

Figure 3.

ML6694

9

FUNCTIONAL DESCRIPTION

TRANSMIT SECTION

100BASE-TX Operation

The transmitter accepts scrambled 5-bit symbols clocked

in at 25MHz and outputs MLT-3 signals onto the twisted-

pair media at 100Mbps. The on-chip transmit PLL converts

a 25MHz TTL-level clock at TXC to an internal 125MHz

bit clock. TXC from the ML6694 clocks scrambled

transmit symbols from the MAC into the ML6694's

TSM<4:0> input pins. Symbols from the TSM<4:0> inputs

are converted from parallel to serial form at the 125MHz

clock rate. The serial transmit data is converted to MLT-3

3-level code and driven differentialy out of the TPOUTP

and TPOUTN pins at nominal

±

2V levels with the proper

loads. The transmitter is designed to drive a center-tapped

transformer with a 2:1 winding ratio, so a differential 400

ohm load is used on the transformer primary to properly

terminate the 100 ohm cable and termination on the

secondary. The transformer's center tap must be tied to

V

CC

. A 2:1 transformer allows using a

±

20mA output

current in 100BASE-TX mode. Using a 1:1 transformer

would have required twice the output current and

increased the on-chip power dissipation. An external

2.49k

, 1% resistor at the RTSET pin creates the correct

output levels at TPOUP/N.

10BASE-T

In 10BASE-T mode, the transmitter acts as a linear buffer

with a gain of 10. 10BASE-T inputs (Manchester data and

normal link pulses) at 10BTTXINP/N appear as full-swing

signals at TPOUTP/N in this mode. Inputs to the

10BTTXINP/N pins should have a nominal

±

0.25V

differential amplitude and a common-mode voltage of

V

CC

/2, and should also be waveshaped or filtered to meet

the 10BASE-T harmonic content requirements. The ML6694

does not provide any 10BASE-T transmit filtering.

RECEIVE SECTION

The receiver converts 3-level MLT-3 signals from the

twisted-pair media to 5-bit scrambled symbols at

RSM<4:0> with extracted clock at RXC. The adaptive

equalizer compensates for the distortion of up to 140m of

cable and attenuates cable-induced jitter, corrects for DC

baseline wander, and converts the MLT-3 signal to 2-level

NRZ. The receive PLL extracts clock from the equalized

signal, providing additional jitter attenuation, and clocks

the signal through the serial to parallel converter. The

resulting 5-bit symbols appear at RSM<4:0>. The

extracted clock appears at RXC. Resistor RGMSET sets

internal time constants controlling the adaptive equalizer's

transfer function. RGMSET must be set to 9.53k

(1%).

LOOPBACK

Tying

LPBK pin low places the part in loopback mode.

Data at TXD<4:0> are serialized, MLT-3 encoded,

equalized, then sent to receive PLL for clock recovery and

sent to the RXD<4:0> outputs.

In this mode, data at TXD<4:0> has to be valid 5-bit

symbol data.

ML6694 SCHEMATIC

Figure 2 shows a general design where the 5-bit and other

control signals interface to the controller. TXC is

connected to a 25MHz, 100ppm clock oscillator.

The inductors L1 and L2 are for the purpose of improving

return loss.

Capacitor C7 is recommended. It decouples some noise at

the inputs of the ML6694 and improves the Bit Error Rate

(BER) performance of the board. It is recommended

having a 0.1

µ

F capacitor on every V

CC

pin as indicated by

C3, 4, 9-12. Also, it is recommended to split the A

VCC

and

D

VCC

, AGND and DGND. It is recommended that AGND

and DGND planes are large enough for low inductance. If

splitting the two grounds and keeping the ground planes

large enough is not possible due to board space, you

could join them into one larger ground plane.

DIFFERENCES BETWEEN THE ML6694 AND ML6698

Both parts are pin to pin compatible and perform the same

functions. The only differences are:

1. SDO: The ML6694 has SDO (Signal Detect Output)

active in 100BASE-TX mode only, while the ML6698

has it active in both 10BASE-T and 100BASE-TX

modes.

2. SEL10/

100 or SEL100/10: The ML6694 has the

100BASE-TX mode active low and the 10BASE-T

mode active high (SEL10/

100). The ML6698 has the

opposite polarity where the 100BASE-TX mode is

active high and the 10BASE-T mode is active low

(SEL100/

10).

ML6694

10

R1

2.49k

1%, 1/8W Surface Mount

R2

9.53k

1%, 1/8W Surface Mount

R8, R9,

200

1%, 1/8W Surface Mount

R23

R10, R11

100

1%, 1/8W Surface Mount

R15-R20

49.9

5%, 1/8W Surface Mount

R21-R22

75

5%, 1/8W Surface Mount

C1, C3,

0.1

µ

F Ceramic Chip Cap

C4, C8-C12

C5, C6

10

µ

F Tantalum Cap

Figure 2. ML6694 Typical Applications Circuit

R22

AVCC

DVCC

CMREF

TPINP

TPINN

AVCC2

AGND2

TPOUTP

TPOUTN

AGND3

RTSET

RGMSET

NC

PWRDN

RSM4

RSM3

DGND1

RSM2

DVCC1

RSM1

DGND2

RSM0

RXC

DGND3

18 19

20

21

22

TSM0

TSM1

TSM2

TSM3

TSM4

AGND1

TXC

AVCC1

LPBK

10BTTXINP

10BTTXINN

DVCC2

DGND4A

DGND4B

DGND4C

DVCC5

DGND5

SDO

SEL10/100

NC

NC

AVCC3

23

24

7

8

9

10

11

12

13

14

15

16

17

6

5

4

3

2

39

38

37

36

35

34

33

32

31

30

29

1

44

25

43

26

42

27

41

28

40

ML6694

U1

U2

U5

1

NC

4

2

3

C1

L2

L1

R9

R8

R17

RJ45

SHIELD

GROUNDED

R18

R21

R19

R20

R16

R15

1

2

3

4

5

6

7

8

TXTP+

TXTP≠

RXTP+

RXTP≠

R2

R1

R11

R10

1:1

2:1

C2

C8

CONTROLLER INTERFACE

OUTPUTS TO A

10BASE-T PHY

INPUT FROM A CONTROLLER,

OTHERWISE FLOAT

INPUT FROM A

10BASE-T PHY

AVCC

C3

C9

C10

R23

C6

FB1

FB2

C7

AVCC

C4

C11

C12

C5

+

+

DVCC

C7

10pF Cap

C2

Board Layer Cap (2kV rated)

U1

ML6694 44-Pin PLCC Surface Mount

U2

Clock Oscillator, 25MHz 4-Pin Surface Mount

U5

Bel Transformer Module S558-1287-02,

XFMRS Inc. XF6692TX, or Valor ST6129

(not pin compatible)

FB1, FB2

Fair-Rite SM Bead P/N 2775019447

L1, L2

130nH Inductors rated at 50MHz

ML6694

11

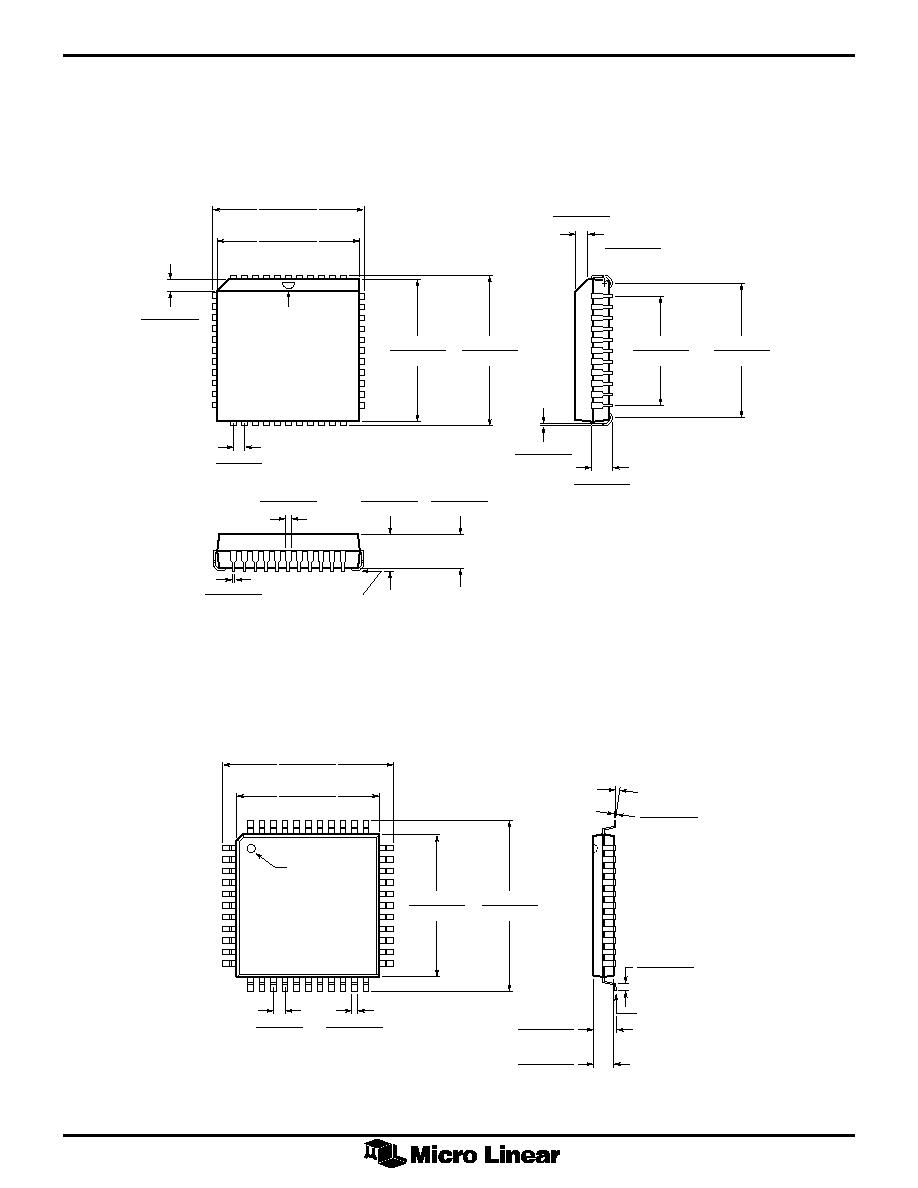

PHYSICAL DIMENSIONS

inches (millimeters)

0.100 - 0.112

(2.54 - 2.84)

PIN 1 ID

SEATING PLANE

0.685 - 0.695

(17.40 - 17.65)

0.650 - 0.656

(16.51 - 16.66)

0.013 - 0.021

(0.33 - 0.53)

0.165 - 0.180

(4.06 - 4.57)

1

0.650 - 0.656

(16.51 - 16.66)

0.685 - 0.695

(17.40 - 17.65)

12

23

34

0.590 - 0.630

(14.99 - 16.00)

0.025 - 0.045

(0.63 - 1.14)

(RADIUS)

0.050 BSC

(1.27 BSC)

0.009 - 0.011

(0.23 - 0.28)

0.042 - 0.056

(1.07 - 1.42)

0.042 - 0.048

(1.07 - 1.22)

0.026 - 0.032

(0.66 - 0.81)

0.500 BSC

(12.70 BSC)

Package: Q44

44-Pin PLCC

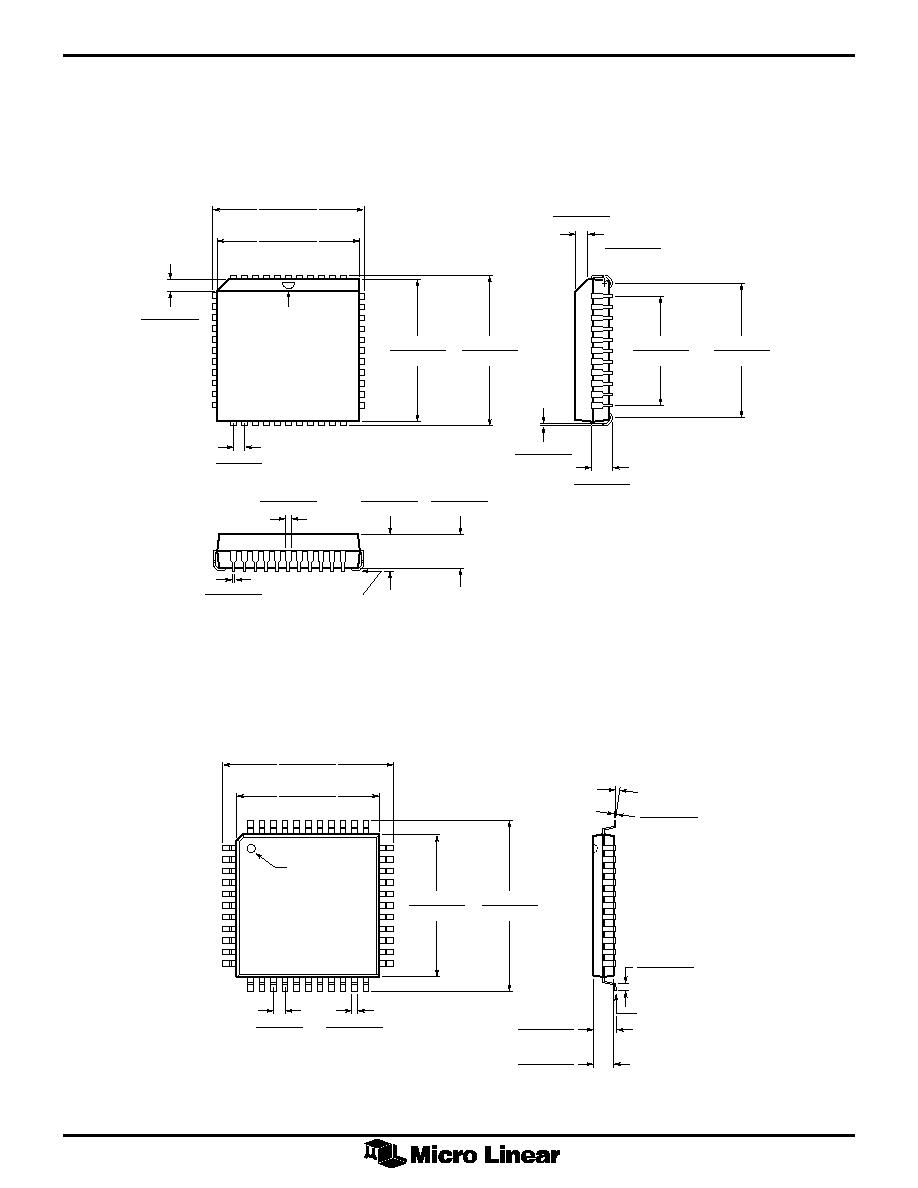

0.148 - 0.156

(3.76 - 3.96)

0.048 MAX

(1.20 MAX)

SEATING PLANE

0.472 BSC

(12.00 BSC)

0.394 BSC

(10.00 BSC)

1

0.394 BSC

(10.00 BSC)

0.472 BSC

(12.00 BSC)

12

34

23

0.032 BSC

(0.80 BSC)

PIN 1 ID

0.012 - 0.018

(0.29 - 0.45)

0.037 - 0.041

(0.95 - 1.05)

0.018 - 0.030

(0.45 - 0.75)

0.003 - 0.008

(0.09 - 0.20)

0∫ - 8∫

Package: H44-10

44-Pin (10 x 10 x 1mm) TQFP

ML6694

12

DS6694-01

2092 Concourse Drive

San Jose, CA 95131

Tel: 408/433-5200

Fax: 408/432-0295

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design.

Micro Linear does not assume any liability arising out of the application or use of any product described herein,

neither does it convey any license under its patent right nor the rights of others. The circuits contained in this

data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to

whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility

or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel

before deciding on a particular application.

ORDERING INFORMATION

PART NUMBER

TEMPERATURE RANGE

PACKAGE

ML6694CQ

0

∞

C to 70

∞

C

44-PIN PLCC (Q44)

ML6694CH

0

∞

C to 70

∞

C

44-PIN TQFP (H44-10)

(End Of Life)

© Micro Linear 1997

Micro Linear

is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940;

5,546,017; 5,559,470; 5,565,761; 5,592,128; 5,594,376; Japan: 2598946; 2619299. Other patents are pending.