PRELIMINARY DATA SHEET

VSP 94x2A

PRIMUS

Powerful Scan Rate Converter

including Multistandard

Color Decoder

Edition Oct. 24, 2001

6251-552-3PD

Micronas

-2

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

VSP 94x2A

Revision History:

10.2001 Preliminary

Previous Versions:

2.0a

2.0f

2.0k

2.1a

A22

3.0

A31

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

docservice@micronas.com

P-MQFP-80-1

P

owerful scan

R

ate converter

I

ncluding

MU

lti

S

tandard color decoder

VSP 94x2A

Micronas

1-3

Version 3.4

CMOS

Preliminary

1

General Description

The VSP 94x2A (PRIMUS) is a new component of the

Micronas MEGAVISION

�

IC set in a CMOS embedded

DRAM technology. The VSP 94x2A comprises all main

functions of a digital featurebox in one monolithic IC. The

amount of features is limited in favour of a low-cost

solution. But no trade-off has been made concerning

picture quality. The family is ideally suited to work in

conjunction with the deflection processors SDA9380

(9402/32) and DDP3315C (9412/42). In combination with

the 'digital TV decoder' MDE 9500 double-scan iDTV are

possible. The package is pin-upward compatible to other

medium-range and high-end devices of the VSP94xy

family. A 50/60Hz derivative is also available (9432, 9442).

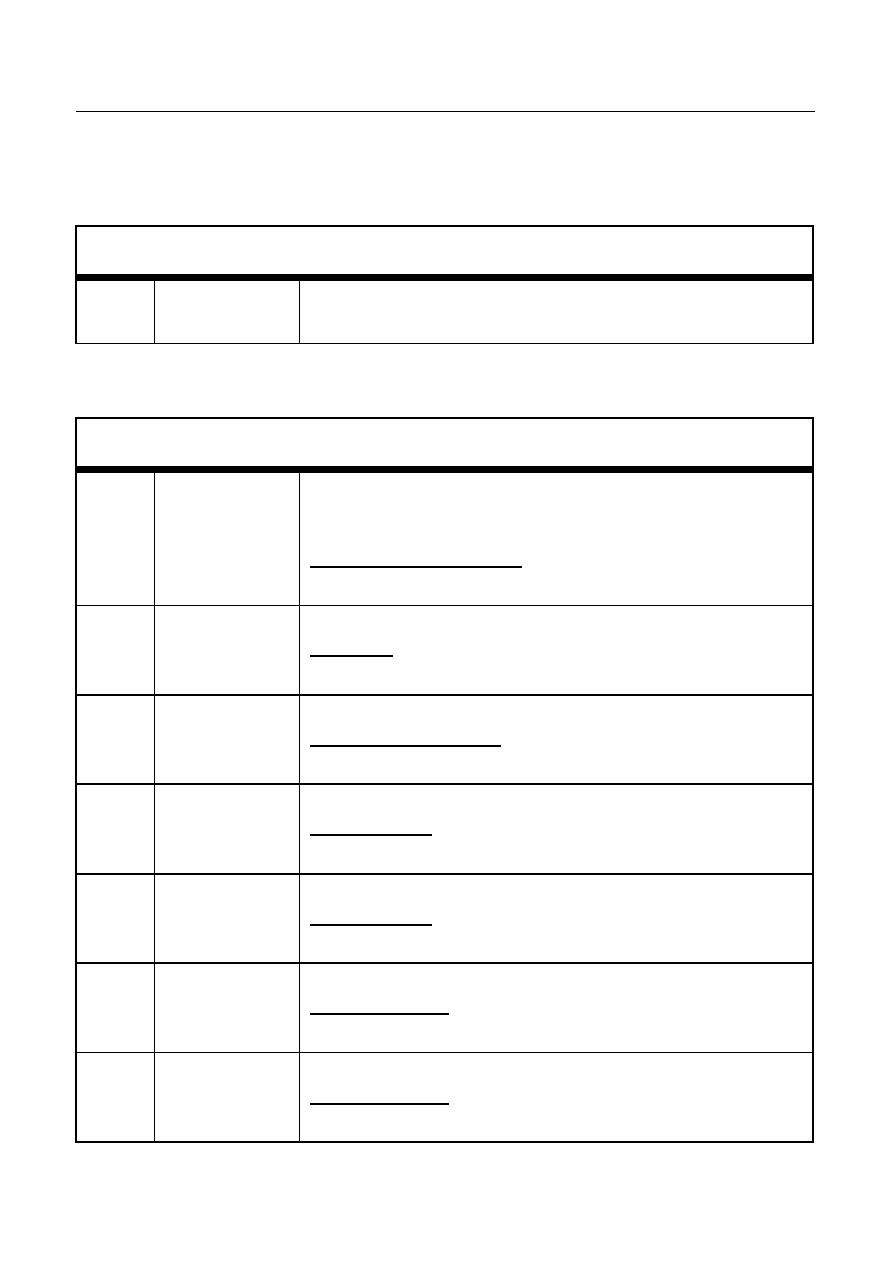

Table 1- 1

Primus' versions

Version

Scan-rate-

conversion

digital

input

digital

output

analog

output

9402A

100i/120i

(X)

1)

1)

Input and output can not be used at same time (pin sharing)

(X)

1)

X

9412A

2)

2)

under development

100i/120i

X

X

9432A

50i/60i

(X)

1)

(X)

1)

X

9442A

2)

50i/60i

X

X

The device comprises a digital multistandard color decoder, a RGB interface with fast-

blank capability (SCART), digital ITU656 input, scaling units including panorama,

embedded DRAM for upconversion, picture improvements, temporal noise reduction as

well as A/D and D/A converter.

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

General Description

Micronas

1-4

1

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

3

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

4

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

4.1

Pin list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

4.2

Pin Configuration P-MQFP80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5

System Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

5.1

CVBS Frontend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

5.1.1

Source select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

5.1.2

Signal Magnitudes and Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

5.1.3

Clamping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

5.1.4

Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

5.1.5

Chroma Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

5.1.6

Luminance Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

5.2

RGB-Frontend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

5.2.1

Source Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

5.2.2

Signal Magnitudes and Gain Control . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

5.2.3

Clamping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5.2.4

Digital Prefiltering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

5.2.5

RGB->YUV Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

5.2.6

Contrast, Brightness and Saturation Control of Input signal . . . . . . . . . .34

5.2.7

Soft Mix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

5.2.8

FBL activity and overflow detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.3

Input Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

5.3.1

Horizontal Prescaler (sample-rate-converter) . . . . . . . . . . . . . . . . . . . . .36

5.3.2

Noise Reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

5.3.3

Noise Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

5.4

Output Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

5.4.1

Horizontal Postscaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

5.4.2

Panorama Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

5.4.3

Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

5.5

Display processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

5.5.1

Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

5.5.2

Digital color transition improvement (DCTI) . . . . . . . . . . . . . . . . . . . . . . .50

5.5.3

Coarse and fine delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

5.5.4

Oversampling and DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

5.5.5

Output-Sync Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

5.5.5.1

HOUT Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

5.5.5.2

VOUT Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

5.5.5.3

BLANK Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

5.5.5.4

Background Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

General Description

Micronas

1-5

5.5.5.5

Window function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.5.6

Digital 656 input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.5.7

Digital 656 output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.6

Clock Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.6.1

Linelocked Clock Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

6

I2C-bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.1

I�C bus slave address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.2

I�C bus format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.3

I�C bus list in alphabetical order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.4

I�C bus Command Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.5

I�C bus Command Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

7

Pin schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

8

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

9

Recommended Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

10

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

11

Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

12

Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

12.1

Application overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

List of Figures

Page

Micronas

1-6

Figure 3-1

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Figure 4-1

Signal flow 940x, 943x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 4-2

Signal flow 941x, 944x, 942x . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 4-3

P-MQFP-80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Figure 4-4

Package outlines P-MQFP-80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Figure 5-1

Input selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 5-2

CVBS ADC characteristic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 5-3

CVBS, Y and C amplitude characteristics . . . . . . . . . . . . . . . . . . . . . . .19

Figure 5-4

Clamping signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Figure 5-5

NSRED characteristic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Figure 5-6

Chroma decoding overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Figure 5-7

Chroma filter characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Figure 5-8

Color killer adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Figure 5-9

IF prefilter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Figure 5-10

Filter characteristics for NTSC, PAL M and PAL N . . . . . . . . . . . . . . . .26

Figure 5-11

Filter characteristics for PAL B/G, NTSC44, PAL60 . . . . . . . . . . . . . . .27

Figure 5-12

Filter characteristics for SECAM (SECNTCH='01', 4.25 MHz) . . . . . . .27

Figure 5-13

Filter characteristics for Y/C mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 5-14

Adjustment of 'Black-' to 'Blankingvalue' at analog output. . . . . . . . . . .28

Figure 5-15

Signal and Clamping organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 5-16

Y/RGBF amplitude characteristics (with or without sync) . . . . . . . . . . .31

Figure 5-17

UV amplitude characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 5-18

RGB ADC characteristic, Fast-blank ADC with clamping (DCLMPF=0) 32

Figure 5-19

Fast-blank ADC characteristic without clamping (DCLMPF=1) . . . . . . .32

Figure 5-20

Digital Prefiltering of RGB input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 5-21

Softmix: Visualization of formulas . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Figure 5-22

Varied FBLOFFST output and static operation mode . . . . . . . . . . . . . .35

Figure 5-23

Image format before memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Figure 5-24

Y and C decimation filter characteristic for standard operation (1.5) . . .37

Figure 5-25

Temporal noise reduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Figure 5-26

Segments of LUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Figure 5-27

Predefined curve characteristics for LUT . . . . . . . . . . . . . . . . . . . . . . . .39

Figure 5-28

Expansion factor of horizontal postscaler dependent on HSCPOSC . .40

Figure 5-29

Visualization of panorama segments . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Figure 5-30

Panorama expansion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Figure 5-31

Explanation of field and display line-scanning pattern . . . . . . . . . . . . . .44

Figure 5-32

50/60 Hz interlaced to 100/120 Hz interlaced conversion (AABB). . . . .46

Figure 5-33

Block diagram of Display processing . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Figure 5-34

Block diagram peaking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Figure 5-35

Peaking filter: Bandpass and Highpass filter . . . . . . . . . . . . . . . . . . . . .48

Figure 5-36

Principles of DCTI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 5-37

DAC output signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

List of Figures

Page

Micronas

1-7

Figure 5-38

Image format behind memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Figure 5-39

Horizontal windowing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 5-40

Vertical windowing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 5-41

Horizontal and vertical windowing . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 5-42

Linelocked clock generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

Figure 5-43

Allowed operation area for clock generation . . . . . . . . . . . . . . . . . . . . .60

Figure 6-1

I�C bus clock domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Figure 7-1

Pin schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

Figure 11-1

I�C bus timing data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Figure 11-2

I�C Bus timing start/stop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

Figure 12-1

Application Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

Figure 12-2

Application Overview with SDA9380 . . . . . . . . . . . . . . . . . . . . . . . . . .153

Figure 12-3

Application Overview with DDP 3315C . . . . . . . . . . . . . . . . . . . . . . . .153

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

List of Tables

Page

Micronas

1-8

Table 1- 1

Primus' versions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

Table 4-1

Hardware compatibility and suited backend ICs . . . . . . . . . . . . . . . . . .12

Table 4- 2

Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Table 5- 1

AGC modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Table 5- 2

Clamping adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Table 5- 3

Allowed combinations for color-standard search . . . . . . . . . . . . . . . . . .23

Table 5- 4

Possible input signals for RGB Frontend . . . . . . . . . . . . . . . . . . . . . . . .29

Table 5- 5

Configurations of input signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Table 5- 6

RGB operation modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Table 5- 7

Horizontal expansion factors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Table 5- 8

Examples of panorama modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Table 5- 9

Operation modes for scan-rate conversion . . . . . . . . . . . . . . . . . . . . . .45

Table 5- 10

Peaking filter adaption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Table 5- 11

Conversion table between HCOF/BCOF and GAINHP/GAINBP . . . . . .49

Table 5- 12

Ingenious configurations of the HOUT and VOUT generator . . . . . . . .52

Table 5- 13

Display line scanning pattern sequence . . . . . . . . . . . . . . . . . . . . . . . .54

Table 5- 14

656 input / output selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Table 5- 15

656 modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Table 5- 16

Clock system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Table 5- 17

LL-PLL settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

Table 6- 1

I�C bus clock domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Table 6- 2

I�C bus register characterization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Table 6- 3

I�C register overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Features

Micronas

2-9

2

Features

� Integrated Video Matrix switch

� Up to seven CVBS inputs, up to two Y/C inputs,

� Up to three CVBS outputs (even when Y/C input)

� 9 bit amplitude resolution for CVBS, Y/C A/D converter

� AGC (Automatic Gain Control)

� Multi-standard color decoder

� PAL/NTSC/SECAM including all substandards

� Automatic recognition of chroma standard

� Only one crystal necessary for all standards

� RGB-FBL or YUV-H-V input

� 8 bit amplitude resolution for RGB or YUV

� 8 bit amplitude resolution for FBL or H

� ITU656 support (version dependent, refer to next chapter)

� ITU656 input/output

� DS656 output (double-scan '656like' output)

� Noise reduction

� Motion adaptive temporal noise reduction

� Field-based temporal noise reduction for luminance and chrominance

� Different motion detectors for luminance and chrominance or identical

� Flexible programming of the temporal noise reduction parameters

� Automatic measurement of the noise level

� Horizontal scaling of the 1f

H

signal

� Split-screen possible with additional PiP or Text processor

� Flexible digital horizontal scaling of the 2f

H

signal

� Scaling factors: 3, ... [2 pixel resolution], ..., 0.75 including 16:9 compatibility

� 5 zone panorama generator

� Embedded memory

� On-chip memory controller

� Embedded DRAM core for field memory

� SRAM for PAL/SECAM delay line

� Data format 4:2:2

� Flexible clock and synchronization concept

� Horizontal line-locked or free-running mode

� Vertical locked or free-running mode

� Scan-rate-conversion

� Simple interlaced modes (100/120 Hz): AABB, AAAA, BBBB (9402A/9412A only)

� No scan-rate-conversion modes (50/60 Hz): AB, AA, BB (9432A/9442A only)

� Flexible output sync controller

� Flexible positioning of the output signal

� Flexible programming of the output sync raster

� 'Blank signal' generation

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Features

Micronas

2-10

� Signal manipulations

� Still field

� Insertion of colored background

� Windowing

� Vertical chrominance shift for improved VCR picture quality

� Sharpness improvement

� Digital color transition improvement (DCTI)

� Peaking (luminance)

� Three D/A converters

� 9 bit amplitude resolution for Y, -(R-Y), -(B-Y) output

� 72 MHz clock frequency

� Two-fold oversampling for Anti-imaging

� Simplification of external analog postfiltering

� 1920 active pixel/per line in default configuration

� I�C-bus control (400 kHz)

� selectable I�C address

� 1.8V� 5% and 3.3V � 5% supply voltages

� P-MQFP-80 package

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Block Diagram

Micronas

3-11

3

Block Diagram

Figure 3-1

Block Diagram

13

6

I�C

inter

f

ace

(5

6

)

19

adr/tdi

s

cl

s

d

a

V

DA

C

(5

4

)

U

DA

C

(5

3

)

Y

DA

C

(5

2

)

O

F

F

SET

GA

I

N

76

2

79

GA

I

N

O

F

F

SET

O

F

F

SET

GA

I

N

AD

C1

(2

)

52

63

62

61

53

54

58

55

56

57

39

40

41

48

37

46

47

GA

IN

AD

C2

(3

)

GA

IN

S

ource

S

e

lect

(1

)

S

ource

S

e

lect

(1

6

)

38

AD

CR

(1

2

)

GA

IN

AD

CG

(1

3

)

GA

IN

AD

CB

(1

4

)

GA

IN

A

DCF

(1

5

)

GA

IN

Notc

h

Deskew

(4

)

Sy

n

c

(6

)

Co

lo

r

Decoder

(5

)

delay

control

(

P

AL

/

S

E

C

AM

)

(7

)

1H delay

18

20

Ant

i

al

ias,

Deskew

(1

7

)

Ant

i

al

ias,

Deskew

(1

8

)

Ant

i

al

ias,

Deskew

(1

9

)

Ant

i

al

ias,

Deskew

(2

0

)

test-

controller

,

memo

r

y

bist

(5

5

)

71

7

tc

lk

tms

69

70

xtal

o

s

cillator

(9

)

x

out

xin

divider

32

31

30

15

22

21

16

10

9

74

8

ITU

656

D

ecoder

(4

1

)

656hi

n/

cl

kf

2

0

656vin/

blank

CLK

F

2

0

RG

B

YU

V

or

bypass

(2

5

)

(2

7

)

Y

brightne

s

s

c

ontra

s

t

(2

6

)

U,

V

sat

u

r

at

io

n

O

ffset,

Gain

(2

9

)

(

3

0

)

soft-mix

ch

a

n

nel

mux

(3

1

)

do

w

n

sampling

2

4:4:4

4:2:2

(2

8

)

H-

pr

escaler

(3

4

)

noise

measur

e

men

t

(3

2

)

clampin

g

cor

r

ection

(2

1

)

clampin

g

cor

r

ection

(2

2

)

clampin

g

cor

r

ection

(2

3

)

DC

T

I

(4

6

)

P

eaking

(4

5

)

C

o

ar

se

Delay

4:4:4

(4

9

)

ITU656

E

n

coder

(5

1

)

8

8:8:8

(5

0

)

Fin

e

de

l

a

y

Y noise

r

e

duction

(3

8

)

UV

moti

on

detection

(3

6

)

Y motion

detection

(3

5

)

UV

noise

r

e

duction

(3

7

)

eDR

A

M

memory

controller

(3

9

)

14

23

17

27

Pix

e

lmixer

(

44)

H-

pos

ts

c

a

le

r

(4

2

)

Pa

nora

m

a

ge

ne

ra

tor

(4

3

)

V

H

avout

au

out

ayout

h

out

vout

cl

ko

u

t

v5

0

h50

v

cv

bs

o3

cvb

s

o

2

cvb

so

1

cv

bs

1

cv

bs

2

cv

bs

3

cv

bs

4

cv

bs

5

cv

bs

6

cv

bs

7

rin1

gi

n1

bi

n1

rin2

gi

n2

bi

n2

fbl2

fbl1

656c

l

k

656i

o0

656i

o1

656i

o2

656i

o3

656i

o4

656i

o5

656i

o6

656i

o7

CLAMP

CLAMP

c

l

am

pi

ng

s

i

gn

al

s

t

o

A

DCs

AG

C

g

ener

at

o

r

Y d

e

l

a

y

(8

)

PRIMUS

(A32

)

VSP9402A

VSP9432A

CLK

B

3

6

Y

U,

V

C

VBS/

Y

C

YC

SEL

Y

U,

V

Y

U

V

F

ma

i

n

in

s

e

r

t

CL

KF2

P

AD

Y

del

a

y

UV

del

a

y

UV

in

Y

in

data b

uff

er

data b

uff

er

24

res

e

t

line locked or

free-r

unnin

g

divider

li

ne-loc

k

e

d

cl

o

c

k

s

(

3

6,

72

M

H

z

)

free-running

cl

o

c

ks

(

2

0.

2

5

,

40.

5

MH

z)

c

l

ampe

d,

f

i

l

t

er

d

sy

n

c

s

i

g

n

a

l

K

c

Ky

de

t

_

bl

oc

k

.

v

s

d 1

/

.

1

0.

20

00

D

.

W

e

n

del

O

u

tput

Dat

a

Contr

o

lle

r

(5

5

)

re

a

d

con

t

ro

l

H/V-

ac

quisition

(3

3

)

In

p

u

t

Sync

Ou

tp

u

t

Sy

n

c

B

a

ck

gr

ou

nd

gen

e

r

a

t

o

r

(5

7

)

O

u

tput

Sy

n

c

C

ont

r

o

ller

(4

0

)

64

8 MH

z

DT

O

(1

0

)

LL-

P

L

L

(1

1

)

64

8 M

H

z

c

l

k

2

16 M

H

z

cl

k

li

ne

-

l

o

c

k

e

d

BL

A

N

K

BL

ANE

N

BL

ANK

FB

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Pin Description

Micronas

4-12

4

Pin Description

Figure 4-1

Signal flow 940x, 943x

Figure 4-2

Signal flow 941x, 944x, 942x

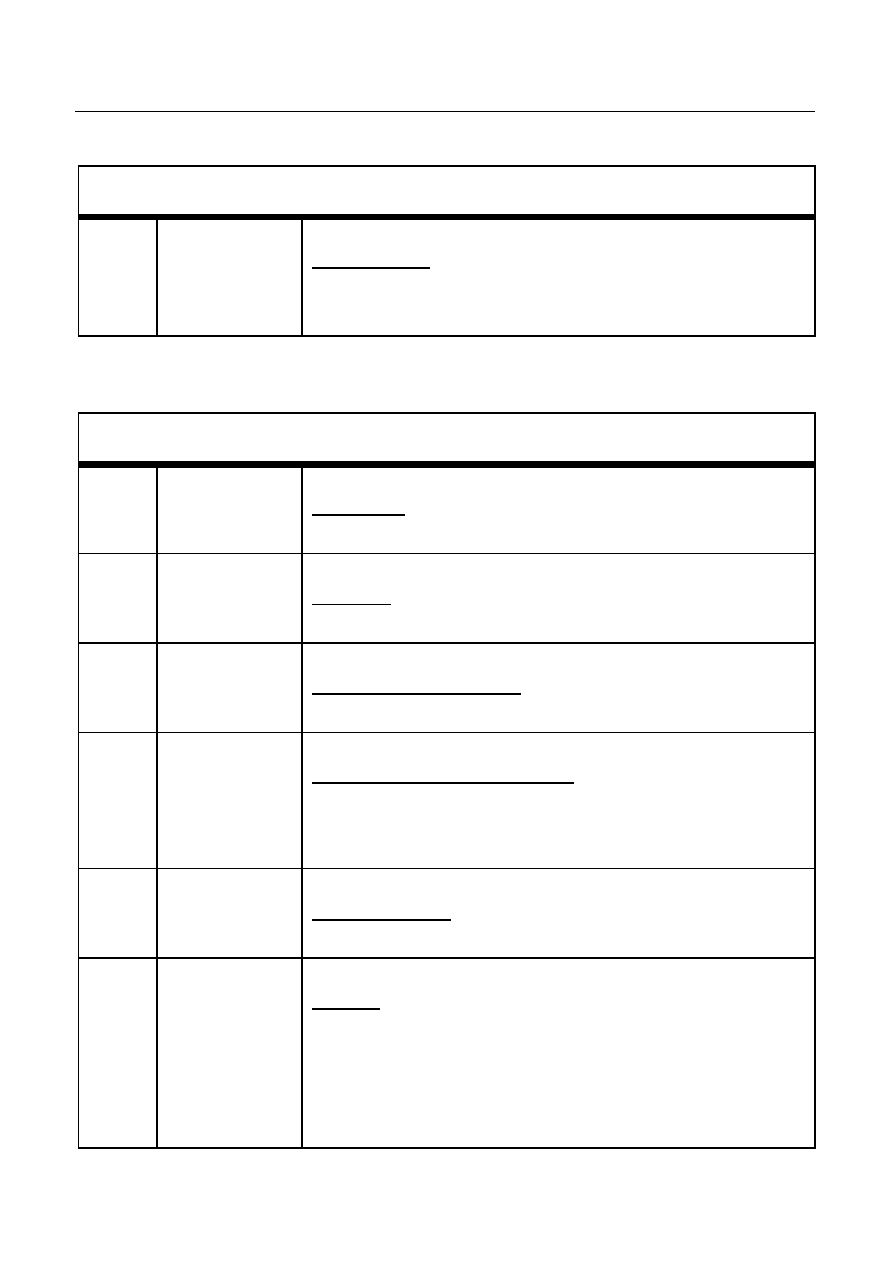

Table 4-1

Hardware compatibility and suited backend ICs

Hardware compatible

1)

1)

with some restrictions. Please refer to pin description and/or respective application note

suited backend IC

DDP3310B

DDP3315C

SDA9380

VSP 9402A, VSP 9432A

VSP 9405B, VSP 9435B

VSP 9407B, VSP 9437B

VSP 9409C

(no ITU656 input

possible)

VSP 9412A, VSP 9442A

VSP 9415B, VSP 9445B

VSP 9417B, VSP 9447B

VSP 9419C

VSP 9425B, VSP 9427B

VSP 9429C

VSP 940xA

VSP 943xA

VSP 940xB

VSP 943xB

VSP 940xA

VSP 943xA

VSP 940xB

VSP 943xB

analog

output

single-scan

656 input

analog

output

single-scan

656 output (943x)

or

double-scan

656 output (940x)

I�C selectable

VSP 941xA

VSP 944xA

VSP 941xB

VSP 944xB

single-scan

656 output (944x)

or

double-scan

656 output (941x)

single-scan

656 input

VSP 9425B

VSP 9427B

single-scan

656 input

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Pin Description

Micronas

4-13

4.1

Pin list

pin 9402/32 9412/42 I/O

9402/32

9412/42

remark

if not used,..

52

cvbs1

I

CVBS input

analog input

connect to vss

53

cvbs2

I

CVBS input

analog input

connect to vss

54

cvbs3

I

CVBS input

analog input

connect to vss

55

cvbs4

I

CVBS input or Y1

analog input

connect to vss

56

cvbs5

I

CVBS input or C1

analog input

connect to vss

57

cvbs6

I

CVBS input or Y2

analog input

connect to vss

58

cvbs7

I

CVBS input or C2

analog input

connect to vss

63

cvbso1

O

CVBS output 1

CVBS output 2

analog output

leave open

62

cvbso2

O

analog output

leave open

61

cvbso3

O

CVBS output 3

analog output

leave open

70

xin

I

Crystal connection 1

69

xout

O

Crystal connection 2

23

vout

O

vertical output

single or double

scan, dependent

on version

leave open

17

hout

O

horizontal output

leave open

3

vssdacy

i656i7

S/I

DAC (Y)

656 input

(MSB)

2

ayout

i656i6

O/I

Y output

656 input

1

vdddacy

i656i5

S/I

DAC (Y)

656 input

80

vssdacu

i656i4

S/I

DAC (U)

656 input

79

auout

i656i3

O/I

U output

656 input

78

vdddacu

i656i2

S/I

DAC (U)

656 input

77

vssdacv

i656i1

S/I

DAC (V)

656 input

leave open

76

avout

i656i0

O/I

V output

656 input

(LSB)

leave open

75

vdddacv

i656iclk S/I

DAC (V)

656 input

clock

27 MHz nom.

leave open

39

rin1

I

R or V in1

analog input

connect to vss

40

gin1

I

G or Y in1

analog input

connect to vss

41

bin1

I

B of U in1

analog input

connect to vss

37

fbl1

I

Fast Blank input 1 (H1)

analog input

connect to vss

46

rin2

I

R or V in2

analog input

connect to vss

47

gin2

I

G or Y in2

analog input

connect to vss

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Pin Description

Micronas

4-14

48

bin2

I

B of U in2

analog input

connect to vss

38

fbl2

I

Fast Blank input 2 (H2)

analog input

connect to vss

14

v

1)

I

vertical pulse for RGB input

connect to vss

6

sda

I/O

I�C-Bus data

13

scl

I

I�C-Bus clk

7

tms

I

testmode select

connect to

vdd33

19

adr / tdi

I

I�C address / test data in

24

reset

I

Reset input

reset, when low

27

clkout

O

Output clock

27 MHz

leave open

59

vdd33c

S

supply voltage CVBS

3.3 V

60

vss33c

S

supply voltage CVBS

0 V

50

vddac1

S

supply voltage CVBS1

1.8 V

51

vssac1

S

supply voltage CVBS1

0 V

64

vddac2

S

supply voltage CVBS2

1.8 V

65

vssac2

S

supply voltage CVBS2

0 V

44

vdd33rgb

S

supply voltage RGB

3.3 V

45

vss33rgb

S

supply voltage RGB

0 V

42

vddargb

S

supply voltage for RGB

1.8 V

43

vssargb

S

supply voltage for RGB

0 V

35

vddafbl

S

supply voltage for FBL

1.8 V

36

vssafbl

S

supply voltage for FBL

0 V

68

vddapll

S

supply voltage for PLL

1.8 V

66

vddd1

S

supply voltage for digital

1.8 V digital

67

vssd1

S

supply voltage for digital

0 V digital

5

vddd2

S

supply voltage for digital

1.8 V digital

4

vssd2

S

supply voltage for digital

0 V digital

28

vddd3

S

supply voltage for DRAM

1.8 V digital

29

vssd3

S

supply voltage for digital

0 V digital

34

vddd4

S

supply voltage for digital

1.8 V digital

33

vssd4

S

supply voltage for digital

0 V digital

72

vddp1

S

supply voltage for digital

3.3 V pad

73

vssp1

S

supply voltage for digital

0 V pad

pin 9402/32 9412/42 I/O

9402/32

9412/42

remark

if not used,..

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Pin Description

Micronas

4-15

Table 4- 2

Pin Description

12

vddp2

S

supply voltage for digital

3.3 V pad

11

vssp2

S

supply voltage for digital

0 V pad

25

vddp3

S

supply voltage for digital

3.3 V pad

26

vssp3

S

supply voltage for digital

0 V pad

71

tclk

I

testclock

connect to vss

18

h50

2)

O

Hout 50 Hz

(with skew)

leave open

20

v50

3)

O

Vout 50 Hz

leave open

32

656io0

I/O

Digital input / output

LSB

leave open

31

656io1

I/O

Digital input / output

leave open

30

656io2

I/O

Digital input / output

leave open

22

656io3

I/O

Digital input / output

leave open

21

656io4

I/O

Digital input / output

leave open

16

656io5

I/O

Digital input / output

leave open

15

656io6

I/O

Digital input / output

leave open

10

656io7

I/O

Digital input / output

MSB

leave open

9

656clk

I/O

Digital input / output clock

leave open

74

656hin/clkf20

I/O

separate H input for 656 /

20.25 clock output

connect to vss

and disable

clock

8

656vin/blank

4)

I/O

separate V input for 656 /

BLANK output

connect to vss

and disable

blank

49

vssd5

5)

S

supply voltage for digital

0V

connect to vss

1)

In VSP94xxB and VSP94xxC this pin is shared by v and intr (C800 controller output)

2)

In VSP94xxB and VSP94xxC this pin is shared by h50 and irq (Data-slicer-interrupt)

3)

In VSP94xxB and VSP94xxC this pin is shared by v50 and blank

4)

In 9402 A31 (and higher) and in VSP94xxA/B/C, this pin is shared by 656vin and blank

5)

This pin is not used and not bonded in VSP94xxA. The use of this pin in VSP94xxB/C will be V

SS

. For

upgradability it is recommended to not leave this pin open.

pin 9402/32 9412/42 I/O

9402/32

9412/42

remark

if not used,..

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

Pin Description

Micronas

4-16

4.2

Pin Configuration P-MQFP80

Figure 4-3

P-MQFP-80

Figure 4-4

Package outlines P-MQFP-80

PRIMUS

VSP 9402A

VSP 9432A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61

vdddacy

ayout

auo

ut

a

v

out

vssdacy

vssd2

vddd2

sda

tms

vssp2

vddp2

scl

v

hout

h50

adr/tdi

v50

(reserved)

bin1

vddargb

vssargb

vdd33rgb

rin2

gin2

bin2

vddac1

vssac1

cvbs1

cvbs2

cvbs3

cvbs4

vdd33c

vss33c

vss33rgb

cvbso1

vdda

c

2

vssac2

vd

dd1

vss

d

1

vdd

apll

xou

t

xin

vd

dp1

vss

p

1

vdd

dacv

vss

d

a

cv

vddd

acu

vssdacu

gin1

ri

n

1

fb

l2

fb

l1

v

s

s

af

bl

vd

dafbl

vssd4 vdd

d

4

v

ssd3

vdd

d

3

clkou

t

v

ssp3

vdd

p

3

vou

t

reset

cvbs5

cvbs6

cvbs7

cvbso2

cvbso3

656clk

656io7

656io6

656io5

656

io4

656

io3

656

io1

65

6io0

65

6hin/c

l

kf2

0

656vin/blank

tcl

k

65

6io2

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-17

5

System Description

All I�C bus registers mentioned are printed in bold and italics (e.g. YCDEL)

5.1

CVBS Frontend

The CVBS frontend consists of the color-decoding circuit itself, a sync processing circuit

for generation of H/V signals out of the CVBS signal, and the luminance processing. The

main task of the luminance processing is to remove the color carrier by means of a notch

filter. For PAL and SECAM operation a baseband delay line is used for U and V signals.

This can be used as comb filter in NTSC operation (only for chrominance). The RGB

input can either be used as an overlay for the CVBS channel (RGB+FBL) or as a full

master channel (RGB+H/V). The overlay is done by means of a soft-mix and can be used

e.g. for 'SCART' connector. This block incorporates a matrix (for RGB signals) which is

switched off for YUV (e.g. YPbPr) input signals. A CBS (contrast, brightness, saturation)

control makes the input signal adjustable.

5.1.1

Source select

Figure 5-1 shows the analog frontend. The analog CVBS signal can be fed to the inputs

CVBS1...7 of VSP 94x2A (amplitude 0.5...1.5V

pp

). One signal is selected via CVBSEL1

and fed to first ADC. A second signal is selected via CVBSEL2 and fed to the other ADC.

CVBS4&5 or CVBS6&7 are intended to use as separate Y/C inputs (YCSEL). After

clamping to the back porch (switchable to sync-tip clamping by CLPSTGY) both signals

are AD-converted with an amplitude resolution of 9 bit. The conversion is done using a

20.25 MHz free-running stable crystal clock. Before this the signals are lowpassed by

antialias filter. Three inputs can be looped back to output CVBSO1-3 (CVBOSEL1,

CVBOSEL2, CVBSELO3). A signal addition is performed to output a CVBS signal even

when separate Y/C signals are used at input. Inputs that are not used are roughly

clamped to fit in the allowed voltage region. For stand-by operation (power-down mode),

A/D and D/A converter are switched off by STANDBY keeping the source-selector

operational.

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-18

Figure 5-1

Input selection

5.1.2

Signal Magnitudes and Gain Control

To adjust to different CVBS input voltages a digitally working automatic gain control with

64 linear steps is implemented for input voltages in the range from 0.6 to 1.8V

pp

. For best

signal-to-noise ratio the maximum available CVBS amplitude is recommended. The

AGC behavior can be chosen from four possible modes (AGCMD):

Table 5- 1

AGC modes

When using the sync height, the A/D gain rises or falls depending on the incoming signal.

When using overflow detection only, the gain is set to maximum and is reduced

whenever an 'overflow' occurs. The signal is lowpassed so that chrominance and noise

are not used for detection. The threshold can be adjusted by PWTHD. A setting of '11'

AGCMD

AGC operation mode

00

AGC uses the height of the sync pulse as a reference and additionally

reduces amplification when ADC overflows

01

AGC uses the height of the sync pulse as a reference

10

AGC uses only ADC overflows

11

AGC is disabled and the ADC fits to the values given in AGCADJ1

CVBS 1

CVBS 2

CVBS 3

CVBS 4 / Y1

CVBS 5 / C1

CVBS 6 / Y2

CVBS 7 / C2

C

C

C

C

C

C

C

1

/

9

1

/

9

1

/

9

1

/

9

1

/

9

Filter

Filter

C

Buffer

Buffer

Buffer

ADC_CVBS1

ADC_CVBS2

CVBSO1

CVBSO2

CVBSO3

Clamping pulse of ADC_CVBS1

or ADC_CVBS2.

Shifting of signal to required

input voltage range for

CVBSO1..3

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-19

equals 511 and means an overflow of the ADC. Other settings react for a lower level.

The gain only becomes higher when a change of the channel is detected or is manually

reset by AGCRES. AGCFRZE holds the current AGC value. With AGCADJ1 and

AGCADJ2, both ADCs are gain controlled manually.

Figure 5-2

CVBS ADC characteristic

The conversion range (CR) is bigger than the signal range (SRY, SRC) leaving a

headroom for overshoots (Figure 5-3)

Figure 5-3

CVBS, Y and C amplitude characteristics

0

8

16

24

32

40

48

56

64

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

1.9

Gain Control Characteristic

AGCADJ1, AGCADJ2 (I�C)

Conversion Range [V]

511

442

144

16

0

white

black

SR

Y(1

V

n

o

m

.

)

C

R

(

1

.

2

V

nom

.)

511

446

256

64

0

SR

C(0.

89

V

n

o

m

.

)

75

% c

h

r

o

m

a

10

0% c

h

r

o

ma

bu

r

s

t

bu

r

s

t

upper headroom

lower headroom

upper headroom

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-20

5.1.3

Clamping

The clamp timing for the analog inputs is generated from its corresponding CVBS signal.

The clamping algorithm works with a split measurement pulse and a clamping pulse. The

measurement pulse is used to detect the clamping error. The clamping pulse is used to

enable current sources for reducing the detected clamping errors. The start and length

of the measurement signal is adjustable independently for both channels (CLMPST1,

CLMPD1, CLMPST2, CLMPD2). The start and length of the clamping signal is

adjustable for both channels independently (CLMPST1S, CLMPD1S, CLMPST2S,

CLMPD2S). Clamping signals for RGB-channel are not split. Clamping for these ADC

are controlled by CLMPST2S and CLMPD2S only. Clamping can be suppressed for

some lines by CLMPLOW and CLMPHIGH to ignore copyprotection information. No

external sync signals are required.

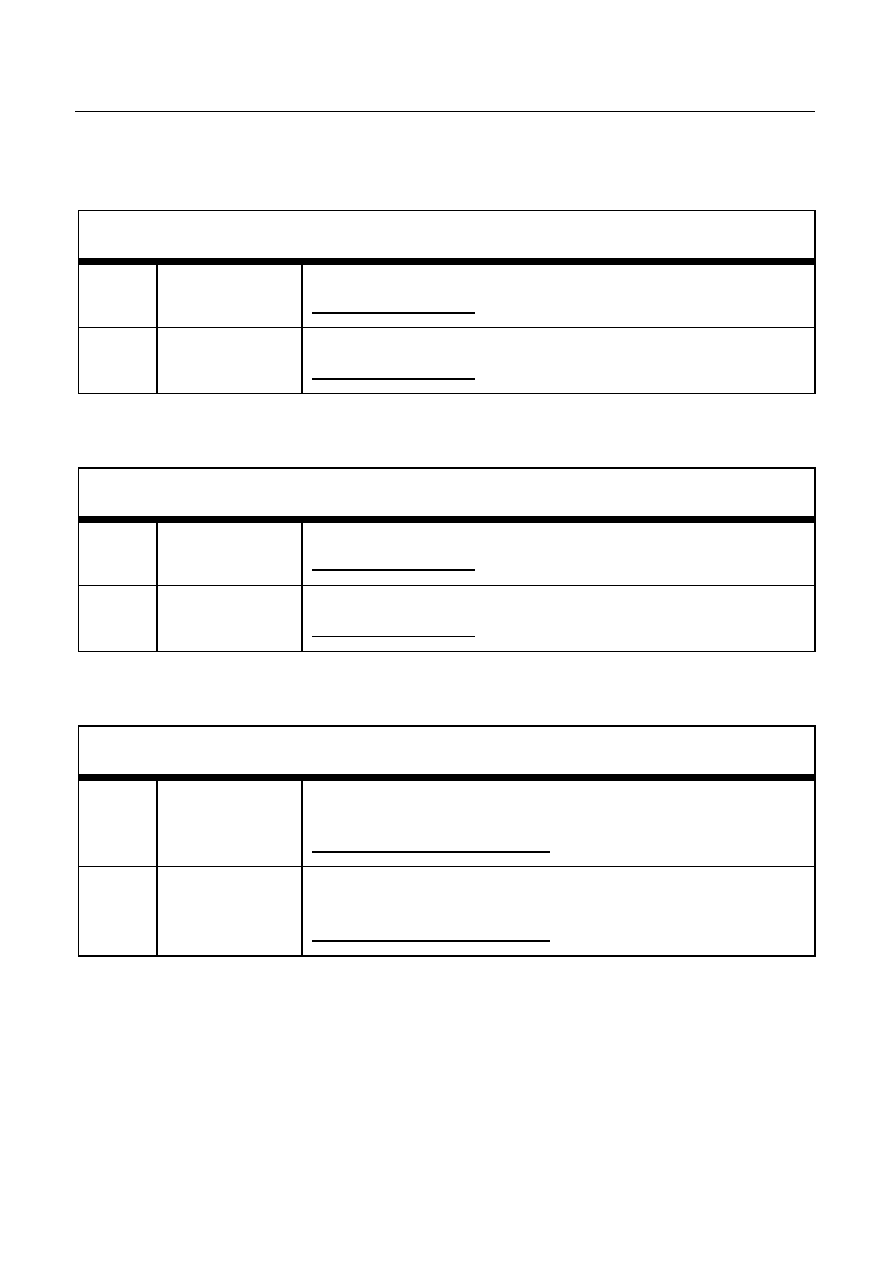

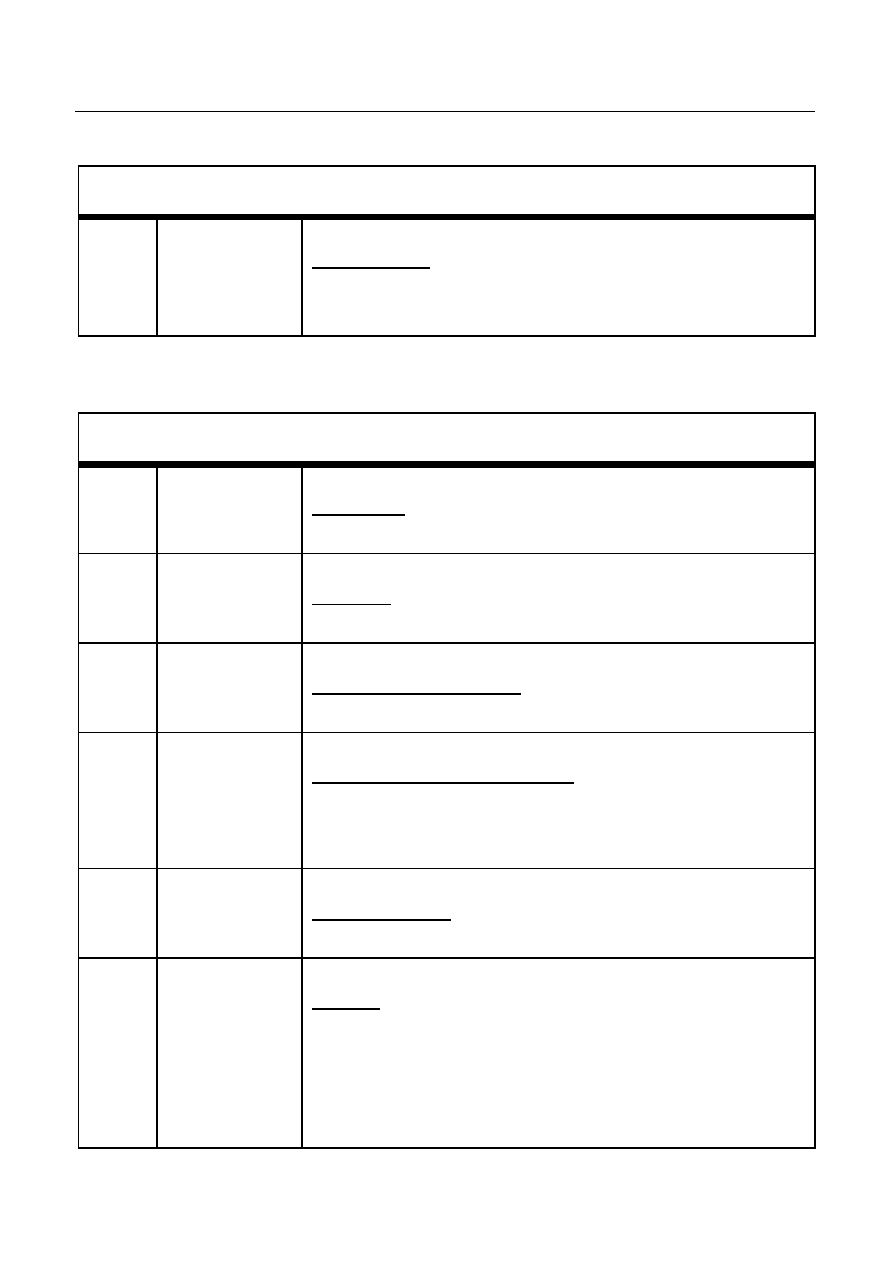

Table 5- 2

Clamping adjustment

Figure 5-4

Clamping signals

signal

description

CLMPST1 measurement pulse start for ADC1

CLMPD1

measurement pulse duration for ADC1

CLMPST1S clamping pulse start for ADC1

CLMPD1S clamping pulse duration for ADC1

CLMPST2 (measurement pulse start for ADC2)

CLMPD2

(measurement pulse duration for ADC2)

CLMPST2S measure and clamp start for RGBF-ADC (clamping start for ADC2)

CLMPD2S measure and clamp duration for RGBF-ADC (clamping duration for ADC2

CLMPD1S

CLMPST1S

CLMPST2S

CLMPD2S

CLMPD1

CLMPST1

CLMPD2

CLMPST2

CLAMP1 signals

CLAMP2 signals

CVBS/Y to ADC1

measure

clamp

for RGB

measure

clamp

C to ADC2

RGB/YUV to RGB frontend

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-21

5.1.4

Synchronization

After elimination of the high frequency components of the CVBS signal by a low pass

filter, horizontal and vertical sync pulses are separated. Horizontal sync pulses are

generated by a digital phase locked loop. The time constant can be adjusted between

fast and slow behavior in four steps (PLLTC) to accommodate different input sources

(e.g. VCR). The time-constant can be changed during normal operation without visible

picture degradation. A fine tuning of the PLL time constant can be done by NSRED.

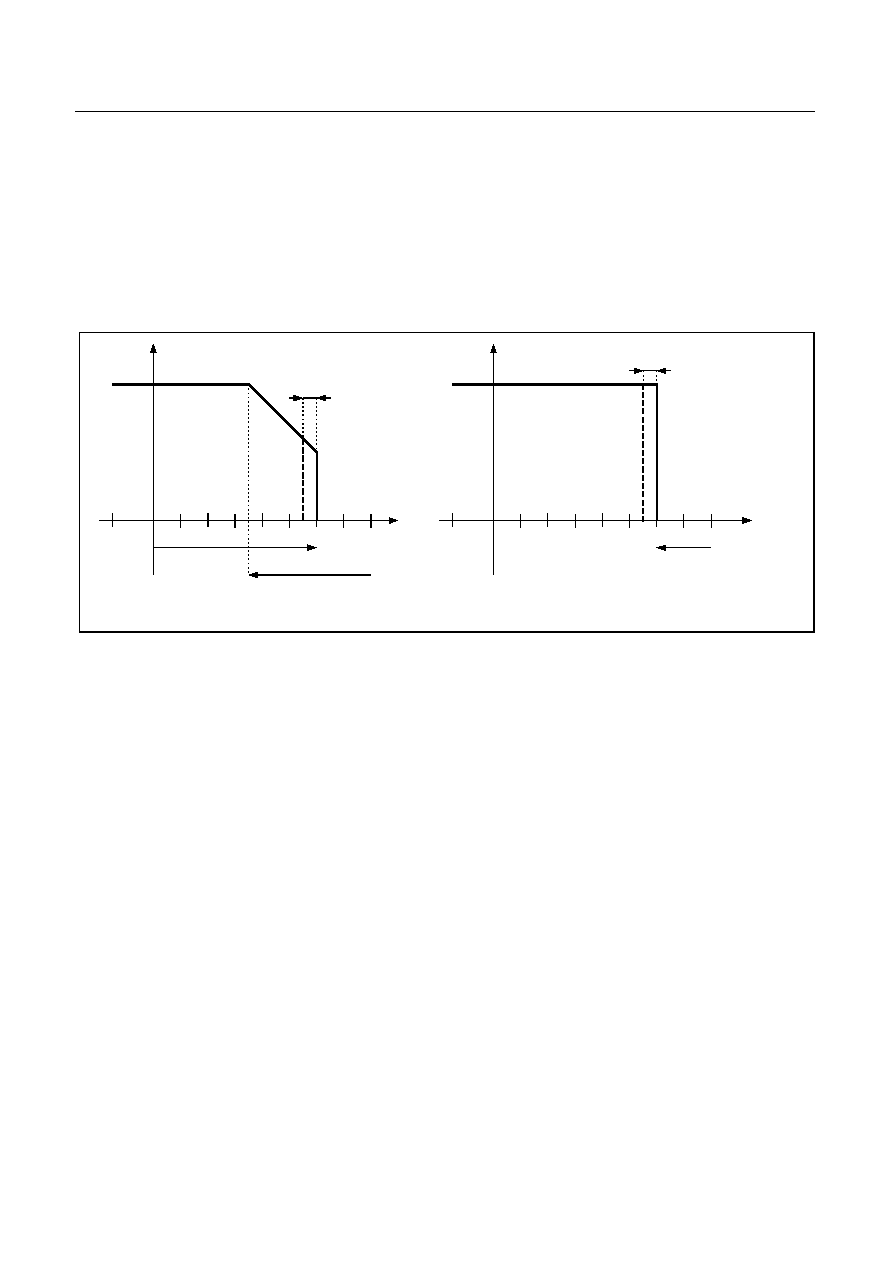

Figure 5-5

NSRED characteristic

Additionally weak input signals from a satellite dish ('fish') become more stable when

SATNR is enabled. Vertical sync pulses are separated by integration of equalizing

pulses. A vertical flywheel mode improves vertical sync separation for weak signals

(VFLYWHL, VFLYWHLMD). Additionally, v-syncs may be gated by VTHRL and VTHRH

to reject invalid v-syncs. When no input signal is connected the device switches to a free-

running mode. The device can be configured to switch-on background color when no or

only a weak signal is applied (NOSIGB). 50 Hz or 60 Hz operation for sync separation

may be forced separately or selected to work automatically (FLNSTRD)

NSRED

(I�C)

phase deviation

multiplication

before PLL

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-22

5.1.5

Chroma Decoder

Figure 5-6

Chroma decoding overview

The digital multistandard chroma decoder is able to decode NTSC and PAL signals with

a subcarrier frequency of 3.58MHz and 4.43MHz (PAL B

1)

/M/N/60

2)

, NTSC M/4.4) as

well as SECAM signals with automatic standard detection. Alternatively a standard can

be forced. The demodulation is done with a regenerated color-carrier. For use of non-

standard crystals or factory adjustment, the frequency of the free-running regenerated

subcarrier can be adjusted via SCADJ. For this purpose the crystal deviation (SCDEV)

can be read out via I�C after chroma PLL locking (indicated by SCOUTEN) and can be

stored in

�

C ROM for SCADJ. For test purposes, CPLLOF allows a loop opening of the

chroma PLL

For adjustment to the specific operational area an automatic norm detection is

selectable. Available 50 Hz color standards are PAL B, PAL N and SECAM. Available

60 Hz color standards are NTSC M, PAL M, PAL60 and NTSC44. For each line standard,

one or more color standards can be chosen for automatic standard detection. In addition,

a standard can be forced as well. Within each line standard, the standard is detected by

consequently switching from one to another. This standard detection process can be set

to slow or fast behavior (LOCKSP). In slow behavior, 25 fields are used to detect the

standard, whereas 15 fields are used in fast behavior. If unsuccessful within this time

period the system tries to detect another standard. For SECAM detection, a choice

between different recognition levels is possible (SCMIDL, SCMREL) and the evaluated

burst position is shiftable (BGPOS).

Color standard (STDET), line standard (LNSTDRD) and color killer status (CKSTAT)

can be read out.

1)

PAL B is representative for PAL B/G/H/I/N

2)

PAL60 and NTSC44 are nonstandard signals which are generated by some VCR or DVD player

IF-prefilter

filter

subsampling

chroma

filter

chroma

filter

burstakku

ACC

generator

SECAM in

colorkiller

PAL/SECAM

delay line

DTO

sin/cos

rom

SECAM

H/2 switch

PAL

loop filter

identifi-

cation

lock

detection

bell filter

FM demod.

(cordic)

deemphase

filter

CVBSin

UVout

PAL/NTSC/

SECAM

PAL/NTSC

only

SECAM

only

PAL/NTSC in

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-23

Table 5- 3

Allowed combinations for color-standard search

Figure 5-7

Chroma filter characteristics

An Automatic Chroma Control (ACC) produces a stable output for input chroma

variations from (approximately) -30 dB to +6 dB compared to nominal burst value. The

Standard

CSTAND

Standard

CSTAND

(60 Hz)

D6

D5

D4

D3

(50 Hz)

D2

D1

D0

none

0

0

0

0

none

0

0

0

PAL60

0

0

0

1

PAL N

0

0

1

PAL M

0

0

1

0

PAL B

0

1

0

NTSC M

0

1

0

0

SECAM

1

0

0

NTSC44

1

0

0

0

automatic

PAL M /

NTSC M

0

1

1

0

automatic

PAL BG /

SECAM

1

1

0

automatic

NTSC M /

NTSC44/

PAL60

1

1

0

0(!)

0

0.5

1

1.5

2

2.5

3

3.5

4

40

35

30

25

20

15

10

5

0

5

Chroma filter

Frequency (MHz)

Damping (dB)

CHRF='001100'

CHRF='001000'

CHRF='001001'

CHRF='111001'

CHRF='001110'

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-24

ACC reference value is programmable for NTSC and PAL independently (NTSCREF,

PALREF) to ensure correct color saturation. With ACCFIX, the ACC is disabled and a

constant value (dependent on NTSCREF and PALREF) is used instead. ACCFRZ holds

the current ACC value. The maximum amplification of the ACC can be limited by

ACCLIM. This results a smooth attenuation of color intensity for weak color carrier

(Figure 5-8).

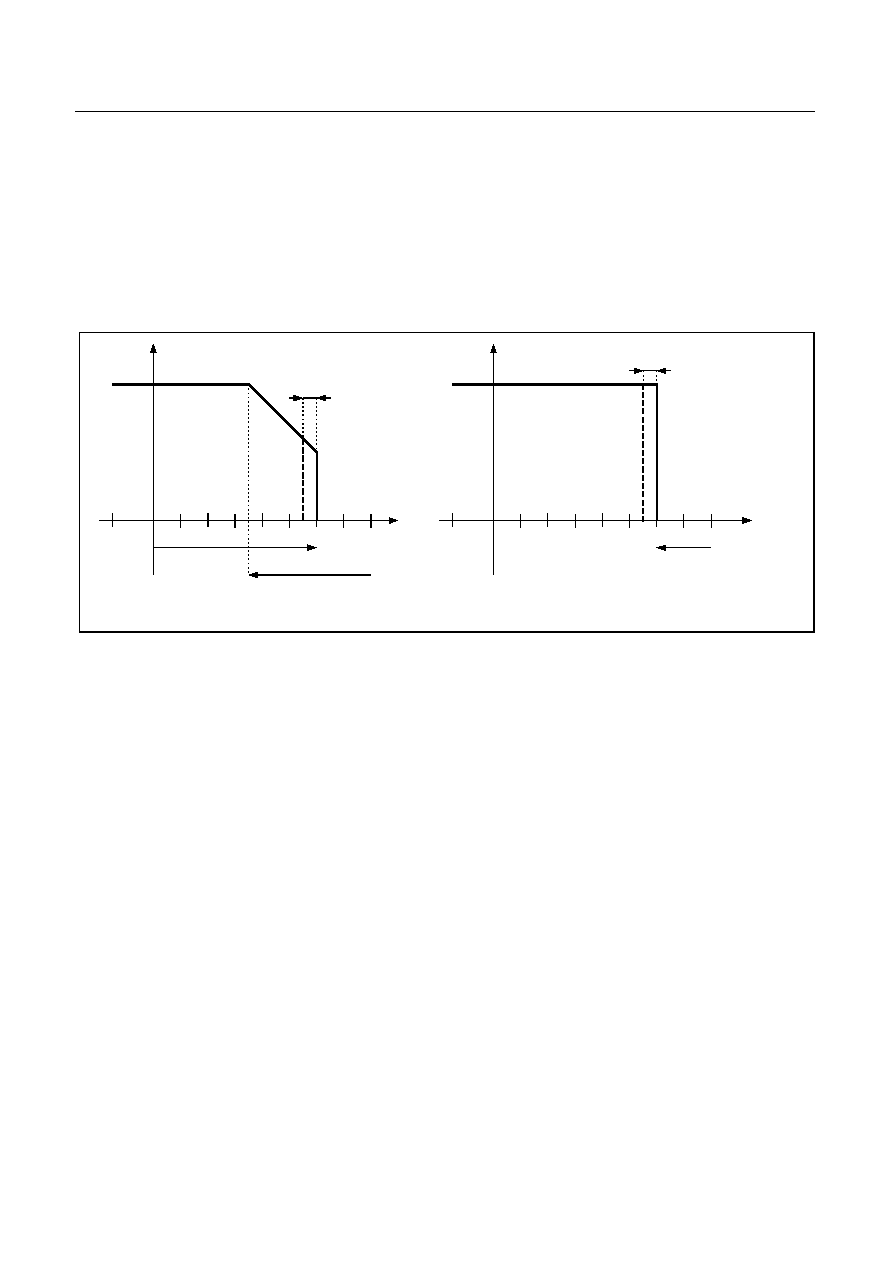

Figure 5-8

Color killer adjustment

If the chrominance signal is below an adjustable threshold (CKILL (PAL; NTSC) or

CKILLS (SECAM)) the color is switched off. To prevent on / off switching, a hysteresis

is given by CON or CONS which is the value of switching on the color.

COLON switches on the color under any circumstance. The output of the colordecoder

can be set to UV or CrCb data by CRCB. For NTSC only, the color impression (tint) can

be adjusted by the Hue Control between -88

�

and 90

�

in steps of 0.7� (HUE). Low

chrominance values (+/- 1...3 LSB) may be deleted by UV-coring (UVCOR). The Chroma

bandwidth can be adjusted by CHRF. The value of CHRF has no linear dependency on

effective bandwidth. The proper constellations are shown in Figure 5-7. A filter with

asymmetrical characteristic around the color carrier is available (IFCOMP) (Figure 5-9).

ACCLIM

CON

CKILL

U,V

attenuation of

color-carrier

+6dB

-4dB

+0dB

color off

CONS

CKILLS

U,V

attenuation of

color-carrier

+6dB

-4dB

+0dB

color off

PAL, NTSC operation

SECAM operation

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-25

Figure 5-9

IF prefilter

For SECAM mode, the de-emphasis filter can be adjusted by DEEMPFIR and

DEEMPIIR. The bell filter can be adjusted by BELLFIR and BELLIIR.

The delay between Y and C is well aligned and can also be adjusted in steps of 50ns

(YCDEL). No picture shifting occurs when switching between different color standards

(e.g. SECAM -> PAL). A delay-line is implemented for PAL and SECAM signals. It acts

as a simple chrominance comb-filter for NTSC and can be disabled by COMB. This

improves the vertical chroma resolution, but cross-color remains.

5.1.6

Luminance Processing

A luminance notch filter is implemented to reject the chroma information from luminance.

Depending on the color standard, one of three different notch characteristics is chosen

('PAL', 'NTSC', 'SECAM'). For PAL and SECAM standards, five different characteristics

are available. For NTSC standard, four different characteristics are available. They can

be selected by NTCHSEL. Alternatively, no notch should be used for Y/C input

(NOTCHOFF). The filter characteristics can be found in Figure 5-10...Figure 5-13. In

SECAM operation, the notch filter can be fixed to one frequency or toggle between 4.4

and 4.25 MHz depending on the transmitted color (Dr, Db) (SECNTCH). A simple

4.433

3.58

0

1

2

3

4

5

6

30

25

20

15

10

5

0

5

10

IF Prefilter

Frequency (MHz)

Damping (dB)

IFCOMP='000'

IFCOMP='011'

IFCOMP='001'

IFCOMP='010'

IFCOMP='100'

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-26

lowpass-filter can be enabled by LPPOST to further reduce high-frequency noise

component from the CVBS signal.

Figure 5-10 Filter characteristics for NTSC, PAL M and PAL N

3.58

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

6

30

25

20

15

10

5

0

5

characteristic for NTSC

frequency [MHz]

attenuation [dB]

'x00'

NTCHSEL=

'x01'

'x10'

'x11'

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-27

Figure 5-11 Filter characteristics for PAL B/G, NTSC44, PAL60

Figure 5-12 Filter characteristics for SECAM (SECNTCH='01', 4.25 MHz)

4.43

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

6

30

25

20

15

10

5

0

5

characteristic for PAL

frequency [MHz]

attenuation [dB]

NTCHSEL=

'000'

'100'

'010'

'011'

'001'

4.25

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

6

30

25

20

15

10

5

0

5

characteristic for SECAM (4.25 MHz)

frequency [MHz]

attenuation [dB]

NTCHSEL=

'000'

'100'

'010'

'011'

'001'

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-28

Figure 5-13 Filter characteristics for Y/C mode

For applications for which a black offset is not desired, controlling may be done using

LMOFST. The positive or negative offset is added to the Y signal before scaling.

Figure 5-14 Adjustment of 'Black-' to 'Blankingvalue' at analog output

5.2

RGB-Frontend

An analog RGB input port for an external RGB or YUV source is available. The incoming

signal is clamped to the back porch by a clamping pulse. As the memory is only able to

store a 4:2:2 picture, the YUV input signal is downconverted to 4:2:2. There are two

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

6

30

25

20

15

10

5

0

5

characteristic for Y/C

frequency [MHz]

attenuation [dB]

LPPOST=1

LPPOST=0

LMOFST='01'

LMOFST='11'

LMOFST='00'

LMOFST='10'

BLANKING BLACK

LMOFST='01'

LMOFST='11'

LMOFST='00'

LMOFST='10'

BLANKING

BLACK

Input signals without 7.5IRE offset

Input signals with 7.5IRE offset

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-29

operation modes available. The first one uses this input as an overlay input (soft mix).

The RGB or YUV signal must then be synchronized to the main CVBS/YC signal. The

so called independent mode uses RGB / YUV including sync or H/V signals. This can be

used, for example, for a DVD player or set-top-box. When using H sync from a non CVBS

input (e.g. separate H-sync) this must be indicated by HINP. The usage of separate V

sync must be set by VINP.

Table 5- 4

Possible input signals for RGB Frontend

The delay of luminance and fast-blank can be adjusted by YFDEL, and chrominance can

be delay adjusted by UVDEL. If necessary, fast-blank can be adjusted fine by FBLDEL.

Input

signal

FBL

IN

V

IN

sync separation remark

Hinp Vinp

RGB

CVBS

1)

1)

instead of FBL input, CVBS input can be used when Hinp=0

sync on CVBS

1

0

YUV

CVBS

1)

sync on CVBS

1

0

RGB

H

1)

V

sync on H

e.g. set-top-box

1

1

YUV

H

1)

V

sync on H

e.g. set-top-box

1

1

RGB

FBL

synchron to CVBS/

YC

soft mix

0

0

YUV

FBL

synchron to CVBS/

YC

soft mix

0

0

RGB

(incl. sync)

sync on G

(maybe on R/B)

no external sync

1

0

YUV

(incl. sync)

sync on Y

no external sync

e.g. DVD

1

0

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-30

Figure 5-15 Signal and Clamping organization

5.2.1

Source Select

Two inputs are available. The choice between the first or second input is made by

RGBSEL.

CLAMPSIGNALS

1

VINP

ADC2

ADC1

ADCR

ADCG

ADCB

ADCF

from CVBS

Source select

from CVBS

Source select

from RGB

Source select

from RGB

Source select

from RGB

Source select

from RGB

Source select

DATAB

DATAF

DATAG

DATAR

Data 2

Sync

processing

ADCSEL

HINP

from VINP pin

CLAMPSIGNALS2

DCLMPF

CLMPVRB

CLMPVG

CLMPVRB

AGCADJF

AGCADJB

AGCADJG

AGCADJR

AGCADJ2

AGCADJ1

CLMPV1

256

AGCMD

R Processing

G Processing

B Processing

F Processing

to soft-mix

to soft-mix

to soft-mix

to soft-mix

RBOFFSET

GOFFSET

RBOFFSET

0

1

0

1

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-31

5.2.2

Signal Magnitudes and Gain Control

Each ADC can be gain adjusted by AGCADJR, AGCADJG, AGCADJB, AGCADJF.

Figure 5-16 Y/RGBF amplitude characteristics (with or without sync)

Figure 5-17 UV amplitude characteristics

CRY

=

1.2 V

p

p

0

16

229

255

80

upper headroom

lower headroom

CRY

=

0.

84 V

p

p

0

255

upper headroom

16

229

SR

Y =

1

Vpp

SR

Y =

0.

7

V

p

p

lower headroom

C

RUV

= 0.

8 V

p

p

S

R

UV

=

0.7

V

p

p

0

16

128

240

255

212

44

C

RUV

=

0.8

V

p

p

SR

U

V

=

0.

7

Vpp

0

16

128

240

255

212

44

lower headroom

upper headroom

upper headroom

lower headroom

100% U

75% U

100% V

75% V

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-32

Figure 5-18 RGB ADC characteristic, Fast-blank ADC with clamping (DCLMPF=0)

5.2.3

Clamping

When using the dynamic softmix-mode with fast-blank, clamping of fast-blank input must

be disabled by DCLMPF. The analog clamping value of red and blue input (V and U

resp.) can be adjusted by CLMPVRB. The analog clamping value of green input (Y

resp.) can be adjusted by CLMPVG. Depending on the input signal format (YUV, RGB,

sync signal or not) these bits must be set accordingly. On the digital side, a correction of

the analog clamping value must be performed to reconstruct the blacklevel. This is

achieved by RBOFST and GOFST.

Figure 5-19 Fast-blank ADC characteristic without clamping (DCLMPF=1)

0

8

16

24

32

40

48

56

64

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

Gain Control Characteristic

AGCADJR, AGCADJG, AGCADJB, AGCADJF (I�C)

Conversion Range [V]

0

8

16

24

32

40

48

56

64

0.2

0.1

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

DC Gain Control Characteristic

AGCADJF (I�C)

Conversion Range [V]

ADC output=255

ADC output=0

conversion range

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-33

Table 5- 5

Configurations of input signals

5.2.4

Digital Prefiltering

A digital prefiltering can be enabled. This reduces the bandwidth of very steep input

signals, such as a display of characters. A band limitation is required, because the

succeeding deskewing filter performs best below 14 MHz. The filtering is performed in

all four channels and can be disabled by AABYP. For signal conversion to 4:2:2, an

additional chrominance lowpass can be enabled by CHRSF. The deskewing filter can be

disabled by SKEWSEL. This is necessary when using the HOUT50-pin in connection

with a Micronas picture-in-picture device (e.g. SDA938x, SDA948x, SDA958x). In this

application, the RGB input (in1, in2, in3) of the PiP can not be used for other RGB signals

(e.g. 'SCART' is not possible).

Figure 5-20 Digital Prefiltering of RGB input

mode

CLMPVG

CLMPVRB

GOFST

RBOFST

DCLMPF

YUV, sync on Y

80

128

64

128

don't care

YUV, sync on H,V

16

128

0

128

0 (clamping enabled)

RGB, sync on G

80

16

64

0

don't care

RGB, sync on RGB

80

80

64

64

don't care

RGB, sync on H,V

16

16

0

0

0 (clamping enabled)

RGB with fast-blank,

synchron to CVBS

16

16

0

0

1 (clamping disabled)

YUV with fast-blank,

synchron to CVBS

16

128

0

128

1 (clamping disabled)

3

0

5

10

15

20

40

30

20

10

0

10

RGB-prefiltering

Frequency [MHz]

attenuation [dB]

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-34

5.2.5

RGB->YUV Matrix

RGB or YUV signals are selected by YUVSEL. The matrix coefficients are set according

to ITU recommendations.

Formula 5-6 RGB to YUV matrix

5.2.7

Contrast, Brightness and Saturation Control of Input signal

The YUV signal can be manipulated in order to fit to the main channel. The contrast can

be adjusted between 0 and 1.97 in 64 steps (CONADJ). The brightness is adjustable in

255 steps (BRTADJ). Due to the independent chroma adjustment of U and V (64 steps

each, USAT, VSAT), UV as well as CrCb input signals can both be displayed correctly.

5.2.8

Soft Mix

The soft-mixing is done by means of alpha-mixing. Alpha is derived from the fast blank

input (FBL), which indicates a signal insertion. The value of

is between '0' and '128'.

'0' means that only the main signal is fed through to the output. '128' means that only the

inserted signal becomes visible. Obviously the formula is:

The mixing is done once for the luminance and once for the chrominance in the

subsampled domain (4:2:2). To fix the displayed picture to each main (CVBS) channel,

RGB channel or softmix-mode, MIXOP is used. Two operation modes are possible

(SMOP). The first is the static operation mode where Fast-blank input has no effect.

Considering MIXGAIN=3,

is obtained by

The function is printed in Figure 5-22 (right). The mixing is only controlled by

FBLOFFST.

The dynamic mode is used for mixing which is dependent on FB input. FB is the

preprocessed digitized fast-blank input in the range from 0...127.

FBL manipulation is done both for luminance and chrominance FBL signal.

Y

U

V

R

G

B

0,299 0,587 0,114

0,147

�

0,289

�

0,436

0,615

0,515

�

0,100

�

=

out

YUVmain 128

�

(

)

YUVinserted

+

128

-------------------------------------------------------------------------------------------------------------

=

158 3 FBLOFFST

limited to 0 and 128

[

]

�

=

MIXGAIN FB FBLOFFST 2

�

(

)

2

----------------------------------------------------------------------------------------- 64

limited to 0 and 128

[

]

+

=

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-35

Table 5- 6

RGB operation modes

Figure 5-21 Softmix: Visualization of formulas

There is a great variety of FBL signal manipulations. First, there is a delay adjustable by

FBLDEL in the range of -2...4 clock cycles. Then an offset is applied to the FBL signal

(FBLOFFST). The result is multiplied by an adjustable factor (MIXGAIN).

Figure 5-22 Varied FBLOFFST output and static operation mode

MIXOP

SMOP

Softmix-mode

00

0

dynamic Soft-Mix (DECTWO must be set to '1')

00

1

static Soft-Mix (DECTWO must be set to '1')

01

x

only RGB/YUV path visible

10

x

only CVBS path visible

11

x

(reserved)

0

64

128

10

0

10

20

30

40

50

60

70

80

90

100

110

120

130

SOFTMIX GAIN

FB

AL

PHA

0

64

128

0

50

100

SOFTMIX

ALPHA

SOFTM

I

X OUTPUT [%

]

0

-2 -3

-6

2

3

6

0

128

10

53

0

16

32

48

64

10

27

64

101

138

Static mixer mode

FBOFFST

AL

PHA

0

64

128

10

0

10

20

30

40

50

60

70

80

90

100

110

120

130

SOFTMIX GAIN

FB

ALP

H

A

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-36

5.2.9

FBL activity and overflow detection

It is important to know whether the FBL input is used or not. Therefore a detection circuit

gives information via the I

2

C bus to the microcontroller. The circuit uses the FBL value

as input. If it is greater than a threshold for one or five clock cycles (FBLCONF), the I�C

register FBLACTIVE is set. This register is reset when it is read by the microcontroller.

PFBL, PG, PR, PB indicate an overflow of the corresponding ADC (upper limit:

ADC=255) exceeding 5 clock cycles duration. These signals are also set by overflow and

reset by I�C reading only.

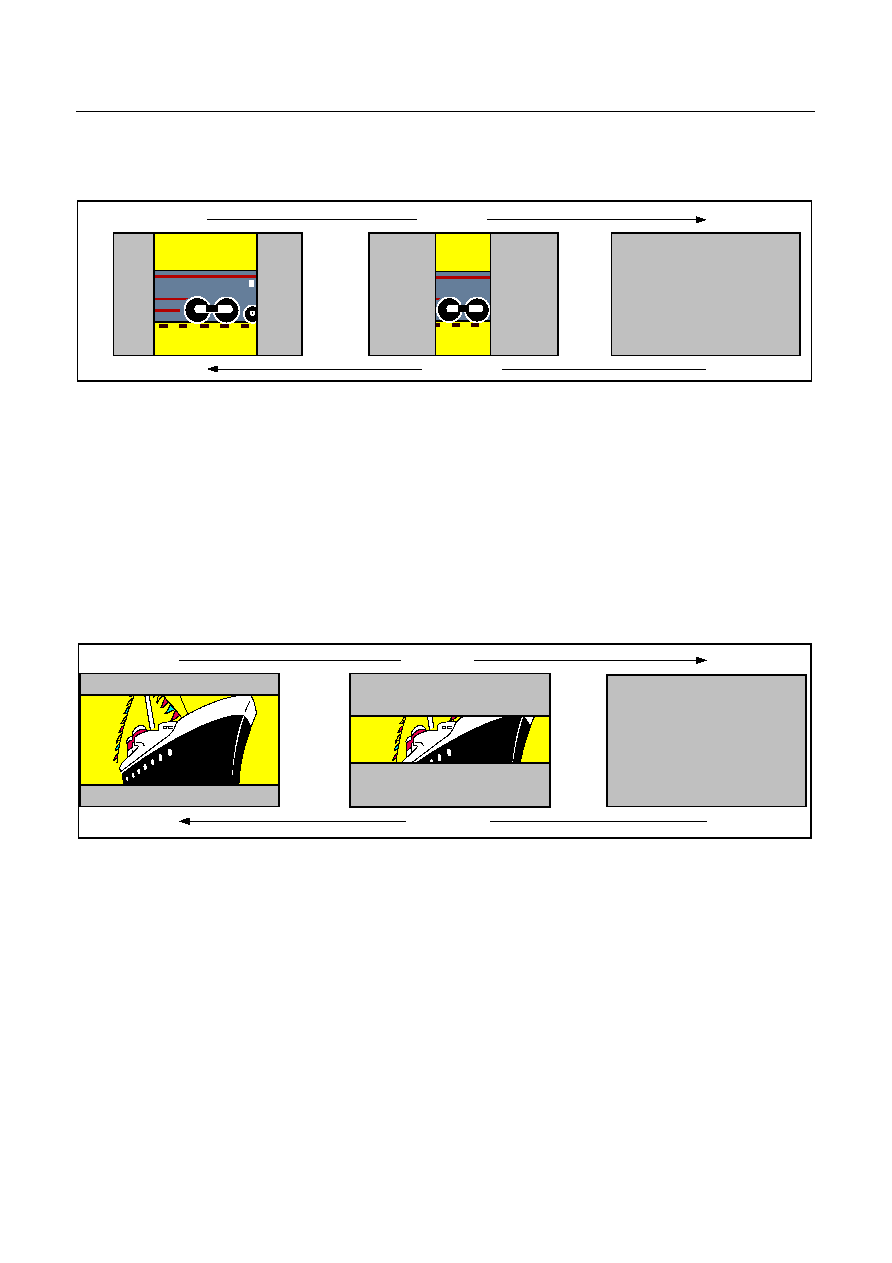

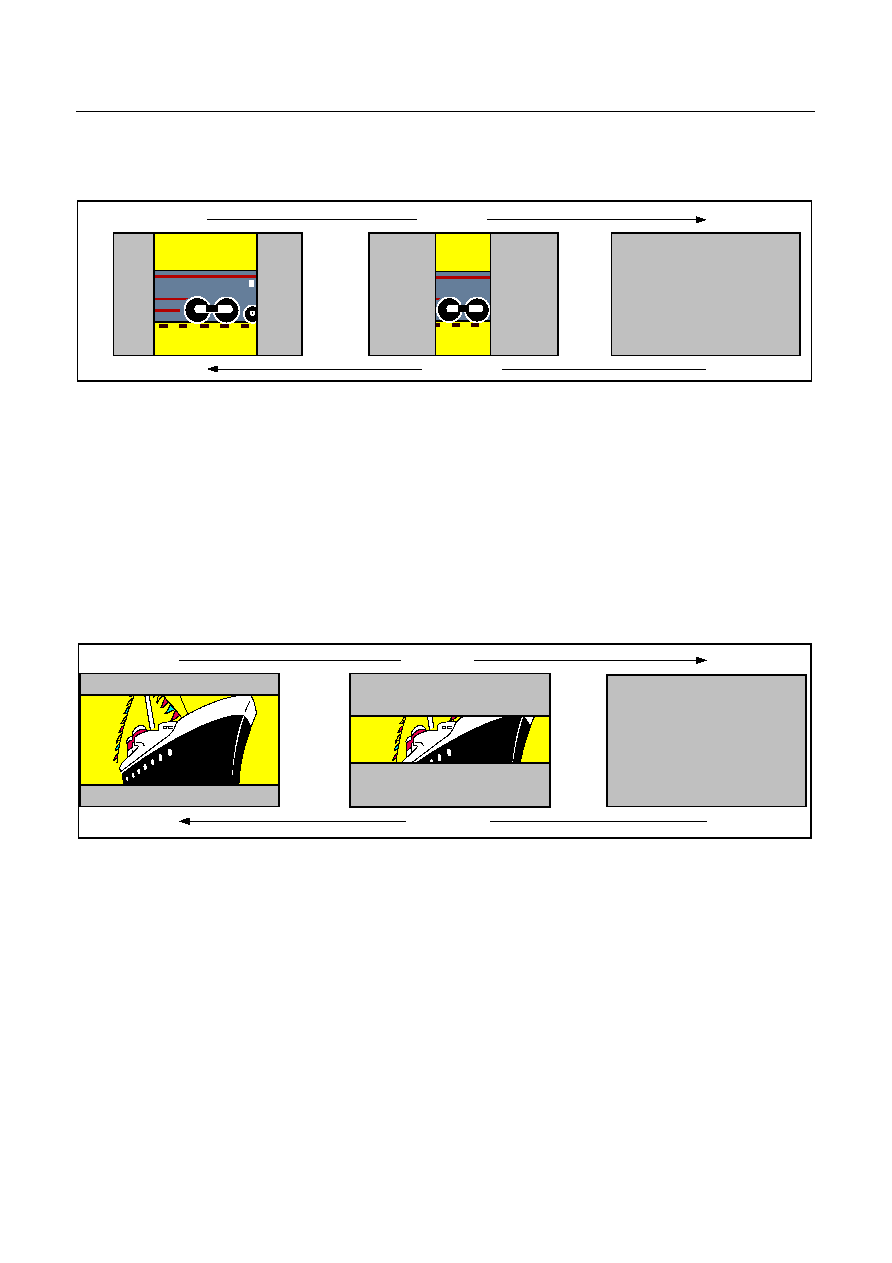

5.3

Input Processing

Figure 5-23 Image format before memory

5.3.1

Horizontal Prescaler (sample-rate-converter)

The main application is the conversion of the data coming from the 40.5/20.25MHz pixel

clock domain down to the number of pixels stored in the memory (factor 2/3). Generally

the number of incoming pixels can be decimated by a factor between 1 and 64 in a

granularity of 2 output pixels. The horizontal scaler reduces the number of incoming

pixels by subsampling. To prevent the introduction of alias distortion low pass filters are

used for luminance and chrominance processing (Figure 5-24). In case of ITU656 input,

the lowpass filter must be disabled by HAAPRESC.

The horizontal prescaler consists of two main subsampling stages. The first stage is a

scaler for rational decimation factors in a range of 1 to 2, controlled by HSCPRESC. The

APPLIP

(active

pixel per

line input)

HSYNC

NALPFIP

(not active

lines input)

ALPFIP

(Active lines

input)

Complete picture area

NAPPLIP

(not active

pixel per

line input)

Active picture

VSY

N

C

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-37

second stage is a MTA (moving target average) filter for integer decimation factors

(1,2,3,4...32), controlled by HDCPRESC. Due to its architecture the MTA filter

automatically adapts its low pass filter characteristic to the used subsampling factor.

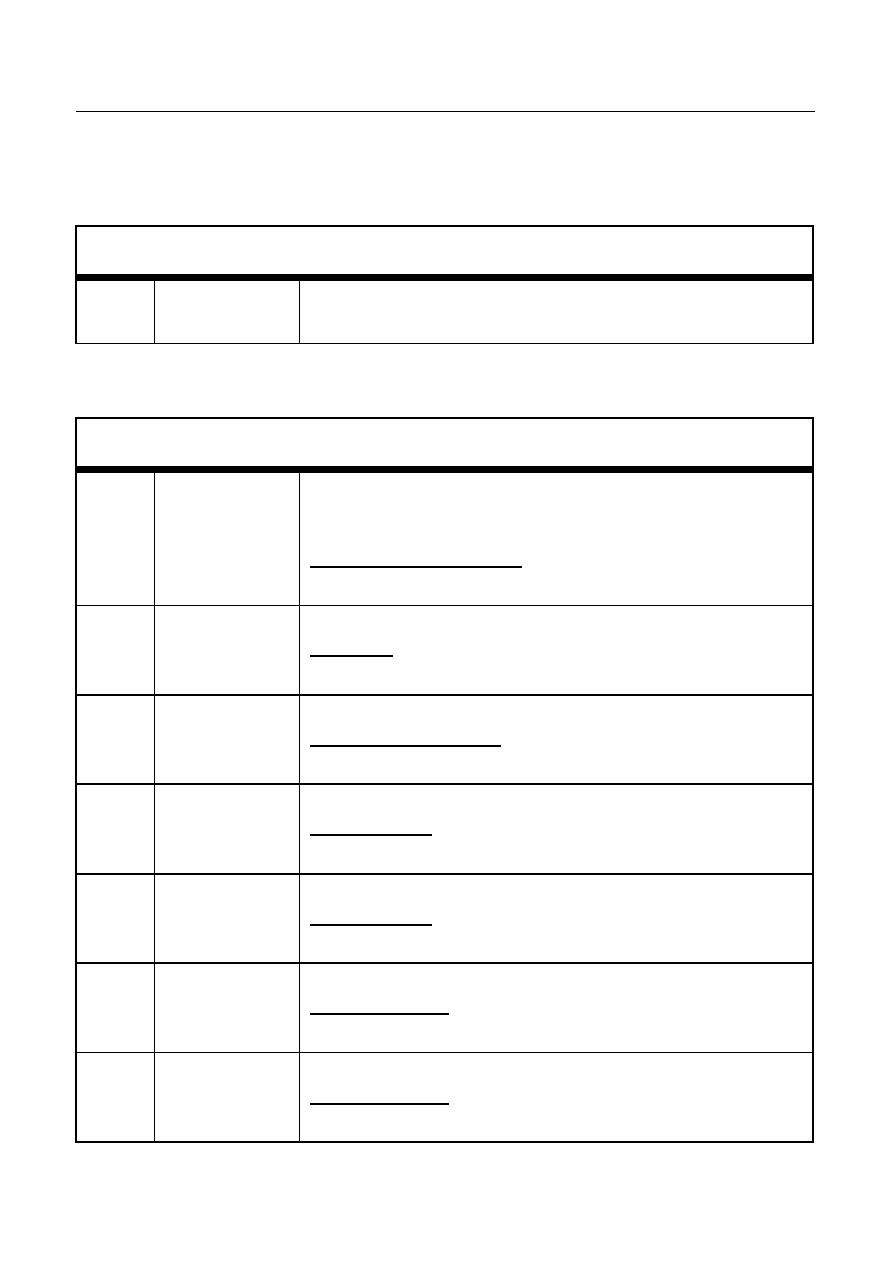

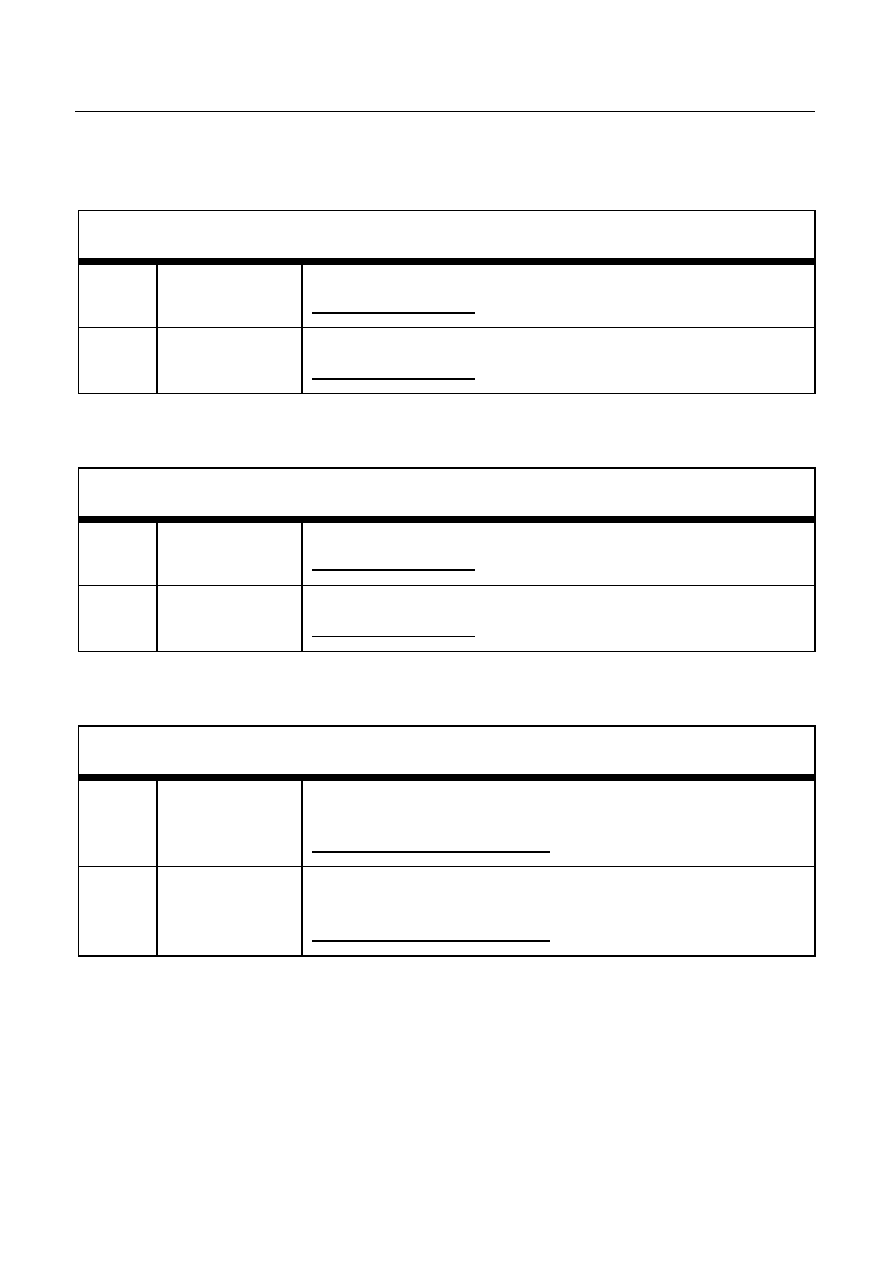

Figure 5-24 Y and C decimation filter characteristic for standard operation (1.5)

5.3.2

Noise Reduction

The Figure 5-25 shows a block diagram of the motion adaptive temporal noise reduction

(first order IIR filter). The structure of the temporal motion adaptive noise reduction is the

same for luminance as for chrominance signal. Noise reduction is enabled by NRON.

Figure 5-25 Temporal noise reduction

The equation below describes the behavior of the temporal adaptive noise reduction

filter. The same equation is valid for the chrominance signal. Depending on the motion

in the input signal, the K-factor Ky (Kuv) is adjustable between 0 (no motion) and 15

3

0

1

2

3

4

5

6

7

8

9

10

40

35

30

25

20

15

10

5

0

5

Y decimation filter

Frequency (MHz)

Attenuation (dB)

3

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

40

35

30

25

20

15

10

5

0

5

UV decimation filter

Frequency (MHz)

Attenuation (dB)

motion

detection Y

LUT Y

noise

reduction Y

Ky

TNRCLY

TNRSxY

Y

in

Y

delay

Y

in

Y

delay

Y

out

motion

detection C

LUT C

noise

reduction C

Kc

TNRCLC

TNRSxC

UV

in

UV

delay

UV

in

UV

delay

UV

out

TNRABS

TNRSEL

NRON

Kuv

VSP 94x2A (A32)

Preliminary Data Sheet 10.2001

System Description

Micronas

5-38

(motion) by the motion detector. The K-factor for the chrominance filter can be either Ky

(output of the luminance motion detector, TNRSEL=0) or Kuv (output of the chrominance

motion detector, TNRSEL=1). The delay of the feedback path is a field delay.

The output of the motion detector is weighted TNRCLC and TNRCLY. The output is

mapped to the values Ky and Kc by look-up-tables (LUT Y and LUT C). The input value