Data Sheet

28236-DSH-001-B

May 2003

CN8236

ATM ServiceSAR Plus with xBR Traffic Management

The CN8236 Service Segmentation and Reassembly Controller integrates ATM terminal

functions, PCI Bus Master and Slave controllers, and a UTOPIA level 1 or 2 interface

with service-specific functions in a single package for AAL0, 3/4, and 5 operations.

The ServiceSAR Controller generates and terminates ATM traffic and automatically

schedules cells for transmission. The CN8236 is targeted at 155 Mbps throughput

systems where the number of VCCs is relatively large, or the performance of the overall

system is critical. Examples of such networking equipment include Routers, Ethernet

switches, ATM Edge switches, or Frame Relay switches.

Service-Specific Performance Accelerators

The CN8236 incorporates numerous service-specific features designed to accelerate

and enhance system performance. As examples, the CN8236 implements Echo

Suppression of LAN traffic via LECID filtering, and supports Frame Relay DE to CLP

interworking.

Advanced xBR Traffic Management

The xBR Traffic Manager in the CN8236 supports multiple ATM service categories. This

includes CBR, VBR (both single and dual leaky bucket), UBR, GFR (Guaranteed Frame

Rate), and ABR. The CN8236 manages each VCC independently. It dynamically

schedules segmentation traffic to comply with up to 16+CBR user-configured

scheduling priorities for the various traffic classes. Scheduling is controlled by a

Schedule table configured by the user and based on a user-specified time reference.

ABR channels are managed in hardware according to user-programmable ABR

templates. These templates tune the performance of the CN8236's ABR algorithms to a

specific system's or network's requirements.

≠Continued≠

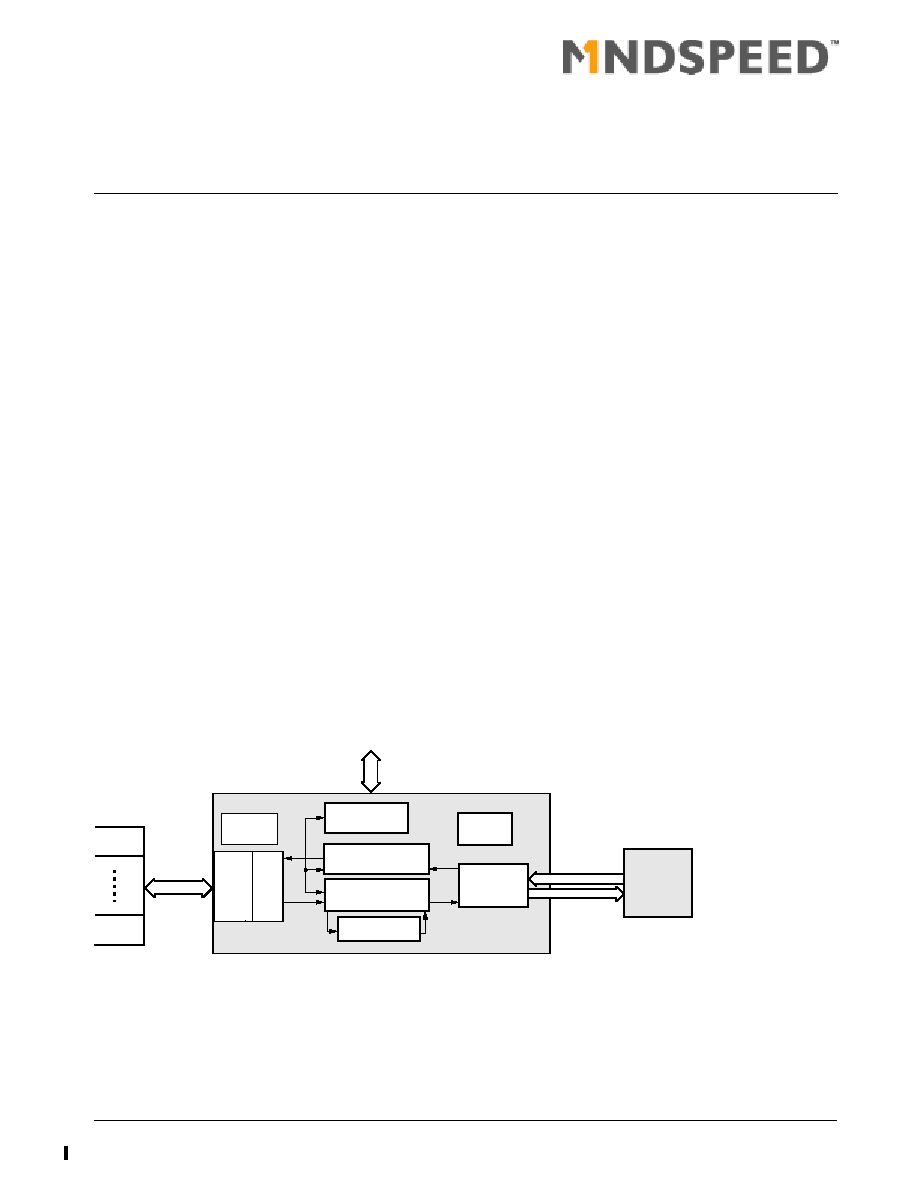

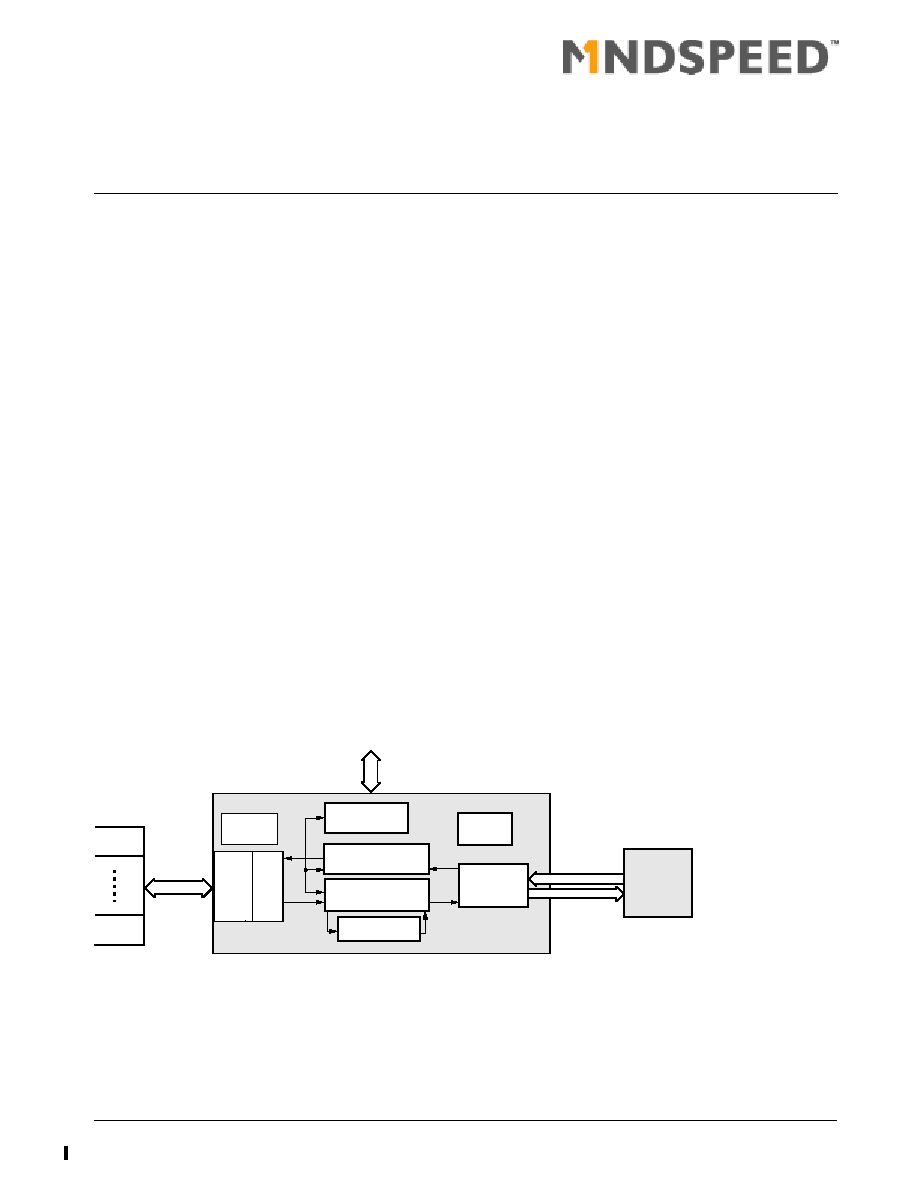

Functional Block Diagram

Multi-client

PCI Bus

Timer

Counters

Local Bus

PCI

Master/

Slave

DMA

Co-

Proc'r

Local Memory

Interface

Segmentation

Coprocessor

Reassembly

Coprocessor

CBR, VBR, ABR,

UBR, GFR

Traffic Manager

Patent Pending

Rx/Tx

UTOPIA

Master/Slave

Control/

Status

CN8236

CN8250

PHY

Device

Cell

FIFO

Distinguishing Features

Service-Specific Performance

Accelerators

∑

LECID filtering and echo suppression

∑

Dual leaky bucket based on CLP

(frame relay)

∑

Frame relay DE interworking

∑

Internal SNMP MIB counters

∑

IP over ATM; supports both CLP0+1

and ABR shaping

Flexible Architectures

∑

Multi-peer host

∑

Direct switch attachment via reverse

UTOPIA

∑

ATM terminal

≠ Host control

≠ Local bus control

∑

Optional local processor

≠Continued≠

© 1999-2003,

Mindspeed TechnologiesTM, a Conexant business

All Rights Reserved.

Information in this document is provided in connection with Mindspeed Technologies ("Mindspeed") products. These materials are

provided by Mindspeed as a service to its customers and may be used for informational purposes only. Mindspeed assumes no

responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at

any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Mindspeed's Terms and Conditions of Sale for such products, Mindspeed assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING

TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE

ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE

MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL

DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE

OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or

selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any

damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Mindspeed TechnologiesTM, the MindspeedTM logo, and "Build It First"TM.

Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties.

Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Mindspeed Technologies Legal Information posted at

www.mindspeed.com

which is incorporated by reference.

28236-DSH-001-B

Mindspeed Technologies

TM

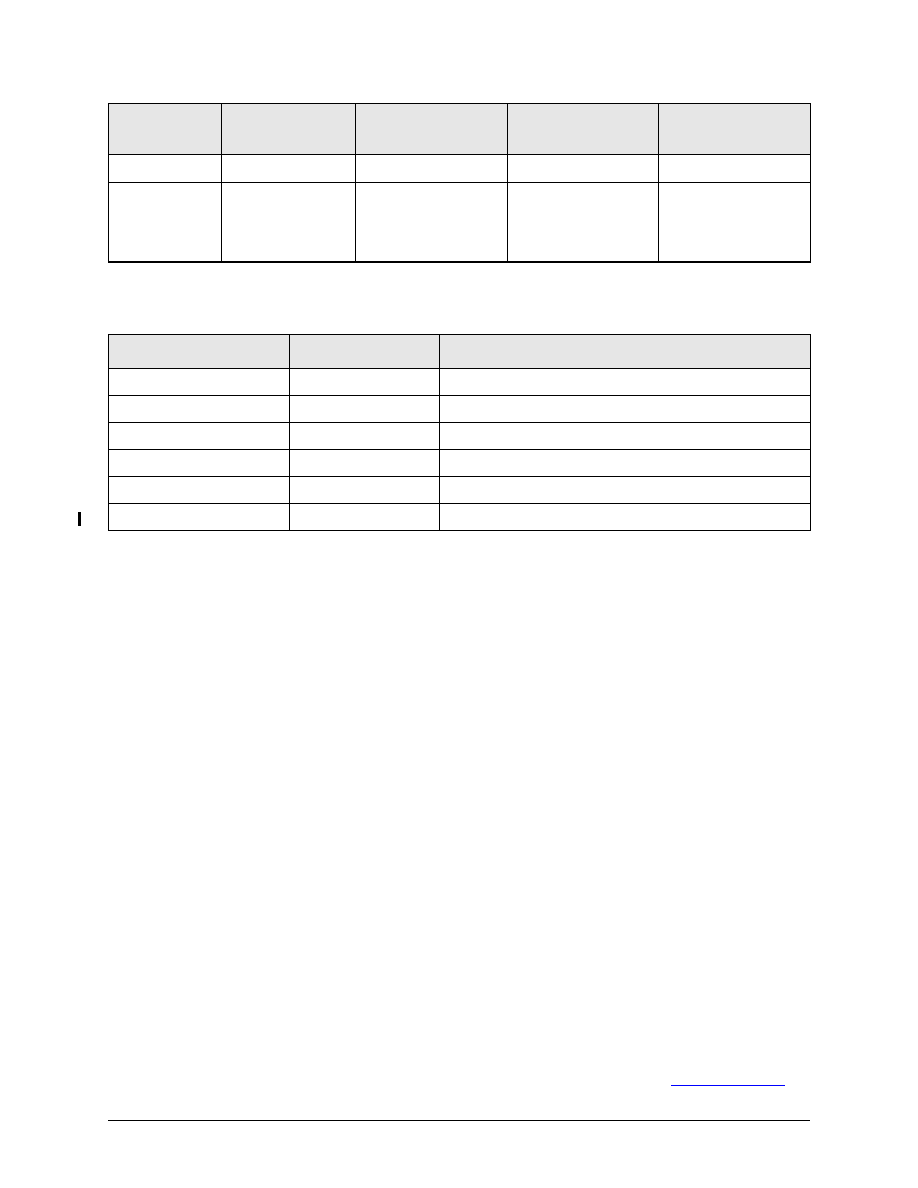

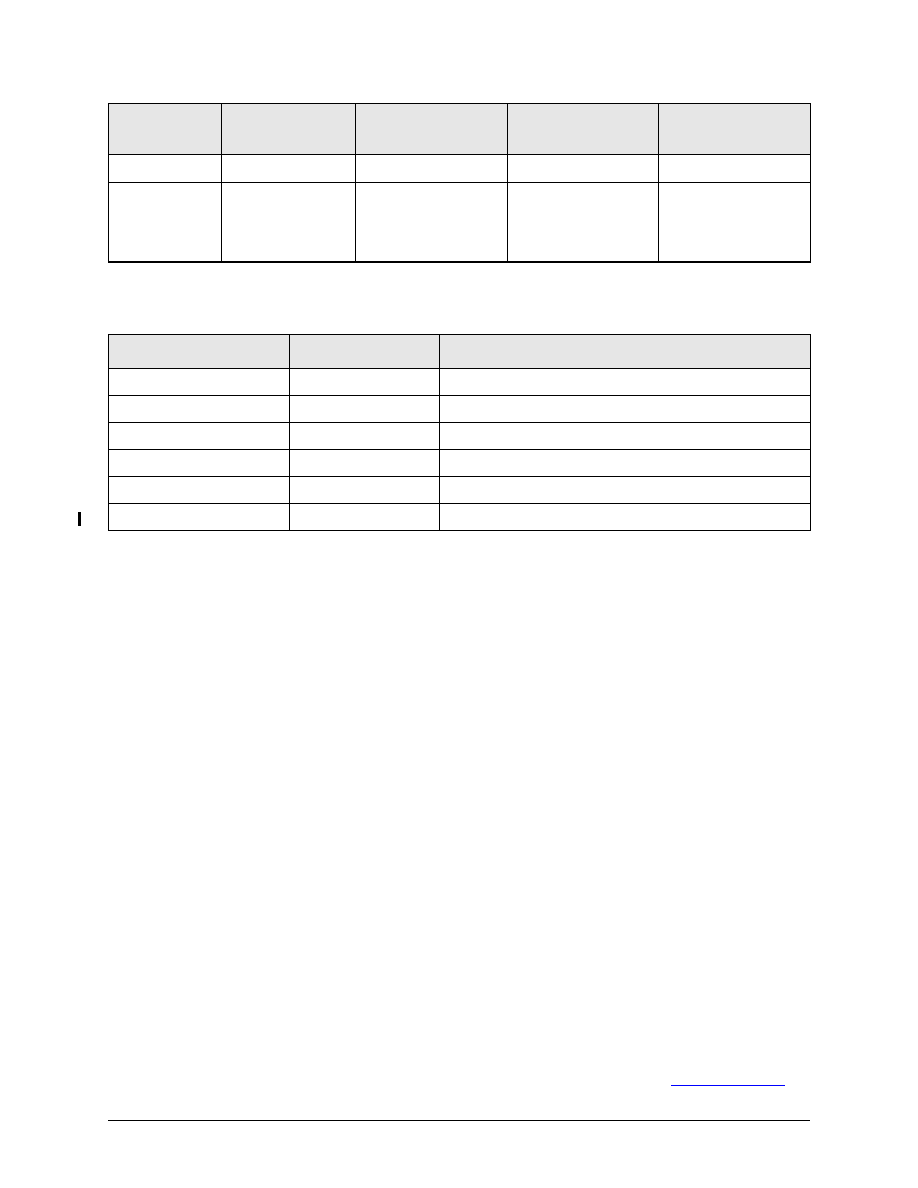

Ordering Information

Document Revision History

Model Number

Manufacturing

Part Number

Product Revision

Package

Operating

Temperature

CN8236

28236-12

B

388-pin BGA

≠40

∞

C to 85

∞

C

CN8236/

CX28250EVM

Evaluation

Module

BT00-D700-601

--

--

--

Document Number

Device Revision

Comments

N8236DSA

CN8236 Rev. A

This is the advanced issue of the data sheet.

100453B

CN8236 Rev. B

Put into new Conexant format.

500372A

CN8236 Rev. B

Revisions made. Changed format from Conexant to Mindspeed.

500372B

CN8236 Rev. B

Corrections as noted by change bars.

28236-DSH-001-A

CN8236 Rev. B

Corrections as noted by change bars.

28236-DSH-001-B

CN8236 Rev. B

Corrections as noted by change bars.

28236-DSH-001-B

Mindspeed Technologies

TM

≠Continued Distinguishing Features≠

New Features

∑

3.3 V, 388 BGA lowers power and

eases PCB assembly

∑

AAL3/4 CPCS generation and

checking

∑

PCI 2.1, including support for serial

EEPROM

∑

Enhancements to xBR Traffic

Manager

≠ fewer ABR templates

≠ improved CBR tunneling

∑

Reduced memory size for VCC

lookup tables

∑

Increased addressing flexibility

∑

Additional byte lane swappers for

increased system flexibility

∑

UTOPIA level 2, 8/16 bit 50 MHz

∑

Programmable size routing tags up

to 64 byte cells

∑

Selectable single/separate UTOPIA

clocks

∑

Interworking function for AAL1 and 2

scheduling

≠ Cell on demand scheduling

∑

Updated PM-OAM processing per i.610

∑

SECBC calculated per GR-1248

∑

Paging function in order to gluelessly

control RS8228 cell delineator (SAR

provides power)

∑

Robust EEPROM operation

∑

Compact PCI Hot Swap capabilities

∑

Master PCI write over read arbitration

control

∑

Increase incoming DMA FIFO buffer

from 2 kB to 8 kB

∑

Prepended VCC index on RSM BOM

cells

∑

Optional reference clock drive

scheduler

∑

Head of Line Flushing (HoLF)

mechanism

∑

Internal loopback in multiPHY mode

∑

Programmable number of slots that

the scheduler can fall behind

xBR Traffic Management

∑

TM4.1 Service Classes

≠ CBR

≠ VBR (single, dual and CLP-based

leaky buckets)

≠ Real time VBR

≠ ABR

≠ UBR

≠ GFC (controlled & uncontrolled

flows)

≠ Guaranteed Frame Rate (GFR)

(guaranteed MCR on UBR VCCs)

∑

16 levels of priorities (16 + CBR)

∑

Dynamic per-VCC scheduling

∑

Multiple programmable ABR

templates (supplied by Mindspeed or

user)

∑

Scheduler driven by selectable clock

≠ Local system clock

≠ External reference clock

∑

Internal RM OAM cell feedback path

∑

Virtual FIFO buffer rate matching

(Source Rate Matching)

∑

Per-VCC MCR and ICR

∑

Tunneling

≠ VP tunnels (VCI interleaving on

PDU boundaries)

≠ CBR tunnels (cells interleaved as

UBR, VBR or ABR with an

aggregate CBR limit)

∑

155 Mbps full duplex (two cell PDUs)

Multi-Queue Segmentation Processing

∑

32 transmit queues with optional

priority levels

∑

64 K VCCs maximum

∑

AAL5 and AAL3/4 CPCS generation

∑

AAL0 Null CPCS (optional use of PTI

for PDU demarcation)

∑

ATM cell header generation

∑

Raw cell mode (52 octet)

∑

200 Mbps half duplex

∑

155 Mbps full duplex (w/ 2-cell PDUs)

∑

Variable length transmit FIFO buffer -

CDV - host latency matching (one to

nine cells)

∑

Symmetric Tx and Rx architecture

≠ buffer descriptors

≠ queues

∑

User defined field circulates back to

the host (32 bits)

∑

Distributed host or SAR-shared

memory segmentation

∑

Simultaneous segmentation and

reassembly

∑

Per-PDU control of CLP/PTI (UBR)

∑

Per-PDU control of AAL5 UU field

∑

Message and streaming status

modes

∑

Virtual Tx FIFO buffer (PCI host)

Multi-Queue Reassembly Processing

∑

32 reassembly queues

∑

64 K VCCs maximum *

∑

AAL5 and AAL3/4 CPCS checking

∑

AAL0

≠ PTI termination

≠ Cell count termination

∑

Early Packet Discard, based on:

≠ Receive buffer underflow

≠ Receive status overflow

≠ CLP with priority threshold

≠ AAL5 max PDU length

≠ Rx FIFO buffer full

≠ Frame relay DE with priority

threshold

≠ LECID filtering and echo

suppression

≠ Per-VCC firewalls

∑

Dynamic channel lookup (NNI or UNI

addressing)

≠ Supports full address space

≠ Deterministic

≠ Flexible VCI count per VPI

≠ Optimized for signalling address

assignment

∑

Message and streaming status

modes

∑

Raw cell mode (52 octet)

∑

200 Mbps half duplex

∑

155 Mbps full duplex (w/ 2-cell

PDUs)

∑

Distributed host or SAR-shared

memory reassembly

∑

Eight programmable reassembly

hardware time-outs (per-VCC

assignable)

∑

Global max PDU length for AAL5

∑

Per-VCC buffer firewall (memory

usage limit)

∑

Simultaneous reassembly and

segmentation

∑

Idle cell filtering

High Performance Host Architecture

with Buffer Isolation

∑

Write-only control and status

∑

Read multiple command for data

transfer

∑

Up to 32 host clients control and

status queues

∑

Physical or logical clients

≠ Enables peer-to-peer architecture

∑

Descriptor-based buffer chaining

∑

Scatter/gather DMA

∑

Endian neutral (allows data word and

control word byte swapping, for both

big and little endian systems)

∑

Non-word (byte) aligned host buffer

addresses

∑

Automatically detects presence of Tx

data or Rx free buffers

∑

Virtual FIFO buffers (PCI bursts

treated as a single address)

∑

Hardware indication of BOM

∑

Allows isolation of system resources

∑

Status queue interrupt delay

Designer Toolkit

∑

Evaluation hardware and software

∑

Reference schematics

∑

Hardware Programming

Interface-RS823xHPI reference

source code (C)

≠Continued≠