| –≠–Ľ–Ķ–ļ—ā—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ļ–ĺ–ľ–Ņ–ĺ–Ĺ–Ķ–Ĺ—ā: CN8472 | –°–ļ–į—á–į—ā—Ć:  PDF PDF  ZIP ZIP |

Data Sheet

Preliminary Information/Conexant Proprietary and Confidential 6/15/99 3/29/99

N8474DSB

June 15, 1999

Preliminary Information

This document contains information on a product under development. The parametric information

contains target parameters that are subject to change.

CN8472/8474

Multichannel Synchronous Communications Controller (MUSYCC)

Product Description

The Bt8474 and Bt8472 are advanced Multichannel Synchronous

Communications Controllers (MUSYCC

) that format and deformat up to

128 (Bt8474) or 64 (Bt8472) High-Level Data Link Control (HDLC) channels

in a single CMOS integrated circuit. MUSYCC operates at Layer 2 of the Open

Systems Interconnection (OSI) protocol reference model and provides a

comprehensive, high-density solution for processing HDLC channels for

inter-networking applications such as Frame Relay, Integrated Services

Digital Network (ISDN) D-channel signaling, X.25, Signaling System 7 (SS7),

Data Exchange Interface (DXI), and LAN/WAN data transport. Under minimal

host supervision, MUSYCC manages a linked list of channel data buffers in

host memory by performing Direct Memory Access (DMA) of up to 128

channels (64 for the Bt8472).

MUSYCC interfaces with up to four independent serial data streams, such

as T1/E1 signals, and then transfers data across the popular 32-bit Peripheral

Component Interface (PCI) bus to system memory at up to 33 MHz. Each

serial interface can operate up to 8.192 MHz. Logical channels may be

mapped as any combination of Digital Service Level 0 (DS-0) timeslots to

support ISDN

hyperchannels

(Nx64 Kbps) or as any number of bits in a

DS-0 for subchanneling applications (Nx8 kbps). MUSYCC also includes a

32-bit expansion port for bridging the PCI bus to local microprocessors or

peripherals. A Joint Test Action Group (JTAG) port enables boundary-scan

testing to replace "bed-of-nails" board testing.

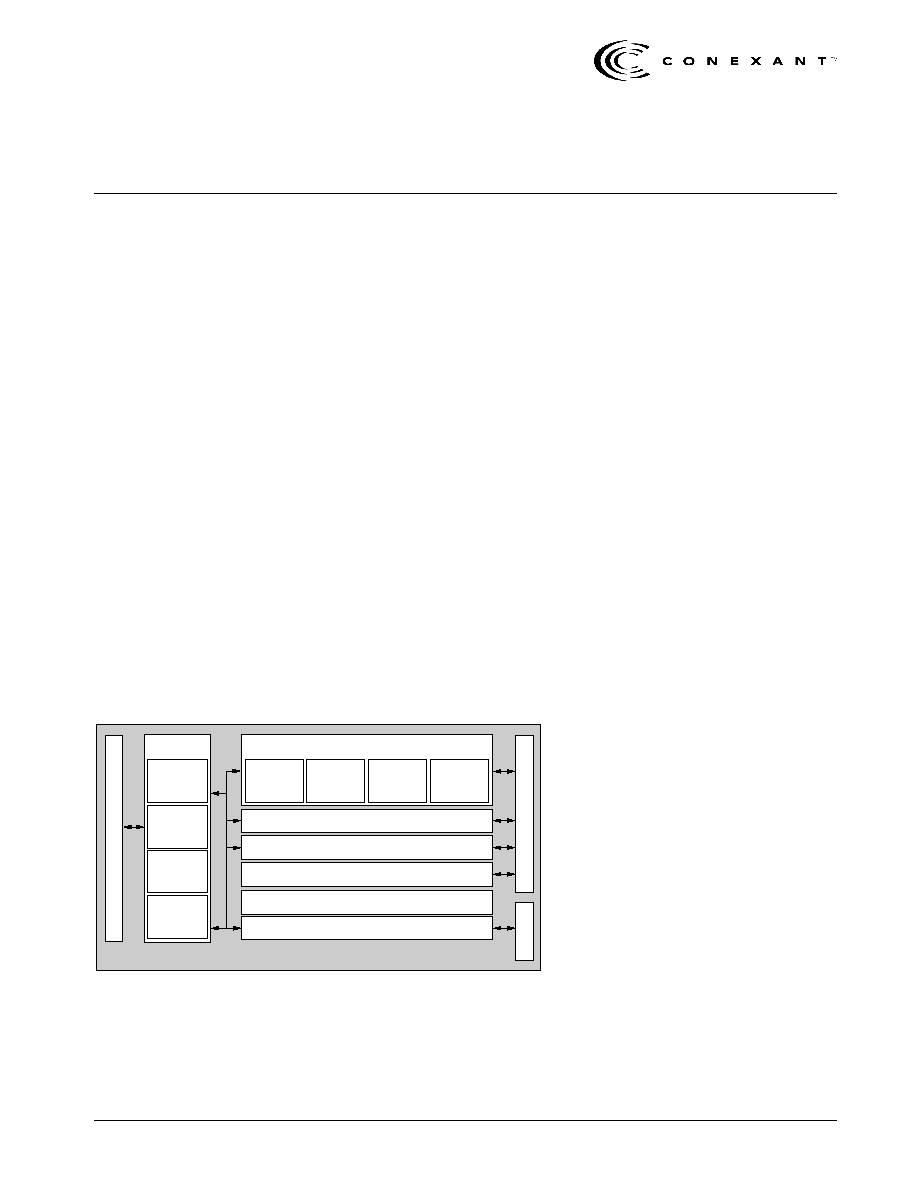

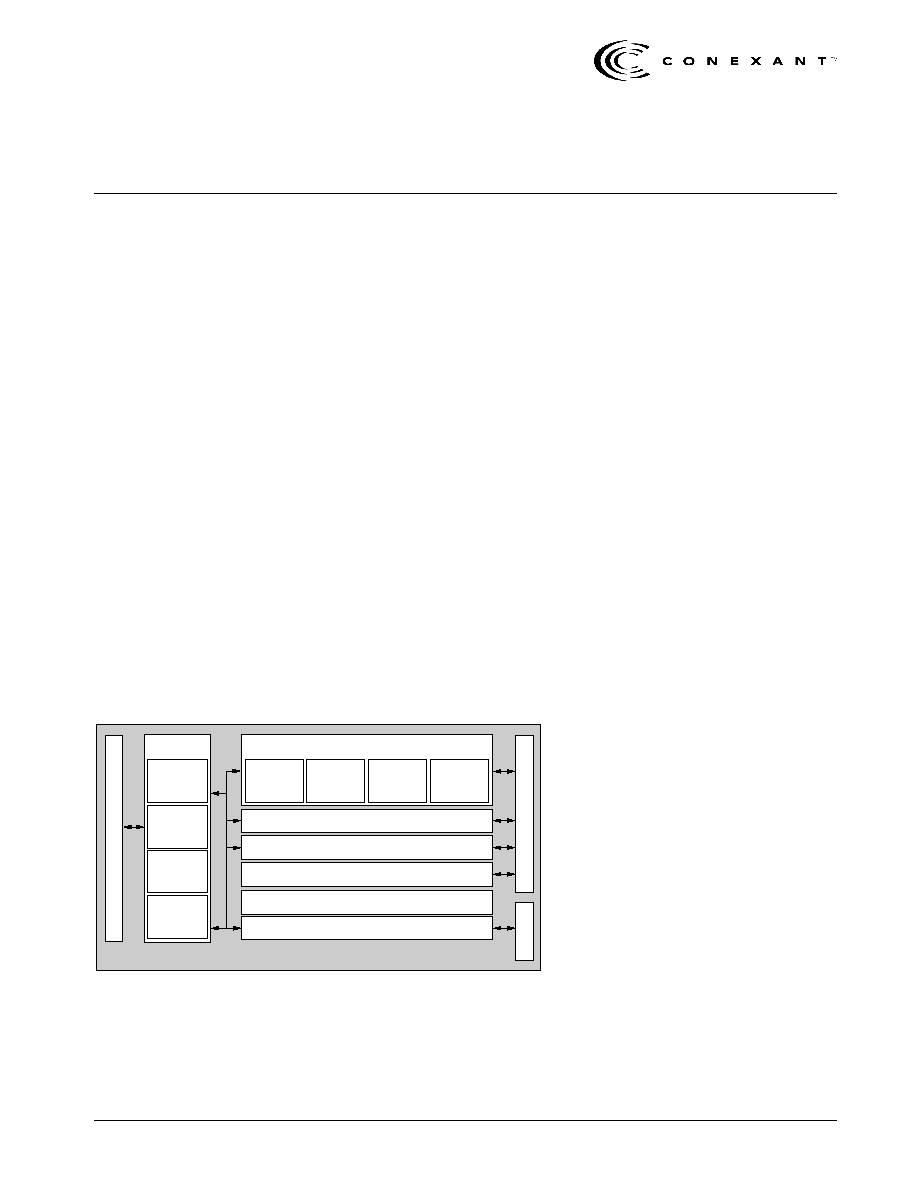

Functional Block Diagram

Distinguishing Features

∑

128/64-channel HDLC controller

∑

OSI Layer 2 protocol support

∑

General purpose HDLC (ISO 3309)

≠ X.25 (LAPB)

≠ Frame relay (LAPF/ANSI T1.618)

≠ ISDN D-channel (LAPD/Q.921)

≠ SS7 support

∑

4 Independent serial interfaces that support:

≠ T1/E1 data streams

≠ DC to 8.192 Mb/s TDM busses

∑

Configurable logical channels

≠ Standard DS0 (56, 64 Kbps)

≠ Hyperchannel (Nx64)

≠ Subchannel (Nx8)

∑

Per-channel protocol mode selection

≠ 16-bit FCS mode

≠ 32-bit FCS mode

≠ SS7 mode (16-bit FCS)

≠ Transparent mode (unformatted data)

∑

Per-channel DMA buffer management

≠ Linked list data structures

≠ Variable size transmit/receive FIFO

∑

Per-channel message length check

≠ Select no length checking

≠ Select from two 14-bit registers to compare

message length

≠ Maximum length: 16,384 bytes

∑

Direct PCI bus interface

≠ 32-bit, 33 MHz operation

≠ Bus master and slave operation

≠ PCI Version 2.1

∑

Local expansion bus interface (EBUS)

≠ 32-bit multiplexed address/data bus

∑

Low power, 5 volt CMOS operation

∑

JTAG boundary scan access port

∑

160-pin PQFP surface-mount package

Applications

∑

ISDN basic-rate or primary-rate interfaces

∑

ISDN D-channel controller

∑

Routers

∑

Cellular base station switch controller

∑

CSU/DSU

∑

Protocol converter

∑

Packet data switch

∑

Frame relay switches/Frame Relay Access Devices

(FRAD)

∑

DXI network interface

∑

Distributed packet-based communications systems

∑

Access multiplexer/concentrator

H ost

Interface

PCI

B

u

s

S

e

r

i

a

l

D

a

ta

B

u

s

Lo

c

a

l

B

u

s

S e rial Interface - C h an ne l G ro up 0

S e rial Interface - C h an ne l G ro up 1

S e rial Interface - C h an ne l G ro up 2

S e rial Interface - C h an ne l G ro up 3

B o u n d a r y S ca n a nd T e st A cce ss

E xpa nsion B u s Interface

Device

Configuration

Registers

PCI

Interface

PCI

configuration

Space

(Function 0)

PCI

configuration

Space

(Function 1)

Interrupt

Controller

DMA

controller

Tx/Rx-DMAC

Bit Level

Processor

Tx/Rx-BLP

Port

Interface

Tx/Rx

N8474DSB

Conexant

Preliminary Information/Conexant Proprietary and Confidential 6/15/99

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is

assumed by Conexant for its use, nor any infringement of patents, copyrights, or other rights of third parties which may result from its

use. No license is granted by implication or otherwise under any patent rights or copyrights of Conexant other than for circuitry

embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject

to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a

Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant

products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from

such improper use or sale.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered

trademarks of third parties. All other marks mentioned herein are the property of their respective owners.

© 1999 Conexant Systems, Inc.

Printed in U.S.A.

All Rights Reserved

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send

comments and suggestions to

conexant.tech.pubs@conexant.com

. For technical questions, contact your local

Conexant

sales office

or field applications engineer.

Conexant, the Conexant symbol

and "What's Next in Communications Technologies" are trademarks of Conexant Systems, Inc.

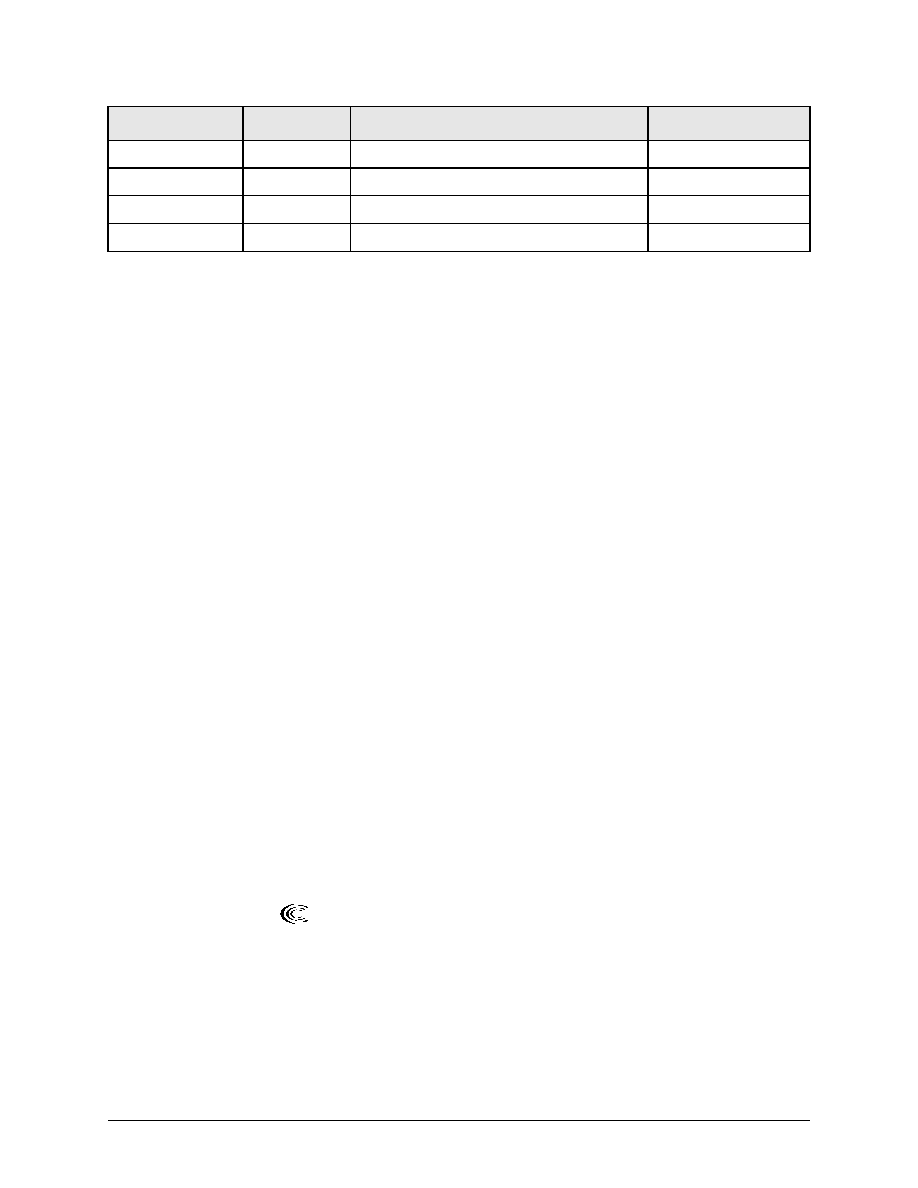

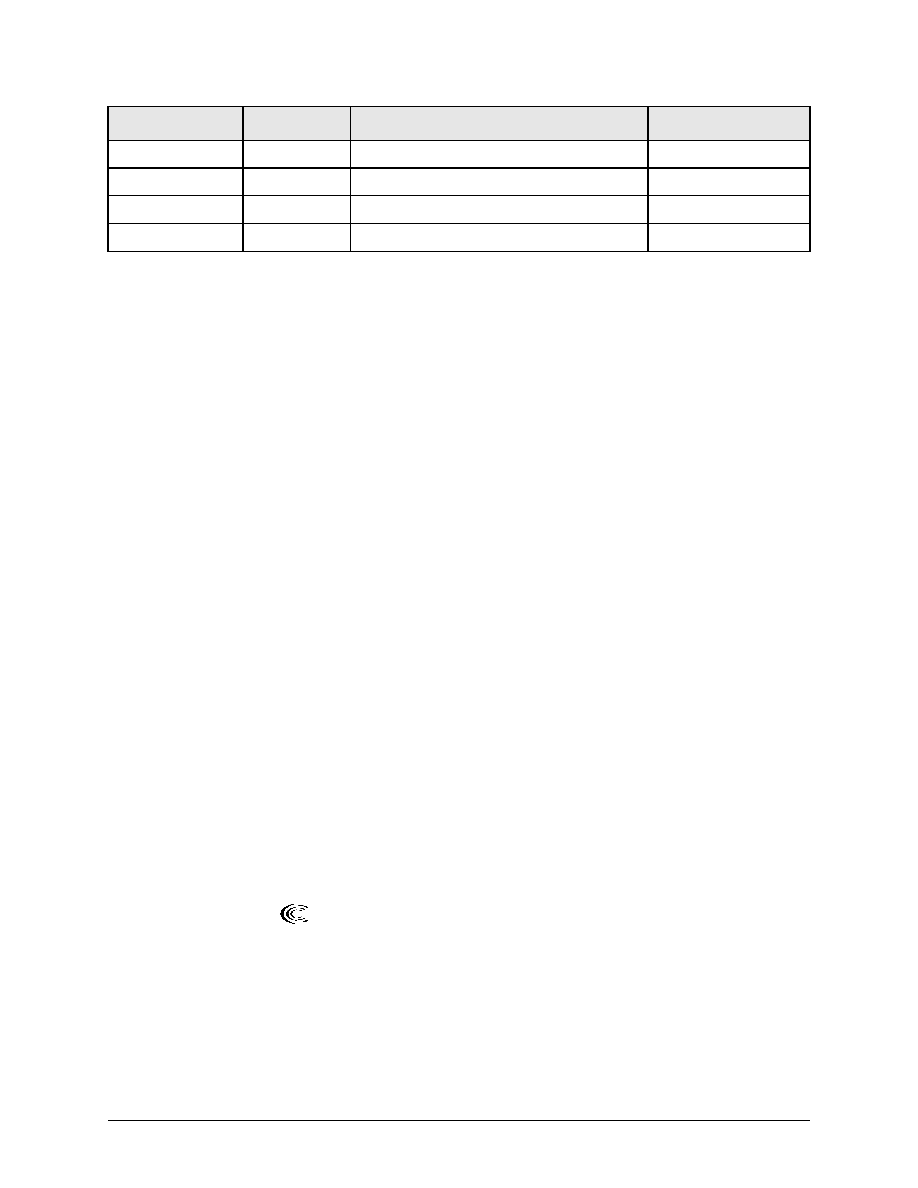

Ordering Information

Model Number

Version

Package

Temperature Range

28472-16

64-Channel

160-Pin Plastic Quad Flat Pack (PQFP)

0 įC to +70 įC

28474-16

128-Channel

160-Pin Plastic Quad Flat Pack (PQFP)

0 įC to +70 įC

28472-17

64-Channel

160-Pin Plastic Quad Flat Pack (PQFP)

≠40 įC to +85 įC

28474-17

128-Channel

160-Pin Plastic Quad Flat Pack (PQFP)

≠40 įC to +85 įC

N8474DSB

Conexant

iii

Preliminary Information/Conexant Proprietary and Confidential 6/15/99

Table of Contents

List of Figures

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

List of Tables

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . xi

1.0

System Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1

Pin Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

2.0

Host Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1

PCI Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.1

PCI Initialization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.1.2

PCI Bus Operations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1.3

PCI Configuration Space

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2

PCI Configuration Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.1

Function 0 Network Controller--PCI Master and Slave

. . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.2.2

Function 1 Expansion Bus Bridge, PCI Slave

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

2.2.3

PCI Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.2.4

Host Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

2.2.5

PCI Bus Parity

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.2.6

PCI Throughput and Latency Considerations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.2.6.1

PCI Bus Latency

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

3.0

Expansion Bus (EBUS)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1

Operation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.1

Initialization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.2

Address and Data

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3.1.3

Clock

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.4

Interrupt

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.1.5

Address Duration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.6

Data Duration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.7

Bus Access Interval

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.1.8

PCI to EBUS Interaction

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.1.9

Microprocessor Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.1.10

Arbitration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.1.11

Connection

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Table of Contents

CN8472/8474

MUSYCC

iv

Conexant

N8474DSB

Preliminary Information/Conexant Proprietary and Confidential 6/15/99

4.0

Serial Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1

Serial Port Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2

Bit Level Processor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.3

Direct Memory Access Controller

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.4

Interrupt Controller

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.5

Channelized Port Mode

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.5.1

Hyperchannels (Nx64)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.5.2

Subchannels (Nx8)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.5.3

Frame Synchronization Flywheel

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.5.4

Change Of Frame Alignment

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.5.5

Out Of Frame

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.6

Serial Port Mapping

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4.7

Tx and Rx FIFO Buffer Allocation and Management

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.7.1

Example Channel BUFFLOC and BUFFLEN Specification

. . . . . . . . . . . . . . . . . . . . . . . . . 4-14

4.7.2

Receiving Bit Stream

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

4.7.3

Transmitting Bit Stream

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

4.7.3.1

Transmit Data Bit Output Value Determination

. . . . . . . . . . . . . . . . . . . . . . . 4-17

5.0

Memory Organization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1

Memory Architecture

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.1.1

Register Map Access and Shared Memory Access

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.1.2

Memory Access Illustration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.2

Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.2.1

Host Interface Level Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.2.1.1

Global Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.2.1.2

Dual Address Cycle Base Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.2.2

Channel Group Level Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2.1

Group Base Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2.2

Service Request

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.2.3

Group Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5.2.2.4

Memory Protection Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5.2.2.5

Port Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

5.2.2.6

Message Length Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.2.2.7

Time Slot Map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.2.2.8

Subchannel Map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

5.2.3

Channel Level Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

5.2.3.1

Channel Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

CN8472/8474

Table of Contents

MUSYCC

N8474DSB

Conexant

v

Preliminary Information/Conexant Proprietary and Confidential 6/15/99

5.2.4

Message Level Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

5.2.4.1

Using Message Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

5.2.4.2

Head Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.2.4.3

Message Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.2.4.4

Message Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.2.4.5

Buffer Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.2.4.6

Buffer Status Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

5.2.4.7

Next Message Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5.2.4.8

Data Buffer Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5.2.4.9

Message Descriptor Handling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5.2.5

Interrupt Level Descriptors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

5.2.5.1

Interrupt Queue Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

5.2.5.2

Interrupt Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-36

5.2.5.3

Interrupt Status Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

5.2.6

Interrupt Handling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

5.2.6.1

Initialization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-43

5.2.6.2

Interrupt Descriptor Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

5.2.6.3

INTA* Signal Line

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-44

5.2.6.4

INTB* Signal Line

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-45

6.0

Basic Operation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1

Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.1

Hard PCI Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.1.2

Soft Chip Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.1.3

Soft Group Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.1.4

Example of Initialization Sequence

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.2

Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.1

PCI Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2.2

Global Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.3

Interrupt Queue Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.4

Channel Group(s) Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.5

Service Request Mechanism

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.2.6

MUSYCC Internal Memory

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.6.1

Read Operation--Slave Reads

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.2.6.2

Write Operation--Slave Writes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.3

Channel Operation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.1

Group Structure

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.2

Group Base Pointer

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

6.3.3

Global Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-10

6.3.4

Interrupt Queue Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.3.5

Group Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.3.6

Memory Protection Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.7

Port Configuration Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.3.8

Message Length Descriptor

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.9

Transmit Time Slot Map--Channel 0

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

6.3.10

Transmit Subchannel Map

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15