| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MH89770S | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

4-125

Æ

Features

∑

Complete interface to a bidirectional T1 link

∑

D3/D4 or ESF framing and SLC-96 compatible

∑

Two frame elastic buffer with jitter tolerance

improved to 156UI

∑

Insertion and detection of A, B, C, D bits

Signalling freeze, optional debounce

∑

Selectable B8ZS, jammed bit (ZCS) or no zero

code suppression

∑

Yellow and blue alarm signal capabilities

∑

Bipolar violation count, F

T

error count, CRC

error count

∑

Frame and superframe sync. signals, Tx and Rx

∑

Per channel, overall, and remote loop around

∑

8 kHz synchronization output

∑

Digital phase detector between T1 line and

ST-BUS

∑

ST-BUS compatible

∑

Pin compatible with the MH89760BN/BS

∑

Inductorless clock recovery

∑

Loss of Signal (LOS) indication

∑

Available in standard, narrow and surface

mount formats

Applications

∑

DS1/ESF digital trunk interfaces

∑

Computer to PBX interfaces (DMI and CPI)

∑

High speed computer to computer data links

Description

The MH89770 is a complete T1 interface solution,

meeting the Extended Super Frame (ESF), D3/D4

and SLC-96 formats. The MH89770 interfaces to the

DS1 1.544 Mbit/sec digital trunk and has the

capability of meeting ACCUNET

Æ1

T1.5 wander

tolerance (138 UI).

The MH89770 is a pin-compatible enhancement of

the MH89760B.

1. ACCUNET

Æ

T1.5 is a registered trademark of AT & T.

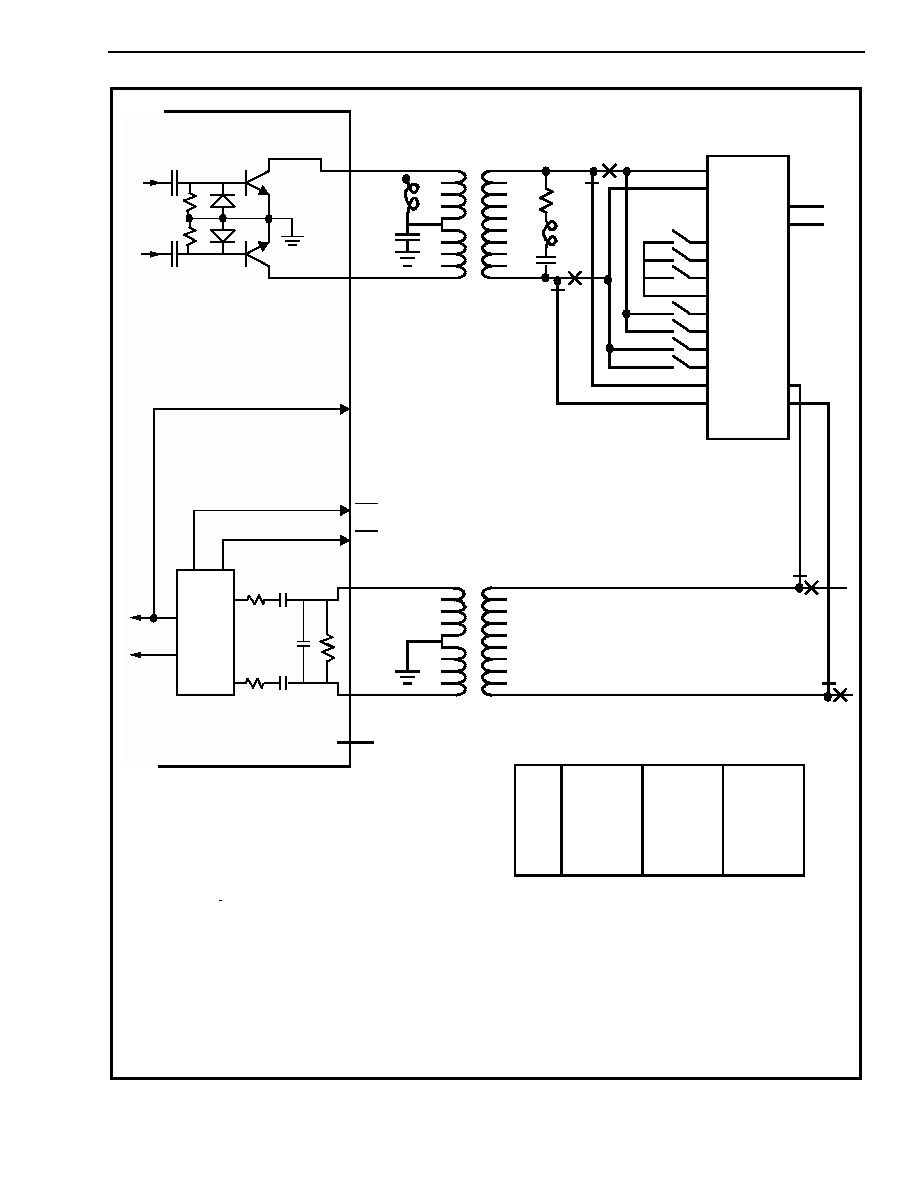

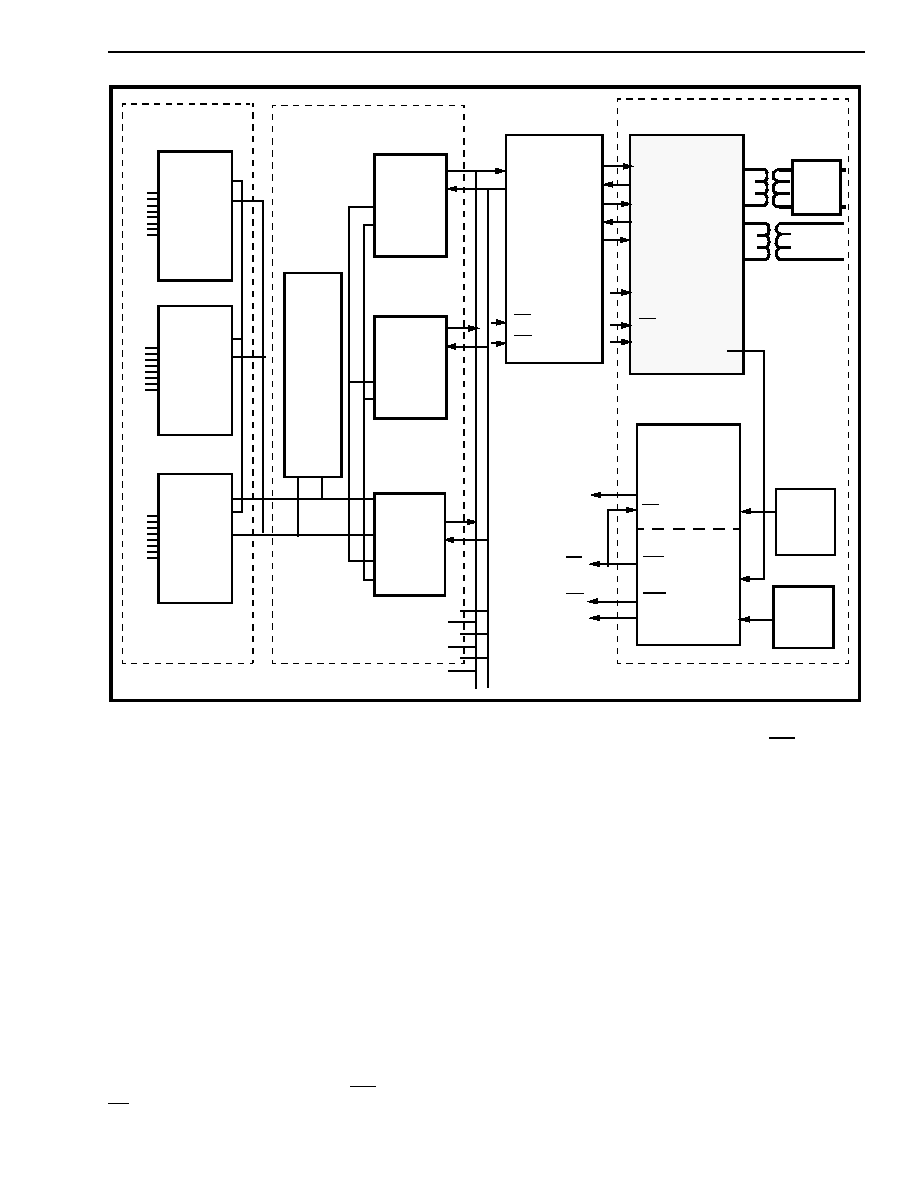

Figure 1 - Functional Block Diagram

TxSF

C2i

F0i

RxSF

DSTo

DSTi

CSTi0

CSTi1

CSTo

VDD

XCtl

XSt

C1.5i

RxFDLClk

RxFDL

TxFDLClk

TxFDL

OUTA

OUTB

RxA

RxT

LOS

RxR

RxB

E1.5o

E8Ko

VSS

ST-BUS

Timing

Circuitry

Data

Interface

Serial

Control

Interface

Control

Logic

Two Frame

Elastic

Buffer with

2048 - 1544

Converter

ABCD

Signalling RAM

DS1

LINK

INTERFACE

Phase

Detector

DS1

Counter

Clock

Extractor

Receiver

Transmitter

Slip Control

ISSUE 2

March 1995

Ordering Information

MH89770N

40 Pin DIL Hybrid 0.8" row pitch

MH89770S

40 Pin Surface Mount Hybrid

0

∞

C to 70

∞

C

MH89770

T1/ESF Framer & Interface

Preliminary Information

4-126

MH89770

Preliminary Information

Figure 2 - Pin Connections

Pin Description

Pin #

Name

Description

2

NC

No Connection.

3

E1.5o

1.544 MHz Extracted Clock (Output): This clock is extracted by the device from the

received DS1 signal. It is used internally to clock in data received at RxT and RxR.

4

V

DD

System Power Supply. +5V.

5

RxA

Received A (Output): The bipolar DS1 signal received by the device at RxR and RxT is

converted to a unipolar format and output at this pin.

6

7

RxT

RxR

Receive Tip and Ring Inputs: Bipolar split phase inputs designed to be connected

directly to the input transformer. Impedance to ground is approximately 1k

.

Impedance between pins=430

.

8

RxB

Received B (Output): The bipolar DS1 signal received by the device at RxR and RxT is

converted to a unipolar format and output at this pin.

9

NC

No Connection.

10

CSTi1

Control ST-BUS Input #1: A 2048 kbit/s serial control stream which carries 24

per-channel control words.

11

CSTi0

Control ST-BUS Input #0: A 2048 kbit/s serial control stream that contains 24 per

channel control words and two master control words.

12

E8Ko

8 kHz Extracted Clock (Output): This is an 8 kHz output generated by dividing the

extracted 1.544 MHz clock by 193 and aligning it with the received DS1 frame. The 8

kHz signal can be used for synchronizing system clocks to the extracted 1.544 MHz

clock. When digital loopback is enabled, the 8kHz is derived from C1.5.

13

XCtl

External Control (Output): This is an uncommitted external output pin which is set or

reset via bit 3 in Master Control Word 1 on CSTi0. The state of XCtl is updated once per

frame.

14

XSt

External Status (Schmitt Trigger Input): The state of this pin is sampled once per

frame and the status is reported in bit 5 of Master Status Word 2 on CSTo.

15

CSTo

Control ST-BUS Output: This is a 2048 kbit/s serial control stream which provides the

24 per-channel status words, and two master status words.

16

NC

No Connection.

NC

LOS

NC

TxFDL

NC

TxFDLClk

VSS

RxFDLClk

DSTo

RxFDL

OUTB

C1.5i

RxSF

TxSF

OUTA

NC

NC

NC

VSS

NC

NC

E1.5o

VDD

RxA

RxT

RxR

RxB

NC

CSTi1

CSTi0

E8Ko

XCtl

XSt

CSTo

NC

DSTi

C2i

E1.5o

F0i

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

4-127

Preliminary Information

MH89770

17

DSTi

Data ST-BUS Input: This pin accepts a 2048 kbit/s serial stream which contains the 24

PCM or data channels to be transmitted on the T1 trunk.

18

C2i

2.048 MHz System Clock (Input): This is the master clock for the ST-BUS section of

the chip. All data on the ST-BUS is clocked in on the falling edge of C2i and out on the

rising edge.

19

E1.5o

1.544 MHz Extracted Clock (Output): Internally connected to Pin 3.

20

F0i

Frame Pulse Input: This is the frame synchronization signal which defines the

beginning of the 32 channel ST-BUS frame.

21

V

SS

System ground.

22-24

NC

No Connection.

25

OUTA

Output A (Open Collector Output): This is the output of the DS1 transmitter circuit. It is

suitable for use with an external pulse transformer to generate the transmit bipolar line

signal.

26

TxSF

Transmit Superframe Pulse Input: A low pulse applied at this pin will determine the

start of the next transmit superframe as illustrated in Figure 20. The device will free run if

this pin is held high.

27

RxSF

Received Superframe Pulse Output: A pulse output on this pin indicates that the next

frame of data on the ST-BUS is from frame 1 of the received superframe. The period is

12 frames long in D3/D4 modes and 24 frames in ESF mode. Active only when device is

synchronized to received DS1 signal.

28

C1.5i

1.544 MHz Clock Input: The rising edge of this clock is used to output data on OUTA,

OUTB. C1.5i must be phase-locked to the C2i system clock.

29

OUTB

Output B (Open Collector Output): This is the output of the DS1 transmitter circuit. It is

suitable for use with an external pulse transformer to generate the transmit bipolar line

signal.

30

RxFDL

Received Facility Data Link (Output): A 4 kbit/s serial output stream that is

demultiplexed from the FDL bits in ESF mode, or the received F

S

bit pattern when in

SLC96 mode. It is clocked out on the rising edge of RxFDLClk.

31

DSTo

Data ST-BUS Output: A 2048 kbit/s serial output stream which contains the 24 PCM or

data channels received from the DS1 line.

32

RxFDLClk

Receive Facility Data Link Clock Output: A 4 kHz clock used to output FDL

information on RxFDL. Data is clocked out on the rising edge of the clock.

33

V

SS

No Connection.

34

TxFDLClk

Transmit Facility Data Link Clock Output: A 4 kHz clock used to input FDL

information on TxFDL. Data is clocked in on the rising edge of the clock.

35

NC

No Connection.

36

TxFDL

Transmit Facility Data Link (Input)

:

A 4 kbit/s serial input stream that is muxed into the

FDL bits in the ESF mode, or the F

S

pattern when in SLC96 mode. It is clocked in on the

rising edge of TxFDLClk.

37

NC

No Connection.

38

LOS

Loss of Signal (Output): This pin goes high when 128 contiguous ZEROs are received

on the RxT and RxR inputs. When LOS is high, RxA and RxB are forced high. LOS is

reset when 48 ones are received in a two T1-frame period.

39

NC

No Connection.

40

NC

No Connection.

Pin Description (Continued)

Pin #

Name

Description

4-128

MH89770

Preliminary Information

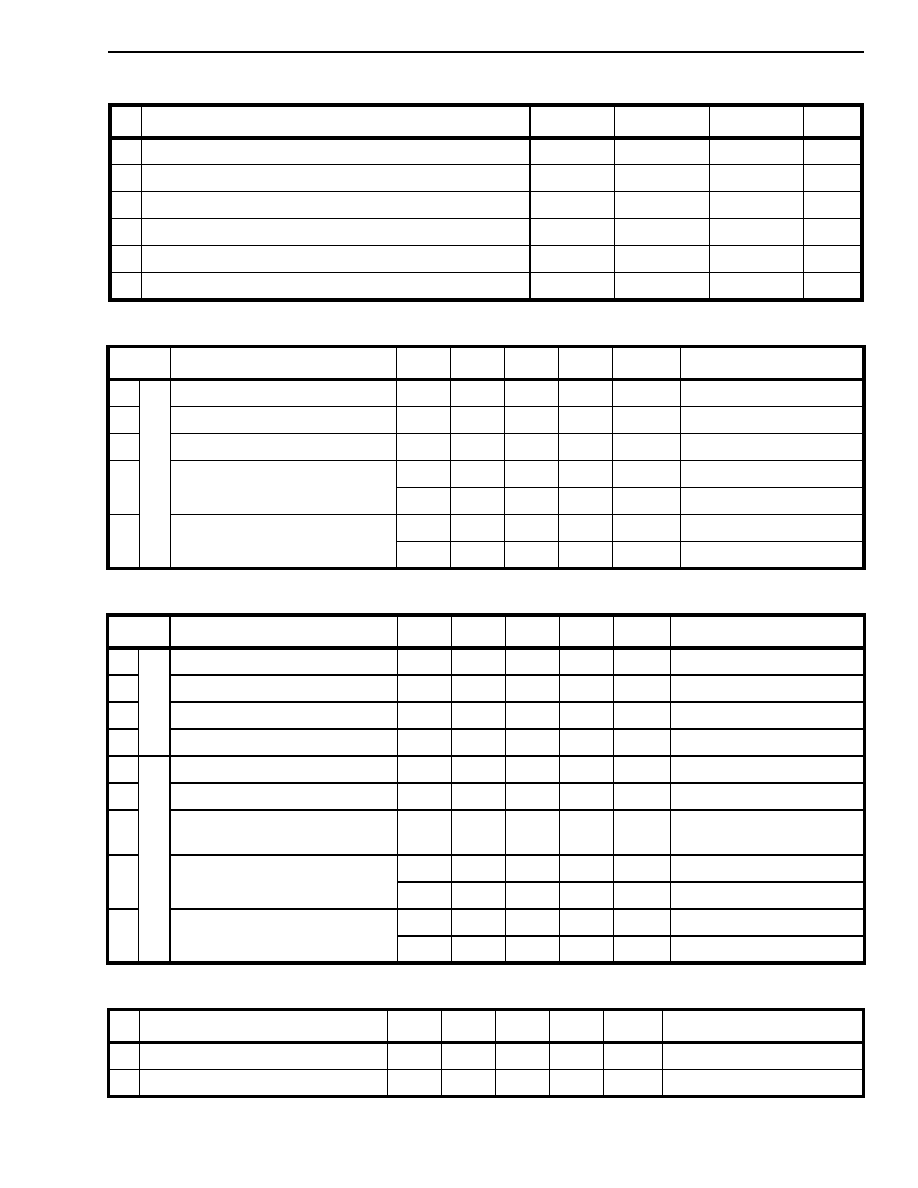

S

T

-B

US

CHA

NN

E

L

V

E

R

S

U

S

DS

1 CHA

NN

E

L

T

R

A

N

S

M

I

T

T

E

D

S

T

-

B

U

S

CH

A

N

NE

L

V

E

RS

US

D

S

1

C

H

A

NNE

L

RE

CE

IV

E

D

P

C

C

W

=P

e

r

C

h

an

ne

l

C

o

n

t

r

o

l W

o

r

d

,

MC

W

1

/

2

=

M

a

s

ter

C

o

n

t

r

o

l W

o

r

d

1/2

S

T

-B

US

CHA

NNE

L V

E

R

S

US

DS

1 CHA

NN

E

L

C

O

NT

RO

LLE

D

P

C

C

W

=P

e

r

C

h

an

ne

l

C

o

n

t

r

o

l W

o

r

d

S

T

-B

US

CHA

NNE

L V

E

R

S

US

DS

1 CHA

NN

E

L

C

O

NT

RO

LLE

D

P

C

S

W

=

P

e

r

C

h

an

ne

l S

t

at

us

W

o

r

d

, P

S

W

=

P

h

a

s

e

S

t

at

u

s

W

o

r

d

,

MS

W

=

Ma

st

er

S

t

a

t

us W

o

r

d

S

T

-

B

US

V

E

RS

US

DS

1 CHA

NNE

L S

T

A

T

U

S

X

=

UNUS

E

D

F

i

gur

e

3

-

S

T

-

B

U

S

C

h

a

n

ne

l

A

l

l

o

c

a

t

i

ons

DST

i

0

X

1234

X

5

678

X

9

1

01

11

2

X

1

3

14

15

16

X

17

18

1

9

2

0

X

21

22

23

2

4

X

25

26

27

28

X

2

9

30

31

DS1

1

2

3

4

5

6

7

8

9

1

0

11

12

13

14

1

5

1

6

1

7

1

8

19

20

21

22

2

3

2

4

DST

o

0

X

12

34

X

5678

X

91

0

1

1

1

2

X

13

14

15

16

X

17

1

8

19

20

X

21

22

23

24

X

25

26

27

28

X

29

30

31

DS1

1

2

3

4

5

6

7

8

9

10

1

1

12

13

1

4

15

16

17

18

19

20

21

22

23

24

C

S

Ti0

0

PC

CW

1

1

PC

CW

1

2

PC

CW

1

3

X

4

PC

CW

1

5

PC

CW

1

6

PC

CW

1

7

X

8

PC

CW

1

9

PC

CW

1

10

PC

CW

1

11

X

12

PC

CW

1

13

PC

CW

1

14

PC

CW

1

15

MC

W1

16

PC

CW

1

17

PC

CW

1

18

PC

CW

1

19

X

20

PC

CW

1

21

PC

CW

1

22

PC

CW

1

23

X

24

PC

CW

1

25

PC

CW

1

26

PC

CW

1

27

X

28

PC

CW

1

29

PC

CW

1

30

PC

CW

1

31

MC

W2

DS1

1

2

3

4

5

6

7

8

9

10

1

1

12

13

14

15

16

17

18

19

20

21

22

23

24

C

S

Ti1

0

PC

CW

2

1

PC

CW

2

2

PC

CW

2

3

X

4

PC

CW

2

5

PC

CW

2

6

PC

CW

2

7

X

8

PC

CW

2

9

PC

CW

2

10

PC

CW

2

11

X

12

PC

CW

2

13

PC

CW

2

14

PC

CW

2

15

X

16

PC

CW

2

17

PC

CW

2

18

PC

CW

2

19

X

20

PC

CW

2

21

PC

CW

2

22

PC

CW

2

23

X

24

PC

CW

2

25

PC

CW

2

26

PC

CW

2

27

X

28

PC

CW

2

29

PC

CW

2

30

PC

CW

2

31

X

DS1

1

2

3

4

5

6

7

8

9

10

1

1

1

2

1

3

1

4

15

16

17

18

1

9

2

0

2

1

22

23

24

CST

o

0

PCS

W

1

PCS

W

2

PCS

W

3

PS

W

4

PCS

W

5

PC

S

W

6

PC

S

W

7

X

8

PCS

W

9

PCS

W

10

PCS

W

11

X

12

PCS

W

13

PCS

W

14

PCS

W

15

MS

W1

16

PC

S

W

17

PC

S

W

18

PCS

W

19

X

20

PCS

W

21

PCS

W

22

PCS

W

23

X

24

PCS

W

25

PCS

W

26

PC

S

W

27

X

28

PC

S

W

29

PCS

W

30

PCS

W

31

MS

W2

DS1

1

2

3

4

5

6

7

8

9

10

1

1

1

2

1

3

1

4

15

16

17

18

1

9

2

0

2

1

22

23

24

Preliminary Information

MH89770

4-129

Functional Description

The MH89770 is a thick film hybrid solution for a T1

interface. All of the formatting and signalling

insertion and detection is done by the device.

Various programmable options in the device include:

ESF, D3/D4 or SLC-96 mode, common channel or

robbed bit signalling, zero code suppression, alarms,

and local and remote loopback. The MH89770 also

has built in bipolar line drivers and receivers and a

clock extraction circuit.

All data and control information is communicated to

the MH89770 via 2048 kbit/s serial streams

conforming to Mitel's ST-BUS format.

The ST-BUS is a TDM serial bus that operates at

2048 kbits/s. The serial streams are divided into 125

µsec frames that are made up of 32 8-bit channels. A

serial stream that is made up of these 32 8 bit

channels is known as an ST-BUS stream, and one of

these 64 kbit/s channels is known as an ST-BUS

channel.

The system side of the MH89770 is made up of

ST-BUS inputs and outputs, i.e., control inputs and

outputs (CSTi/o) and data inputs and outputs

(DSTi/o). These signals are functionally represented

in Figure 32. The DS1 line side of the device is made

up of split phase inputs (RxT, RxR) and outputs

(OUTA, OUTB) which can be connected to line

coupling transformers. Functional transmit and

receive timing is shown in Figures 33 and 34.

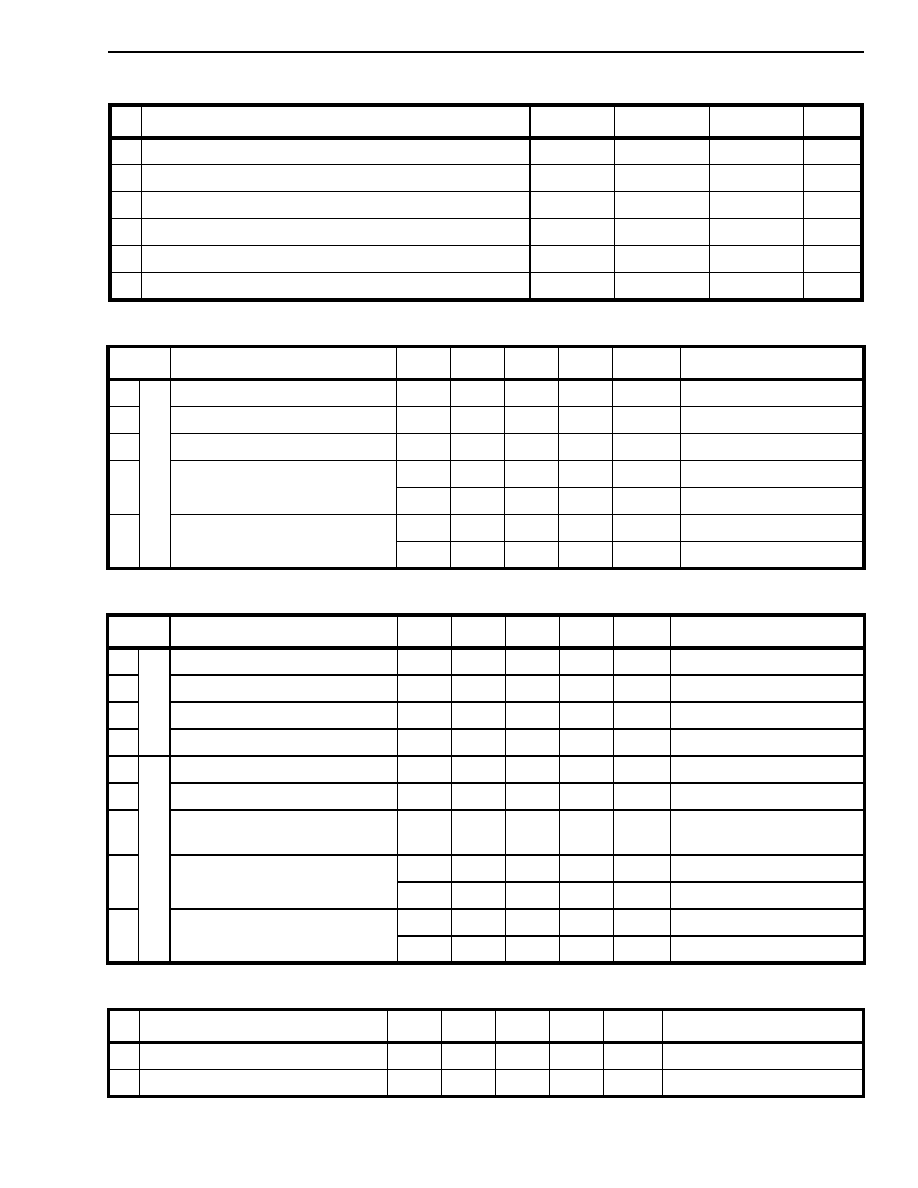

Data for transmission on the DS1 line is clocked

serially into the device at the DSTi pin. The DSTi pin

accepts a 32 channel time division multiplexed

ST-BUS stream. Data is clocked in with the falling

edge of the C2i clock. ST-BUS frame boundaries are

defined by the frame pulse applied at the F0i pin.

Only 24 of the available 32 channels on the ST-BUS

serial stream are actually transmitted on the DS1

side. The unused 8 channels are ignored by the

device.

Data received from the DS1 line is clocked out of the

device in a similar manner at the DSTo pin. Data is

clocked out on the rising edge of the C2i clock. Only

24 of the 32 channels output by the device contain

the information from the DS1 line. The DSTo pin is,

however, actively driven during the unused channel

timeslots. Figure 3 shows the correspondence

between the DS1 channels and the ST-BUS

channels.

All control and monitoring of the device is

accomplished through two ST-BUS serial control

inputs and one serial control output. Control ST-BUS

input number 0 (CSTi0) accepts an ST-BUS serial

stream which contains the 24 per channel control

words and two master control words. The per channel

control words relate directly to the 24 information

channels output on the DS1 side. The master control

words affect operation of the whole device. Control

ST-BUS input number 1 (CSTi1) accepts an ST-BUS

stream containing the A, B, C and D signalling bits.

The relationship between the CSTi channels and the

controlled DS0 channels is shown in Figure 3. Status

and signalling information is received from the device

via the control ST-BUS output (CSTo). This serial

output stream contains two master status words, 24

per channel status words and one Phase Status

Word. Figure 3 shows the correspondence between

the received DS1 channels and the status words.

Detailed information on the operation of the control

interface is presented below.

Programmable Features

The main features in the device are programmed

through two master control words which occupy

channels 15 and 31 in Control ST-BUS input stream

number 0 (CSTi0). These two eight bit words are

used to:

∑

Select the different operating modes of the

device ESF, D3/D4 or SLC-96.

∑

Activate the features that are needed in a

certain application; common channel signalling,

zero code suppression, signalling debounce,

etc.

∑

Turn on in service alarms, diagnostic loop

arounds, and the external control function

Tables 1 and 2 contain a complete explanation of the

function of the different bits in Master Control Words

1 and 2.

Major Operating Modes

The major operating modes of the device are

enabled by bits 2 and 4 of Master Control Word 2.

The Extended Superframe (ESF) mode is enabled

when bit 4 is set high. Bit 2 has no effect in this

mode. The ESF mode enables the transmission of

the S bit pattern shown in Table 3. This includes the

frame/superframe pattern, the CRC-6, and the

Facility Data Link (FDL). The device generates the

frame/multiframe pattern and calculates the CRC for

each superframe. The data clocked into the device

on the TxFDL pin is incorporated into the FDL. ESF

mode will also insert A, B, C and D signalling bits into

the 24 frame multiframe. The DS1 frame begins after

4-130

MH89770

Preliminary Information

.

Table 1. Master Control Word 1 (Channel 15, CSTi0)

Table 2. Master Control Word 2 (Channel 31, CSTi0)

Bit

Name

Description

7

Debounce

When set the received A, B, C and D signalling bits are reported directly in the per

channel status words output at CSTo. When clear, the signalling bits are debounced for 6

to 9 ms before they are placed on CSTo.

6

TSPZCS

Transparent Zero Code Suppression. When this bit is set, no zero code suppression is

implemented.

5

B8ZS

Binary Eight Zero Suppression. When this bit is set, B8ZS zero code suppression is

enabled. When clear, bit 7 in data channels containing all zeros is forced high before

being transmitted on the DS1 side. This bit is inactive if the TSPZCS bit is set.

4

8kHSel

8 kHz Output Select. When set, the E8Ko pin is held high. When clear, the E8Ko

generates an 8 kHz output derived from the extracted 1.544 MHz clock or C1.5i clock

(see Pin Description for E8Ko).

3

XCtl

External Control Pin. When set, the XCtl pin is held high. When clear, XCtl is held low.

2

ESFYLW

ESF Yellow Alarm. Valid only in ESF mode. When set, a sequence of eight 1's followed

by eight 0's is sent in the FDL bit positions. When clear, the FDL bit contains data input at

the TxFDL pin.

1

Robbed bit

When this bit is set, robbed bit signalling is disabled on all DS0 transmit channels. When

clear, A, B, C and D signalling bits are inserted into bit position 8 of all DS0 channels in

every 6th frame.

0

YLALR

Yellow Alarm. When set, bit 2 of all DS0 channels is set low. When clear, bit 2 operates

normally.

Bit

Name

Description

7

RMLOOP

Remote Loopback. When set, the data received at RxR and RxT is looped back to OUTB

and OUTA respectively. The data is clocked into the device with the extracted 1.544 MHz

clock. The device still monitors the received data and outputs it at DSTo. The device

operates normally when the bit is clear.

6

DGLOOP

Digital Loopback. When set, the data input on DSTi is looped around to DSTo. The

normal received data on RxR and RxT is ignored. However, the data input at DSTi is still

transmitted on OUTA and OUTB. The device frames up on the looped data using the C1.5i

clock.

5

ALL1'S

All One's Alarm. When set, the chip transmits an unframed all 1's signal on OUTA and

OUTB.

4

ESF/D4

ESF/D4 Select. When set, the device is in ESF mode. When clear, the device is in D3/D4

mode.

3

ReFR

Reframe. If set for at least one frame and then cleared, the chip will begin to search for a

new frame position. Only the change from high to low will cause a reframe, not a

continuous low level.

2

SLC-96

SLC-96 Mode Select. The chip is in SLC-96 mode when this bit is set. This enables input

and output of the F

S

bit pattern using the same pins as the facility data link in ESF mode.

The chip will use the same framing algorithm as D3/D4 mode. The user must insert the

valid F

S

bits in 2 out of 6 superframes to allow the receiver to find superframe sync, and

the transmitter to insert A and B bits in every 6th frame. The SLC-96 FDL completely

replaces the F

S

pattern in the outgoing S bit position. Inactive in ESF mode.

1

CRC/MIMIC

In ESF mode, when set, the chip disregards the CRC calculation during synchronization.

When clear, the device will check for a correct CRC before going into synchronization. In

D3/D4 mode, when set, the device will synchronize on the first correct S-bit pattern

detected. When this bit is clear, the device will not synchronize if it has detected more than

one candidate for the frame alignment pattern (i.e., a mimic).

0

Maint.

Maintenance Mode. When set, the device will declare itself out-of-sync if 4 out of 12

consecutive F

T

bits are in error. When clear, the out-of-sync threshold is 2 errors in 4 F

T

bits. In this mode, four consecutive bits following an errored F

T

bit are examined.

Preliminary Information

MH89770

4-131

approximately 25 periods of the C1.5i clock from the

F0i frame pulse.

Table 3. ESF Frame Pattern

These signalling bits are only valid if the robbed bit signalling is

active.

During synchronization the receiver locks on to the

incoming frame, calculates the CRC and compares it

to the CRC received in the next multiframe. The

device will not declare itself to be in synchro-

nization unless a valid framing pattern in the S-bit is

detected and a correct CRC is received. The CRC

check in this case provides protection against false

framing. The CRC check can be turned off by setting

bit 1 in Master Control Word 2.

The device can be forced to resynchronize itself. If

Bit 3 in Master Control Word 2 is set for one frame

and then subsequently reset, the device will start to

search for a new frame position. The decision to

reframe is made by the user's system processor on

the basis of the status conditions detected in the

received master status words. This may include

consideration of the number of errors in the received

CRC in conjunction with an indication of the

presence of a mimic. When the device attains

synchronization the mimic bit in Master Status Word

1 is set if the device found another possible

candidate when it was searching for the framing

pattern.

Note that the device will resynchronize automatically

if the errors in the terminal framing pattern (F

T

or

Frame #

FPS

FDL

CRC

Signalling

1

X

2

CB1

3

X

4

0

5

X

6

CB2

A

7

X

8

0

9

X

10

CB3

11

X

12

1

B

13

X

14

CB4

15

X

16

0

17

X

18

CB5

C

19

X

20

1

21

X

22

CB6

23

X

24

1

D

FPS) exceed the threshold set with bit 0 in Master

Control Word 2.

Table 4. D3/D4 Framer

These signalling bits are only valid if the robbed bit signalling is

active.

Standard D3/D4 framing is enabled when bit 4 of

Master Control Word 2 is reset (logic 0). In this mode

the device searches for and inserts the framing

pattern shown in Table 4. This mode only supports

AB bit signalling, and does not contain a CRC check.

The CRC/MIMIC bit in Master Control Word 2, when

set high, allows the device to synchronize in the

presence of a mimic. If this bit is reset, the device will

not synchronize in the presence of a mimic. (Also

refer to section on Framing Algorithm.)

In the D3/D4 mode the device can also be made

compatible with SLC-96 by setting bit two of Master

Control Word 2. This allows the user to insert and

extract the signalling framing pattern on the DS1 bit

stream using the FDL input and output pins. The

user must format this 4 kbits of information externally

to meet all of the requirements of the SLC-96

specification (see Table 5). The device multiplexes

and demultiplexes this information into the proper

position. This mode of operation can also be used for

any other application that uses all or part of the

signalling framing pattern. As long as the serial

stream clocked into the TxFDL contains two proper

sets of consecutive synchronization bits (as shown in

Table 5 for frames 1 to 24), the device will be

able to insert and extract the A, B signalling bits.

The TxSF pin should be held high in this mode.

Superframe boundaries cannot be defined by a pulse

on this input. The RxSF output functions normally

and indicates the superframe boundaries based on

the synchronization pattern in the F

S

received bit

position.

Frame #

F

T

F

S

Signalling

1

1

2

0

3

0

4

0

5

1

6

1

A

7

0

8

1

9

1

10

1

11

0

12

0

B

4-132

MH89770

Preliminary Information

Table 5. SLC-96 Framing Pattern

Note: The FS pattern has to be supplied by the user.

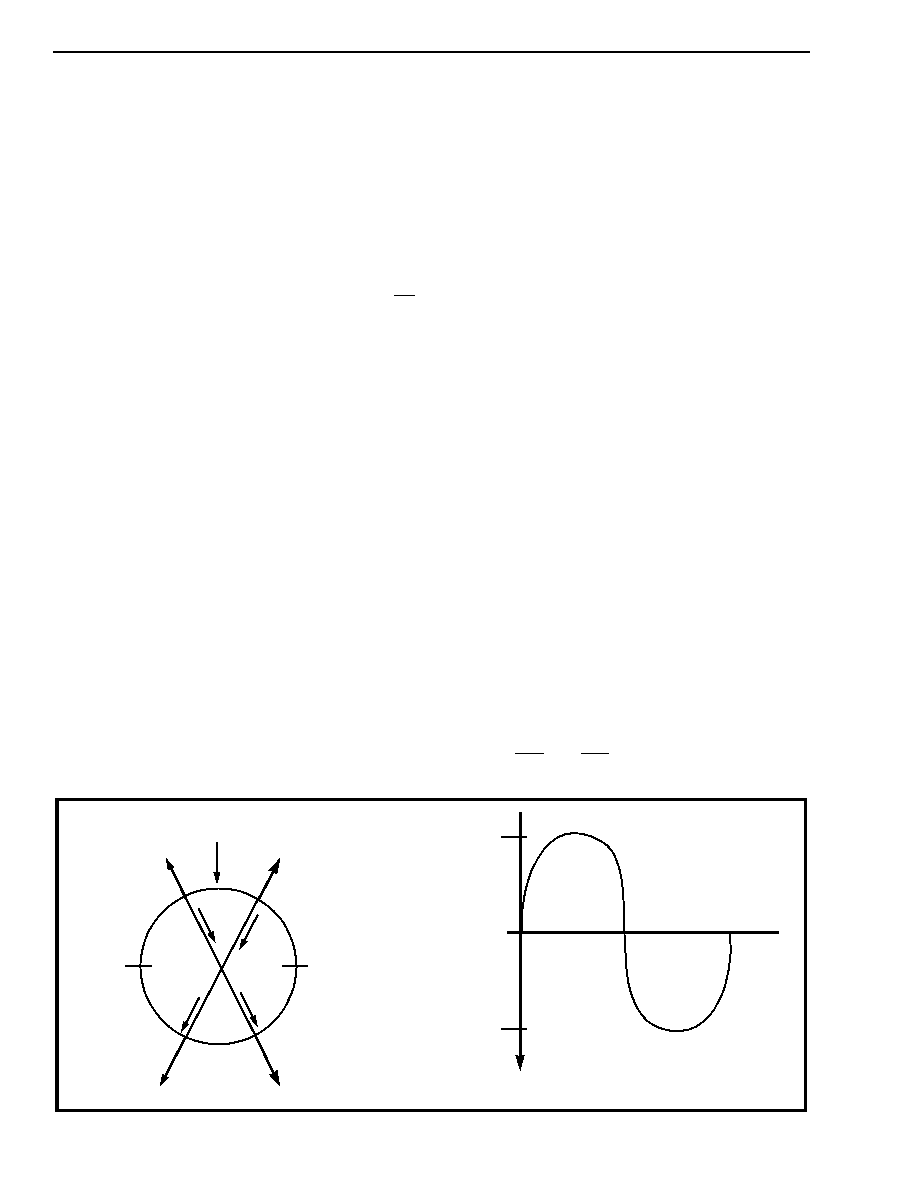

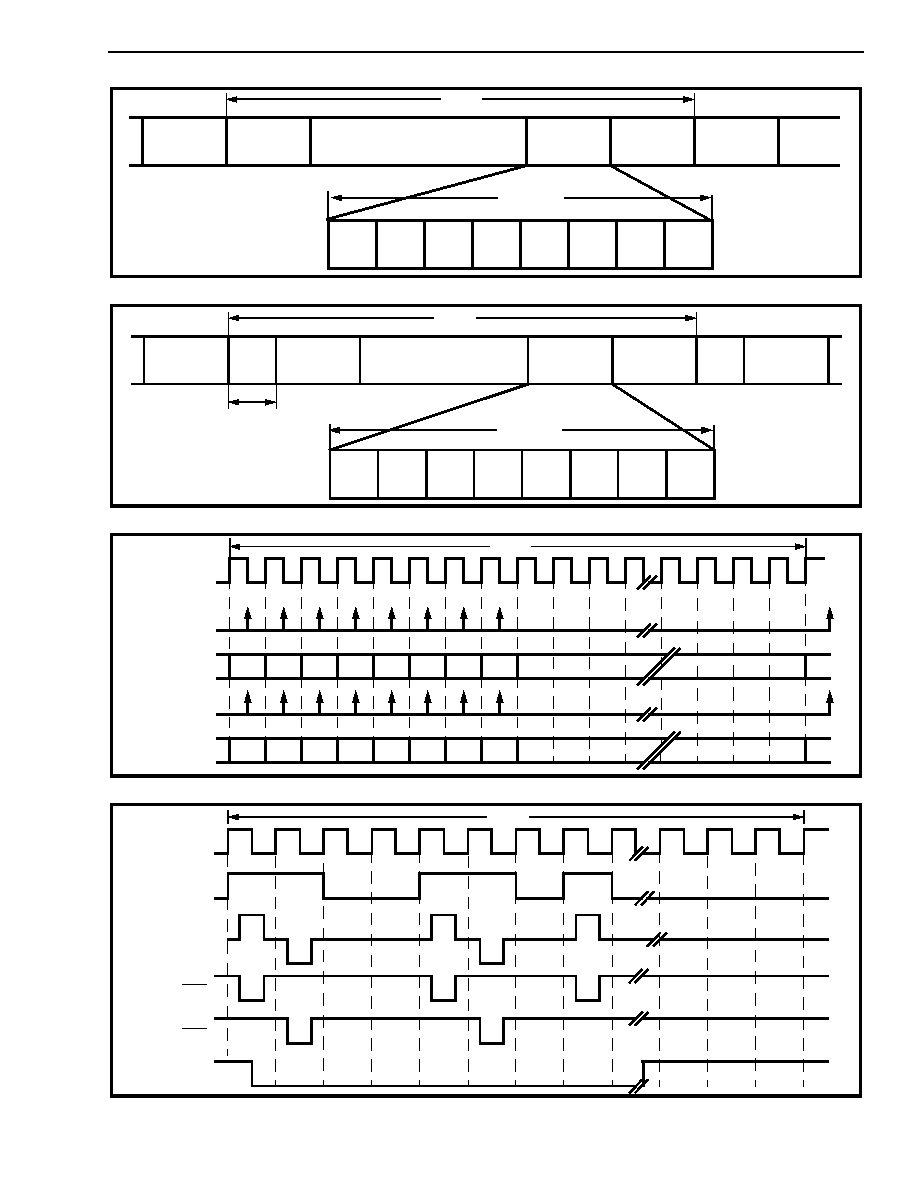

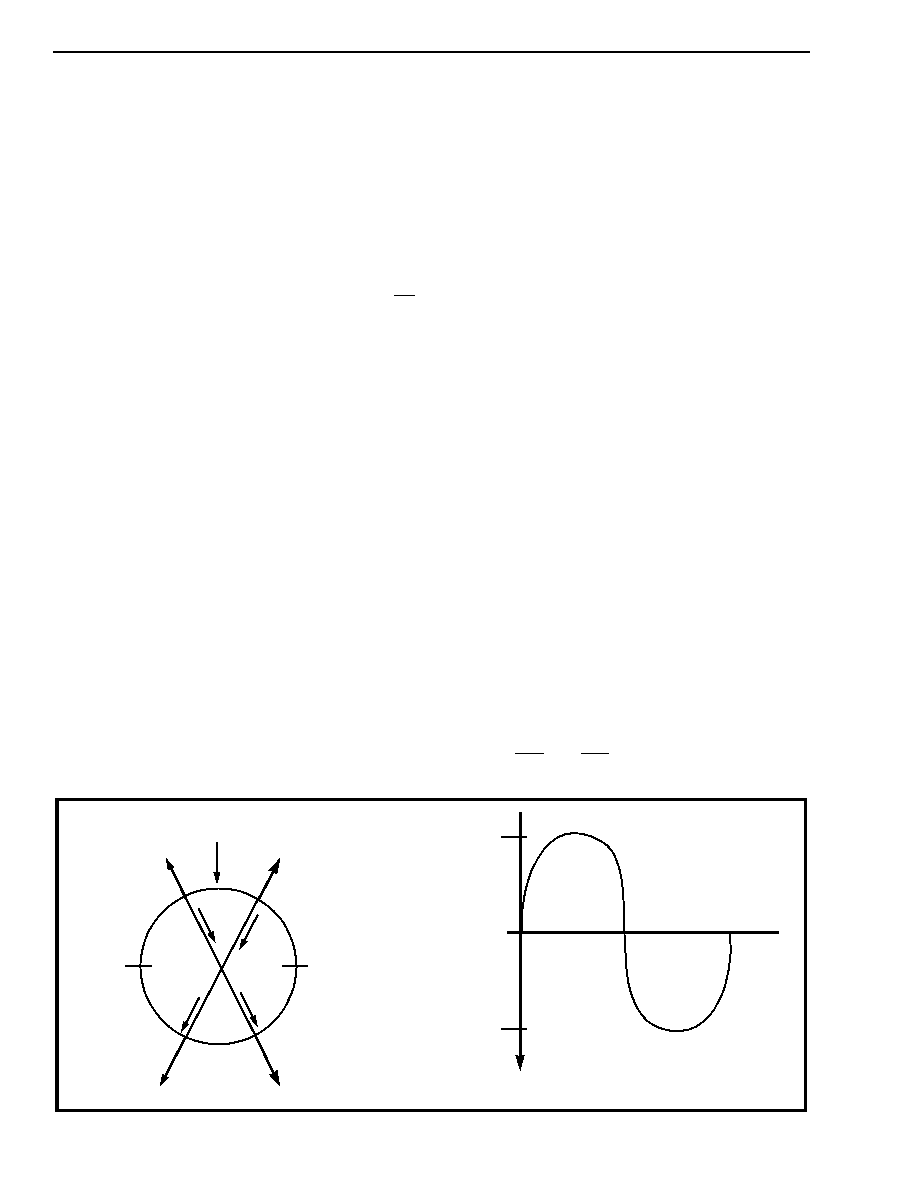

Figure 4 - B8ZS Output Coding

Frame

#

F

T

F

S

Notes

Frame

#

F

T

F

S

Notes

1

1

Resynchronization

Data

Bits

37

1

X = Concentrator

Field Bits

2

0

38

X

3

0

39

0

4

0

40

X

5

1

41

1

6

0

42

X

7

0

43

0

8

1

44

X

9

1

45

1

10

1

46

X

11

0

47

0

S = Spoiler Bits

12

1

48

S

13

1

49

1

14

0

50

S

15

0

51

0

16

0

52

S

17

1

53

1

18

0

54

C

C = Maintenance

Field

Bits

19

0

55

0

20

1

56

C

21

1

57

1

22

1

58

C

23

0

59

0

A = Alarm Field

Bits

24

1

60

A

25

1

X =Concentrator

Field Bits

61

1

26

X

62

A

27

0

63

0

L = Line Switch

Field Bits

28

X

64

L

29

1

65

1

30

X

66

L

31

0

67

0

32

X

68

L

33

1

69

1

34

X

70

L

35

0

71

0

S = Spoiler Bits

36

X

72

S

DATA

B8ZS

B8ZS

B

0

0

0

V

B

0

V

B

B

0

0

0

V

B

0

V

B

B

V = Violation

B = Bipolar

0 = No Pulse

B

4-133

Preliminary Information

MH89770

Zero Code Suppression

The combination of bits 5 and 6 in Master Control

Word 1 allow one of three zero code suppression

schemes to be selected. The three choices are:

none, binary 8 zero suppression (B8ZS), or jammed

bit (bit 7 forced high). No zero code suppression

allows the device to interface with systems that have

already applied some form of zero code suppression

to the data input on DSTi. B8ZS zero code

suppression replaces all strings of 8 zeros with a

known bit pattern and a specific pattern of bipolar

violations. This bit pattern and violation pattern is

shown in Figure 4. The receiver monitors the

received bit pattern and the bipolar violation pattern

and replaces all matching strings with 8 zeros.

Loopback Modes

Remote and digital loopback modes are enabled by

bits 6 and 7 in Master Control Word 2. These modes

can be used for diagnostics in locating the source of

a fault condition. Remote loop around loops back

data received at RxR and RxT back out on OUTA

and OUTB, thus effectively sending the received

DS1 data back to the far end unaltered so that the

transmission line can be tested. The received signal

with the appropriate received channels on the DS1

side made available in the proper format at DSTo.

The digital loop around mode diverts the data

received at DSTi back out the DSTo pin. Data

received on DSTi is, however, still transmitted out via

OUTA and OUTB. This loop back mode can be used

to test the near end interface equipment when there

is no transmission line or when there is a suspected

failure of the line.

The all ones transmit alarm (also known as the blue

alarm or the keep alive signal) can be activated in

conjunction with the digital loop around so that the

transmission line sends an all 1's signal while the

normal data is looped back locally.

The MH89770 also has a per channel loopback

mode. See Table 6 and the following section for more

information.

Per Channel Control Features

In addition to the two master control words in CSTi0

there are also 24 Per Channel Control Words. These

control words only affect individual DS0 channels.

The correspondence between the channels on

CSTi0 and the affected DS0 channel is shown in

Fig. 3. Each control word has three bits that enable

robbed bit signalling, DS0 channel loopback and

inversion of the DS0 channel. A full description of

each of the bits is provided in Table 6.

Transmit Signalling Bits

Control ST-BUS input number 1 (CSTi1) contains 24

additional per channel control words. These 24

ST-BUS channels contain the A, B, C and D

signalling bits that the device uses at transmit time.

The position of these 24 per channel control words in

the ST-BUS is

shown in Figure 3 and the position of

the ABCD signalling bits is shown in Table 7. Even

though the device only inserts the signalling

Table 6. Per Channel Control Word 1 Input at CSTi0

Table 7. Per Channel Control Word 2 Input at CSTi1

Bit

Name

Description

7-3

IC

Internal Connections. Must be kept at 0 for normal operation.

2

Polarity

When set, the applicable channel is not inverted on the transmit or the receive side of

the device. When clear, all the bits within the applicable channel are inverted both on

transmit and receive side.

1

Loop

Per Channel Loopback. When set, the received DS0 channel is replaced with the

transmitted DS0 channel. Only one DS0 channel may be looped back in this manner at

a time. The transmitted DS0 channel remains unaffected. When clear the transmit and

receive DS0 sections operate normally.

0

Data

Data Channel Enable. When set, robbed bit signalling for the applicable channel is

disabled. When clear, every 6th DS1 frame is available for robbed bit signalling. This

feature is enabled only if bit 1 in Master Control Word is low.

Bit

Name

Description

7-4

Unused

Keep at 0 for normal operation

3

2

1-0

A

B

C, D

These are the 4 signalling bits inserted in the appropriate channels of the DS1 stream

being output from the chip, when in ESF mode. In D3/D4 modes where there are only

two signalling bits, the values of C and D are ignored.

4-134

MH89770

Preliminary Information

.

Table 8. Master Status Word 1 (Channel 15, CSTo)

Table 9. Master Status Word 2 (Channel 31, CSTo)

Table 10. Phase Status Word (Channel 3, CSTo)

Bit

Name

Description

7

YLALR

Yellow Alarm Indication. This bit is set when the chip is receiving a 0 in bit position 2

of every DS0 channel.

6

MIMIC

This bit is set if the frame search algorithm found more than one possible frame

candidate when it went into frame synchronization.

5

ERR

Terminal Framing Bit Error. The state of this bit changes every time the chip detects

4 errors in the F

T

or FPS bit pattern. The bit will not change state more than once every

96ms.

4

ESFYLW

ESF Yellow Alarm. This bit is set when the device has observed a sequence of eight

one's and eight 0's in the FDL bit positions.

3

MFSYNC

Multiframe Synchronization. This bit is cleared when D3/D4 multiframe

synchronization has been achieved. Applicable only in D3/D4 and SLC-96 modes of

operation.

2

BPV

Bipolar Violation Count. The state of this bit changes every time the device counts

256 bipolar violations.

1

SLIP

Slip Indication. This bit changes state every time the elastic buffer in the device

performs a controlled slip.

0

SYN

Synchronization. This bit is set when the device has not achieved synchronization.

The bit is clear when the device has synchronized to the received DS1 data stream.

Bit

Name

Description

7

BlAlm

Blue Alarm. This bit is set if the receiver has detected two frames of 1's and an out of

frame condition. It is reset by any 250 microsecond interval that contains a zero.

6

FrCnt

Frame Count. This is the ninth and most significant bit of the "Phase Status Word"

(see Table 10). If the phase status word is incrementing, this bit will toggle when the

phase reading exceeds channel 31, bit 7. If the phase word is decrementing, then this

bit will toggle when the reading goes below channel 0, bit 0.

5

XSt

External Status. This bit reflects the state of the external status pin (XSt). The state of

the XSt pin is sampled once per frame.

4-3

BPVCnt

Bipolar Violation Count. These two bits change state every 128 and every 64 bipolar

violations, respectively.

2-0

CRCCNT

CRC Error Count. These three bits count received CRC errors. The counter will reset

to zero when it reaches terminal count. Valid only in ESF mode.

Bit

Name

Description

7-3

ChannelCnt

Channel Count. These five bits indicate the ST-BUS channel count between the

ST-BUS frame pulse and the rising edge of E8Ko.

2-0

BitCnt

Bit Count. These three bits provide one bit resolution within the channel count

described above.

information in every 6th DS1 frame this information

must be input every ST-BUS frame.

Robbed bit signalling can be disabled for all

channels on the DS1 link by bit 1 of Master Control

Word 1. It can also be disabled on a per channel

basis by bit 0 in the Per Channel Control Word 1.

Operating Status Information

Status Information regarding the operation of the

device is output serially via the Control ST-BUS

output (CSTo). The CSTo serial stream contains

Master Status Words 1 and 2, 24 Per Channel Status

Words, and a Phase Status Word. The Master Status

Words contain all of the information needed to

determine the state of the interface and how well it is

operating. The information provided includes frame

and super frame synchronization, slip, bipolar

4-135

Preliminary Information

MH89770

.

Table 11. Per Channel Status Word Output on CSTo

Bit

Name

Description

7-4

Unused

Unused Bits. Will be output as 0's.

3

2

1

0

A

B

C

D

These are the 4 signalling bits as extracted from the received DS1 bit stream.

The bits are debounced for 6 to 9 ms if the debounce feature is enabled via bit 7 in

Master Control Word 1.

violation counter, alarms, CRC error count, F

T

error

count, synchronization pattern mimic and a phase

status word. Tables 8 and 9 give a description of each

of the bits in Master Status Words 1 and 2, and Table

10 gives a description of the Phase Status Word.

In addition, the MH89770 has a Loss of Signal (LOS)

pin that is set High when 128 consecutive ZEROs are

received. While LOS is set High, RxA and RxB are

forced High. The LOS signal goes Low when a ONEs

density on 12.5% of the bits (equivalent to 48 bits)

occurs in a two DS1 frame period.

Alarm Detection

The device detects the yellow alarm for both D3/D4

frame format and ESF format. The D3/D4 yellow

alarm will be activated if a `0' is received in bit

position 2 of every DS0 channel for 600 msec. It will

be released in 200 msec after the contents of the bit

change. The alarm is detectable in the presence of

errors on the line. The ESF yellow alarm will become

active when the device has detected a string of eight

0's followed by eight 1's in the facility data link. It is

not detectable in the presence of errors on the line.

This means that the ESF yellow alarm will drop out

for relatively short periods of time, so the system will

have to integrate the ESF yellow alarm. The blue

alarm signal, in Master Status Word 2, will also drop

out if there are errors on the line.

Mimic Detection

The mimic bit in Master Status Word 1 will be set if,

during synchronization, a frame alignment pattern

(F

T

or FPS bit pattern) was observed in more than

one position, i.e., if more than one candidate for the

frame synchronization position was observed. It will

be reset when the device resynchronizes. The mimic

bit, the terminal framing error bit and the CRC error

counter can be used separately or together to decide

if the receiver should be forced to reframe.

Bipolar Violation Counter

The Bipolar Violation bit in Master Status Word 1 will

toggle after 256 violations have been detected in the

received signal. It has a maximum refresh time of 96

ms. This means that the bit can not change state

faster than once every 96 ms. For example, if there

are 256 violations in 80 ms the BPV bit will not

change state until 96 ms. Any more errors in that

extra 16 ms are not counted. If there are 256 errors

in 200 ms then the BPV bit will change state after

200 ms. In practical terms this puts an upper limit

on the error rate that can be calculated from the BPV

information, but this rate (1.7 X 10

-3

) is well above

any normal operating condition.

Bits 4 and 3 also provide bipolar violations

infor-mation. Bit 4 will change state after 128

violations. Bit 3 changes state after 64 bipolar

violations. These bits are refreshed independently

and are not subject to the 96 ms refresh rate

described above.

DS1/ST-BUS Phase Difference

An indication of the phase difference between the

ST-BUS and the DS1 frame can be ascertained from

the information provided by the eight bit Phase

Status Word and the Frame Count bit. Channel three

on CSTo contains the Phase Status Word. Bits 7-3 in

this word indicate the number of ST-BUS channels

between the ST-BUS frame pulse and the rising

edge of the E8Ko signal. The remaining three bits

provide one bit resolution within the channel count

indicated by bits 7-3. The frame count bit in Master

Status Word 2 is the ninth and most significant bit of

the phase status word. It will toggle when the phase

status word increments above channel 31, bit 7 or

decrements below channel 0, bit 0. The E8Ko signal

has a specific relationship with received DS1 frame.

The rising edge of E8Ko occurs during bit 2, channel

17 of the received DS1 frame. The Phase Status

Word in conjunction with the frame count bit, can be

used to monitor the phase relationship between the

received DS1 frame and the local ST-BUS frame.

The local 2.048 MHz ST-BUS clock must be

phase-locked to the 1.544 MHz clock extracted from

the received data. When the two clocks are not

phase-locked, the input data rate on the DS1 side

will differ from the output data rate on the ST-BUS

side. If the average input data rate is higher than the

MH89770

Preliminary Information

4-136

average output data rate, the channel count and bit

count in the phase status word will be seen to

decrease over time, indicating that the E8Ko rising

edge, and therefore the DS1 frame boundary is

moving with respect to the ST-BUS frame pulse.

Conversely, a lower average input data rate will

result in an increase in the phase reading.

In an application where it is necessary to minimize

jitter transfer from the received clock to the local

system clock, a phase lock loop with a relatively

large time constant can be implemented using

information provided by the phase status word. In

such a system, the local 2.048 MHz clock is derived

from a precision VCO. Frequency corrections are

made on the basis of the average trend observed in

the phase status word. For example, if the channel

count in the phase status word is seen to increase

over time, the feedback applied to the VCO is used

to decrease the system clock frequency until a

reversal in the trend is observed.

The elastic buffer in the MT8977 permits the device

to handle 26 ST-BUS channels or 156 UI of jitter/

wander (see description of elastic buffer in the next

section). In order to prevent slips from occurring, the

frequency corrections would have to be implemented

such that the deviation in the phase status word is

limited to 26 channels peak-to-peak. It is possible to

use a more sophisticated protocol, which would

center the elastic buffer and permit more

jitter/wander to be handled. However, for most

applications, including ACCUNET

Æ

T1.5 (138 UI), the

156 UI of jitter/wander tolerance is acceptable.

Received Signalling Bits

The A, B, C and D signalling bits are output from the

device in the 24 Per Channel Status Words. Their

location in the serial steam output at CSTo is shown

in Figure 3 and the bit positions are shown in Table

11. The internal debouncing of the signalling bits can

be turned on or off by Master Control Word 1. In ESF

mode, A, B, C and D bits are valid. Even though the

signalling bits are only received once every six

frames the device stores the information so that it is

available on the ST-BUS every frame. The ST-BUS

will always contain the most recent signalling bits.

The state of the signalling bits is frozen if

synchronization is lost.

In D3/D4 mode, only the A and B bits are valid. The

state of the signalling bits is frozen when terminal

frame synchronization is lost. The freeze is disabled

when the device regains terminal frame

synchronization. The signalling bits may go through

a random transition stage until the device attains

multiframe synchronization.

Clock and Framing Signals

The MH89770 has a built in clock extraction circuit

which creates a 1.544 MHz clock synchronized to

the received DS1 signal. This clock is used internally

by the MH89770 to clock in data received on RxT

and RxR, and is also output at the E1.5o pin. The

circuit has been designed to operate within the

constraints imposed by the minimum 1's density

requirements, typically specified for T1 networks

(maximum of 15 consecutive 0's).

The extracted clock is internally divided by 193 and

aligned with the received DS1 frame. The resulting 8

kHz signal is output at the E8Ko pin and can be used

to phase lock the local system C2 and the transmit

C1.5 clocks to the extracted clock.

The MH89770 requires three clock signals which

have to be generated externally. The ST-BUS

interface on the device requires a 2.048 MHz signal

which is applied at the C2i pin and an 8 kHz

framing signal applied at the F0i pin. The framing

signal is used to delimit individual ST-BUS frames.

Figure 19 illustrates the relationship between the C2i

and F0i signals. The F0i signal can be derived from

the 2.048 MHz C2 clock. The transmit side of the

DS1 interface requires a 1.544 MHz clock applied at

C1.5i. The C1.5 and C2 clocks must be phase

locked. There must be 193 clock cycles of the C1.5

clock for every 256 cycles of the C2 clock in order for

the 2.048 to 1.544 rate converter to function properly.

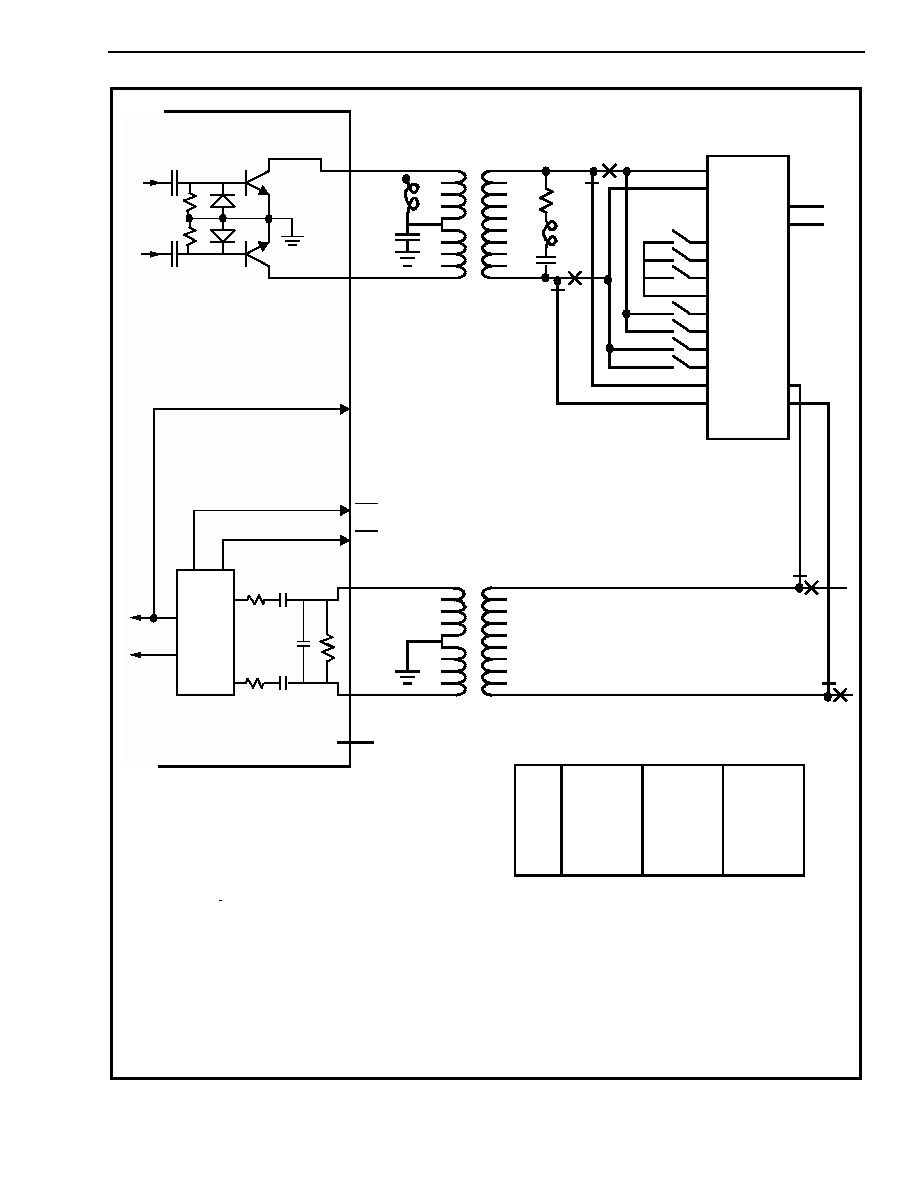

Figure 5 - MT8941 Clock Generator

F0i

C12i

MS1

C8Kb

C16i

MS0

MS2

MS3

F0b

C4b

C2o

ENC4o

ENC2o

CVb

ENCv

C1.5

+5V

F0i

C4i

C2i

+5V

Yo

5V

Ai

Bi

MT8941

DPLL #1

DPLL #2

4-137

Preliminary Information

MH89770

Figure 6 - Input/Output Configuration

Extracted

Clock

Received

Data

Transmit

Data

OUTA

+12V

L2

C2

OUTB

1:

1:

:0.5

R1

L1

C1

EIT

EIR

EA

EB

EC

SW

RCLT

RCHT

RCLR

RCHR

Ti

Ri

E1.5o

RxA

RxB

RxT

RxR

1:

:1

V

DD

1:

S1

S2

S3

S4

S5

S6

S7

TxT

TxR

TL

RL

TR2

Rx

Line

Receiver

S1

S2

S4

S4

S5

S6

S7

0-150'

CLOSE

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

150-450'

OPEN

CLOSE

OPEN

CLOSE

OPEN

CLOSE

OPEN

450-655'

OPEN

OPEN

CLOSE

OPEN

CLOSE

OPEN

CLOSE

Equalizer settings

COMPONENT VALUES:

R1 = 150

1% W

C1 = 0.01

µ

F 5% 250V

C2 = 0.47

µ

F 5% 100V

L1 = 33

µ

H 130mA

L2 = 33

µ

H 165 mA

TR1 = 1:1:0.5 Filtran* Part # TFS2573

TR2 = 1:1:1 Filtran* Part # TFS2574

*Filtran Ltd.

229 Colonnade Road

Nepean, Ontario

Canada K2E 7K3

613-226-1626

Note: The equalizer has been optimized for 22 gauge ABAM

cable. The exact distances may vary with the type of cable and the

output transformer. Different line length settings may be

required if a transformer other than the Filtran TFS2573 is used.

1

4

+5V

MH89770

MH89761

TR1

4-138

MH89770

Preliminary Information

In synchronous operation the slave end of the link

must have its C2 and C1.5 clocks phase locked to

the extracted clock. In plesiochronous clocking

applications where the master and slave end are

operating under controlled slip conditions, phase

locking to the extracted clock is generally not

required.

Mitel's MT8941 Digital Phase Lock Loop (DPLL) can

be used to generate all timing signals required by the

MH89770. The MT8941 has two DPLLs built into the

device. Figure 5 shows how DPLL #1 can be set up

to generate the C1.5 clock phase locked to the F0i

which in turn is derived from the same source as the

C2 clock. Figure 5 also shows how DPLL #2 is set up

to generate the ST-BUS clocks that are phase locked

to the received data rate. If E8Ko from the MH89770

is connected to the C8Kb input on the MT8941,

DPLL #2 in the device will generate the ST-BUS

clocks that are phase locked to the T1 line.

DS1 Line Interface

Line Transmitter

The transmit line interface is made up of two open

collector drivers (OUTA and OUTB) that can be

coupled to the line with a center tapped pulse

transformer (see Figure 6). A step function is applied

to the transformer when either of the transistors is

turned on. By operating in the transient portion of the

inductance response, the secondary of the

transformer produces an almost square pulse. The

capacitor and inductor on the center tap of the

transmit transformer shown in Figure 6 suppress

transients in the 12 volt supply. The series RLC

across the output of the transformer shape the pulse

to meet the AT & T or CCITT pulse templates. A

detailed transformer specification is presented in the

applications section of this data sheet.

To complete the interfaces to the transmit line, a

pre-equalizer and line impedance matching network

is required. The pulse output at the transformer

secondary must be pre-equalized to drive different

lengths of cable. Mitel`s MH89761 T1 Equalizer is

configurable to provide pre-emphasis for 0-150,

150-450 and 450-655 foot lengths of 22 AWG

transmission line. A separate 6dB pad is also

provided on the MH89761 for use in implementing

external looparound. Both circuits have input and

output impedance of 100

. Figure 6 shows how the

equalizer is connected in a typical application. (Refer

to the MH89761 data sheet for more details.)

Line Receiver

The bipolar receiver inputs on the device, RxT and

RxR, are intended to be coupled to the line through a

center tapped pulse transformer as shown in Figure

6. The device presents a 400

impedance to the

receive transformer to permit matching to 100

twisted pair cable. The signal detect threshold level

of the receiver circuit is set at approximately 1.5V.

There is no equalization of the received signal. The

receiver circuit is designed to accurately decode a

signal attenuated by a maximum of 3 dB from the

digital crossconnect point. The MH89770 is not

designed to directly accept a signal from the last

network repeater. Interface to the public network

generally requires a Channel Service Unit (CSU).

The receiver decodes the bipolar signal into a split

phase unipolar return to zero format. The two

resulting unipolar signals are used for bipolar

violation detection within the device and are also

output at RxA and RxB. The input jitter tolerance of

the MH89770 is shown in Figure 7.

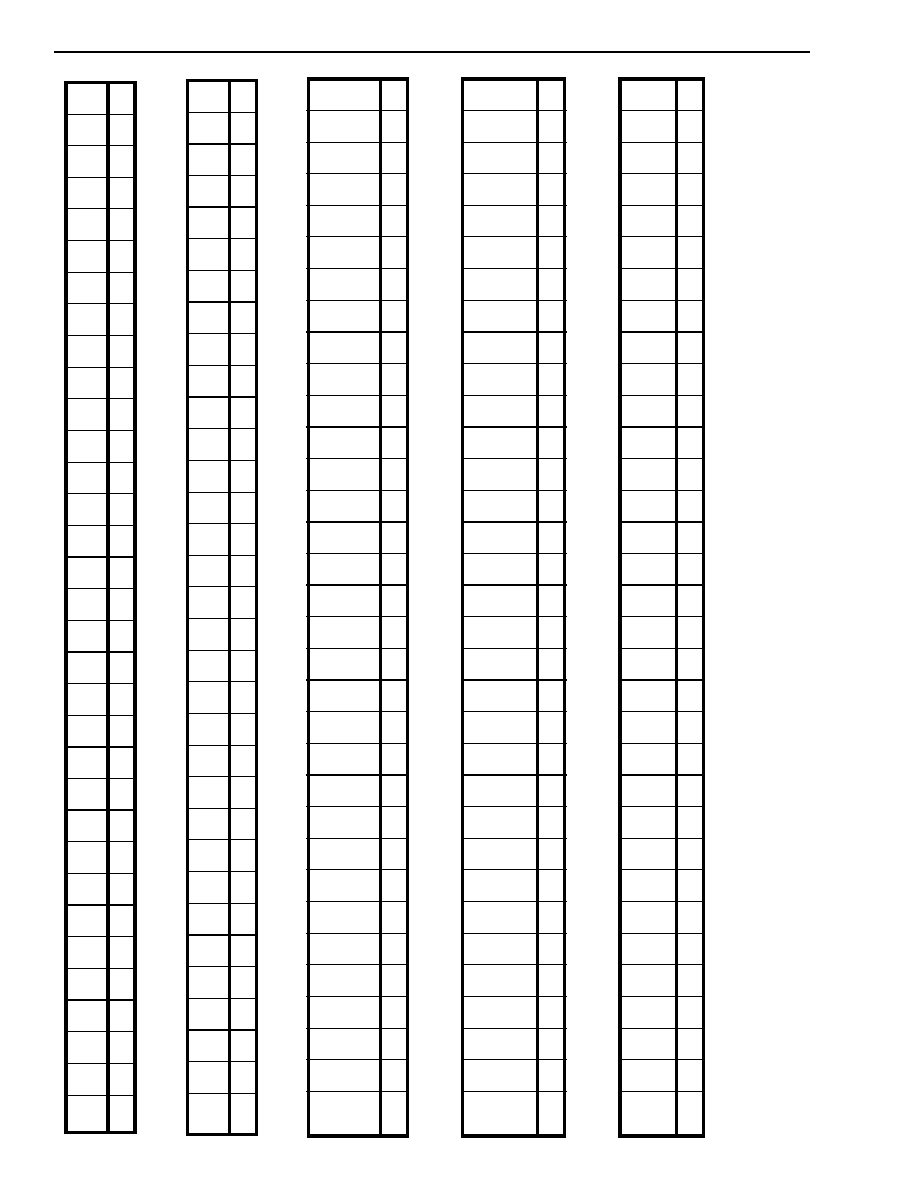

Figure 7 - Elastic Buffer Functional Diagram (156 UI Wander Tolerance)

Write

Pointer

60 CH

2 CH

47 CH

15 CH

34 CH

28 CH

386 Bit

Elastic

Store

13 CH

-13 CH

Wander Tolerance

Preliminary Information

MH89770

4-139

Elastic Buffer

The MH89770 has a two frame elastic buffer which

absorbs jitter in the received DS1 signal. The buffer

is also used in the rate conversion between the

1.544 Mbit/s DS1 rate and the 2.048 Mbit/s ST-BUS

data rate.

The received data is written into the elastic buffer

with the extracted 1.544 MHz clock. The data is read

out of the buffer on the ST-BUS side with the system

2.048 MHz clock. The maximum delay through the

buffer is 1.875 ST-BUS frames or 60 ST-BUS

channels, see Figure 7. The minimum delay required

to avoid bus contention in the buffer memory is two

ST-BUS channels.

Under normal operating conditions, the system C2i

clock is phase locked to the extracted E1.5o clock

using external circuitry. If the two clocks are not

phase-locked, then the rate at which the data is

being written into the device on the DS1 side may

differ from the rate at which it is being read out on

the ST-BUS side. The buffer circuit will perform a

controlled slip if the throughput delay conditions

described above are violated. For example, if the

data on the DS1 side is being written in at a rate

slower than what it is being read out on the ST-BUS

side, the delay between the received DS1 write

pointer and the ST-BUS read pointer will begin to

decrease over time. When this delay approaches the

minimum two channel threshold, the buffer will

perform a controlled slip which will reset the internal

ST-BUS read pointers so that there is exactly 34

channels delay between the two pointers. This will

result in some ST-BUS channels containing

information output in the previous frame. Repetition

of up to one DS1 frame of information is possible.

Conversely, if the data on the DS1 side is being

written into the buffer at a rate faster than it is being

read out on the ST-BUS side, the delay between the

DS1 frame and the ST-BUS frame will increase over

time. A controlled slip will be performed when the

throughput delay exceeds 60 ST-BUS channels. This

slip will reset the internal ST-BUS counters so that

there is a 28 channel delay between the DS1 write

pointer and the ST-BUS read pointer, resulting in

loss of up to one frame of received DS1 data.

Figure 7 illustrates the relationship between the read

and write pointers of the receive elastic buffer.

Measuring clockwise from the write pointer, if the

read pointer comes within two channels of the writer

pointer a frame slip will occur, which will put the read

pointer 34 channels from the write pointer.

Conversely, if the read pointer moves more than 60

channels from the write pointer, a slip will occur,

which will put the read pointer 28 channels from the

write pointer. This provides a worst case hysteresis

of 13 ST-BUS channels peak (26 ST-BUS channels

peak-to-peak). This can be translated into a low

frequency jitter (wander) tolerance value, accounting

for the DS1 to ST-BUS rate conversion, as follows:

(1.544/2.048) X 26 X 8 = 156 UI pp.

There is no loss of frame sync, multiframe sync or

any errors in the signalling bits when the device

performs a slip. The information on the FDL pins in

ESF or SLC-96 mode will, however, undergo slips at

the same time.

Framing Algorithm

A state diagram of the framing algorithm is shown in

Figure 8. The dotted lines show which feature can be

switched in and out depending upon the operating

mode of the device.

In ESF mode, the framer searches for the FPS bits.

Once this pattern is detected and verified, bit 0 in

Master Status Word 1 is cleared.

When the device is operating in the D3/D4 format,

the framer searches for the F

T

pattern, i.e., a

repeating 1010... pattern in a specific bit position

every alternate frame. It will synchronize to this

pattern and declare valid terminal frame

synchronization by clearing bit 0 in Master Status

Word 1. The device will subsequently initiate a

search for the F

S

pattern to locate the signalling

frames (see Figure 21). When a correct F

S

pattern

has been located, bit 3 in Master Status Word 1 is

cleared indicating that the device has achieved

multiframe synchronization.

Note: the device will remain in terminal frame

synchronization even if no F

S

pattern can be located.

In D3/D4 format, when the CRC/MIMIC bit in Master

Control Word 1 is cleared, the device will not go into

synchronization if more than one bit position in the

frame has a repeating 1010.... pattern, i.e., if more

than one candidate for the terminal framing position

is located. The framer will continue to search until

only one terminal framing pattern candidate is

discovered. It is, therefore, possible that the device

may not synchronize at all in the presence of PCM

code sequences (e.g., sequences generated by

some types of test signals) which contain mimics of

the terminal framing pattern.

4-140

MH89770

Preliminary Information

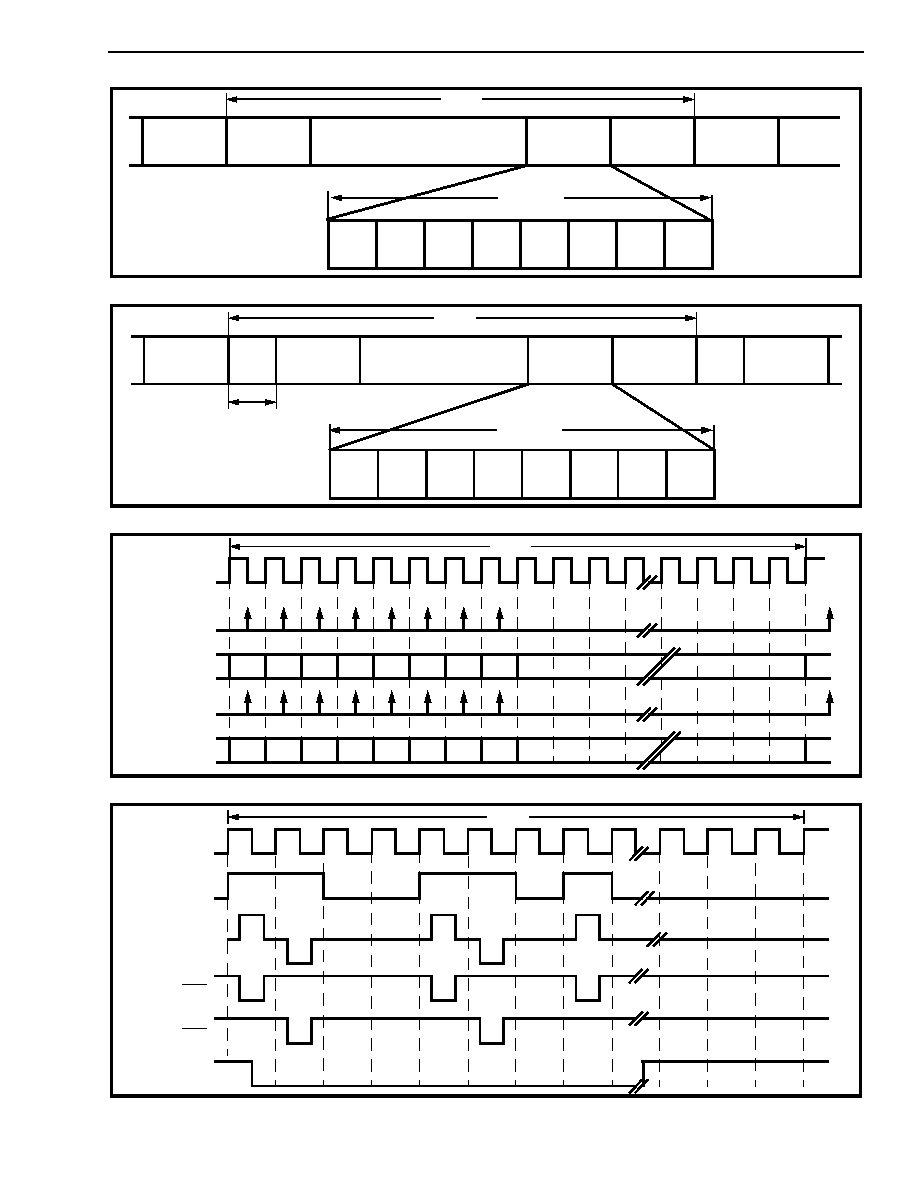

Figure 8 - Off-Line Framer State Diagram

Hunt Mode

False Candidate

False

Candidate

Forced

Reframe

Out of

Sync.

False

Candidate

Verify

Candidate

Candidate

CRC

Check

In sync

Candidate

*

Candidate

Valid Candidate

Maintenance

Resync

Receiver

Valid Candidate

New Frame Position

* Note: Only when in ESF mode and CRC

option is enabled.

Setting CRC/MIMIC bit high will force the framer to

synchronize to the first terminal framing pattern

detected. In standard D3/D4 applications, the user's

system software should monitor the multiframe

synchronization state indicated by bit 3 in Master

Status Word 1. Failure of the device to achieve

multiframe synchronization within 4.5ms of terminal

frame synchronization, is an indication that the

device has framed up to a terminal framing pattern

mimic and should be forced to reframe.

One of the main features of the framer is that it

performs its function "off line". That is, the framer

repositions the receive circuit only when it has

detected a valid frame position. When the framer

exits maintenance mode the receive counters remain

where they are until the framer has found a new

frame position. This means that if the user forces a

reframe when the device was really in the right

place, there will not be any disturbance in the circuit

because the framer has no effect on the receiver

until it has found synchronization.

The out of

synchronization criterion can be controlled by bit 0 in

Master Control Word 2. This bit changes the out of

frame conditions for the maintenance state.

4-141

Preliminary Information

MH89770

Figure 9 - Reframe Time

AAA

AAA

AAA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAAAAA

AAAAAA

AAA

AA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AA

AA

AA

AA

AA

AA

AA

AA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AA

AAA

AAA

AA

AAA

AAA

AAA

AAA

AAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAAA

AAA

AAA

AAA

AAA

AAA

AAA

50

40

30

20

10

0

%

0

7

8

10

12

14

16

18

20

22

24

26

28

30

32

34

Reframe Time (ms)

Percentage Reframe Time Probability Versus Reframe Time

With Pseudo Random Data

D4

ESF

The out of sync threshold can be changed from 2 out

of 4 errors in F

T

(or FPS) to 4 out of 12 errors in F

T

(or FPS). The average reframe time is 24 ms for ESF

mode, and 12ms for D3/D4 modes.

Figure 9 is a bar graph which shows the probability

of achieving frame synchronization at a specific time.

The chart shows the results for ESF mode with CRC

check, and D3/D4 modes of operation. The average

reframe time with random data is 24 ms for ESF, and

13 ms for D3/D4 modes. The probability of a

reframe time of 35 ms or less is 88% for ESF

mode, and 97% for D3/D4 modes. In ESF mode it is

recommended that the CRC check be enabled

unless the line has a high error rate. With the CRC

check disabled the average reframe time is greater

because the framer must also check for mimics.

Applications

1. Typical T1 Application

Figure 10 shows the external components that are

required in a typical T1 application using the

MH89770. The MT8980 is used to control and

monitor the device as well as

switch data to DSTi and

DSTo (refer to Application Note MSAN-123 for more

information on the operation of the MT8980). The

MT8952, HDLC protocol controller, is shown in this

application to illustrate how the data on the FDL

could be used. The digital phase-locked loop, the

MT8941, provides all the clocks necessary to make

a functional interface. The 1.544 MHz clock

extracted by the MH89770 is used to clock in data at

RxT and RxR. It is also internally divided by 193 to

obtain an 8 kHz clock which is output at E8Ko. The

MT8941 uses this 8 kHz signal to provide a phase

locked 2.048 MHz clock for the ST-BUS interface

and a 1.544 MHz clock for the DS1 transmit side.

Note: the configurations shown in Figures 10 and 12

using the MT8941 may not meet specific jitter

performance requirements. A more sophisticated

PLL may be required for applications designed to

meet specific standards. Please refer to the MT8941

data sheet for further details on its jitter performance.

The split phase unipolar signals output by the

MT8977 at TxA and TxB are used by the line driver

circuit to generate a bipolar AMI signal. The line

driver is transformer coupled to an equalization

circuit and the DS1 line. Equalization of the

transmitted signal is required to meet AT & T

specifications for crossconnect compatible

equip-ment (see AT&T Technical Advisory #34).

Specifica-tions for the input and output transformers

are shown in Figure 11. On the receive side the

bipolar line signal is converted into a unipolar format

by the line receiver circuit. The resulting split phase

signals are input at the RxA and RxB pins on the

4-142

MH89770

Preliminary Information

Figure 10 - Typical ESF Configuration

Figure 11 - Typical Parameters of the Input and Output Transformers

∑

∑

Tx

Line

Driver

RX

EQU

DIP SWITCH

MH89761

OUTA

OUTB

RxT

12.352 MHz

Osc.

16.384 MHz

Osc.

1.544 MHz

MT8941

CVb

F0i

C2o

F0b

C4b

C8Kb

Micro

Processor

CLOCK

EXTRACTOR

MT8977

TxFDL

TxFLDClk

RxFDL

E1.5i

RxD

TxSF

RxSF

E8Ko

RxFDLClk

F0i

C1.5i

RxA

RxB

C2i

DSTi

TxA

TxB

CSTi1

CSTo

CSTi0

DSTo

MT8980

STi3

STo3

STo0

STi0

STi1

STo2

C4i

F0i

STo1

MT8952

CDSTo

CDSTi

Cki

∑

∑

∑

RxR

MH89770

Line

Receiver

Parameter

Input Transformer

Output Transformer

Units

Line Impedance

100

100

Inductance

(1-8) >2.2

(4-8) 0.46

mH

Turns Ratio

(1-8):(3-6) 1:1

(1-8):(4-5) 1:1

(1-5):(4-8) 1.89:1

(2-6):(4-8) 1.89:1

Isolation

1500

1500

V(rms)

Line Side

MH89770

∑

∑

∑

O

O

O

O

O

O

1

8

3

4

6

5

Line Side

MH89770

∑

∑

∑

O

O

O

O

O

O

6

4

5

1

8

2

4-143

Preliminary Information

MH89770

Figure 12 - Using the MH89770 in a Parallel Bus Environment

MH89770

MT8920B

(Mode 2)

D

0

-D

7

A

0

-A

5

CS

R/W

OE

MMS MS1 24/32

STo0

STi0

STo1

C4i

F0i

+5V

+5V

MT8977

E8Ko

RxD

RxB

RxA

TxB

TxA

E1.5i

C1.5i

C2i

F0i

CSTi1

CSTo

CSTi0

DSTo

DSTi

CLOCK

EXTRACTOR

MMS

High Speed

Parallel

Telecom Bus

Line

Rx

Driver

Line

Tx

Driver

OUTA

OUTB

RxT

RxR

EQU

DIP

SWITCH

MT8941

CVb

F0i

C2o

F0b

C4b

C8Kb

12.352 MHz

Osc.

16.384 MHz

Osc.

∑

∑

∑

∑

∑

∑

∑

MT89761

Signalling and

Link Control

BUS

IACK

IRQ

DTACK

R/W

DS

CS

A

0

-A

5

D

0

-D

7

STo0

STi0

STo1

C4i

F0i

MT8920B

(Mode 1)

1.544 MHz

MT8976. The signals are combined to produce a

composite return to zero signal which is clocked into

the MT8976 at RxD.

2. Interfacing the MH89770 to a Parallel Bus

The MH89770 can be interfaced to a high speed

parallel bus or to a microprocessor using MT8920B

Parallel Access Circuit (STPA). Fig. 12 shows the

MT8977 interfaced to a parallel bus structure using

two STPA's operating in modes 1 and 2.

The first STPA operating in mode 2 (MMS=0,

MS1=1, 24/32=0), routes data and/or voice

information between the parallel telecom bus and the

T1 or CEPT link via DSTi and DSTo. The second

STPA, operating in mode 1 (MMS=1) provides

access from the signalling and link control bus to the

MH89770 status and control channels. All signalling

and link functions may be controlled easily through

the STPA transmit RAM's Tx0, Tx1, while status

information is read at receive RAM Rx0. In addition,

interrupts can be set up to notify the system in case

of slips, loss of sync, alarms, violations, etc.

3. PCM/Voice Channel Bank

The D3/D4 channel bank is one of the most widely

used pieces of equipment in the North American

network today. The D3/D4 channel converts 24

analog telephone lines into the 24 channels of a T1

serial stream. The channel bank is the interface point

between a digital switching or transmission system

and the analog telephone loop. The industry is

moving towards end-to-end digital connections

(ISDN), but the analog channel bank will still be in

use for many years to come.

4-144

MH89770

Preliminary Information

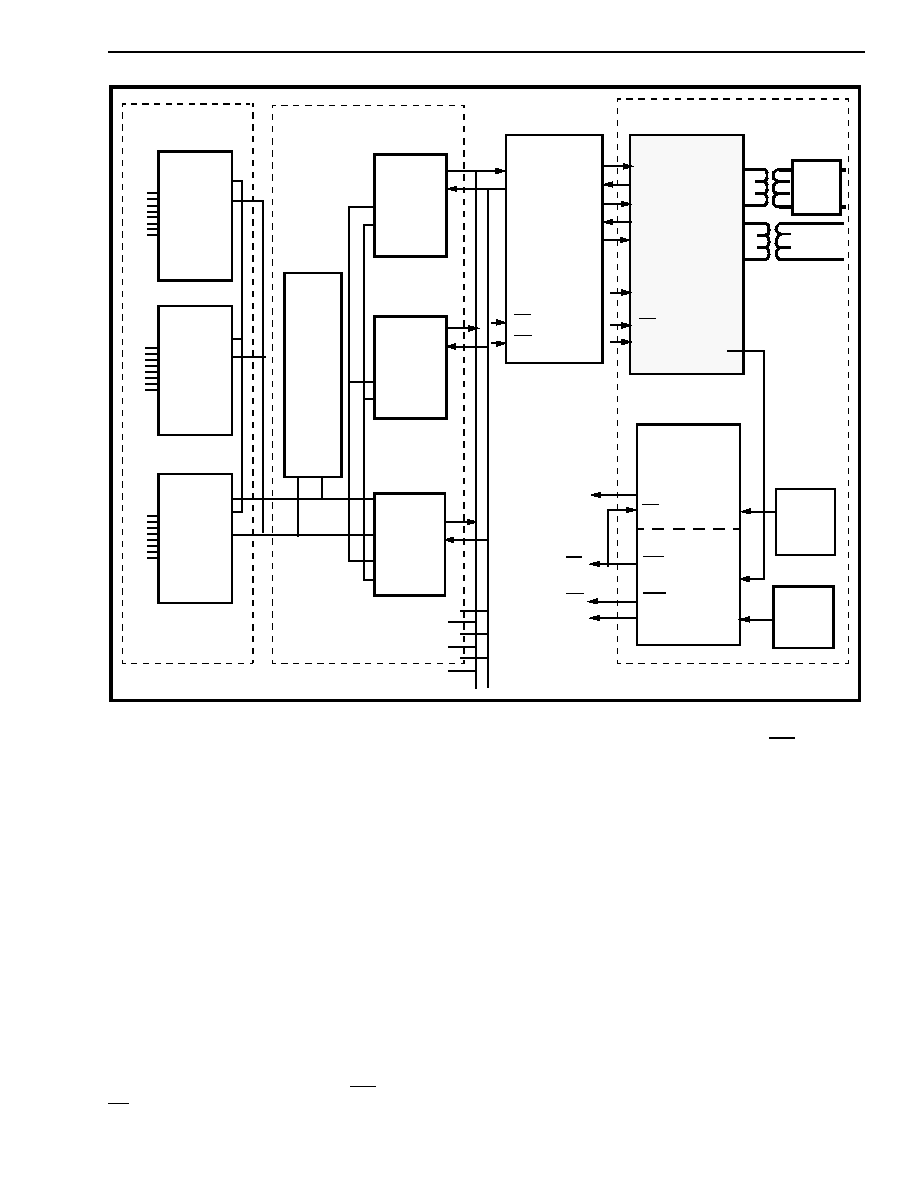

Figure 13 - PCM/Voice Data Channel Bank

Switch Matrix

T1 Interface

Equal-

izer

12.352

MHz Osc.

16.384

MHz Osc.

MT8941

DPLL#1

CVb

F0i

C12i

DPLL#2

F0b

C4b

C2o

C8Kb

C16i

MH89770

DSTi

DSTo

CSTi0

CSTo

CSTi1

C2i

F0i

C1.5i

OUTA

OUTB

RxR

E8Ko

RxT

µ

P

MT8980

STo0

STi0

STo3

STi3

F0i

C4i

STo1

STi1

STo2

STi2

STo4

C1.5i

C2i

C4i

F0i

Shift

Reg.

MT8870

MT8964

MT8870

MT8964

Shift

Reg.

CTLo

OFHK

MUX

Signalling Interface

Analog Line Interface

SLIC #1

CTLi

OFHK

STD

#1

D3

Do

#1

#N

Do

STD

D3

#N

PCMi

PCMi

PCMo

T

R

T

R

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

SLIC #24

Figure 13 shows a block diagram of a channel bank

that has been divided into four sections, the analog

line interface, signalling interface, switch matrix, and

T1 interface. The subscriber line interface circuit

(SLIC) provides interface to the telephone line, i.e.,

provides loop current and ringing voltage, and

converts the analog voice signal into µ

-

Law PCM.

The SLIC also detects the off-hook condition for

conventional POTS (Plain Old Telephone Set)

signalling.

Once the voice is encoded into digital format the

switch matrix transfers the 24 consecutive channels

that are received from the SLICs to the 24 valid

channels used by the MH89770. The MH89770

formats and transmits this information on the T1 line.

Signalling information from the telephone sets can

be routed straight through to the output T1 channel,

or it can be routed to the DTMF receiver pool. This is

easily accomplished by the MT8980 switch matrix

once the SLIC has digitized the analog signal.

Channel banks must be able to operate in a loop

timed mode so that they meet the clock

synchronization requirements of a level four entity.

Phase-locked loop #2 of the MT8941 generates the

ST-BUS clocks that are synchronized to the

extracted 8kHz clock, and phase-locked loop #1

generates the transmit T1 clock synchronized to the

ST-BUS.

4. ISDN Voice/Data Channel Bank/Concentrator

The ISDN channel bank is a term that is used in this

context to describe a system that performs the same

logical function as the D3/D4 channel bank. That is,

it concentrates the subscribers digital loop into the

primary digital transmission scheme, the T1 trunk.

4-145

Preliminary Information

MH89770

Figure 14 - ISDN Voice Data Channel Bank

Digital Line Interface

Switch Matrix

T1 Interface

MT8910

MT8980

MT8910

MT8952

MT8952

MT8952

MT8941

Z

T

Z

T

DSTo

DSTi

DSTo

DSTi

DSTo