| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MM1068 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

MITSUMI

No-adjustment Sync Separator MM1068

No-adjustment Sync Separator

Monolithic IC MM1068

Outline

This IC is a no-adjustment sync IC designed for use in VCR, TV and other video equipment. A ceramic

resonator is used in the oscillation circuit for stable operation.

Features

1. Sync separator with AFC

2. Ceramic resonator means no adjustment required

3. High precision due to use of PLL format

4. Ceramic resonator can be selected for use in either PAL or NTSC

5. Power supply voltage V

CC

=5V

Package

SIP-10A (MM1068XS)

Applications

1. TV

2. VCR

3. Other video equipment

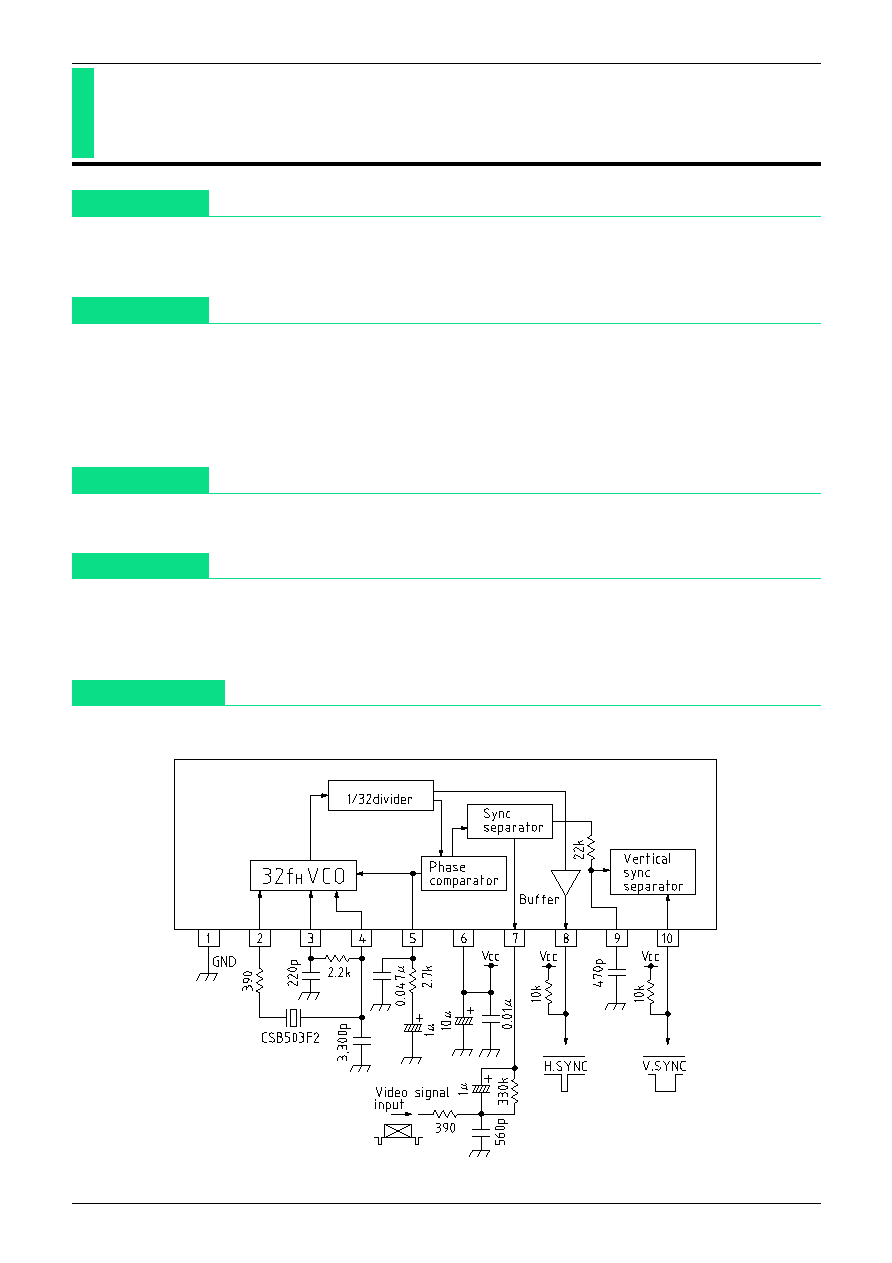

Block Diagram

MITSUMI

No-adjustment Sync Separator MM1068

Pin Description

Pin no.

Pin name

Internal equivalent circuit diagram Pin no.

Pin name

Internal equivalent circuit diagram

1

GND

2

OSC OUT

3

OSC IN1

4

OSC IN2

5

LPF

6

V

CC

7

VIDEO IN

8

H.SYNC

9

V.INT

10

V.SYNC

Absolute Maximum Ratings

(Ta=25∞C)

Item

Symbol

Ratings

Units

Storage temperature

T

STG

-40~+125

∞C

Operating temperature

T

OPR

-20~+75

∞C

Power supply voltage

V

CC

max.

7

V

Allowable loss

Pd

500

mW

MITSUMI

No-adjustment Sync Separator MM1068

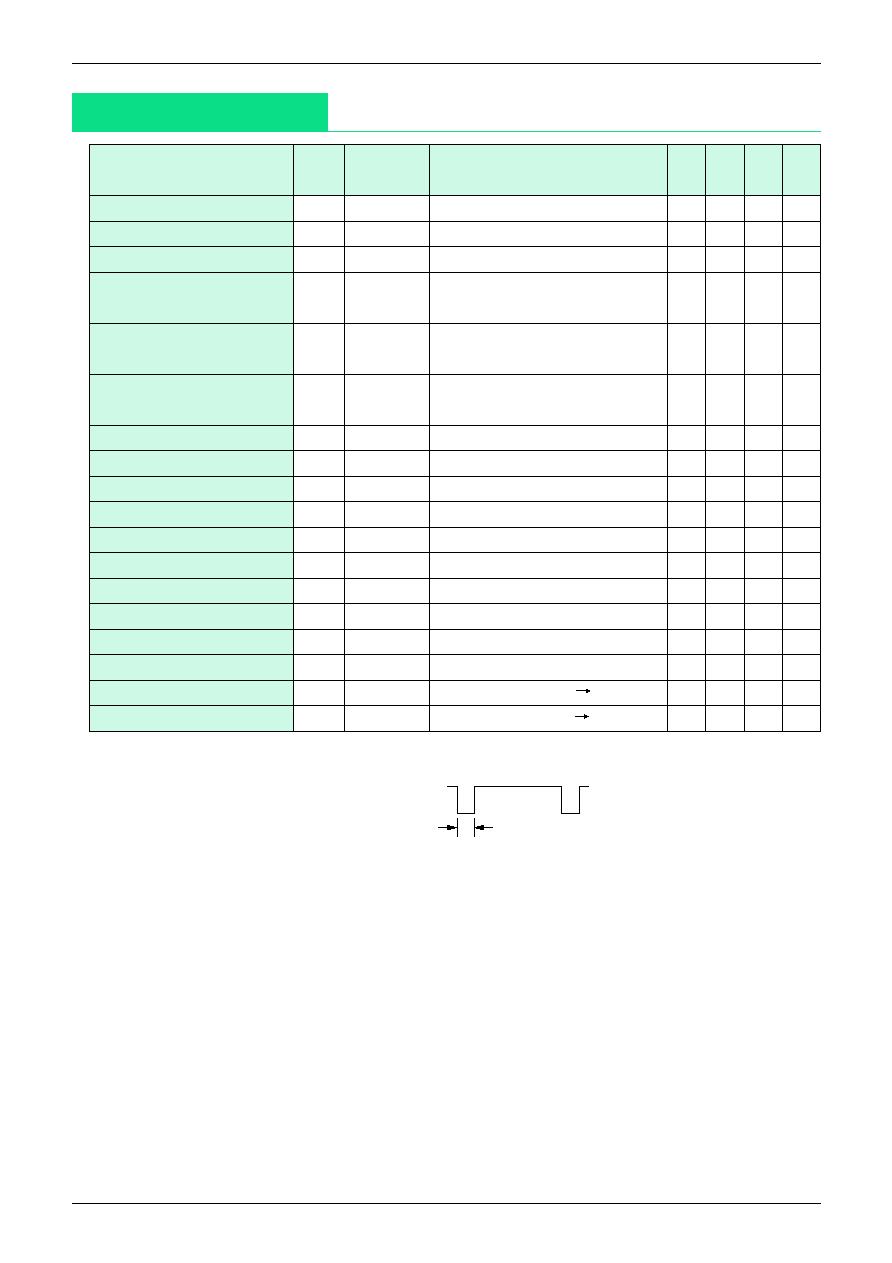

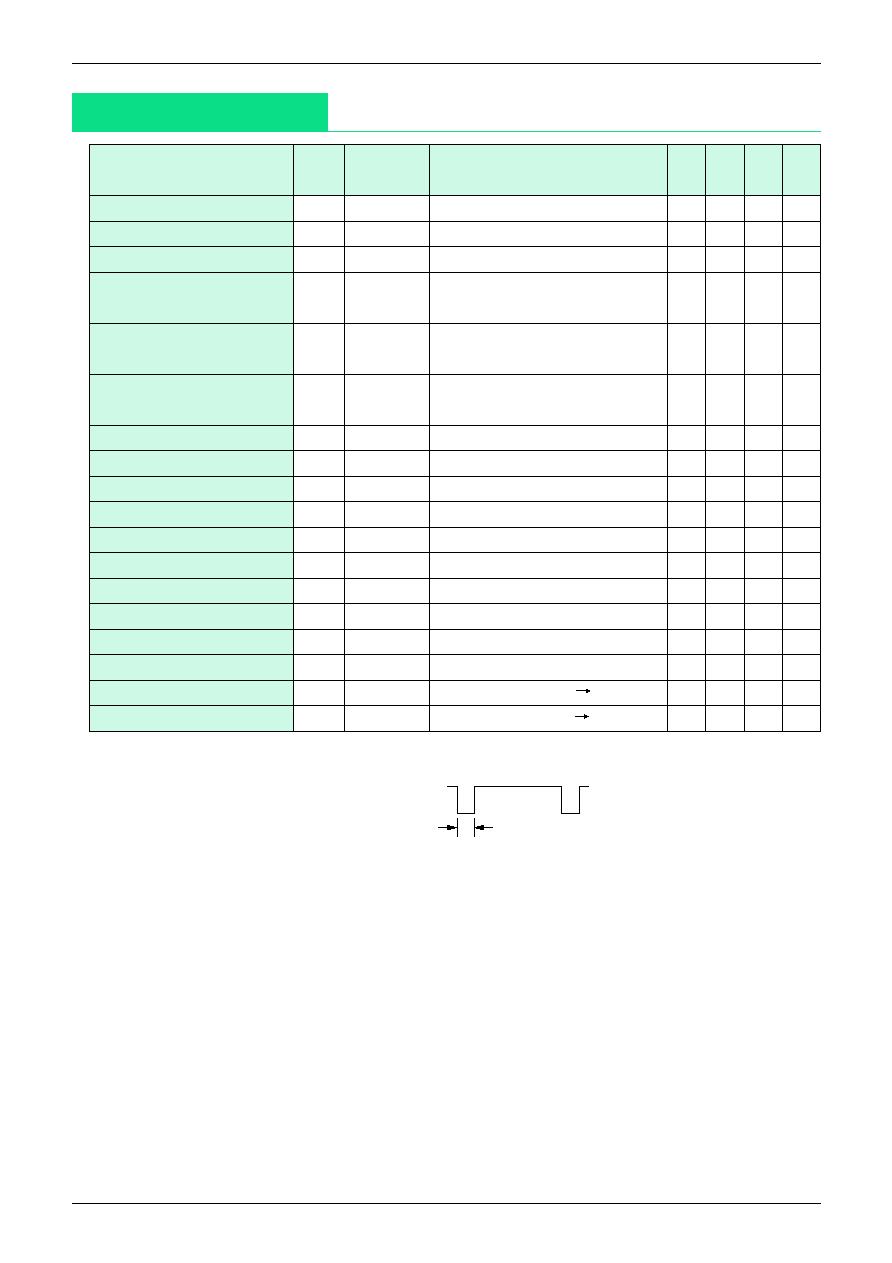

Electrical Characteristics

(Except where noted otherwise, Ta=25∞C, V

CC

=5.0V, X=CSB503F2,

R=390 [OHM], C=3300pF, SW1=ON, SW2=OFF)

Item

Symbol

Measurement

Measurement conditions

Min. Typ. Max. Units

circuit

Operating power supply voltage

V

CC

V

CC

4.7

5.0

5.3

V

Consumption current

Id

Id

8.0

11.5 mA

Free-running frequency NTSC

f

O

1

TP1

15.534 15.734 15.934 kHz

Horizontal sync signal

f

CAP

1

TP1

V

IN

: signal 1

*

1

*

2

300

500

Hz

acquisition range NTSC

Free-running frequency PAL

f

O

2

TP1

X=CSB500F40, R=200OHM,

C=4700pF

15.425 15.625 15.825 kHz

Horizontal sync signal

f

CAP

2

TP1

X=CSB500F40, R=200OHM,

acquisition range PAL

C=4700pF, V

IN

: signal 1

*

1

*

3

300

500

Hz

LPF pin DC level

V

LPF

TP4

SW2 : ON

0.9

1.4

1.9

V

Sync separation level

V

SEPA

V

IN

SW1 : OFF, V

IN

: staircase wave 1V

P-P

*

4

20

50

80

mV

H. sync pulse width

t

W

1

TP1

V

IN

: signal 1, 15.734kHz

*

5

3.9

4.2

4.5

uS

H. sync delay time

T

d

1

TP1

V

IN

: signal 1, 15.734kHz

*

5

0.7

1.2

1.7

uS

H. sync output voltage L

V

L

1

TP1

V

IN

: signal 1, 15.734kHz

*

5

0.2

0.4

V

H. sync output voltage H

V

H

1

TP1

V

IN

: signal 1, 15.734kHz

*

5

4.8

5.0

V

V. sync pulse width

t

W

3

TP3

V

IN

: staircase wave 1V

P-P

*

6

150

190

230

uS

V. sync delay time

t

d

3

TP3

V

IN

: staircase wave 1V

P-P

*

6

8.0

10.0 12.0

uS

V. sync output voltage L

V

L

3

TP3

V

IN

: staircase wave 1V

P-P

*

6

0.2

0.4

V

V. sync output voltage H

V

H

3

TP3

V

IN

: staircase wave 1V

P-P

*

6

4.8

5.0

V

V. sync switching voltage L

V

THL

3

TP2

TP2 : DC voltage 5V Low

*

7

1.5

1.8

2.1

V

V. sync switching voltage H

V

THH

3

TP2

TP2 : DC voltage 0V High

*

7

2.3

2.6

2.9

V

Notes:

*

1 Signal 1 : Pulse signal with 0.3V amplitude and pulse width 4.7µS

*

2 Measuring horizontal sync signal pull-in range for NTSC

With TP1 waveform not synchronized to signal 1, adjust signal 1 frequency toward 15.734kHz. The

measurement value is the smaller of the synchronized frequency and the difference from 15.734.

*

3 Measuring horizontal sync signal pull-in range for PAL

With TP1 waveform not synchronized to signal 1, adjust signal 1 frequency toward 15.625kHz. The

measurement value is the smaller of the synchronized frequency and the difference from 15.625.

*

4 Measuring sync separation level

Gradually lower staircase wave signal sync tip level, and measure sync tip level when Pin 9 waveform

starts to change.

Signal 1 waveform

4.7uS

MITSUMI

No-adjustment Sync Separator MM1068

*

5 H. SYNC measurement

*

6 V. SYNC measurement

*

7 V. SYNC switching voltage measurement

Gradually change the DC voltage impressed on TP2, and measure TP2 voltage when TP3 output switches.

Signal 1

TP1 waveform

t

w

1

t

d

1

V

H

1

V

L

1

Input video signal

(Horizontal sync signal portion)

TP3 waveform

t

w

3

t

d

3

V

H

3

V

L

3

Measuring Circuit

NTSC

PAL

X

CSB503F2

CSB500F40

R

390

220

C

3300pF

4700pF

Note :

*

1

MITSUMI

No-adjustment Sync Separator MM1068

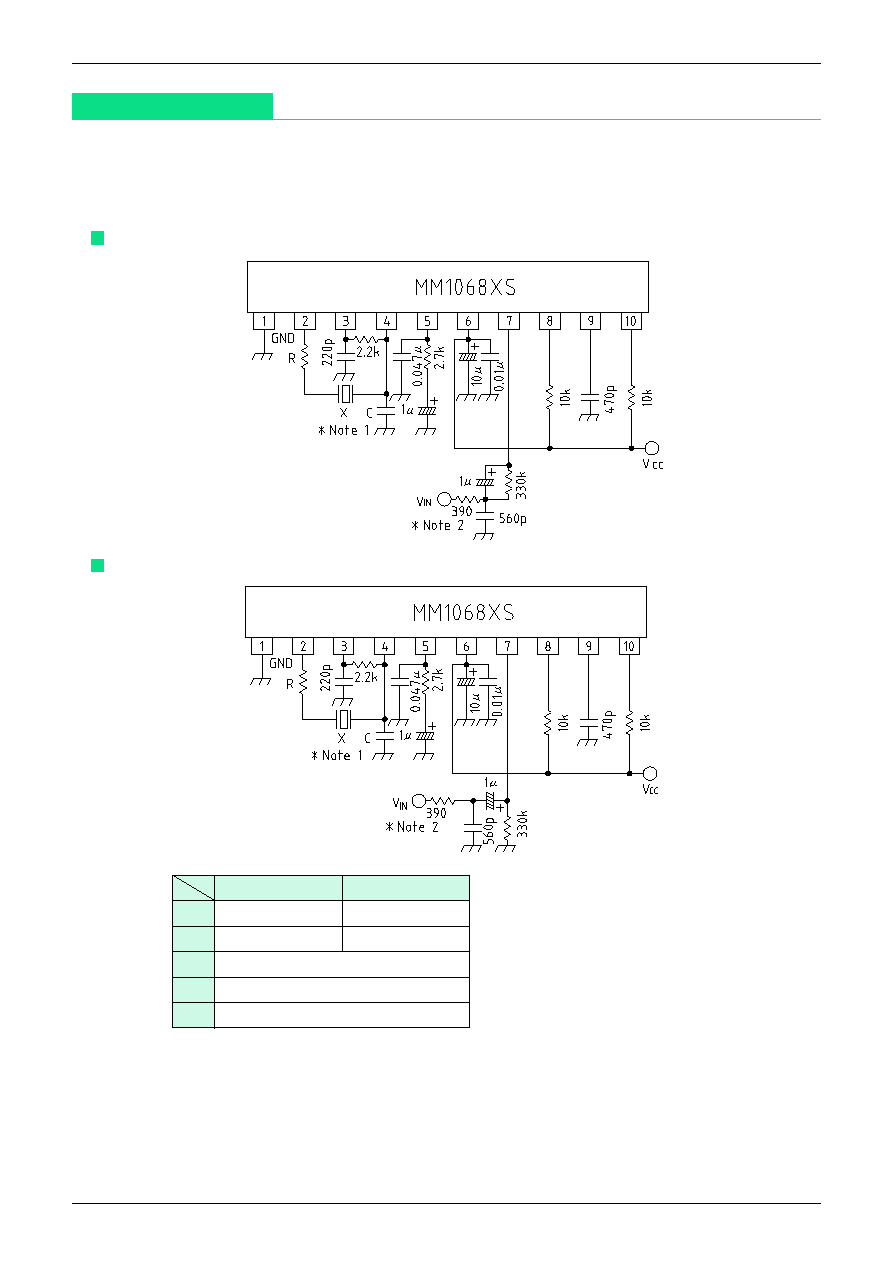

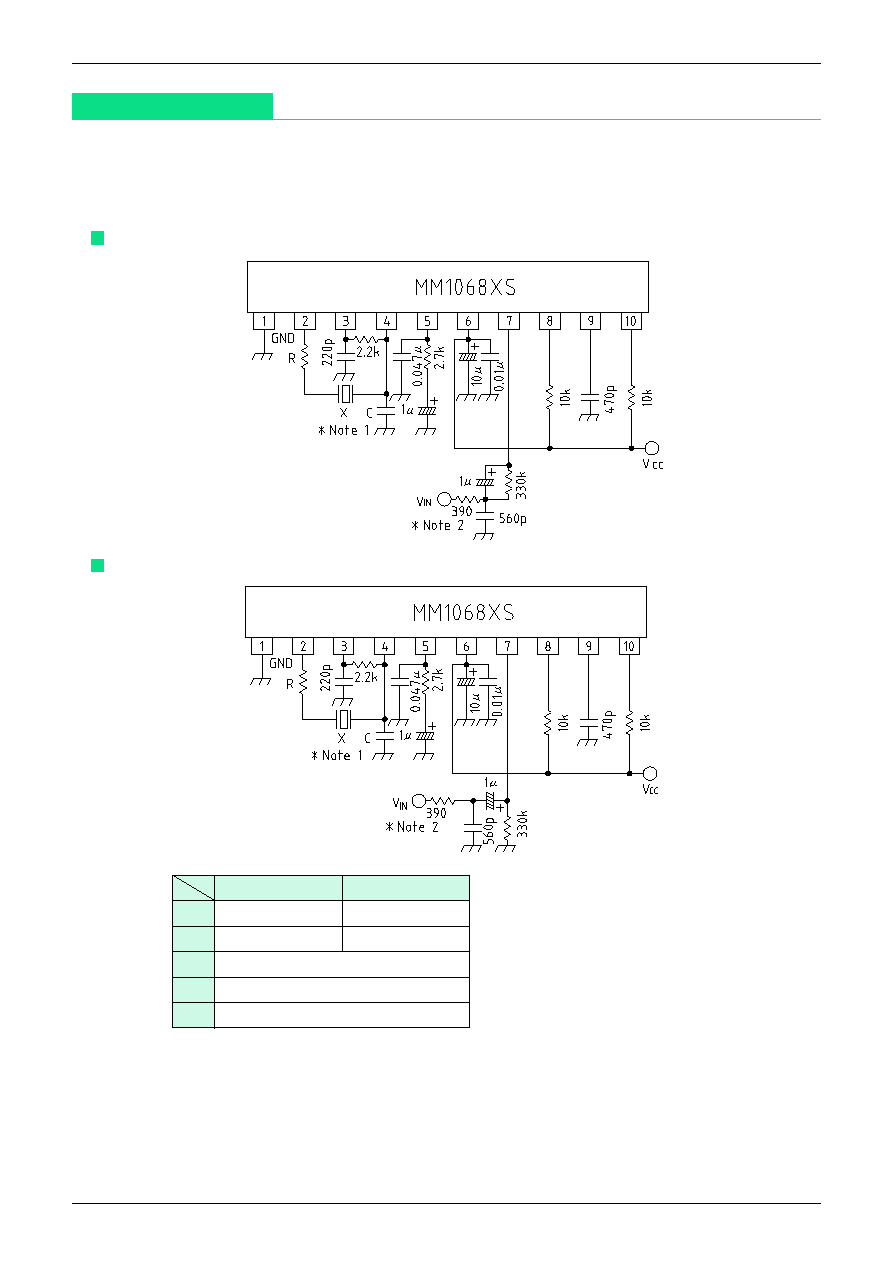

Application Circuits

There is a momentary phase lag in the H. SYNC output vertical feedback interval. When using this IC for OSD

timing, characters at the top of the screen may bend due to IC deviation. If this happens, change the

resistance between Pins 13 and 14 as shown, and the bending will improve by several H from the top edge of

the screen.

Application Circuit 1

Application Circuit 2

Note 1 : 1.

*

1

NTSC

PAL

X

CSB503F2

CSB500F40

R1

1.5k

1.8k

R2

390

C1

220pF

C2

3300pF

Note 2 :

1.

*

2 Input signal sync tip must be less than

1V for application circuit 1 Pin 7

external circuit.

2. The above 1. does not apply for

application circuit 2 Pin 7 external circuit.

Pin 1 is clamped at approximately 2.5V.

2. Resistors R1 and R2 should have precision of ±1%.

3. Capacitors C1 and C2 should have precision of

±5% and temperature characteristic of CH class.