| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: MS6266 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

MO

SA

MS6266

6-Channel Electronic Volume Controller

REV1

1

www.mosanalog.com.tw

6-Channel Volume Controller

Gain and Attenuation 16~-79dB

Low voltage, High Channel Separation

FEATURES

Operation range: 2.7V~5.5V

Low power consumption

Gain/Attenuation: 16dB to ≠79dB at 1dB/step

Good PSRR

I

2

C interface

Pop noise free

Housed in SSOP20, SOP20

APPLICATIONS

Multimedia system

Hi-Fi audio system

Car audio

Portable audio equipment

DESCRIPTION

The MS6266 is a 6-channel volume controller IC with gain and attenuation. It uses CMOS technology specially for the

low voltage application with low noise, rail-to-rail output. The MS6266 provide an I

2

C control interface with gain /

attenuation range of 16dB to -79dB, 1dB/step. The initial condition is set to be maximum attenuation ≠79dB and mute

on mode when the power is on.

PIN CONFIGURATION

Symbol

Pin

Description

IN1 1

1

st

channel input

IN2 2

2

nd

channel input

IN3 3

3

rd

channel input

AC2

4

Address code 2

DGND 5

Digital

Ground

SCL 6

I

2

C clock input

SDA 7

I

2

C data input

IN4 8

4

th

channel input

IN5 9

5

th

channel input

IN6 10

6

th

channel input

OUT6 11

6

th

channel output

OUT5 12

5

th

channel output

OUT4 13

4

th

channel output

GND 14

Analog

ground

V

REF

15

Reference voltage = 1/2V

DD

V

DD

16

Positive supply voltage

AC1

17

Address code 1

OUT3 18

3

rd

channel output

OUT2 19

2

nd

channel output

OUT1 20

1

st

channel output

19

18

17

20

2

3

4

1

OUT1

OUT2

OUT3

AC1

IN1

IN2

IN3

AC2

15

14

13

16

12

11

6

7

8

5

9

10

MS6266

V

DD

V

REF

GND

OUT4

OUT5

OUT6

IN6

IN5

IN4

SDA

SCL

DGND

Note: 1. The address codes have four types, selected by AC1and AC2.

MO

SA

MS6266

6-Channel Electronic Volume Controller

REV1

2

www.mosanalog.com.tw

BLOCK DIAGRAM

I

2

C Interface

Reference

source

-1dB/Step

-10dB/Step

IN1

IN2

GND

SDA

SCL

V

REF

OUT1

IN6

-1dB/Step

-1dB/Step

OUT2

OUT6

AC1

AC2

DGND

V

DD

V

REF

2dB/Step

-10dB/Step

2dB/Step

-10dB/Step

2dB/Step

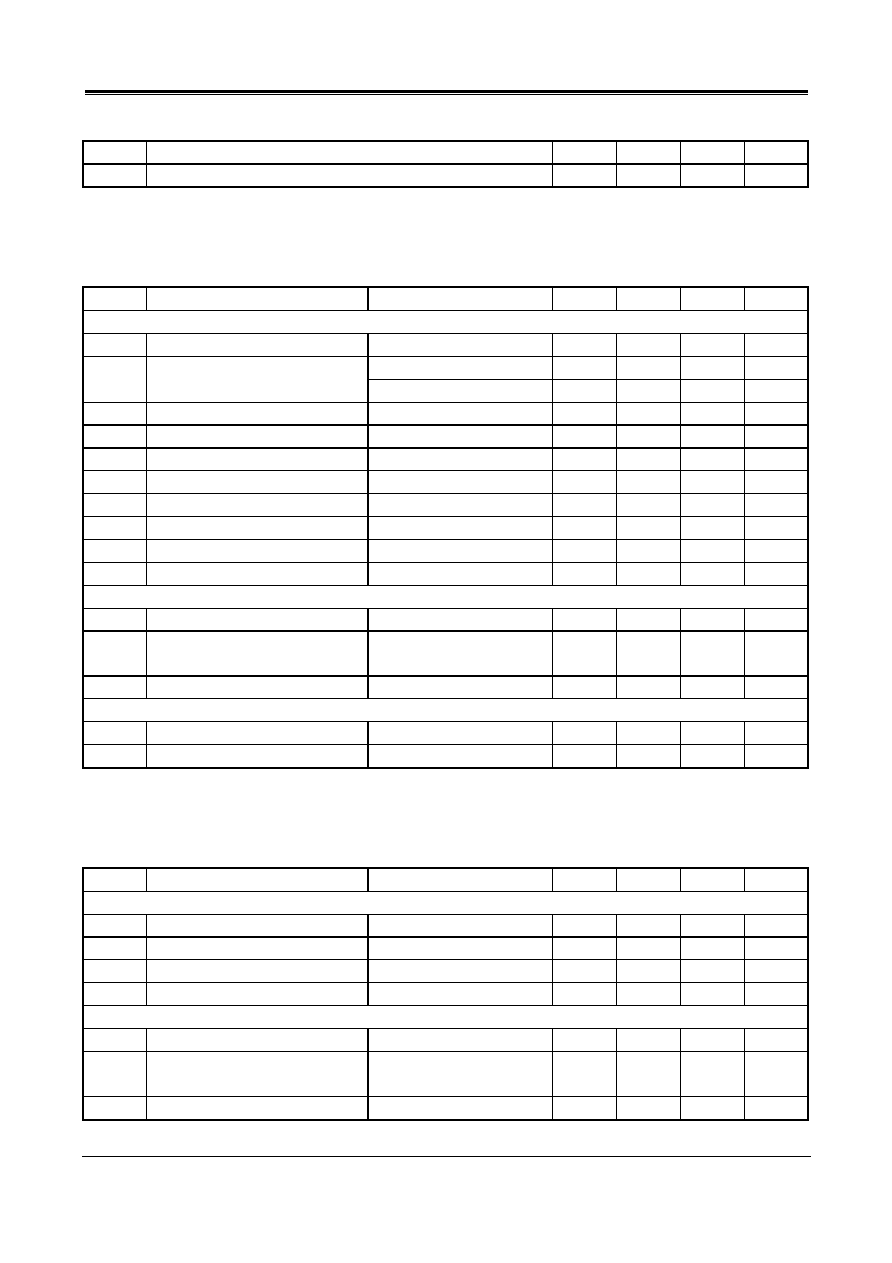

ORDERING INFORMATION

Package

Part number

Packaging Marking

Transport Media

20-Pin SOP

MS6266TR

MS6266

1k Units Tape and Reel

20-Pin SOP

MS6266U

MS6266

35 Units Tube

20-Pin SOP (lead free)

MS6266GTR

MS6266G

1k Units Tape and Reel

20-Pin SOP (lead free)

MS6266GU

MS6266G

35 Units Tube

20-Pin SSOP

MS6266SSTR

MS6266

2.5k Units Tape and Reel

20-Pin SSOP

MS6266SSU

MS6266

50 Units Tube

20-Pin SSOP (lead free)

MS6266SSGTR

MS6266G

2.5k Units Tape and Reel

20-Pin SSOP (lead free)

MS6266SSGU

MS6266G

50 Units Tube

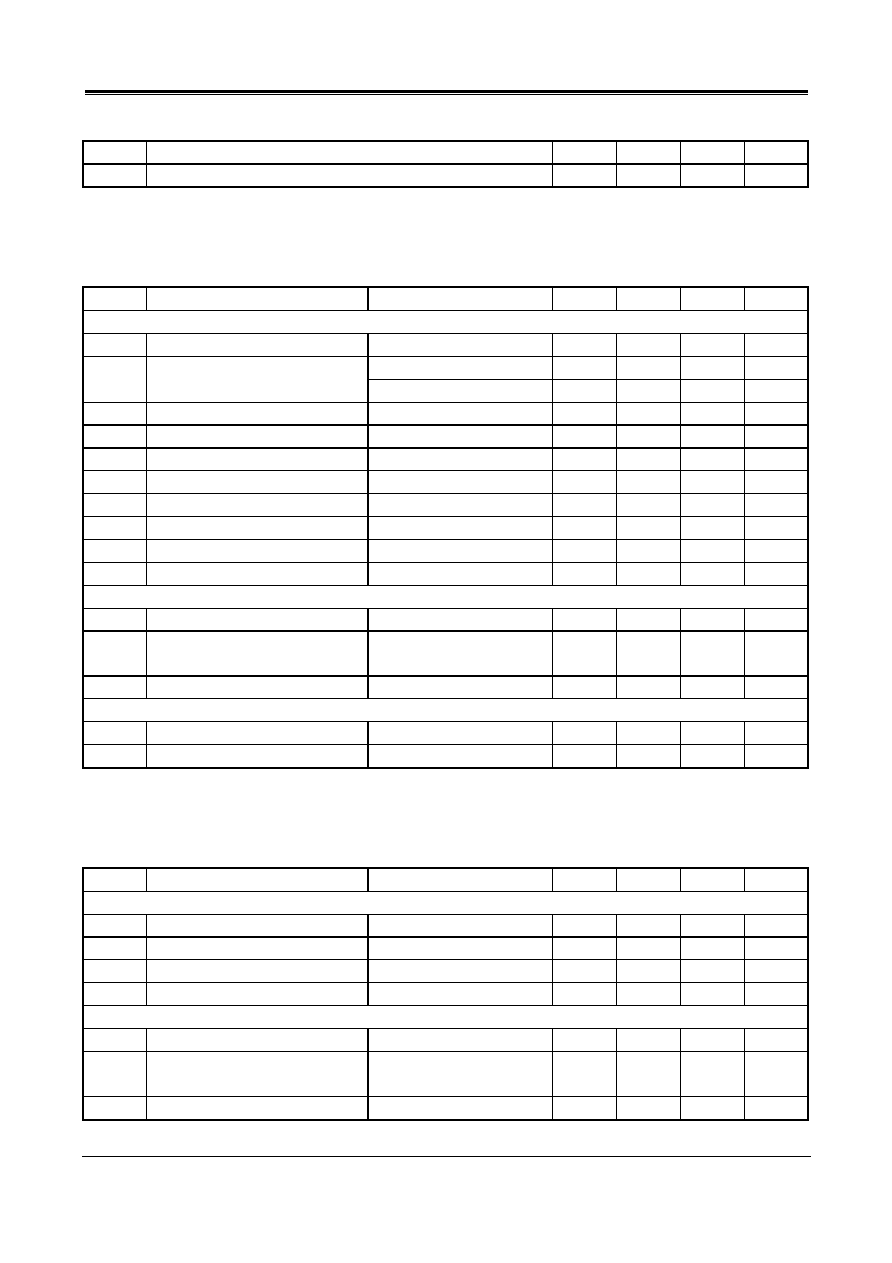

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter Rating

Unit

V

DD

Supply

Voltage

6

V

V

ESD

Electrostatic Handling

-3000 to 3000

V

T

STG

Storage Temperature Range

-65 to 150

T

A

Operating Ambient Temperature Range

-40 to 85

T

J

Maximum Junction Temperature

150

T

S

Soldering Temperature, 10 seconds

260

R

THJA

Thermal Resistance from Junction to Ambient in Free Air

SOP20

SSOP20

210

210

/W

MO

SA

MS6266

6-Channel Electronic Volume Controller

REV1

3

www.mosanalog.com.tw

OPERATING RATINGS

Symbol Parameter Min Typ Max Unit

V

DD

Supply Voltage

2.7

-

5.5

V

5V ELECTRICAL CHARACTERISTICS

(V

DD

=5.0V, V

SS

=0V, Attenuation=0dB, Gain=0dB, f=1kHz, V

O

=0dBV, V

REF

Cap=10uF; unless otherwise specified)

Symbol Parameter

Conditions Min

Typ

Max

Unit

DC Characteristics

I

Q

Quiescent current

-

10.4

11

mA

Max gain

-

16

-

dB

A

GA

Gain/Attenuation

Max attenuation

-

-79

-

dB

A

STEP

Gain/Attenuation step

-

1

-

dB

E

GA

Gain/Attenuation step error

-

0.3

-

dB

E

IGA

Interchannel gin/attenuation error

-

0.3

-

dB

CS Channel

separation

95 105 - dB

PSRR

Power supply rejection ratio

Cap = 10uF (100Hz)

-

53

-

dB

MUTE Mute

Attenuation

Vin=0dBV

-

85

-

dB

Rin Input

Impedance

18 20 - k

Rout Output

Impedance

-

50 100

AC Characteristics

Vo

Maximum output voltage swing

(THD+N)/S < 0.1%

-

4.8

-

Vpp

THD+N

Total harmonic distortion plus

noise

-

-69

-64

dB

S/N Signal-to-noise

ratio

V

O

=4.8Vpp 95

100

-

dB

Bus Characteristics

V

IH

Bus high input level

-

-

0.7V

DD

V

V

IL

Bus low input level

0.3V

DD

- - V

2.7V ELECTRICAL CHARACTERISTICS

(V

DD

=2.7V, V

SS

=0V, Attenuation=0dB, Gain=0dB, f=1kHz, V

O

=-3dBV, V

REF

Cap=10uF; unless otherwise specified)

Symbol Parameter

Conditions Min

Typ

Max

Unit

DC Characteristics

I

Q

Quiescent current

-

8.2

8.8

mA

CS Channel

separation

90 100 - dB

PSRR

Power supply rejection ratio

Cap = 10uF (100Hz)

-

51

-

dB

MUTE Mute

Attenuation

Vin=-3dBV

-

80

-

dB

AC Characteristics

Vo

Maximum output voltage swing

(THD+N)/S < 0.1%

-

2.6

-

Vpp

THD+N

Total harmonic distortion plus

noise

-

-69

-64

dB

S/N Signal-to-noise

ratio

V

O

=2.6Vpp 85

90

-

dB

MO

SA

MS6266

6-Channel Electronic Volume Controller

REV1

4

www.mosanalog.com.tw

TYPICAL PERFORMANCE CHARACTERISTICS

(Ta=25, R

L

=100k

, V

REF

Cap=10uF; unless otherwise specified)

THD+N (%)

OUTPUT VOLTAGE (dBV)

THD+N (%)

OUTPUT VOLTAGE (dBV)

THD+N (%)

OUTPUT VOLTAGE (dBV)

THD+N vs. output voltage

THD+N vs. output voltage

THD+N vs. output voltage

f=20kHz

f=20kHz

f=20kHz

f=20Hz

f=20Hz

f=20Hz

f=1kHz

f=1kHz

f=1kHz

V

DD

=5V

V

DD

=2.7V

V

DD

=3.3V

THD+N (%)

FREQUENCY (Hz)

C

H

A

N

N

E

L SEPAR

ATION

(

d

B)

FREQUENCY (Hz)

QUIE

S

C

E

N

T CURRE

NT (mA

)

SUPPLY VOLTAGE (V)

THD+N vs. frequency

Channel separation vs. frequency

Quiescent current vs. supply voltage

V

DD

=5V

V

O

=0dBV

V

DD

=3.3V

V

O

=-3dBV

V

DD

=2.7V

V

O

=-3dBV

V

DD

=3.3V

V

O

=-3dBV

V

DD

=2.7V

V

O

=-3dBV

V

DD

=5V

V

O

=0dBV

PSR

R

(

d

B)

FREQUENCY (Hz)

PSR

R

(

d

B)

FREQUENCY (Hz)

PSR

R

(

d

B)

FREQUENCY (Hz)

PSRR vs. frequency

PSRR vs. frequency

PSRR vs. frequency

CAP=22uF

CAP=22uF

CAP=22uF

CAP=10uF

CAP=10uF

CAP=10uF

CAP=2.2uF

CAP=2.2uF

CAP=2.2uF

V

DD

=5V

V

RR

=-20dBV

V

DD

=3.3V

V

RR

=-20dBV

V

DD

=2.7V

V

RR

=-20dBV

MO

SA

MS6266

6-Channel Electronic Volume Controller

REV1

5

www.mosanalog.com.tw

I

2

C BUS DESCRIPTION

Start and stop conditions

A start condition is activated when the SCL is set to HIGH and SDA shifts from HIGH to LOW state. The stop

condition is activated when SCL is set to HIGH and SDA shifts from LOW to HIGH state. Please refer to the timing

diagram below.

SDA

SCL

Start

Stop

SCL : Serial Clock Line, SDA : Serial Data Line

Data validity

A data on the SDA line is considered valid and stable only when the SCL signal is in HIGH state. The HIGH and

LOW states of the SDA line can only change when the SCL signal is LOW. Please refer to the figure below.

SDA

SCL

Data line

stable,

Data valid

Data

change

allowed

Byte format

Every byte transmitted to the SDA line consists of 8 bits. Each byte must be followed by an acknowledge bit.

The MSB is transmitted first.

Acknowledge

During the Acknowledge clock pulse, the master (up) put a resistive HIGH level on the SDA line. The peripheral

(audio processor) that acknowledges has to pull-down (LOW) the SDA line during the Acknowledge clock pulse so that

the SDA line is in a stable LOW state during this clock pulse. Please refer to the diagram below.

SCL

SDA

MSB

Acknowledge

1

2

3

7

8

9

Start

The audio processor that has been addressed has to generate an Acknowledge after receiving each byte, otherwise,

the SDA line will remain at the HIGH level during the ninth (9

th

) clock pulse. In this case, the master transmitter can

generate the STOP information in order to abort the transfer.