MOSEL VITELIC

1

V53C16258SH

HIGH PERFORMANCE

256K X 16 EDO PAGE MODE

CMOS DYNAMIC RAM

SELF REFRESH

PRELIMINARY

V53C16258SH Rev 0.3 September 1998

HIGH PERFORMANCE

50

Max. RAS Access Time, (t

RAC

)

50 ns

Max. Column Address Access Time, (t

CAA

)

24 ns

Min. Extended Data Out Mode Cycle Time, (t

PC

)

19 ns

Min. Read/Write Cycle Time, (t

RC

)

90 ns

Features

s

256K x 16-bit organization

s

EDO Page Mode for a sustained data rate of

53 MHz (-50ns)

s

RAS access time: 50 ns

s

Dual CAS Inputs

s

Low power dissipation

s

Read-Modify-Write, RAS-Only Refresh,

CAS-Before-RAS Refresh

s

Self Refresh

s

Refresh Interval: 512 cycles/8 ms

s

Available in 40-pin 400 mil SOJ and 40/44L-pin

400 mil TSOP-II packages

s

Single +5V

�

10% Power Supply

s

TTL Interface

Description

The V53C16258SH is a high speed 262,144 x 16

bit high performance CMOS dynamic random

access memory. The V53C16258SH offers a

combination of unique features including: EDO

Page Mode operation for higher sustained

bandwidth with Page Mode cycle times as short as

19ns. All inputs are TTL compatible. Input and

output capacitance is significantly lowered to

increase performance and minimize loading. These

features make the V53C16258SH ideally suited for

a wide variety of high performance computer

systems and peripheral applications.

Device Usage Chart

Operating

Temperature

Range

Package Outline

Access Time (ns)

Power

Temperature

Mark

K

T

50

Std.

0

�

C to 70

�

C

�

�

�

�

Blank

2

V53C16258SH Rev 0.2 Aug. 1998

MOSEL VITELIC

V53C16258SH

FAMILY

DEVICE

PKG

( t

RAC

)

SPEED

PWR.

V

5

3

C

2

5

8

50 (50 ns)

TEMP.

BLANK (0

�

C to 70

�

C)

BLANK (NORMAL)

K (SOJ)

H (5V)

T (TSOP-II)

H

16

S STANDARD

SELF REFRESH)

S

Pin Names

A

0

�A

8

Address Inputs

RAS

Row Address Strobe

UCAS

Column Address Strobe/Upper Byte Control

LCAS

Column Address Strobe/Lower Byte Control

WE

Write Enable

OE

Output Enable

I/O

1

�I/O

16

Data Input, Output

V

CC

+5V Supply

V

SS

0V Supply

NC

No Connect

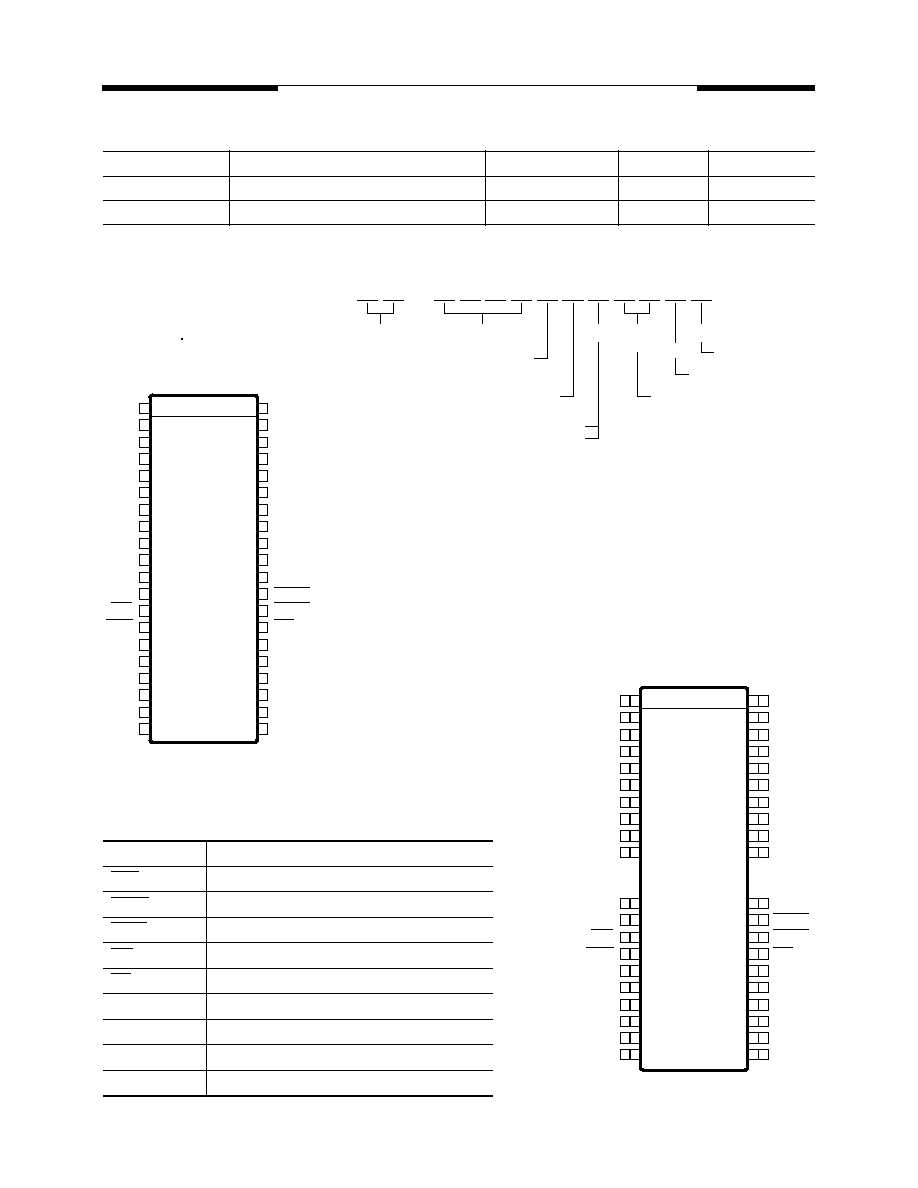

40-Pin SOJ

PIN CONFIGURATION

Top View

5

6

7

8

9

10

11

12

Vcc

I/O1

I/O2

I/O3

I/O4

Vcc

I/O5

I/O6

I/O7

I/O8

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

16258H-02

39

38

37

36

35

34

33

32

31

30

29

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

Vss

I/O16

I/O15

I/O14

I/O13

Vss

I/O12

I/O11

I/O10

I/O9

NC

LCAS

UCAS

OE

A8

A7

A6

A5

A4

Vss

Part Name

Self Refresh

Supply Voltage

Package

Speed

V53C16258SHK50

Standard Self Refresh (8ms)

5V

SOJ

50

V53C16258SHT50

Standard Self Refresh (8ms)

5V

TSOP

50

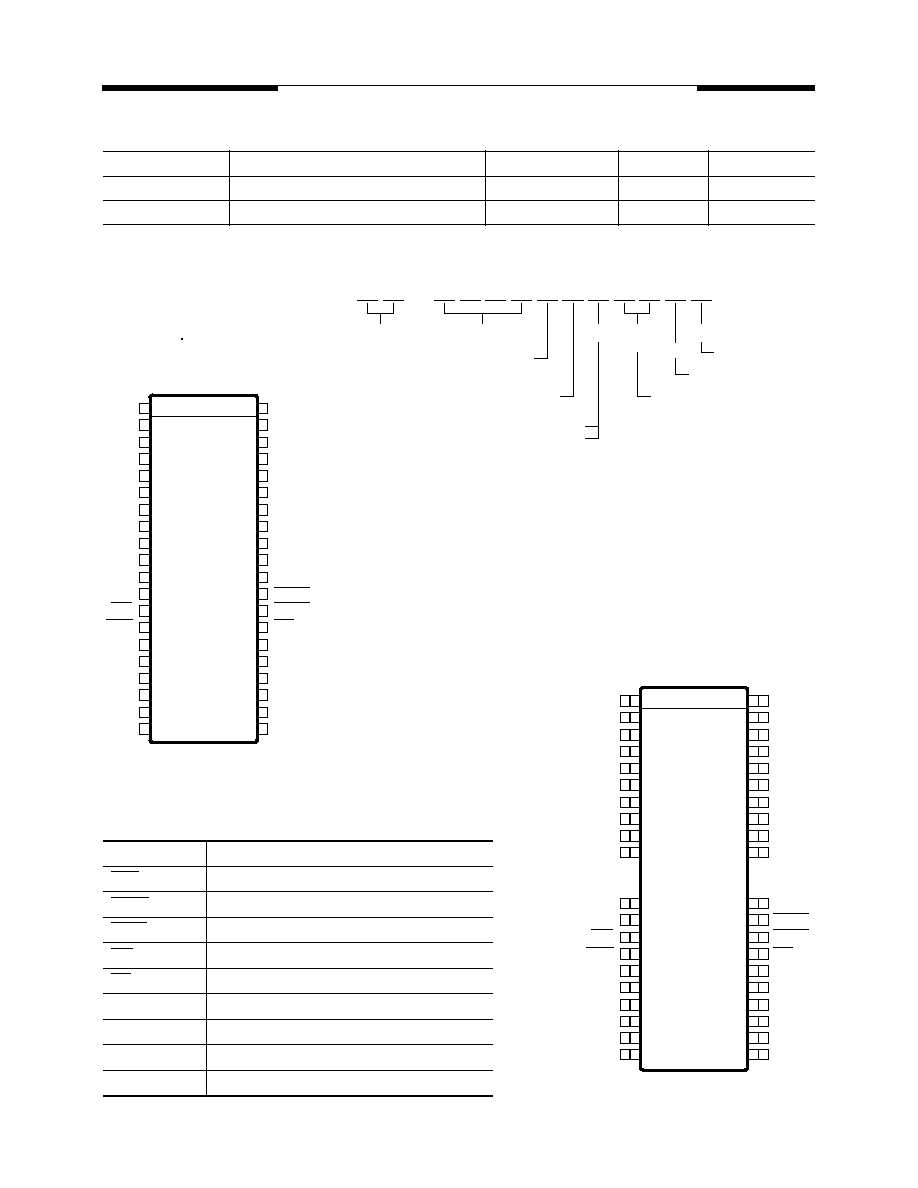

40/44 Pin Plastic TSOP-II

PIN CONFIGURATION

Top View

5

6

7

8

9

10

Vcc

I/O1

I/O2

I/O3

I/O4

Vcc

I/O5

I/O6

I/O7

I/O8

NC

NC

WE

RAS

NC

A0

A1

A2

A3

Vcc

1

2

3

4

16258H-03

43

44

42

41

40

39

38

37

36

35

13

14

15

16

17

18

19

20

21

22

32

31

30

29

28

27

26

25

24

23

Vss

I/O16

I/O15

I/O14

I/O13

Vss

I/O12

I/O11

I/O10

I/O9

NC

LCAS

UCAS

OE

A8

A7

A6

A5

A4

Vss

3

MOSEL VITELIC

V53C16258SH

V53C16258SH Rev 0.2 Aug. 1998

Absolute Maximum Ratings*

Ambient Temperature

Under Bias ..................................... �10

�

C to +80

�

C

Storage Temperature (plastic) ..... �55

�

C to +125

�

C

Voltage Relative to V

SS

.................�1.0 V to +7.0 V

Data Output Current ..................................... 50 mA

Power Dissipation .......................................... 1.0 W

*Note:

Operation above Absolute Maximum Ratings can

adversely affect device reliability.

Capacitance*

T

A

= 25

�

C, V

CC

= 5 V

�

10%, V

SS

= 0 V

* Note:

Capacitance is sampled and not 100% tested

Symbol

Parameter Typ.

Max.

Unit

C

IN1

Address Input

3

4

pF

C

IN2

RAS, CAS, WE, OE

4

5

pF

C

OUT

Data Input/Output

5

7

pF

Block Diagram

A0

A1

A7

A8

SENSE AMPLIFIERS

REFRESH

COUNTER

VCC

VSS

9

I/O 1

ADDRESS BUFFERS

AND PREDECODERS

X0 -X

ROW

DECODERS

512

MEMORY

ARRAY

256K x 16

COLUMN DECODERS

DATA I/O BUS

Y0 -Y8

512 x 16

I/O

BUFFER

I/O2

I/O3

I/O4

OE CLOCK

GENERATOR

WE CLOCK

GENERATOR

CAS CLOCK

GENERATOR

RAS CLOCK

GENERATOR

OE

WE

LCAS

RAS

�

�

�

8

I/O 5

I/O6

I/O7

I/O8

I/O 9

I/O10

I/O11

I/O12

I/O 13

I/O14

I/O15

I/O16

UCAS

256K x 16

16258H-04

4

V53C16258SH Rev 0.2 Aug. 1998

MOSEL VITELIC

V53C16258SH

DC and Operating Characteristics

(1-2)

T

A

= 0

�

C to 70

�

C, V

CC

= 5 V

�

10%, V

SS

= 0 V, unless otherwise specified.

Symbol

Parameter

V53C16258SH

Unit

Test Conditions

Notes

Min.

Typ.

Max.

I

LI

Input Leakage Current

(any input pin)

�10

10

m

A

V

SS

�

V

IN

�

V

CC

I

LO

Output Leakage Current

(for High-Z State)

�10

10

m

A

V

SS

�

V

OUT

�

V

CC

RAS, CAS at V

IH

I

CC1

V

CC

Supply Current,

Operating

160

mA

t

RC

= t

RC

(min.)

1, 2

I

CC2

V

CC

Supply Current,

TTL Standby

2

mA

RAS, CAS at V

IH

other inputs

�

V

SS

I

CC3

V

CC

Supply Current,

RAS-Only Refresh

160

mA

t

RC

= t

RC

(min.)

2

I

CC4

V

CC

Supply Current,

EDO Page Mode Operation

150

mA

Minimum Cycle

1, 2

I

CC5

V

CC

Supply Current,

Standby, Output Enabled

other inputs

�

V

SS

2

mA

RAS = V

IH

, CAS = V

IL

1

I

CC6

V

CC

Supply Current,

CMOS Standby

1

mA

RAS

�

V

CC

� 0.2 V,

CAS

�

V

CC

� 0.2 V,

All other inputs

�

V

SS

I

CC7

Self Refresh Current

400

m

A

CBR Cycle with t

RAS

�

t

RASS

(Min.) and

CAS = V

IL

V

CC

Supply Voltage

4.5

5.0

5.5

V

V

IL

Input Low Voltage

�1

0.8

V

3

V

IH

Input High Voltage

2.4

V

CC

+ 1

V

3

V

OL

Output Low Voltage

0.4

V

I

OL

= 2 mA

V

OH

Output High Voltage

2.4

V

I

OH

= �2 mA

5

MOSEL VITELIC

V53C16258SH

V53C16258SH Rev 0.2 Aug. 1998

AC Characteristics

T

A

= 0

�

C to 70

�

C, V

CC

= 5 V

�

10%, V

SS

= 0V unless otherwise noted

AC Test conditions, input pulse levels 0 to 3V

#

Symbol

Parameter

50

Unit

Notes

Min.

Max.

1

t

RAS

RAS Pulse Width

50

75K

ns

2

t

RC

Read or Write Cycle Time

90

ns

3

t

RP

RAS Precharge Time

30

ns

4

t

CSH

CAS Hold Time

50

ns

5

t

CAS

CAS Pulse Width

9

ns

6

t

RCD

RAS to CAS Delay

19

36

ns

7

t

RCS

Read Command Setup Time

0

ns

4

8

t

ASR

Row Address Setup Time

0

ns

9

t

RAH

Row Address Hold Time

9

ns

10

t

ASC

Column Address Setup Time

0

ns

11

t

CAH

Column Address Hold Time

7

ns

12

t

RSH (R)

RAS Hold Time (Read Cycle)

10

ns

13

t

CRP

CAS to RAS Precharge Time

5

ns

14

t

RCH

Read Command Hold Time

Referenced to CAS

0

ns

5

15

t

RRH

Read Command Hold Time

Referenced to RAS

0

ns

5

16

t

ROH

RAS Hold Time Referenced

to OE

10

ns

17

t

OAC

Access Time from OE

14

ns

12

18

t

CAC

Access Time from CAS

14

ns

6, 7, 14

19

t

RAC

Access Time from RAS

50

ns

6, 8, 9

20

t

CAA

Access Time from Column

Address

24

ns

6, 7, 10

21

t

LZ

OE or CAS to Low-Z Output

0

ns

16

22

t

HZ

OE or CAS to High-Z Output

0

8

ns

16

23

t

AR

Column Address Hold Time from RAS

40

ns

24

t

RAD

RAS to Column Address

Delay Time

14

26

ns

11

25

t

RSH (W)

RAS or CAS Hold Time in

Write Cycle

10

ns

26

t

CWL

Write Command to CAS

Lead Time

14

ns

27

t

WCS

Write Command Setup Time

0

ns

12, 13

28

t

WCH

Write Command Hold Time

7

ns

29

t

WP

Write Pulse Width

7

ns