MOSEL VITELIC

1

V826516G04S

128 MB 200-PIN DDR UNBUFFERED SODIMM

2.5 VOLT 16M x 64

PRELIMINARY

V826516G04S Rev. 1.5 March 2002

Features

JEDEC 200 Pin DDR Unbuffered Small-Outline,

Dual In-Line memory module (SODIMM);

16,777,216 x 64 bit organization.

Utilizes High Performance 16M x 8 DDR

SDRAM in TSOPII-66 Packages

Single +2.5V (± 0.2V) Power Supply

Programmable CAS Latency, Burst Length, and

Wrap Sequence (Sequential & Interleave)

Auto Refresh (CBR) and Self Refresh

All Inputs, Outputs are SSTL-2 Compatible

4096 Refresh Cycles every 64 ms

Serial Presence Detect (SPD)

DDR SDRAM Performance

Description

The V826516G04S memory module is organized

16,777,216 x 64 bits in a 200 pin memory module.

The 16M x 64 memory module uses 8 Mosel-Vitelic

16M x 8 DDR SDRAM. The x64 modules are ideal

for use in high performance computer systems

where increased memory density and fast access

times are required.

Component Used

-7

-75

-8

Units

t

CK

Clock Frequency

(max.)

143

(PC266A)

133

(PC266B)

125

(PC200)

MHz

t

AC

Clock Access Time

CAS Latency = 2.5

7

7.5

8

ns

Module Speed

A1

PC1600 (100MHz @ CL2)

B0

PC2100B (133MHz @ CL2.5)

B1

PC2100A (133MHz @ CL2)

2

MOSEL VITELIC

V826516G04S

V826516G04S Rev. 1.5 March 2002

Part Number Information

V 8 2 65 16 G 0 4 S X T G - XX

DDRSDRAM

2.5V

WIDTH

DEPTH

200 PIN Unbuffered

SODIMM X8 COMPONENT

REFRESH

RATE 4K

4 BANKS

STTL

COMPONENT

REV LEVEL

COMPONENT

PACKAGE, T = TSOP

LEAD FINISH

G = GOLD

SPEED

A1 (100MHZ@CL2)

MOSEL VITELIC

MANUFACTURED

B0 (133MHZ@CL2.5)

B1 (133MHZ@CL2)

MOSEL VITELIC

V826516G04S

3

V826516G04S Rev. 1.5 March 2002

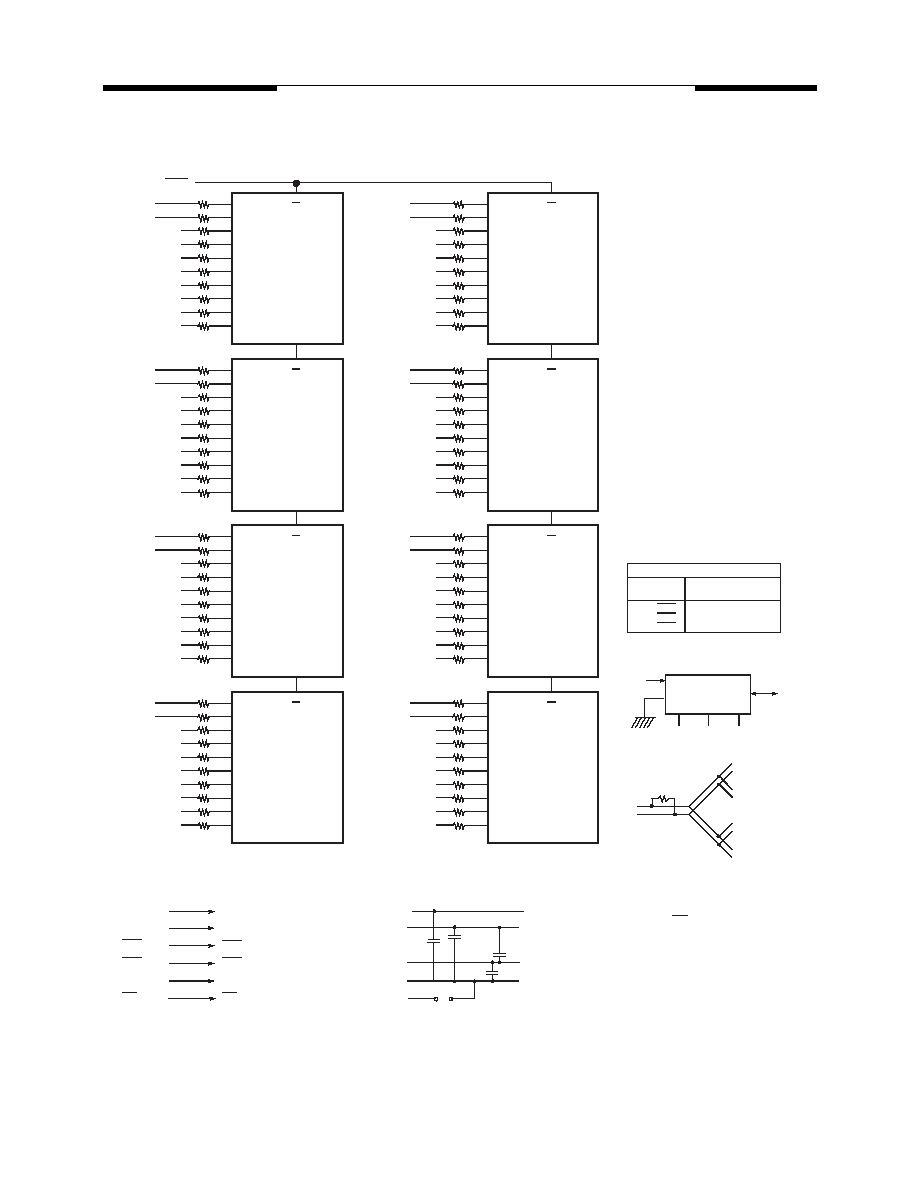

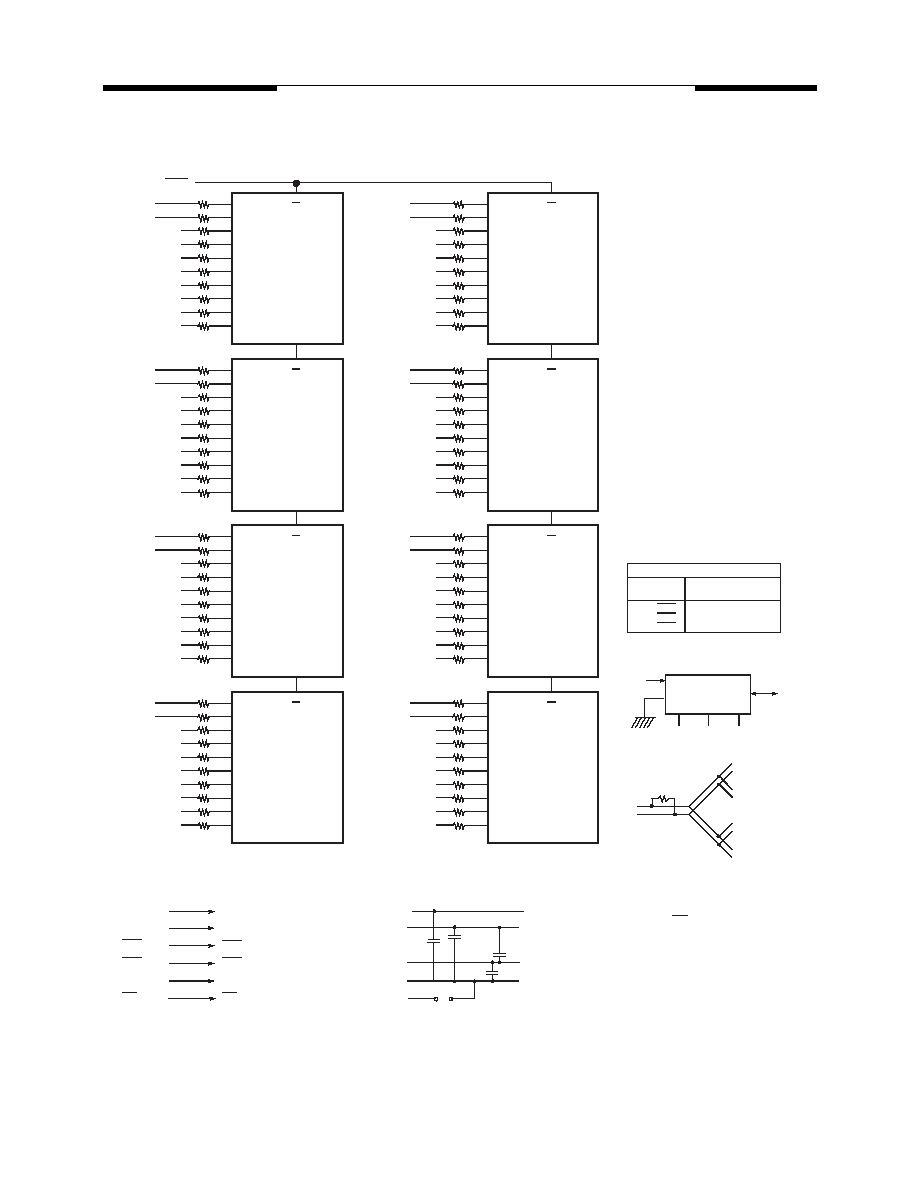

Block Diagram

CS0

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

S

A0 - A13

A0-A13: DDR SDRAMs D0 - D7

BA0 - BA1

BA0-BA1: DDR SDRAMs D0 - D7

RAS

RAS: SDRAMs D0 - D7

CAS

CAS: SDRAMs D0 - D7

CKE0

CKE: SDRAMs D0 - D7

WE

WE: SDRAMs D0 - D7

Notes:

1. DQ-to-I/O wiring is shown as recom-

mended but may be changed.

2. DQ/DQS/DM/CKE/CS relationships must

be maintained as shown.

3. DQ, DQS, DM/DQS resistors: 22 Ohms.

4. VDDID strap connections

(for memory device VDD, VDDQ):

STRAP OUT (OPEN): VDD = VDDQ

STRAP IN (VSS): VDD

VDDQ.

A0

Serial PD

A1

A2

SA0

SA1

SA2

SCL

SDA

WP

V

SS

D0 - D7

D0 - D7

V

DD

/V

DDQ

D0 - D7

D0 - D7

VREF

V

DDID

Strap: see Note 4

V

DDSPD

SPD

Clock Wiring

Clock

Input

SDRAMs

CK0/CK0

CK1/CK1

CK2/CK2

4 SDRAMs

4 SDRAMs

NC

DM

DQS0

DM0

*Clock Net Wiring

Card

Edge

Dram1

Dram2

R=120

±

5%

Dram3

Dram4

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D4

DQS

S

DM

DQS4

DM4

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQS

S

DM

DQS1

DM1

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D5

DQS

S

DM

DQS5

DM5

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQS

S

DM

DQS2

DM2

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D6

DQS

S

DM

DQS6

DM6

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQS

S

DM

DQS3

DM3

I/0 0

I/0 1

I/0 2

I/0 3

I/0 4

I/0 5

I/0 6

I/0 7

D7

DQS

S

DM

DQS7

DM7

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

4

MOSEL VITELIC

V826516G04S

V826516G04S Rev. 1.5 March 2002

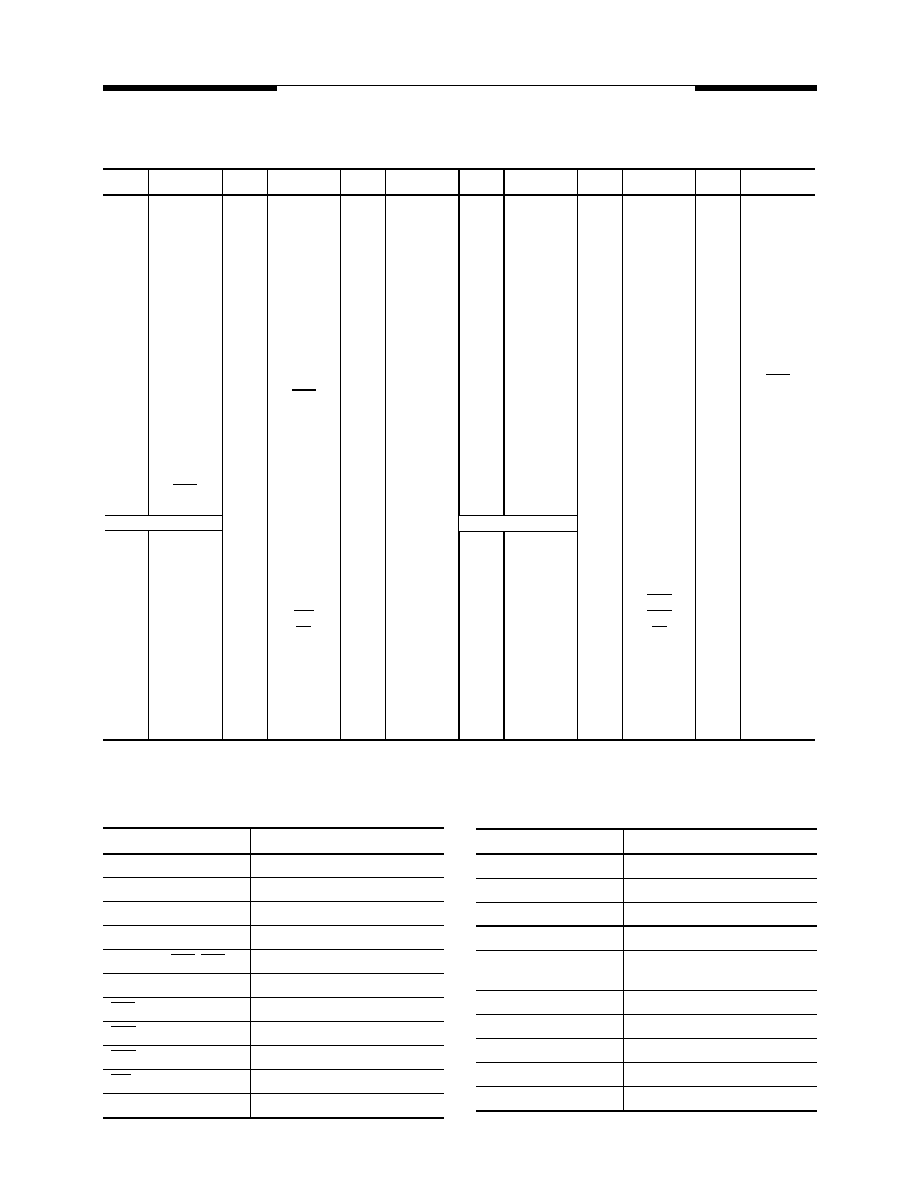

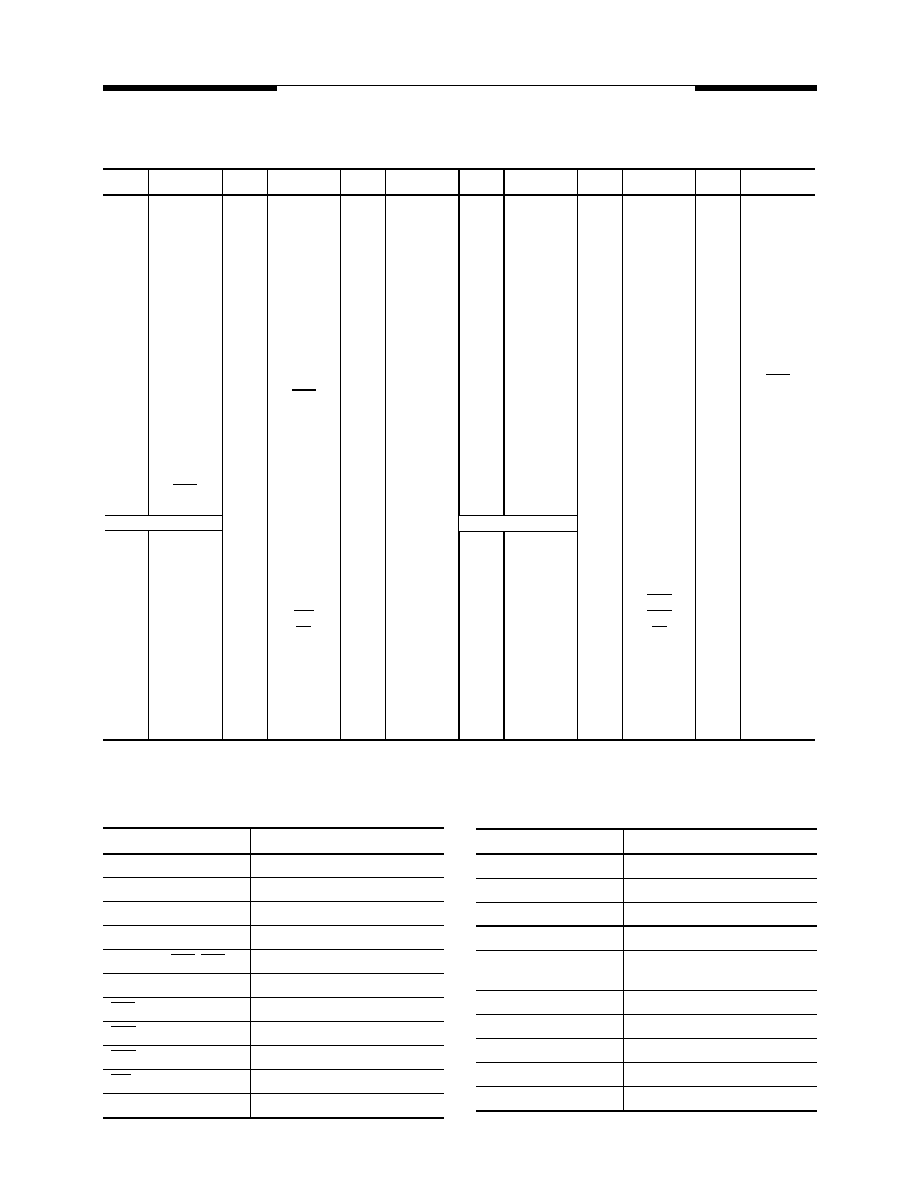

Pin Configurations (Front Side/Back Side)

Notes:

* These pins are not used in this module.

Pin

Front

Pin

Front

Pin

Front

Pin

Back

Pin

Back

Pin

Back

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

VREF

VSS

DQ0

DQ1

VDD

DQS0

DQ2

VSS

DQ3

DQ8

VDD

DQ9

DQS1

VSS

DQ10

DQ11

VDD

CK0

CK0

VSS

DQ16

DQ17

VDD

DQS2

DQ18

VSS

DQ19

DQ24

VDD

DQ25

DQS3

VSS

DQ26

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

DQ27

VDD

CB0

CB1

VSS

DQS8

CB2

VDD

CB3

DU

VSS

CK2

CK2

VDD

CKE1

DU(A13)

A12

A9

VSS

A7

A5

A3

A1

VDD

A10/AP

BA0

WE

S0

DU

VSS

DQ32

DQ33

VDD

DQS4

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

DQ34

VSS

DQ35

DQ40

VDD

DQ41

DQS5

VSS

DQ42

DQ43

VDD

VDD

VSS

VSS

DQ48

DQ49

VDD

DQS6

DQ50

VSS

DQ51

DQ56

VDD

DQ57

DQS7

DQ58

DQ58

DQ59

VDD

SDA

SCL

VDDSPD

VDDID

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

VREF

VSS

DQ4

DQ5

VDD

DM0

DQ6

VSS

DQ7

DQ12

VDD

DQ13

DM1

VSS

DQ14

DQ15

VDD

VDD

VSS

VSS

DQ20

DQ21

VDD

DM2

DQ22

VSS

DQ23

DQ28

VDD

DQ29

DM3

VSS

DQ30

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

DQ31

VDD

CB4

CB5

VSS

DM8

CB6

VDD

CB7

DU/(RESET)

VSS

VSS

VDD

VDD

CKE0

DU(BA2)

A11

A8

VSS

A6

A4

A2

A0

VDD

BA1

RAS

CAS

S1

DU

VSS

DQ36

DQ37

VDD

DM4

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DQ38

VSS

DQ39

DQ44

VDD

DQ45

DM5

VSS

DQ46

DQ47

VDD

CK1

CK1

VSS

DQ52

DQ53

VDD

DM6

DQ54

VSS

DQ55

DQ60

VDD

DQ61

DM7

VSS

DQ62

DQ63

VDD

SA0

SA1

SA2

DU

Pin Names

Pin Pin

Description

A0~A11

Address Input (Multiplexed)

BA0~BA1

Bank Select Address

DQ0~DQ63

Data Input/Output

DQS0~DQS7

Data Strobe Input/Output

CK0~CK2, CK0~CK2,

Clock Input

CKE0

Clock Enable Input

CS0

Chip Select Input

RAS

Row Address Strobe

CAS

Column Address Strobe

WE

Write Enable

DM0~DM7

Data - In Mask

VDD

Power Supply (2.5V)

VDDQ

Power Supply for DQS(2.5V)

VSS

Ground

VREF

Power Supply for Reference

VDDSPD

Serial EEPOM Power Supply (2.3V

to 3.6V)

SDA

Serial Data I/O

SCL

Serial Clock

SA0~2

Address in EEPROM

VDDID

VDD Identification Flag

NC

No Connection

Pin Pin

Description

Key

Key

MOSEL VITELIC

V826516G04S

5

V826516G04S Rev. 1.5 March 2002

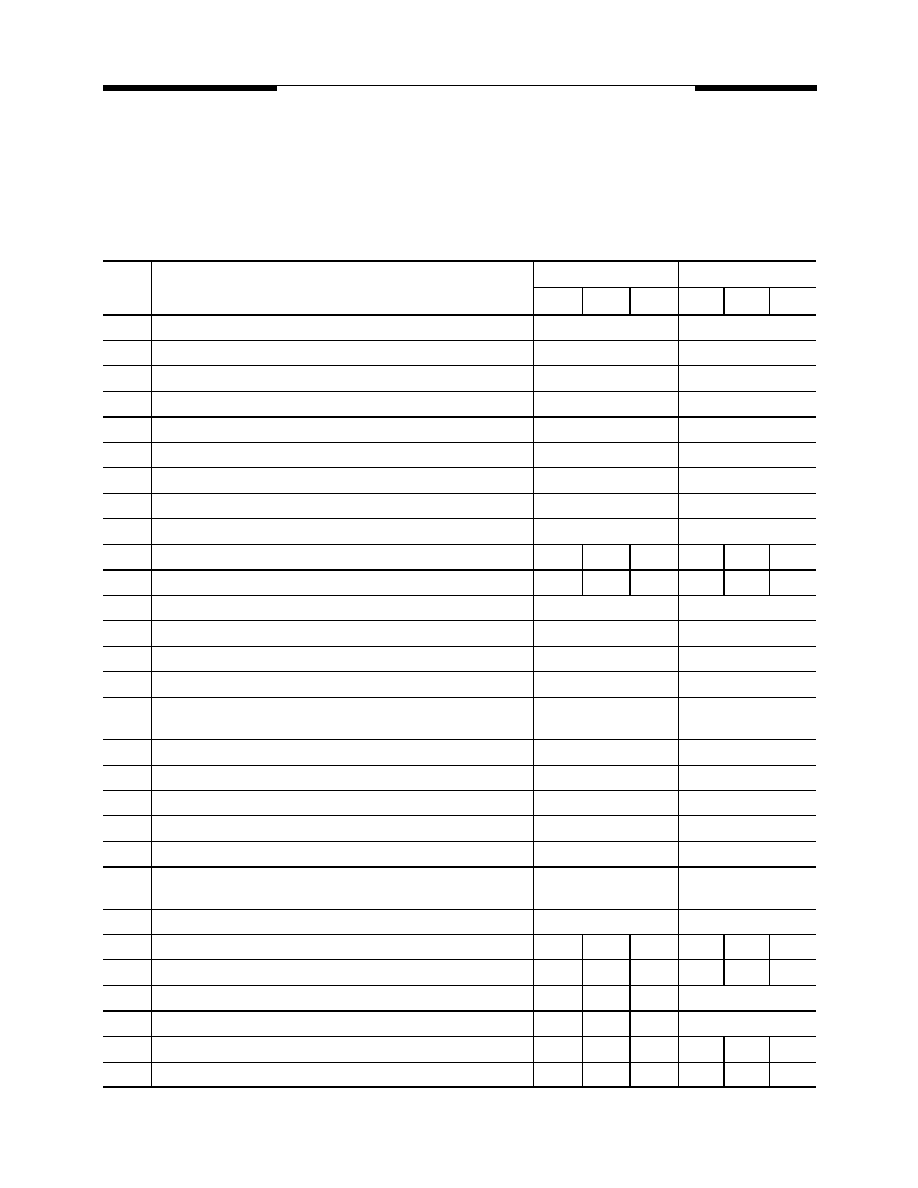

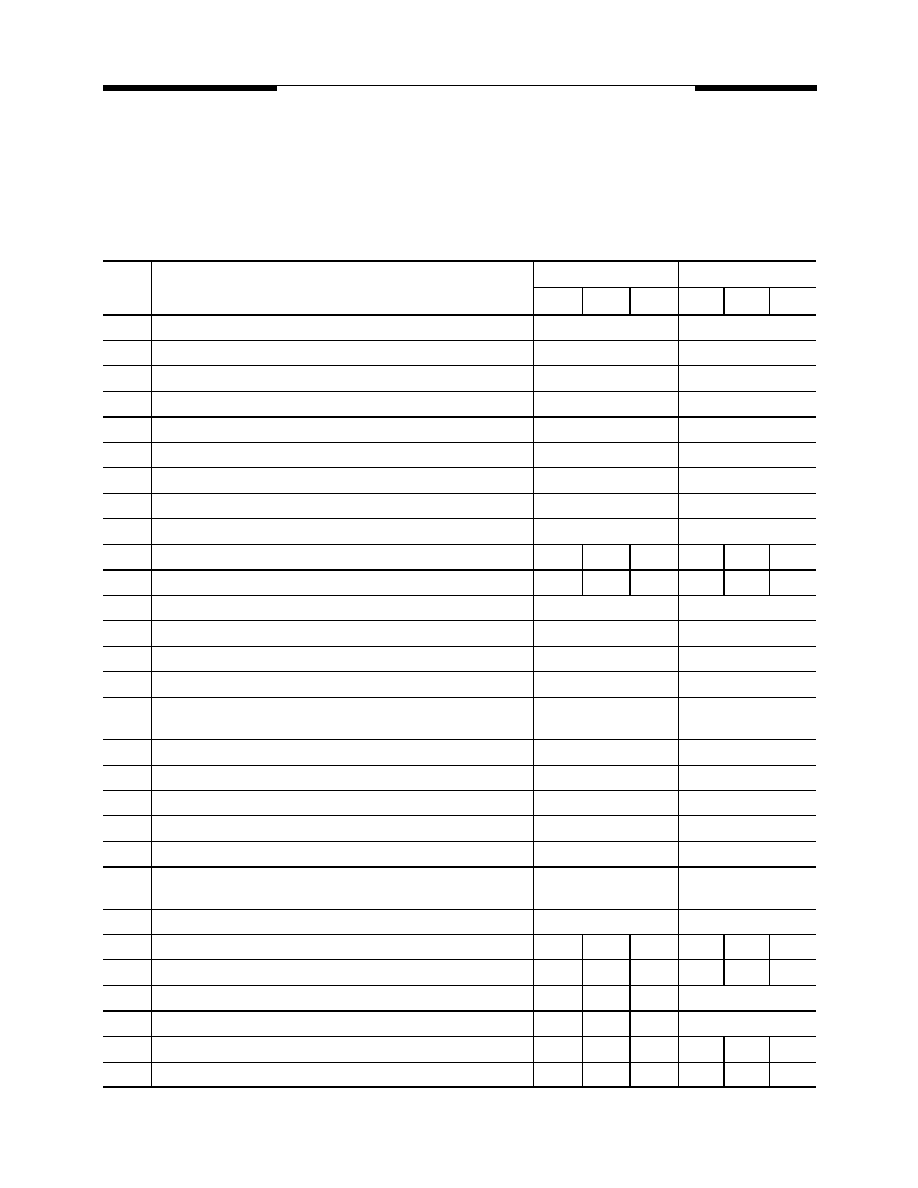

Serial Presence Detect Information

Bin Sort:

A1 (PC1600 @ CL2)

B0 (PC2100B @ CL2.5)

B1 (PC2100A @ CL2)

Byte #

Function described

Function Supported

Hex value

A1 B0

B1

A1 B0

B1

0

Defines # of Bytes written into serial memory at module manufacturer

128bytes

80h

1

Total # of Bytes of SPD memory device

256bytes

08h

2

Fundamental memory type

SDRAM DDR

07h

3

# of row address on this assembly

12

0Ch

4

# of column address on this assembly

10

0Ah

5

# of module Rows on this assembly

1 Bank

01h

6

Data width of this assembly

64 bits

40h

7

.........Data width of this assembly

-

00h

8

VDDQ and interface standard of this assembly

SSTL 2.5V

04h

9

DDR SDRAM cycle time at CAS Latency =2.5

8ns

7.5ns

7ns

80h

75h

70h

10

DDR SDRAM Access time from clock at CL=2.5

±0.8ns ±0.75ns ±0.70ns

80h

75h

70h

11

DIMM configuration type(Non-parity, Parity, ECC)

Non-parity, ECC

00

12

Refresh rate & type

15.6us & Self refresh

80h

13

Primary DDR SDRAM width

x8

08h

14

Error checking DDR SDRAM data width

x0

00h

15

Minimum clock delay for back-to-back random column

address

t

CCD

=1CLK 01h

16

DDR SDRAM device attributes : Burst lengths supported

2,4,8

0Eh

17

DDR SDRAM device attributes : # of banks on each DDR SDRAM

4 banks

04h

18

DDR SDRAM device attributes : CAS Latency supported

2,2.5

0Ch

19

DDR SDRAM device attributes : CS Latency

0CLK

01h

20

DDR SDRAM device attributes : WE Latency

1CLK

02h

21

DDR SDRAM module attributes

Unbuffered

Diff Clock

20h

22

DDR SDRAM device attributes : General

+/-0.2V voltage tolerance

00h

23

DDR SDRAM cycle time at CL =2

10ns

10ns

7.5ns

A0h

A0h

75h

24

DDR SDRAM Access time from clock at CL =2

±0.8ns ±0.80ns ±0.75ns

80h

80h

75h

25

DDR SDRAM cycle time at CL =1.5

-

-

-

00h

26

DDR SDRAM Access time from clock at CL =1.5

-

-

-

00h

27

Minimum row precharge time (=t

RP

)

20ns 20ns 18ns 50h 50h 48h

28

Minimum row activate to row active delay(=t

RRD

) 15ns

15ns

14ns

3Ch

3Ch

38h