DSP56853/D

Rev. # 2.0 3/2003

© Motorola, Inc., 2003. All rights reserved.

DSP56853

Preliminary Technical Data

DSP56853 16-bit Digital Signal Processor

∑ 120 MIPS at 120MHz

∑ 12K x 16-bit Program SRAM

∑ 4K x 16-bit Data SRAM

∑ 1K x 16-bit Boot ROM

∑ Access up to 2M words of program memory or 8M

of data memory

∑ Chip Select Logic for glue-less interface to ROM

and SRAM

∑ Six (6) independent channels of DMA

∑ Enhanced Synchronous Serial Interfaces (ESSI)

∑ Two (2) Serial Communication Interfaces (SCI)

∑ Serial Port Interface (SPI)

∑ 8-bit Parallel Host Interface

∑ General Purpose 16-bit Quad Timer

∑ JTAG/Enhanced On-Chip Emulation (OnCETM) for

unobtrusive, real-time debugging

∑ Computer Operating Properly (COP)/Watchdog

Timer

∑ Time-of-Day (TOD)

∑ 128 LQFP package

∑ Up to 41 GPIO

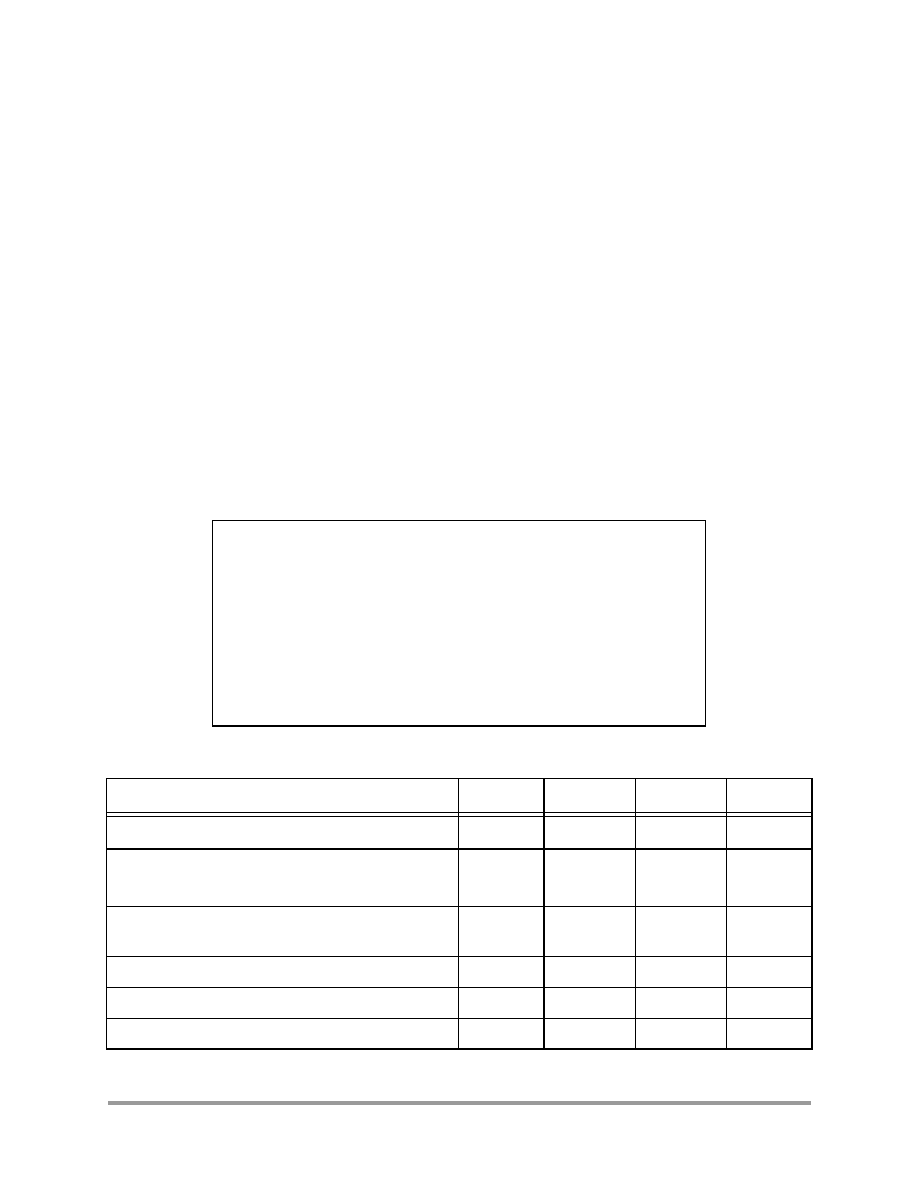

Figure 1. DSP56853 Block Diagram

JTAG/

Enhanced

OnCE

Program Controller

and

Hardware Looping Unit

Data ALU

16 x 16 + 36

36-Bit MAC

Three 16-bit Input Registers

Four 36-bit Accumulators

Address

Generation Unit

Bit

Manipulation

Unit

16-Bit

DSP56800E Core

XTAL

EXTAL

Interrupt

Controller

Quad

Timer

or

GPIOG

4

CLKO

External Address

Bus Switch

External Bus

Interface Unit

4

RESET

IRQA

IRQB

V

DD

V

SSIO

V

DDA

V

SSA

External Data

Bus Switch

Bus Control

WR Enable

RD Enable

CS0-CS3[3:0] or

A0-20 [20:0]

MODEA-C or

D0-D15 [15:0]

6

Program Memory

12,288 x 16 SRAM

Boot ROM

1024 x 16 ROM

Data Memory

4,096 x 16 SRAM

PDB

PDB

XAB1

XAB2

XDB2

CDBR

SPI

or

GPIOF

2 SCI

or

GPIOE

IPBus Bridge (IPBB)

3

(GPIOH0-H2)

6

10

V

DDIO

11

Decoding

Peripherals

4

System

Bus

Control

Memory

PAB

PAB

CDBW

CDBR

CDBW

V

SS

6

GPIOA0-A3[3:0]

6

ESSI0

or

GPIOC

Host

Interface

or

GPIOB

16

RSTO

DMA

6 channel

POR

Integration

Module

System

COP/

Watch-

dog

Time

of

Day

Clock

Generator

OSC PLL

IPBus CLK

COP/TOD CLK

Co

r

e

CLK

IP

AB

IPW

D

B

IP

RDB

DM

A

Reques

t

s

2

DSP56853 Preliminary Technical Data

MOTOROLA

Part 1 Overview

1.1 DSP56853 Features

1.1.1

Digital Signal Processing Core

∑

Efficient 16-bit DSP engine with dual Harvard architecture

∑

120 Million Instructions Per Second (MIPS) at 120MHz core frequency

∑

Single-cycle 16

◊ 16-bit parallel Multiplier-Accumulator (MAC)

∑

Four (4) 36-bit accumulators including extension bits

∑

16-bit bidirectional shifter

∑

Parallel instruction set with unique DSP addressing modes

∑

Hardware DO and REP loops

∑

Three (3) internal address buses and one (1) external address bus

∑

Four (4) internal data buses and one (1) external data bus

∑

Instruction set supports both DSP and controller functions

∑

Four (4) hardware interrupt levels

∑

Five (5) software interrupt levels

∑

Controller-style addressing modes and instructions for compact code

∑

Efficient C Compiler and local variable support

∑

Software subroutine and interrupt stack with depth limited only by memory

∑

JTAG/Enhanced OnCE debug programming interface

1.1.2

Memory

∑

Harvard architecture permits up to three (3) simultaneous accesses to program and data memory

∑

On-Chip Memory

-- 12K

◊ 16-bit Program SRAM

-- 4K

◊ 16-bit Data SRAM

-- 1K

◊ 16-bit Boot ROM

∑

Off-Chip Memory Expansion (EMI)

-- Access up to 2M words of program memory or 8M data memory

-- Chip Select Logic for glue-less interface to ROM and SRAM

1.1.3

Peripheral Circuits for DSP56853

∑

General Purpose 16-bit Quad Timer*

∑

Two (2) Serial Communication Interfaces (SCI)*

∑

Serial Peripheral Interface (SPI) Port*

∑

Enhanced Synchronous Serial Interface (ESSI) modules*

∑

Computer Operating Properly (COP)

DSP56853 Description

MOTOROLA

DSP56853 Preliminary Technical Data

3

∑

Watchdog Timer

∑

JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, real-time debugging

∑

Six (6) independent channels of DMA

∑

8-bit Parallel Host Interface*

∑

Time-of-Day (TOD)

∑

128 LQFP package

∑

Up to 41 GPIO

* Each peripheral I/O can be used alternately as a General Purpose I/O if not needed

1.1.4

Energy Information

∑

Fabricated in high-density CMOS with 3.3V, TTL-compatible digital inputs

∑

Wait and Stop modes available

1.2 DSP56853 Description

The DSP56853 is a member of the DSP56800E core-based family of Digital Signal Processors (DSPs). It

combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with

a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost,

configuration flexibility, and compact program code, the DSP56853 is well-suited for many applications.

The DSP56853 includes many peripherals that are especially useful for low-end Internet appliance

applications and low-end client applications such as telephony; portable devices;; Internet audio and point-

of-sale systems, such as noise suppression; ID tag readers; sonic/subsonic detectors; security access

devices; remote metering; sonic alarms.

The Product Family core is based on a Harvard-style architecture consisting of three execution units

operating in parallel, allowing as many as six operations per instruction cycle. The microprocessor-style

programming model and optimized instruction set allow straightforward generation of efficient, compact

code for both DSP and MCU applications. The instruction set is also highly efficient for C Compilers,

enabling rapid development of optimized control applications.

The DSP56853 supports program execution from either internal or external memories. Two data operands

can be accessed from the on-chip Data RAM per instruction cycle. The DSP56853 also provides two

external dedicated interrupt lines, and up to 41 General Purpose Input/Output (GPIO) lines, depending on

peripheral configuration.

The DSP56853 DSP controller includes 12K words of Program RAM, 4K words of Data RAM, and 1K

words of Boot ROM. It also supports program execution from external memory. The DSP56800 core can

access two data operands from the on-chip Data RAM per instruction cycle.

This DSP controller also provides a full set of standard programmable peripherals that include an 8-bit

parallel Host Interface, Enhanced Synchronous Serial Interface (ESSI), one Serial Peripheral Interface

(SPI), the option to select a second SPI or two Serial Communications Interfaces (SCIs), and Quad Timer.

The Host Interface, ESSI, SPI, SCI, four chip selects and quad timer can be used as General Purpose Input/

Outputs (GPIOs) if its primary function is not required.

4

DSP56853 Preliminary Technical Data

MOTOROLA

1.3 "Best in Class" Development Environment

The SDK (Software Development Kit) provides fully-debugged peripheral drivers, libraries and interfaces

that allow a programmer to create his own unique C application code independent of component

architecture. The CodeWarrior Integrated Development Environment is a sophisticated tool for code

navigation, compiling, and debugging. A complete set of evaluation modules (EVMs) and development

system cards will support concurrent engineering. Together, the SDK, CodeWarrior, and EVMs create a

complete, scalable tools solution for easy, fast and efficient development.

1.4 Product Documentation

The four documents listed in

Table 1

are required for a complete description of and proper design with the

DSP56853. Documentation is available from local Motorola distributors, Motorola semiconductor sales

offices, Motorola Literature Distribution Centers, or online at www.motorola.com/semiconductors/.

Table 1. DSP56853 Chip Documentation

1.5 Data Sheet Conventions

This data sheet uses the following conventions:

Topic

Description

Order Number

DSP56800E

Reference Manual

Detailed description of theDSP56800E architecture,

16-bit DSP core processor and the instruction set

DSP56800ERM/D

DSP56853

User's Manual

Detailed description of memory, peripherals, and

interfaces of the DSP56853

DSP5685xUM/D

DSP56853

Technical Data Sheet

Electrical and timing specifications, pin descriptions,

and package descriptions

DSP56853/D

DSP56853

Product Brief

Summary description and block diagram of the

DSP56853 core, memory, peripherals and interfaces

(this document)

DSP56853PB/D

OVERBAR

This is used to indicate a signal that is active when pulled low. For example, the RESET pin is

active when low.

"asserted"

A high true (active high) signal is high or a low true (active low) signal is low.

"deasserted"

A high true (active high) signal is low or a low true (active low) signal is high.

Examples:

Signal/Symbol

Logic State

Signal State

Voltage

1

1.

Values for VIL, VOL, VIH, and VOH are defined by individual product specifications.

PIN

True

Asserted

V

IL

/V

OL

PIN

False

Deasserted

V

IH

/V

OH

PIN

True

Asserted

V

IH

/V

OH

PIN

False

Deasserted

V

IL

/V

OL

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

5

Part 2 Signal/Connection Descriptions

2.1 Introduction

The input and output signals of the DSP56853 are organized into functional groups, as shown in

Table 2

and as illustrated in

Figure 2

. In

Table 3

each table row describes the package pin and the signal or signals

present.

1.

V

DD

=

V

DD CORE,

V

SS

=

V

SS CORE,

V

DDIO

=

V

DD IO,

V

SSIO

=

V

SS IO,

V

DDA

=

V

DD ANA,

V

SSA

=

V

SS ANA

2. MODA, MODB and MODC can be used as GPIO after the bootstrap process has completed.

3. The following Host Interface signals are multiplexed: HRWB to HRD, HDS to HWR, HREQ to HTRQ

and HACK to HRRQ.

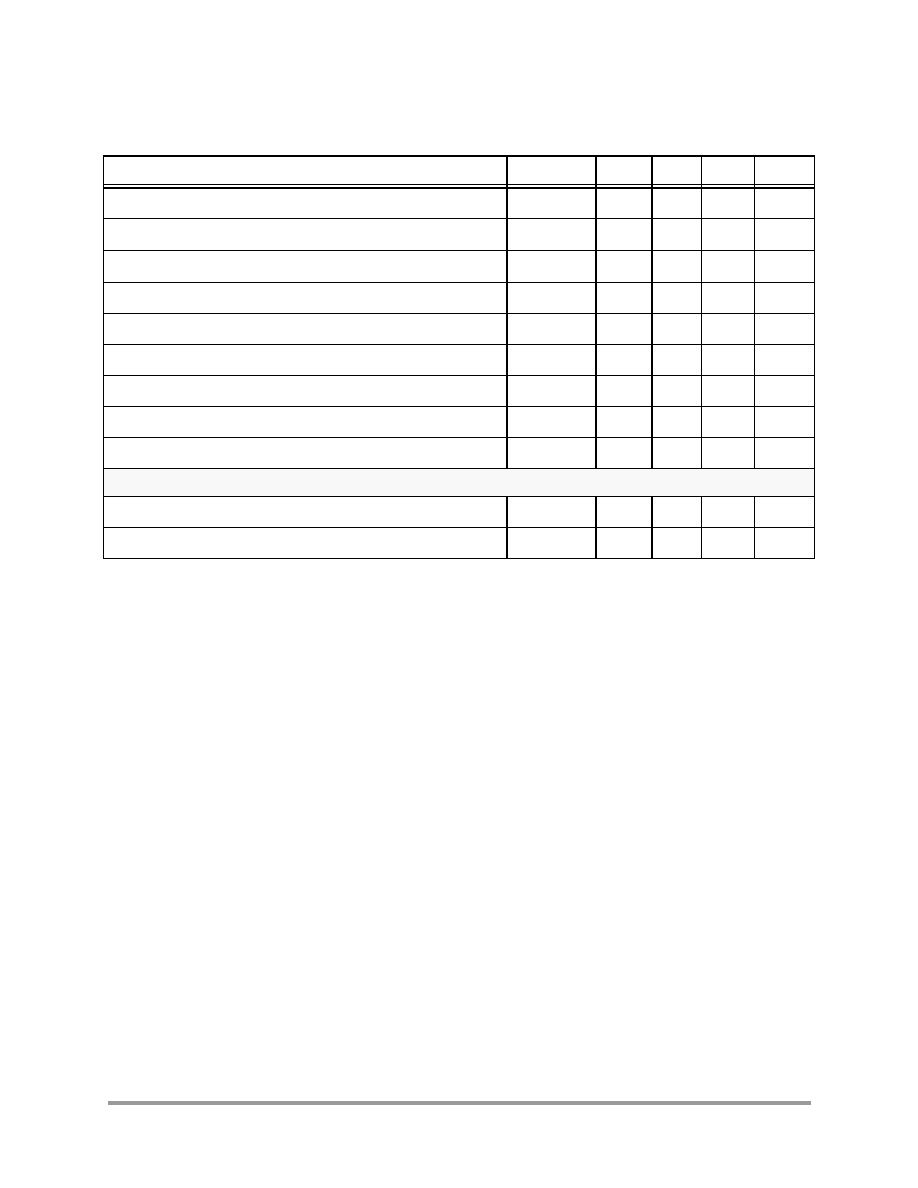

Table 2. DSP56853 Functional Group Pin Allocations

Functional Group

Number of Pins

Power (V

DD,

V

DDIO, or

V

DDA

)

(6, 11, 1)

1

Ground (V

SS,

V

SSIO,

or V

SSA

)

(6, 10, 1)

1

PLL and Clock

3

External Bus Signals

39

External Chip Select*

4

Interrupt and Program Control

7

2

Host Interface (HI)*

16

3

Enhanced Synchronous Serial Interface (ESSI0) Port*

6

Serial Communications Interface (SCI0) Ports*

2

Serial Communications Interface (SCI1) Ports*

2

Serial Peripheral Interface (SPI) Port*

4

Quad Timer Module Port*

4

JTAG/Enhanced On-Chip Emulation (EOnCE)

6

*Alternately, GPIO pins

6

DSP56853 Preliminary Technical Data

MOTOROLA

.

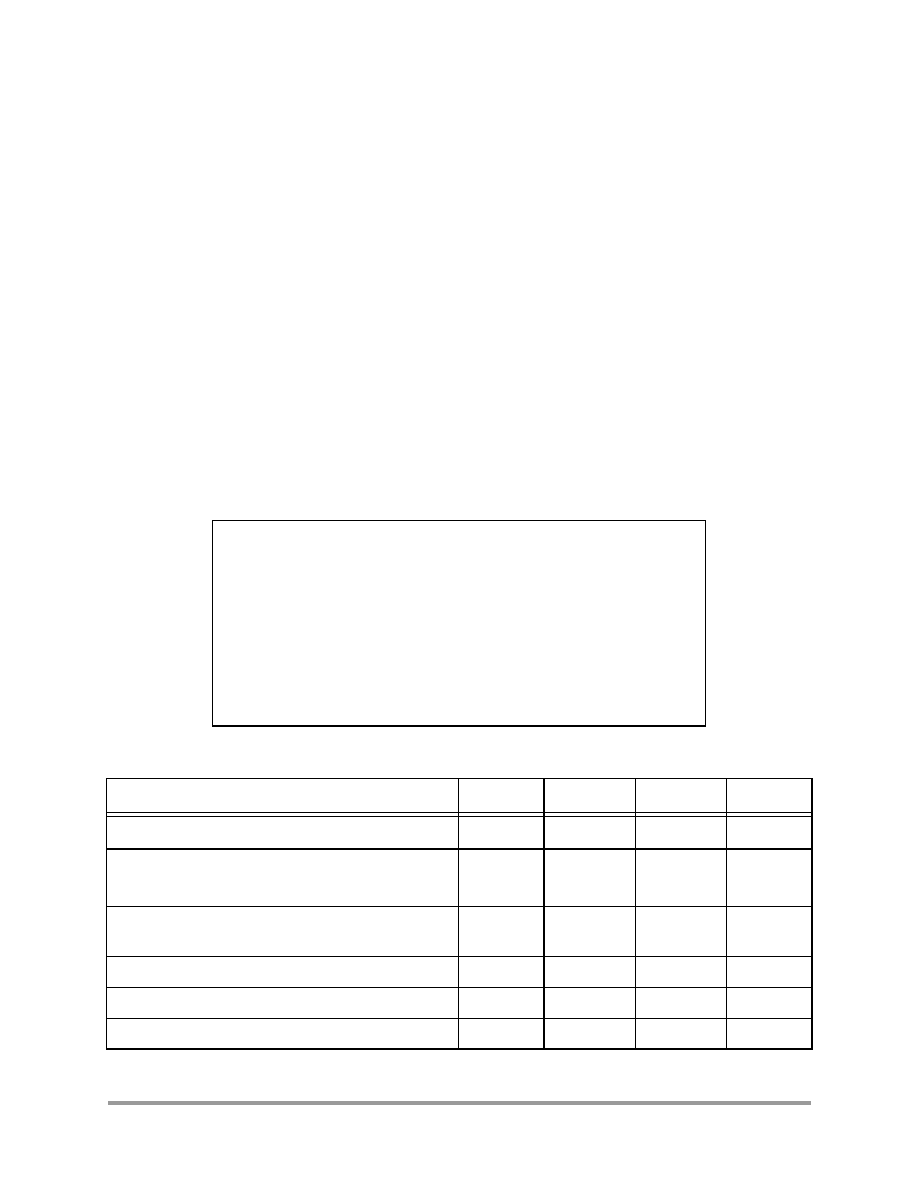

Figure 2. DSP56853 Signals Identified by Functional Group

2

1. Specifically for PLL, OSC, and POR.

2. Alternate pin functions are shown in parentheses.

DSP56853

Logic

Power

I/O

Power

SCI 0

JTAG /

Enhanced

OnCE

Timer

Module

ESSI 0

SPI

Chip

Select

External

Bus

Analog

Power

1

PLL/Clock

Host

Interface

SCI 2

Interrupt/

Program

Control

V

DD

V

SS

V

DDIO

V

SSIO

V

DDA

V

SSA

A0 - A20

RD

D0 - D15

WR

CS0 - CS3 (GPIOA0 - A3)

HD0 - HD7 (GPIOB0 - B7)

HA0 - HA2 (GPIOB8 - B10)

HRWB (HRD) (GPIOB11)

HDS (HWR) (GPIOB12)

HCS (GPIOB13)

HREQ (HTRQ) (GPIOB14)

HACK (HRRQ) (GPIOB15)

TIO0 - TIO3 (GPIOG0 - G3)

IRQA

IRQB

MODA, MODB, MODC

(GPIOH0 - H2)

RESET

RSTO

Host

Interface

XTAL

RXDO (GPIOE0)

TXDO (GPIOE1)

RXD1 (GPIOE2)

TXD1 (GPIOE3)

STD0 (GPIOC0)

SRD0 (GPIOC1)

SCK0 (GPIOC2)

SC00 (GPIOC3)

SC01 (GPIOC4)

SC02 (GPIOC5)

MISO (GPIOF0)

MOSI (GPIOF1)

SCK (GPIOF2)

SS (GPIOF3)

EXTAL

CLKO

TCK

TDI

TDO

TMS

TRST

DE

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

3

1

1

4

1

1

1

1

1

3

8

4

1

1

16

21

1

1

10

11

6

6

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

7

Part 3 Signals and Package Information

All digital inputs have a weak internal pull-up circuit associated with them. These pull-up circuits

are enabled by default. Exceptions:

1. When a pin has GPIO functionality, the pull-up may be disabled under software control.

2. MODE A, MODE B and MODE C pins have no pull-up.

3. TCK has a weak pull-down circuit always active.

4. Bidirectional I/O pullups automatically disable when the output is enabled.

This table is presented consistently with the Signals Identified by Functional Group figure.

1. BOLD entries in the Type column represents the state of the pin just out of reset.

2. Ouput(Z) means an output in a High-Z condition

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

13

V

DD

V

DD

Power (V

DD

)--These pins provide power to the internal

structures of the chip, and should all be attached to V

DD.

47

V

DD

64

V

DD

79

V

DD

80

V

DD

112

V

DD

14

V

SS

V

SS

Ground (V

SS

)--These pins provide grounding for the

internal structures of the chip and should all be attached to

V

SS.

48

V

SS

63

V

SS

81

V

SS

96

V

SS

113

V

SS

5

V

DDIO

V

DDIO

Power (V

DDIO

)--These pins provide power for all I/O and

ESD structures of the chip, and should all be attached to

V

DDIO

(3.3V)

.

18

V

DDIO

41

V

DDIO

55

V

DDIO

61

V

DDIO

72

V

DDIO

91

V

DDIO

92

V

DDIO

100

V

DDIO

114

V

DDIO

124

V

DDIO

8

DSP56853 Preliminary Technical Data

MOTOROLA

6

V

SSIO

V

SSIO

Ground (V

SSIO

)--These pins provide grounding for all I/O

and ESD structures of the chip and should all be attached to

V

SS.

19

V

SSIO

42

V

SSIO

56

V

SSIO

62

V

SSIO

74

V

SSIO

93

V

SSIO

102

V

SSIO

115

V

SSIO

125

V

SSIO

22

V

DDA

V

DDA

Analog Power (V

DDA

)--These pins supply an analog power

source.

23

V

SSA

V

SSA

Analog Ground (V

SSA

)--This pin supplies an analog

ground.

9

A0

Output(Z)

Address Bus (A0-A20)--These signals specify a word

address for external program or data memory access.

10

A1

11

A2

12

A3

26

A4

27

A5

28

A6

29

A7

43

A8

44

A9

45

A10

46

A11

57

A12

58

A13

59

A14

60

A15

67

A16

68

A17

69

A18

70

A19

71

A20

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

9

73

D0

Input/Output(Z)

Data Bus (D0-D15)--These pins provide the bidirectional data

for external program or data memory accesses.

86

D1

87

D2

88

D3

89

D4

90

D5

107

D6

108

D7

109

D8

110

D9

111

D10

122

D11

123

D12

126

D13

127

D14

128

D15

7

RD

Output

Read Enable (RD) --is asserted during external memory

read cycles.

This signal is pulled high during reset.

8

WR

Output

Write Enable (WR)-- is asserted during external memory

write cycles.

This signal is pulled high during reset.

75

CS0

GPIOA0

Output

Input/Output

External Chip Select (CS0)--This pin is used as a dedicated

GPIO.

Port A GPIO (0) --This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

76

CS1

GPIOA1

Output

Input/Output

External Chip Select (CS1)--This pin is used as a dedicated

GPIO.

Port A GPIO (1) --This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

77

CS2

GPIOA2

Output

Input/Output

External Chip Select (CS2)--This pin is used as a dedicated

GPIO.

Port A GPIO (2) --This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

78

CS3

GPIOA3

Output

Input/Output

External Chip Select (CS3)--This pin is used as a dedicated

GPIO.

Port A GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

10

DSP56853 Preliminary Technical Data

MOTOROLA

30

HD0

GPIOB0

Input

Input/Output

Host Address (HD0)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (0)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

31

HD1

GPIOB1

Input

Input/Output

Host Address (HD1)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

32

HD2

GPIOB2

Input

Input/Output

Host Address (HD2)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

36

HD3

GPIOB3

Input

Input/Output

Host Address (HD3)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

37

HD4

GPIOB4

Input

Input/Output

Host Address (HD4)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (4)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

38

HD5

GPIOB5

Input

Input/Output

Host Address (HD5)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (5)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

39

HD6

GPIOB6

Input

Input/Output

Host Address (HD6)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (6)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

11

40

HD7

GPIOB7

Input

Input/Output

Host Address (HD7)--This input provides data selection for

HI registers.

This pin is disconnected internally during reset.

Port B GPIO (7)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

82

HA0

GPIOB8

Input

Input/Output

Host Address (HA0)--These inputs provide the address

selection for HI registers.

These pins are disconnected internally during reset.

Port B GPIO (8)--These pins are General Purpose I/O

(GPIO) pins when not configured for host port usage.

83

HA1

GPIOB9

Input

Input/Output

Host Address (HA0)--These inputs provide the address

selection for HI registers.

These pins are disconnected internally during reset.

Port B GPIO (9)--These pins are General Purpose I/O

(GPIO) pins when not configured for host port usage.

84

HA2

GPIOB10

Input

Input/Output

Host Address (HA0)--These inputs provide the address

selection for HI registers.

These pins are disconnected internally during reset.

Port B GPIO (10)--These pins are General Purpose I/O

(GPIO) pins when not configured for host port usage.

85

HRWB

HRD

GPIOB11

Input

Input

Input/Output

Host Read/Write (HRWB)--When the HI08 is programmed

to interface to a single-data-strobe host bus and the HI

function is selected, this signal is the Read/Write input.

These pins are disconnected internally.

Host Read Data (HRD)--This signal is the Read Data input

when the HI08 is programmed to interface to a double-data-

strobe host bus and the HI function is selected.

Port B GPIO (11)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

103

HDS

HWR

GPIOB12

Input

Input

Input/Output

Host Data Strobe (HDS)--When the HI08 is programmed to

interface to a single-data-strobe host bus and the HI function

is selected, this input enables a data transfer on the HI when

HCS is asserted.

These pins are disconnected internally.

Host Write Enable (HWR)--This signal is the Write Data

input when the HI08 is programmed to interface to a double-

data-strobe host bus and the HI function is selected.

Port B GPIO (12)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

12

DSP56853 Preliminary Technical Data

MOTOROLA

104

HCS

GPIOB13

Input

Input/Output

Host Chip Select (HCS)--This input is the chip select input

for the Host Interface.

These pins are disconnected internally.

Port B GPIO (13)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

105

HREQ

HTRQ

GPIOB14

Open Drain

Output

Open Drain

Output

Input/Output

Host Request (HREQ)--When the HI08 is programmed for

HRMS=0 functionality (typically used on a single-data-strobe

bus), this open drain output is used by the HI to request

service from the host processor. The HREQ may be

connected to an interrupt request pin of a host processor, a

transfer request of a DMA controller, or a control input of

external circuitry.

These pins are disconnected internally.

Transmit Host Request (HTRQ)--This signal is the

Transmit Host Request output when the HI08 is programmed

for HRMS=1 functionality and is typically used on a double-

data-strobe bus.

Port B GPIO (14)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

106

HACK

HRRQ

GPIOB15

Input

Open Drain

Output

Input/Output

Host Acknowledge (HACK)--When the HI08 is

programmed for HRMS=0 functionality (typically used on a

single-data-strobe bus), this input has two functions: (1)

provide a Host Acknowledge signal for DMA transfers or (2)

to control handshaking and provide a Host Interrupt

Acknowledge compatible with the MC68000 family

processors.

These pins are disconnected internally.

Receive Host Request (HRRQ)--This signal is the Receive

Host Request output when the HI08 is programmed for

HRMS=1 functionality and is typically used on a double-data-

strobe bus.

Port B GPIO(15)--This pin is a General Purpose I/O (GPIO)

pin when not configured for host port usage.

101

TIO0

GPIOG0

Input/Output

Input/Output

Timer Input/Outputs (TIO0)--This pin can be independently

configured to be either a timer input source or an output flag.

Port G GPIOG0--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as an input or output

pin.

99

TIO1

GPIOG1

Input/Output

Input/Output

Timer Input/Outputs (TIO1)--This pin can be independently

configured to be either a timer input source or an output flag.

Port G GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as an input or output

pin.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

13

98

TIO2

GPIOG2

Input/Output

Input/Output

Timer Input/Outputs (TIO2)--This pin can be independently

configured to be either a timer input source or an output flag.

Port G GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as an input or output

pin.

97

TIO3

GPIOG3

Input/Output

Input/Output

Timer Input/Outputs (TIO3)--This pin can be independently

configured to be either a timer input source or an output flag.

Port G GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as an input or output

pin.

20

IRQA

Input

External Interrupt Request A and B--The IRQA and IRQB

inputs are asynchronous external interrupt requests that

indicate that an external device is requesting service. A

Schmitt trigger input is used for noise immunity. They can be

programmed to be level-sensitive or negative-edge-

triggered. If level-sensitive triggering is selected, an external

pull-up resistor is required for Wired-OR operation.

21

IRQB

15

MODA

GPIOH0

Input

Input/Output

Mode Select (MODA)--During the bootstrap process MODA

selects one of the eight bootstrap modes.

Port H GPIO (0)--This pin is a General Purpose I/O (GPIO)

pin after the bootstrap process has completed.

16

MODB

GPIOH1

Input

Input/Output

Mode Select (MODB)--During the bootstrap process MODB

selects one of the eight bootstrap modes.

Port H GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin after the bootstrap process has completed.

17

MODC

GPIOH2

Input

Input/Output

Mode Select (MODC)--During the bootstrap process MODC

selects one of the eight bootstrap modes.

Port H GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin after the bootstrap process has completed.

35

RESET

Input

Reset (RESET)--This input is a direct hardware reset on the

processor. When RESET is asserted low, the DSP is

initialized and placed in the Reset state. A Schmitt trigger

input is used for noise immunity. When the RESET pin is

deasserted, the initial chip operating mode is latched from the

MODA, MODB, and MODC pins.

To ensure complete hardware reset, RESET and TRST

should be asserted together. The only exception occurs in a

debugging environment when a hardware DSP reset is

required and it is necessary not to reset the JTAG/Enhanced

OnCE module. In this case, assert RESET, but do not assert

TRST.

34

RSTO

Output

Reset Output (RSTO)--This output is asserted on any reset

condition (external reset, low voltage, software or COP).

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

14

DSP56853 Preliminary Technical Data

MOTOROLA

65

RXD0

GPIOE0

Input

Input/Output

Serial Receive Data 0 (RXD0)--This input receives byte-

oriented serial data and transfers it to the SCI 0 receive shift

register.

Port E GPIO (0)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

66

TXD0

GPIOE1

Output(Z)

Input/Output

Serial Transmit Data 0 (TXD0)--This signal transmits data

from the SCI 0 transmit data register.

Port E GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

94

RXD1

GPIOE2

Input

Input/Output

Serial Receive Data 1 (RXD1)--This input receives byte-

oriented serial data and transfers it to the SCI 1 receive shift

register.

Port E GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

95

TXD1

GPIOE3

Output(Z)

Input/Output

Serial Transmit Data 1 (TXD1)--This signal transmits data

from the SCI 1 transmit data register.

Port E GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

116

STD0

GPIOC0

Output

Input/Output

ESSI Transmit Data (STD0)--This output pin transmits

serial data from the ESSI Transmitter Shift Register.

Port C GPIO (0)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

117

SRD0

GPIOC1

Input

Input/Output

ESSI Receive Data (SRD0)--This input pin receives serial

data and transfers the data to the ESSI Receive Shift

Register.

Port C GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

118

SCK0

GPIOC2

Input/Output

Input/Output

ESSI Serial Clock (SCK0)--This bidirectional pin provides

the serial bit rate clock for the transmit section of the ESSI.

The clock signal can be continuous or gated and can be used

by both the transmitter and receiver in synchronous mode.

Port C GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

15

119

SC00

GPIOC3

Input/Output

Input/Output

ESSI Serial Control Pin 0 (SC00)--The function of this pin is

determined by the selection of either synchronous or

asynchronous mode. For asynchronous mode, this pin will be

used for the receive clock I/O. For synchronous mode, this

pin is used either for transmitter1 output or for serial I/O flag

0.

Port C GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

120

SC01

GPIOC4

Input/Output

Input/Output

ESSI Serial Control Pin 1 (SC01)--The function of this pin is

determined by the selection of either synchronous or

asynchronous mode. For asynchronous mode, this pin is the

receiver frame sync I/O. For synchronous mode, this pin is

used either for transmitter2 output or for serial I/O flag 1.

Port C GPIO (4)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

121

SC02

GPIOC5

Input/Output

Input /Output

ESSI Serial Control Pin 2 (SC02)--This pin is used for

frame sync I/O. SC02 is the frame sync for both the

transmitter and receiver in synchronous mode and for the

transmitter only in asynchronous mode. When configured as

an output, this pin is the internally generated frame sync

signal. When configured as an input, this pin receives an

external frame sync signal for the transmitter (and the

receiver in synchronous operation).

Port C GPIO (5)--This pin is a General Purpose I/O (GPIO)

pin when the ESSI is not in use.

1

MISO

GPIOF0

Input/Output

Input/Output

SPI Master In/Slave Out (MISO)--This serial data pin is an

input to a master device and an output from a slave device.

The MISO line of a slave device is placed in the high-

impedance state if the slave device is not selected. The

driver on this pin can be configured as an open-drain driver

by the SPI's Wired-OR mode (WOM) bit when this pin is

configured for SPI operation.

Port F GPIO (0)--This pin is a General Purpose I/O (GPIO)

pin that can be individually programmed as input or output

pin.

2

MOSI

GPIOF1

Input/Output (Z)

Input/Output

SPI Master Out/Slave In (MOSI)--This serial data pin is an

output from a master device and an input to a slave device.

The master device places data on the MOSI line a half-cycle

before the clock edge that the slave device uses to latch the

data. The driver on this pin can be configured as an open-

drain driver by the SPI's WOM bit when this pin is configured

for SPI operation.

Port F GPIO (1)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

16

DSP56853 Preliminary Technical Data

MOTOROLA

3

SCK

GPIOF2

Input/Output

Input/Output

SPI Serial Clock (SCK)--This bidirectional pin provides a

serial bit rate clock for the SPI. This gated clock signal is an

input to a slave device and is generated as an output by a

master device. Slave devices ignore the SCK signal unless

the SS pin is active low. In both master and slave SPI

devices, data is shifted on one edge of the SCK signal and is

sampled on the opposite edge, where data is stable. The

driver on this pin can be configured as an open-drain driver

by the SPI's WOM bit when this pin is configured for SPI

operation. When using Wired-OR mode, the user must

provide an external pull-up device.

Port F GPIO (2)--This pin is a General Purpose I/O (GPIO)

pin that can be individually programmed as input or output

pin.

4

SS

GPIOF3

Input

Input/Output

SPI Slave Select (SS)--This input pin selects a slave device

before a master device can exchange data with the slave

device. SS must be low before data transactions and must

stay low for the duration of the transaction. The SS line of the

master must be held high.

Port F GPIO (3)--This pin is a General Purpose I/O (GPIO)

pin that can individually be programmed as input or output

pin.

24

XTAL

Input/Output

Crystal Oscillator Output (XTAL)--This output connects

the internal crystal oscillator output to an external crystal. If

an external clock source other than a crystal oscillator is

used, XTAL must be used as the input.

25

EXTAL

Input

External Crystal Oscillator Input (EXTAL)--This input

should be connected to an external crystal. If an external

clock source other than a crystal oscillator is used, EXTAL

must be tied off. See

Section 4.5.2

33

CLKO

Output

Clock Output (CLKO)--This pin outputs a buffered clock

signal. When enabled, this signal is the system clock divided

by four.

54

TCK

Input

Test Clock Input (TCK)--This input pin provides a gated

clock to synchronize the test logic and to shift serial data to

the JTAG/Enhanced OnCE port. The pin is connected

internally to a pull-down resistor.

52

TDI

Input

Test Data Input (TDI)--This input pin provides a serial input

data stream to the JTAG/Enhanced OnCE port. It is sampled

on the rising edge of TCK and has an on-chip pull-up resistor.

51

TDO

Output (Z)

Test Data Output (TDO)--This tri-statable output pin

provides a serial output data stream from the JTAG/

Enhanced OnCE port. It is driven in the Shift-IR and Shift-DR

controller states, and changes on the falling edge of TCK.

53

TMS

Input

Test Mode Select Input (TMS)--This input pin is used to

sequence the JTAG TAP controller's state machine. It is

sampled on the rising edge of TCK and has an on-chip pull-

up resistor.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

Introduction

MOTOROLA

DSP56853 Preliminary Technical Data

17

50

TRST

Input

Test Reset (TRST)--As an input, a low signal on this pin

provides a reset signal to the JTAG TAP controller. To ensure

complete hardware reset, TRST should be asserted

whenever RESET is asserted. The only exception occurs in a

debugging environment, since the Enhanced OnCE/JTAG

module is under the control of the debugger. In this case it is

not necessary to assert TRST when asserting RESET .

Outside of a debugging environment RESET should be

permanently asserted by grounding the signal, thus disabling

the Enhanced OnCE/JTAG module on the DSP.

49

DE

Input/Output

Debug Event (DE)--This is an open-drain, bidirectional,

active low signal. As an input, it is a means of entering debug

mode of operation from an external command controller. As

an output, it is a means of acknowledging that the chip has

entered debug mode.

This pin is connected internally to a weak pull-up resistor.

Table 3. DSP56853 Signal and Package Information for the 128-pin LQFP

Pin No.

Signal Name

Type

Description

18

DSP56853 Preliminary Technical Data

MOTOROLA

Part 4 Specifications

4.1 General Characteristics

The DSP56853 is fabricated in high-density CMOS with 5-volt tolerant TTL-compatible digital inputs.

The term "5-volt tolerant" refers to the capability of an I/O pin, built on a 3.3V compatible process

technology, to withstand a voltage up to 5.5V without damaging the device. Many systems have a mixture

of devices designed for 3.3V and 5V power supplies. In such systems, a bus may carry both 3.3V and 5V-

compatible I/O voltage levels (a standard 3.3V I/O is designed to receive a maximum voltage of 3.3V

±

10% during normal operation without causing damage). This 5V tolerant capability therefore offers the

power savings of 3.3V I/O levels while being able to receive 5V levels without being damaged.

Absolute maximum ratings given in

Table 4

are stress ratings only, and functional operation at the

maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent

damage to the device.

The DSP56853 DC/AC electrical specifications are preliminary and are from design simulations. These

specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized

specifications will be published after complete characterization and device qualifications have been

completed.

CAUTION

This device contains protective circuitry to guard

against damage due to high static voltage or

electrical fields. However, normal precautions are

advised to avoid application of any voltages higher

than maximum rated voltages to this high-impedance

circuit. Reliability of operation is enhanced if unused

inputs are tied to an appropriate voltage level.

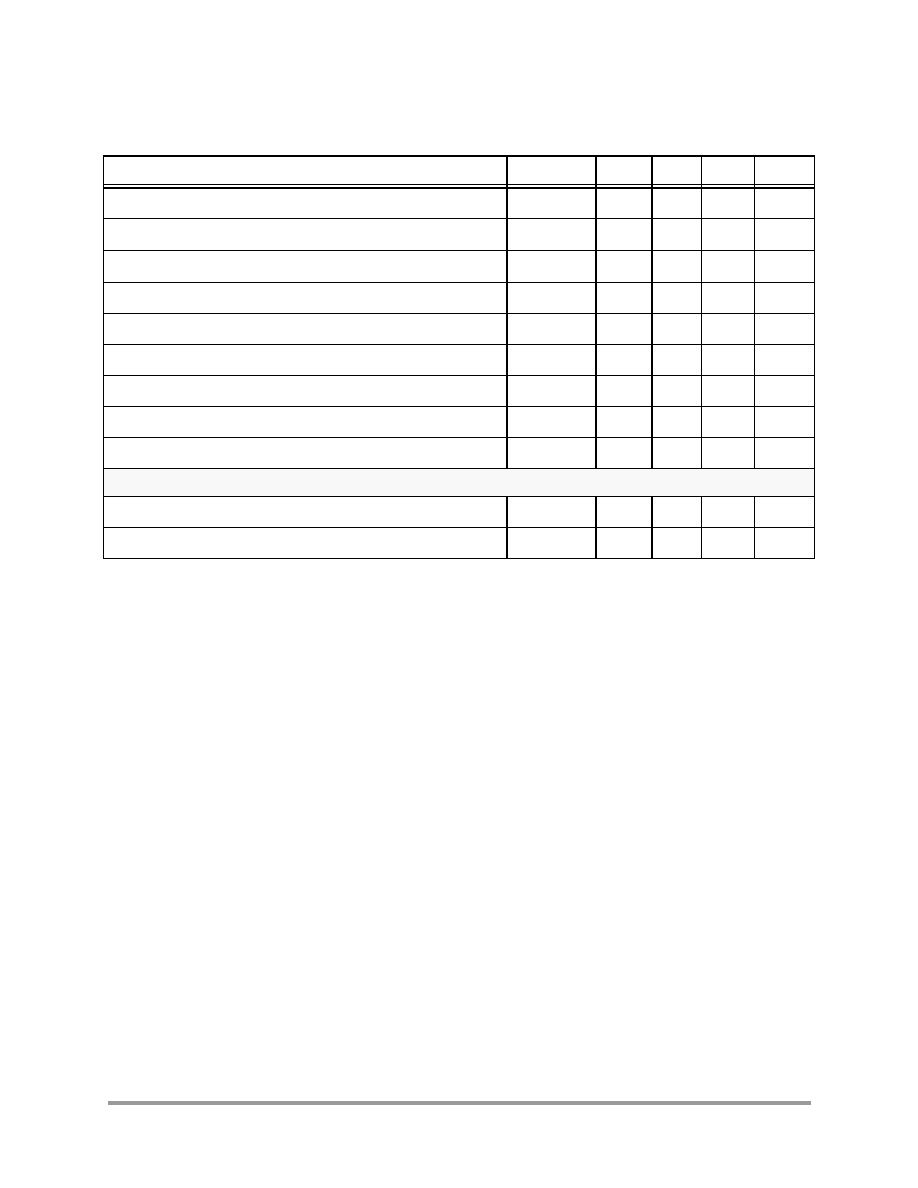

Table 4. Absolute Maximum Ratings

Characteristic

Symbol

Min

Max

Unit

Supply voltage, core

V

DD

1

1.

V

DD

must not exceed V

DDIO

V

SS

≠ 0.3

V

SS

+ 2.0

V

Supply voltage, IO

Supply voltage, analog

V

DDIO

2

V

DDIO

2

2.

V

DDIO

and V

DDA

must not differ by more that 0.5V

V

SSIO

≠ 0.3

V

SSA

≠ 0.3

V

SSIO

+ 4.0

V

DDA

+ 4.0

V

Digital input voltages

Analog input voltages (XTAL, EXTAL)

V

IN

V

INA

V

SSIO

≠ 0.3

V

SSA

≠ 0.3

V

SSIO

+ 5.5

V

DDA

+ 0.3

V

Current drain per pin excluding V

DD

, GND

I

--

8 mA

Junction temperature

T

J

-40

120

∞C

Storage temperature range

T

STG

-55

150

∞C

General Characteristics

MOTOROLA

DSP56853 Preliminary Technical Data

19

Table 5. Recommended Operating Conditions

Characteristic

Symbol

Min

Max

Unit

Supply voltage for Logic Power

V

DD

1.62

1.98

V

Supply voltage for I/O Power

V

DDIO

3.0

3.6

V

Supply voltage for Analog Power

V

DDA

3.0

3.6

V

Ambient operating temperature

T

A

-40

85

∞C

PLL clock frequency

1

1.

Assumes clock source is direct clock to EXTAL or crystal oscillator running 2-4MHz. PLL must be enabled, locked, and

selected. The actual frequency depends on the source clock frequency and programming of the CGM module.

f

pll

--

240

MHz

Operating Frequency

2

2.

Master clock is derived from on of the following four sources:

f

clk

= f

xtal

when the source clock is the direct clock to EXTAL

f

clk

= f

pll

when PLL is selected

f

clk

= f

osc

when the source clock is the crystal oscillator and PLL is not selected

f

clk

= f

extal

when the source clock is the direct clock to EXTAL and PLL is not selected

f

op

--

120

MHz

Frequency of peripheral bus

f

ipb

--

60

MHz

Frequency of external clock

f

clk

--

240

MHz

Frequency of oscillator

f

osc

2

4

MHz

Frequency of clock via XTAL

f

xtal

--

240

MHz

Frequency of clock via EXTAL

f

extal

2

4

MHz

Table 6. Thermal Characteristics

1

1.

See

Section 6.1

for more detail.

Characteristic

128-pin LQFP

Symbol

Value

Unit

Thermal resistance junction-to-ambient

(estimated)

JA

43.1

∞C/W

I/O pin power dissipation

P

I/O

User Determined

W

Power dissipation

P

D

P

D

= (I

DD

◊

V

DD

) + P

I/O

W

Maximum allowed P

D

P

DMAX

(T

J

≠ T

A

) /

JA

∞

C

20

DSP56853 Preliminary Technical Data

MOTOROLA

4.2 DC Electrical Characteristics

Table 7. DC Electrical Characteristics

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

Characteristic

Symbol

Min

Typ

Max

Unit

Input high voltage (XTAL/EXTAL)

V

IHC

V

DDA

≠ 0.8

V

DDA

V

DDA

+ 0.3

V

Input low voltage (XTAL/EXTAL)

V

ILC

-0.3

--

0.5

V

Input high voltage

V

IH

2.0

--

5.5

V

Input low voltage

V

IL

-0.3

--

0.8

V

Input current low (pullups disabled)

I

IL

-1

--

1

µ

A

Input current high (pullups disabled)

I

IH

-1

--

1

µ

A

Output tri-state current low

I

OZL

-10

--

10

µ

A

Output tri-state current high

I

OZH

-10

--

10

µ

A

Output High Voltage

V

OH

V

DD

≠ 0.7

--

--

V

Output Low Voltage

V

OL

--

--

0.4

V

Output High Current

I

OH

8

--

16

mA

Output Low Current

I

OL

8

--

16

mA

Input capacitance

C

IN

--

8

--

pF

Output capacitance

C

OUT

--

12

--

pF

V

DD

supply current @ nominal voltage and 25

∞

C

Run

1

Deep Stop

2

Light Stop

3

1.

Run (operating) I

DD

measured using external square wave clock source (f

osc

= 4MHz) into XTAL. All inputs 0.2V from

rail; no DC loads; outputs unloaded. All ports configured as inputs; measured with all modules enabled. PLL set to 240MHz

out. Running Core, performing 50% NOP and 50% FIR. Clock at 120 MHz.

I

DD

4

--

--

--

70

100

2.6

--

--

--

mA

µ

A

mA

V

DDIO

supply current @ nominal voltage and 25

∞

C

Run

5

I

DDIO

--

40

--

mA

V

DDA

supply current @ nominal voltage and 25

∞

C

Deep Stop

2

I

DDA

--

60

--

µ

A

Low Voltage Interrupt

6

V

EI

--

2.5

2.85

V

Low Voltage Interrupt Recovery Hysteresis

V

EIH

--

50

--

mV

Power on Reset

7

POR

--

1.5

2.0

V

Supply Voltage Sequencing and Separation Cautions

MOTOROLA

DSP56853 Preliminary Technical Data

21

4.3 Supply Voltage Sequencing and Separation Cautions

Figure 1

shows two situations to avoid in sequencing the V

DD

and V

DDIO,

V

DDA

supplies.

Notes: 1. V

DD

rising before V

DDIO

, V

DDA

2. V

DDIO

, V

DDA

rising much faster than V

DD

Figure 3. Supply Voltage Sequencing and Separation Cautions

V

DD

should not be allowed to rise early (1). This is usually avoided by running the regulator for the V

DD

supply (1.8V) from the voltage generated by the 3.3V V

DDIO

supply, see

Figure 2

. This keeps V

DD

from

rising faster than V

DDIO

.

V

DD

should not rise so late that a large voltage difference is allowed between the two supplies (2). Typically

this situation is avoided by using external discrete diodes in series between supplies, as shown in

Figure 2

.

The series diodes forward bias when the difference between V

DDIO

and V

DD

reaches approximately 2.1,

causing V

DD

to rise as V

DDIO

ramps up. When the V

DD

regulator begins proper operation, the difference

between supplies will typically be 0.8V and conduction through the diode chain reduces to essentially

leakage current. During supply sequencing, the following general relationship should be adhered to:

V

DDIO

> V

DD

> (V

DDIO

- 2.1V)

In practice, V

DDA

is typically connected directly to V

DDIO

with some filtering.

2.

Deep Stop Mode - Operation frequency = 4 MHz, PLL set to 4 MHz, crystal oscillator and time of day module operat-

ing.

3.

Light Stop Mode - Operation frequency = 120 MHz, PLL set to 240 MHz, crystal oscillator and time of day module

operating.

4.

I

DD

includes current for core logic, internal memories, and all internal peripheral logic circuitry.

5.

Running core and performing external memory access. Clock at 120 MHz.

6.

When V

DD

drops below V

EI

max value, an interrupt is generated.

7.

Power-on reset occurs whenever the digital supply drops below 1.8V. While power is ramping up, this signal remains

active for as long as the internal 2.5V is below 1.8V no matter how long the ramp up rate is. The internally regulated voltage

is typically 100 mV less than V

DD

during ramp up until 2.5V is reached, at which time it self-regulates.

3.3V

1.8V

Time

0

2

1

Supplies Stable

V

DD

V

DDIO,

V

DDA

D

C

P

o

wer

Suppl

y V

o

l

t

a

g

e

22

DSP56853 Preliminary Technical Data

MOTOROLA

Figure 4. Example Circuit to Control Supply Sequencing

4.4 AC Electrical Characteristics

Timing waveforms in

Section 4.2

are tested with a V

IL

maximum of 0.8 V and a V

IH

minimum of 2.0 V for

all pins except XTAL, which is tested using the input levels in

Section 4.2

. In

Figure 5

the levels of V

IH

and V

IL

for an input signal are shown.

Figure 5. Input Signal Measurement References

Figure 6

shows the definitions of the following signal states:

∑

Active state, when a bus or signal is driven, and enters a low impedance state.

∑

Tri-stated, when a bus or signal is placed in a high impedance state.

∑

Data Valid state, when a signal level has reached V

OL

or V

OH.

∑

Data Invalid state, when a signal level is in transition between V

OL

and V

OH.

Figure 6. Signal States

3.3V

Regulator

1.8V

Regulator

Supply

V

DD

V

DDIO,

V

DDA

V

IH

V

IL

Fall Time

Input Signal

Note: The midpoint is V

IL

+ (V

IH

≠ V

IL

)/2.

Midpoint1

Low

High

90%

50%

10%

Rise Time

Data Invalid State

Data1

Data2 Valid

Data

Tri-stated

Data3 Valid

Data2

Data3

Data1 Valid

Data Active

Data Active

External Clock Operation

MOTOROLA

DSP56853 Preliminary Technical Data

23

4.5 External Clock Operation

The DSP56853 system clock can be derived from a crystal or an external system clock signal. To generate

a reference frequency using the internal oscillator, a reference crystal must be connected between the

EXTAL and XTAL pins.

4.5.1

Crystal Oscillator

The internal oscillator is designed to interface with a parallel-resonant crystal resonator in the frequency

range specified for the external crystal in

Table 9

. In

Figure 7

a typical crystal oscillator circuit is shown.

Follow the crystal supplier's recommendations when selecting a crystal, because crystal parameters

determine the component values required to provide maximum stability and reliable start-up. The crystal

and associated components should be mounted as close as possible to the EXTAL and XTAL pins to

minimize output distortion and start-up stabilization time.

Figure 7. Crystal Oscillator

4.5.2

High Speed External Clock Source (> 4MHz)

The recommended method of connecting an external clock is given in

Figure 8

. The external clock source

is connected to XTAL and the EXTAL pin is held at ground, V

DDA

, or V

DDA

/2. The TOD_SEL bit in

CGM must be set to 0.

Figure 8. Connecting a High Speed External Clock Signal using XTAL

4.5.3

Low Speed External Clock Source (2-4MHz)

The recommended method of connecting an external clock is given in

Figure 9

. The external clock source

is connected to XTAL and the EXTAL pin is held at V

DDA

/2. The TOD_SEL bit in CGM must be set to 0.

Sample External Crystal Parameters:

R

z

= 10M

TOD_SEL bit in CGM must be set to 0

Crystal Frequency = 2≠4 MHz (optimized for 4MHz)

EXTAL XTAL

R

z

DSP56853

XTAL

EXTAL

External

GND,

V

DDA

,

Clock

(up to 240MHz)

or V

DDA

/2

24

DSP56853 Preliminary Technical Data

MOTOROLA

Figure 9. Connecting a Low Speed External Clock Signal using XTAL

Figure 10. External Clock Timing

Table 8. External Clock Operation Timing Requirements

4

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

Characteristic

Symbol

Min

Typ

Max

Unit

Frequency of operation (external clock driver)

1

1.

See

Figure 8

for details on using the recommended connection of an external clock driver.

f

osc

0

--

240

MHz

Clock Pulse Width

4

t

PW

6.25

--

--

ns

External clock input rise time

2, 4

2.

External clock input rise time is measured from 10% to 90%.

t

rise

--

--

TBD

ns

External clock input fall time

3,

4

3.

External clock input fall time is measured from 90% to 10%.

4.

Parameters listed are guaranteed by design.

t

fall

--

--

TBD

ns

Table 9. PLL Timing

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

Characteristic

Symbol

Min

Typ

Max

Unit

External reference crystal frequency for the PLL

1

1.

An externally supplied reference clock should be as free as possible from any phase jitter for the PLL to work correctly.

The PLL is optimized for 4MHz input crystal.

f

osc

2

4

4

MHz

PLL output frequency

f

clk

40

--

240

MHz

PLL stabilization time

2

2.

This is the minimum time required after the PLL setup is changed to ensure reliable operation.

t

plls

--

1

10

ms

DSP56853

XTAL

EXTAL

External

Clock

(2-4MHz)

V

DDA

/2

External

Clock

V

IH

V

IL

Note: The midpoint is V

IL

+ (V

IH

≠ V

IL

)/2.

90%

50%

10%

90%

50%

10%

t

PW

t

PW

t

fall

t

rise

External Memory InterfaceTiming

MOTOROLA

DSP56853 Preliminary Technical Data

25

4.6 External Memory InterfaceTiming

The External Memory Interface is designed to access static memory and peripheral devices.

Figure 11

shows sample timing and parameters that are detailed in

Table 10

.

The timing of each parameter consists of both a fixed delay portion and a clock related portion; as well as

user controlled wait states. The equation:

t = D + P * (M + W)

should be used to determine the actual time of each parameter. The terms in the above equation are

defined as:

t

parameter delay time

D

fixed portion of the delay, due to on-chip path delays.

P

the period of the system clock, which determines the execution rate of the part (i.e. when the

device is operating at 120 MHz, P = 8.33 ns).

M Fixed portion of a clock period inherent in the design. This number is adjusted to account for

possible clock duty cycle derating.

W the sum of the applicable wait state controls. See the "Wait State Controls" column of

Table 10

for the applicable controls for each parameter. See the EMI chapter of the 83x

Peripheral Manual for details of what each wait state field controls.

Some of the parameters contain two sets of numbers. These parameters have two different paths and clock

edges that must be considered. Check both sets of numbers and use the smaller result. The appropriate entry

may change if the operating frequency of the part changes.

The timing of write cycles is different when WWS = 0 than when WWS > 0. Therefore, some parameters

contain two sets of numbers to account for this difference. The "Wait States Configuration" column of

Table 10

should be used to make the appropriate selection.

Figure 11. External Memory Interface Timing

t

DRD

t

RDD

t

AD

t

DOH

t

DOS

t

DWR

t

RDWR

t

WAC

t

WRRD

t

WR

t

AWR

t

WRWR

t

ARDD

t

RDA

t

RDRD

t

RD

t

ARDA

Data Out

Data In

A0-Axx,CS

RD

WR

D0-D15

Note: During read-modify-write instructions and internal instructions, the address lines do not change state.

26

DSP56853 Preliminary Technical Data

MOTOROLA

Table 10. External Memory Interface Timing

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98 V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞ to +120∞C, C

L

50pF, P = 8.333ns

Characteristic

Symbol

Wait States

Configuration

D

M

Wait States

Controls

Unit

Address Valid to WR Asserted

t

AWR

WWS=0 -0.79

0.50

WWSS

ns

WWS>0

-1.98

0.69

WR Width Asserted to WR

Deasserted

t

WR

WWS=0 -0.86

0.19

WWS

ns

WWS>0

-0.01

0.00

Data Out Valid to WR Asserted

t

DWR

WWS=0

-1.52

0.00

WWSS

ns

WWS=0 -

5.69

0.25

WWS>0

-2.10

0.19

WWS>0

-4.66

0.50

Valid Data Out Hold Time after WR

Deasserted

t

DOH

-1.47

0.25

WWSH

ns

Valid Data Out Set Up Time to WR

Deasserted

t

DOS

-2.36

0.19

WWS,WWSS

ns

-4.67

0.50

Valid Address after WR

Deasserted

t

WAC

-1.60

0.25

WWSH

RD Deasserted to Address Invalid

t

RDA

- 0.44

0.00

RWSH

ns

Address Valid to RD Deasserted

t

ARDD

-2.07

1.00

RWSS,RWS

ns

Valid Input Data Hold after RD

Deasserted

t

DRD

0.00

N/A

1

1.

N/A since device captures data before it deasserts RD

--

ns

RD Assertion Width

t

RD

-1.34

1.00

RWS

ns

Address Valid to Input Data Valid

t

AD

-10.27

1.00

RWSS,RWS

ns

-13.5

1.19

Address Valid to RD Asserted

t

ARDA

- 0.94

0.00

RWSS

ns

RD Asserted to Input Data Valid

t

RDD

-9.53

1.00

RWSS,RWS

ns

-12.64

1.19

WR Deasserted to RD Asserted

t

WRRD

-0.75

0.25

WWSH,RWSS

ns

RD Deasserted to RD Asserted

t

RDRD

-0.16

2

2.

If RWSS = RWSH = 0, RD does not deassert during back-to-back reads and D=0.00 should be used.

0.00

RWSS,RWSH

ns

WR Deasserted to WR Asserted

t

WRWR

WWS=0

-0.44

0.75

WWSS, WWSH

ns

WWS>0

-0.11

1.00

RD Deasserted to WR Asserted

t

RDWR

0.14

0.50

MDAR, BMDAR,

RWSH, WWSS

ns

-0.57

0.69

Reset, Stop, Wait, Mode Select, and Interrupt Timing

MOTOROLA

DSP56853 Preliminary Technical Data

27

4.7 Reset, Stop, Wait, Mode Select, and Interrupt Timing

Table 11. Reset, Stop, Wait, Mode Select, and Interrupt Timing

1, 2

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

1.

In the formulas, T = clock cycle. For f

op

= 120MHz operation and f

ipb

= 60MHz, T = 8.33ns.

2.

Parameters listed are guaranteed by design.

Characteristic

Symbol

Min

Max

Unit

See

Figure

RESET Assertion to Address, Data and Control

Signals High Impedance

t

RAZ

--

11

ns

Figure 12

Minimum RESET Assertion Duration

3

3.

At reset, the PLL is disabled and bypassed. The part is then put into Run mode and t

clk

assumes the period of the source

clock, t

xtal

, t

extal

or t

osc

.

t

RA

30

--

ns

Figure 12

RESET Deassertion to First External Address Output

t

RDA

--

120T

ns

Figure 12

Edge-sensitive Interrupt Request Width

t

IRW

1T + 3

--

ns

Figure 13

IRQA, IRQB Assertion to External Data Memory

Access Out Valid, caused by first instruction execution

in the interrupt service routine

t

IDM

--

18T

ns

Figure 14

IRQA, IRQB Assertion to General Purpose Output

Valid, caused by first instruction execution in the

interrupt service routine

t

IG

--

18T

ns

Figure 14

IRQA Low to First Valid Interrupt Vector Address Out

recovery from Wait State

4

4.

The minimum is specified for the duration of an edge-sensitive IRQA interrupt required to recover from the Wait state.

This is not the minimum required so that the IRQA interrupt is accepted.

t

IRI

--

13T

ns

Figure 15

IRQA Width Assertion to Recover from Stop State

5

Fast

6

Normal

7, 8

5.

This interrupt instruction fetch is visible on the pins only in Mode 3.

6.

Fast stop mode:

Fast stop recovery applies when fast stop mode recovery is requested (OMR bit 6 is set to 1). The PLL and the master

clock are unaffected by stop mode entry. Recovery takes one less cycle and t

clk

will continue with the same value it had before

stop mode was entered.

7.

Normal stop mode:

As a power saving feature, normal stop mode disables and bypasses the PLL. Stop mode will then shut down the master

clock, recovery will take an extra cycle (to restart the clock), and t

clk

will resume at the input clock source rate.

8.

ET = External Clock period; for an external crystal frequency of 4MHz, ET=250ns.

t

IW

4T

8ET

--

--

ns

ns

Figure 16

Delay from IRQA Assertion to Fetch of first instruction

(exiting Stop)

Fast

5

Normal

6,7

t

IF

--

--

13T

25ET

ns

ns

Figure 16

RSTO pulse width

7

normal operation

internal reset mode

t

RSTO

128ET

8ET

--

--

--

--

Figure 17

28

DSP56853 Preliminary Technical Data

MOTOROLA

Figure 12. Asynchronous Reset Timing

Figure 13. External Interrupt Timing (Negative-Edge-Sensitive)

Figure 14. External Level-Sensitive Interrupt Timing

Figure 15. Interrupt from Wait State Timing

First Fetch

A0≠A20,

D0≠D15

CS,

RD, WR

RESET

First Fetch

t

RDA

t

RA

t

RAZ

IRQA

IRQB

t

IRW

A0≠A20,

CS,

RD

,

WR

IRQA,

IRQB

First Interrupt Instruction Execution

a) First Interrupt Instruction Execution

Purpose

I/O Pin

IRQA,

IRQB

b) General Purpose I/O

t

IG

t

IDM

General

Instruction Fetch

IRQA,

IRQB

First Interrupt Vector

A0≠A20,

CS,

RD, WR

t

IRI

Host Interface Port

MOTOROLA

DSP56853 Preliminary Technical Data

29

Figure 16. Recovery from Stop State Using Asynchronous Interrupt Timing

Figure 17. Reset Output Timing

4.8 Host Interface Port

Table 12. Host Interface Port Timing

1

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

1.

The formulas: T = clock cycle. f ipb = 60MHz, T = 16.7ns.

Characteristic

Symbol

Min

Max

Unit

See Figure

Access time

TACKDV

--

13

ns

Figure 18

Disable time

TACKDZ

3

--

ns

Figure 18

Time to disassert

TACKREQH

3.5

9

ns

Figure 18

Figure 21

Lead time

TREQACKL

0

--

ns

Figure 18

Figure 21

Access time

TRADV

--

13

ns

Figure 19

Figure 20

Disable time

TRADX

5

--

ns

Figure 19

Figure 20

Disable time

TRADZ

3

--

ns

Figure 19

Figure 20

Setup time

TDACKS

3

--

ns

Figure 21

Hold time

TACKDH

1

--

ns

Figure 21

Setup time

TADSS

3

--

ns

Figure 22

Figure 23

Hold time

TDSAH

1

--

ns

Figure 22

Figure 23

Pulse width

TWDS

5

--

ns

Figure 22

Figure 23

Time to re-assert

1. After second write in 16-bit mode

2. After first write in 16-bit mode or after write in 8-bit mode

TACKREQL

4T + 5

5

5T + 9

13

ns

ns

Figure 18

,

Figure 21

Not IRQA Interrupt Vector

IRQA

A0≠A20,

CS,

RD, WR

First Instruction Fetch

t

IW

t

IF

RESET

t

RSTO

30

DSP56853 Preliminary Technical Data

MOTOROLA

Figure 18. DSP-to-Host DMA Read Mode

Figure 19. Single Strobe Read Mode

Figure 20. Dual Strobe Read Mode

HACK

HD

HREQ

TACKDV

TACKDZ

TREQACKL

TACKREQL

TACKREQH

TRADV

TRADZ

TRADX

HA

HCS

HDS

HD

HRW

TRADV

TRADZ

TRADX

HA

HCS

HWR

HD

HRD

Host Interface Port

MOTOROLA

DSP56853 Preliminary Technical Data

31

Figure 21. Host-to-DSP DMA Write Mode

Figure 22. Single Strobe Write Mode

Figure 23. Dual Strobe Write Mode

HACK

HREQ

HD

TDACKS

TACKDH

TREQACKL

TACKREQL

TACKREQH

HA

HCS

HDS

HD

HRW

TADSS

TADSS

TDSAH

TDSAH

TWDS

TDSAH

HA

HCS

HWR

HD

HRD

TWDS

TADSS

TADSS

TDSAH

32

DSP56853 Preliminary Technical Data

MOTOROLA

4.9 Serial Peripheral Interface (SPI) Timing

1. Parameters listed are guaranteed by design.

Table 13. SPI Timing

1

Operating Conditions: V

SS

= V

SSIO

= V

SSA

= 0 V, V

DD

= 1.62-1.98V, V

DDIO

= V

DDA

=

3.0≠3.6V, T

A

= ≠40

∞

to +120

∞

C, C

L

50pF, f

op

= 120MHz

Characteristic

Symbol

Min

Max

Unit

See

Figure

Cycle time

Master

Slave

t

C

25

25

--

--

ns

ns

Figures

24

,

25

,

26

,

27

Enable lead time

Master

Slave

t

ELD

--

12.5

--

--

ns

ns

Figure

27

Enable lag time

Master

Slave

t

ELG

--

12.5

--

--

ns

ns

Figure

27

Clock (SCLK) high time

Master

Slave

t

CH

9

12.5

--

--

ns

ns

Figures

24

,

25

,

26

,

27

Clock (SCLK) low time

Master

Slave

t

CL

12

12.5

--

--

ns

ns

Figure

27

Data set-up time required for inputs

Master

Slave

t

DS

10

2

--

--

ns

ns

Figures

24

,

25

,

26

,

27

Data hold time required for inputs

Master

Slave

t

DH

0

2

--

--

ns

ns

Figures

24

,

25

,

26

,

27

Access time (time to data active from high-impedance state)

Slave

t

A

5

15

ns

ns

Figure

27

Disable time (hold time to high-impedance state)

Slave

t

D

2

9

ns

ns

Figure

27

Data valid for outputs

Master

Slave (after enable edge)

t

DV

--

--

2

14

ns

ns

Figures

24

,

25

,

26

,

27

Data invalid

Master

Slave

t

DI

0

0

--

--

ns

ns

Figures

24

,

25

,

26

,

27

Rise time

Master

Slave

t

R

--

--

11.5

10.0

ns

ns

Figures

24

,

25

,

26

,

27

Fall time

Master

Slave

t

F

--

--

9.7

9.0

ns

ns

Figures

24

,

25

,

26

,

27

Serial Peripheral Interface (SPI) Timing

MOTOROLA

DSP56853 Preliminary Technical Data

33

Figure 24. SPI Master Timing (CPHA = 0)

Figure 25. SPI Master Timing (CPHA = 1)

SCLK (CPOL = 0)

(Output)

SCLK (CPOL = 1)

(Output)

MISO

(Input)

MOSI

(Output)

MSB in

Bits 14≠1

LSB in

Master MSB out

Bits 14≠1

Master LSB out

SS

(Input)

SS is held High on master

t

C

t

R

t

F

t

CH

t

CL

t

F

t

R

t

CH

t

CH

t

DV

t

DH

t

DS

t

DI

t

DI

(ref)

t

F

t

R

t

CL

SCLK (CPOL = 0)

(Output)

SCLK (CPOL = 1)

(Output)

MISO

(Input)

MOSI

(Output)

MSB in

Bits 14≠1

LSB in

Master MSB out

Bits 14≠ 1

Master LSB out

SS

(Input)

SS is held High on master

t

R

t

F

t

C

t

CH

t

CL

t

CH

t

CL

t

F

t

DS

t

DH

t

R

t

DI

t

DV

(ref)

t

DV

t

F

t

R

34

DSP56853 Preliminary Technical Data

MOTOROLA

Figure 26. SPI Slave Timing (CPHA = 0)

Figure 27. SPI Slave Timing (CPHA = 1)

SCLK (CPOL = 0)

(Input)

SCLK (CPOL = 1)

(Input)

MISO

(Output)

MOSI

(Input)

Slave MSB out

Bits 14≠1

MSB in

Bits 14≠1

LSB in

SS

(Input)

Slave LSB out

t

DS

t

CL

t

CL

t

DI

t

DI

t

CH

t

CH

t

R

t

R

t

ELG

t

DH

t

ELD

t

C

t

F