4707 Dey Road Liverpool, N.Y. 13088

M.S.KENNEDY CORP.

(315) 701-6751

4358

FEATURES:

500V, 25 Amp Capability at 110∞C

Fully Isolated Bridge

Ultra Low Thermal Resistance

Integral Free Wheeling Fast Recovery Epitaxial Diode (FRED)

Self-Contained, Smart Lowside/Highside Drive Circuitry and Isolated Supply

Adjustable Deadtime

Capable of Switching Frequencies to 20KHz

Isolated Case Allows Direct Heat Sinking

Case Bolt-down Design Allows Superior Heat Dissipation

MIL-PRF-38534 CERTIFIED

25 AMP, 500 VOLT IGBT PLUS DIODE

FULLY ISOLATED

SMART POWER 3-PHASE MOTOR

DRIVE POWER HYBRID

EQUIVALENT SCHEMATIC

DESCRIPTION:

The MSK 4358 is a 25 Amp, 3 Phase Isolated Bridge Smart Power Motor Drive Hybrid with a 500 volt rating. The

output switches are Insulated Gate Bipolar Transistors (IGBT's) tailored for high switching speeds. The free-wheeling

diodes are Fast Recovery Epitaxial Diodes (FRED's) to provide matched current capabilities with the IGBT's and are

specified with excellent reverse recovery times at high current ratings. The bridge is optically isolated from the control

circuitry. This new smart power motor drive hybrid is compatible with 5v CMOS or TTL logic levels. The internal circuitry

prevents simultaneous turn-on of the in-line half bridge transistors with adjustable deadtime to prevent shoot-through.

Undervoltage lockout shuts down the bridge when the supply voltage gets to a point of incomplete turn-on of the output

switches. The isolated internal high-side power supply derived from the +15 volt supply completely eliminates the need for

3 floating independent power supplies for the high-side drive.

1

2

3

4

5

6

7

8

9

10

11

+15V

GND

AHI

ALO

BHI

BLO

+15V

GND

CHI

CLO

+15V

TYPICAL APPLICATIONS

ISO-9001 CERTIFIED BY DSCC

3 PHASE SIX STEP DC BRUSHLESS MOTOR DRIVE

OR 3 PHASE SINUSOIDAL INDUCTION MOTOR DRIVE

PIN-OUT INFORMATION

PRELIMINARY Rev. B 11/01

1

12

13

14

15

16

17

18

19

20

21

22

GND

RESET

R/C

+15V

GND

OSCOUT

N/C

N/C

N/C

N/C

N/C

23

24

25

26

27

28

29

30

31

32

33

N/C

N/C

RKELVIN+

RKELVIN-

RSENSE-

RSENSE+

CV-

N/C

Cÿ

CV+

N/C

34

35

36

37

38

39

40

41

42

43

N/C

BV-

N/C

Bÿ

BV+

N/C

AV-

N/C

Aÿ

AV+

Storage Temperature Range

Lead Temperature Range(

10 Seconds

)

Case Operating Temperature

MSK4358

MSK4358H/E

Junction Temperature

-65∞C to +150∞C

300∞C

-40∞C to +85∞C

-55∞C to +125∞C

+150∞C

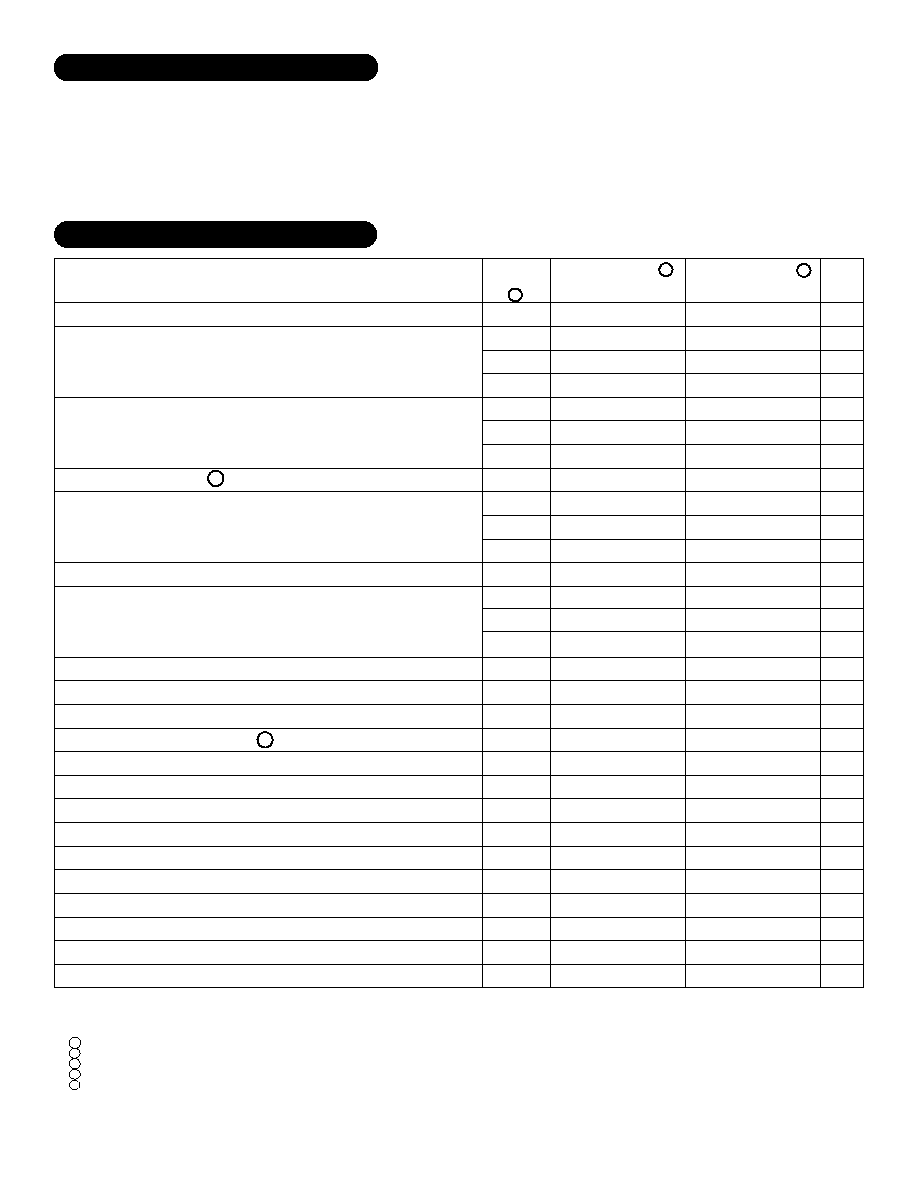

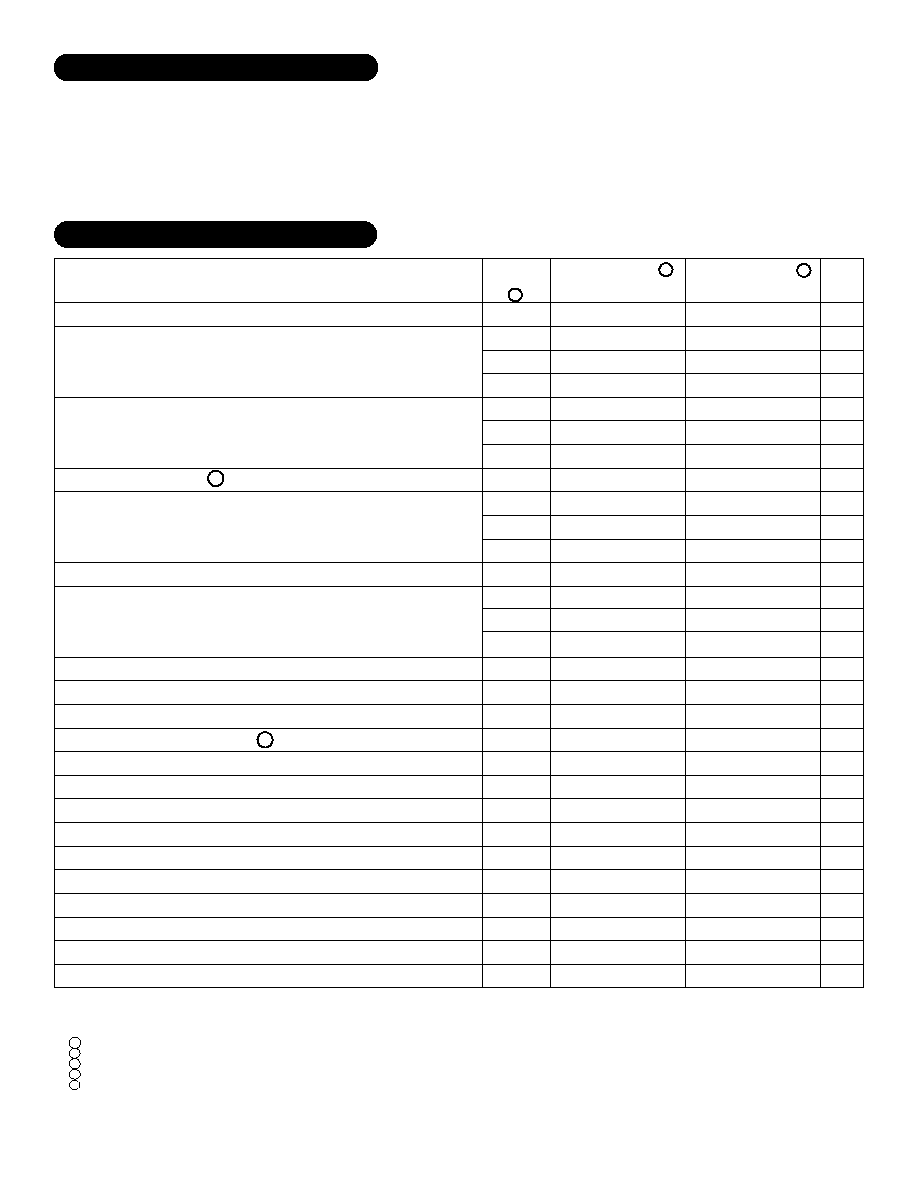

OUTPUT CHARACTERISTICS

VC-E On Voltage (Each IGBT)

Instantaneous Forward Voltage

(FRED Flyback Diode)

Reverse Recovery Time 1

Leakage Current

BIAS SUPPLY CHARACTERISTICS

Quiescent Bias Current

INPUT SIGNALS CHARACTERISTICS

Positive Trigger Threshold Voltage

Negative Trigger Threshold Voltage

SWITCHING CHARACTERISTICS 1

Upper Drive:

Turn-On Propagation Delay

Turn-Off Propagation Delay

Turn-On

Turn-Off

Lower Drive:

Turn-On Propagation Delay

Turn-Off Propagation Delay

Turn-On

Turn-Off

Subgroup 1,4

2,5

3,6

T

A

=T

C

=+25∞C

T

A

=T

C

=+125∞C

T

A

=T

C

=-55∞C

Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

Industrial grade and "E" suffix devices shall be tested to subgroups 1 and 4 unless otherwise specified.

Military grade devices ("H" suffix) shall be 100% tested to subgroups 1,2,3, and 4.

Subgroups 5 and 6 testing available upon request.

All Ratings: Tc = +25∞C Unless Otherwise Specified

High Voltage Supply

Logic Supply

Continuous Output Current

Peak Output Current

Thermal Resistance

(Output Switches) (Junction to Case)

V

+

V

CC

I

OUT

I

PK

JC

T

ST

T

LD

T

C

T

J

Parameters

Min.

-

-

-

-

-

-

-

-

-

-

-

-

-

2.2

-

-

-

-

-

-

-

-

-

Typ.

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

Min.

-

-

-

-

-

-

-

-

-

-

-

-

-

2.2

-

-

-

-

-

-

-

-

-

Typ.

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

Max.

2.2

-

-

1.7

-

-

180

400

-

-

TBD

-

-

-

0.8

TBD

TBD

45

350

TBD

TBD

45

350

MSK 4358 2

Max.

2.0

1.7

TBD

1.7

1.3

2.5

180

400

1.5

400

TBD

TBD

TBD

-

0.8

TBD

TBD

45

350

TBD

TBD

45

350

UNITS

V

V

V

V

V

V

nS

uA

mA

uA

mA

mA

mA

V

V

nS

nS

nS

nS

nS

nS

nS

nS

ELECTRICAL SPECIFICATIONS

ABSOLUTE MAXIMUM RATING

1

2

3

1

2

3

-

1

2

3

1

2

3

1,2,3

1,2,3

4

4

4

4

4

4

4

4

Group A

Subgroup

5

500V

18V

25A

60A

0.66∞C/W

MSK 4358H/E 3

1

2

3

4

5

I

C

=25A

I

D

=25A

I

D

=25A,

di

/

dt

=100A/uS,V

r

=350V

V

+

=500V

V

+

=400V

V

+

=500V

V

CC

=15V

Test Conditions

V

+

=270V, I

C

=25A

V

+

=270V, I

C

=25A

PRELIMINARY Rev. B 11/01

2

NOTES:

+15V - is the low voltage supply for all the internal logic and

isolated supplies which provide power to the gate drivers. A

0.1µF ceramic capacitor in parallel with a 22µF tantalum capaci-

tor is recommended for bypassing the low voltage supply to

GND.

GND - is the low voltage supply return for the +15V. All

bypassing of the +15V should return here. Since the output

section of the hybrid is completely isolated, there are no restric-

tions for potential differences between this GND and any hi-

voltage returns, up to 500V.

AHI,BHI,CHI - are the logic inputs for controlling the switching

of the corresponding hi-side bridge outputs. A logic high will

turn on the corresponding hi-side output. The input levels are

5V CMOS or TTL compatible. If one of these inputs are active

at the same time as the corresponding low-side bridge outputs,

neither output will be allowed to turn on until one of the inputs

is switched low. There will be a deadtime inserted before the

corresponding bridge output is switched in all cases. This pre-

vents simultaneous conduction of the output, shorting high

voltage supply and destroying the bridge.

ALO,BLO,CLO - are the logic inputs for controlling the switching

of the corresponding low-side bridge outputs. A logic high will

turn on the corresponding low-side output. The input levels are

5V CMOS or TTL compatible. If one of these inputs are active

at the same time as the corresponding hi-side bridge outputs,

neither output will be allowed to turn on until one of the inputs

is switched low. There will be a deadtime inserted before the

corresponding bridge output is switched in all cases. This pre-

vents simultaneous conduction of the output, shorting the high

voltage supply and destroying the bridge.

RESET - is an active low logic input for causing all switching to

cease. The input level is 5V CMOS or TTL compatible. Upon

releasing RESET, the outputs will resume after the dead time.

R/C - is the input pin for setting the deadtime of the bridge.

Connecting a resistor between this input and OSC OUT, and a

capacitor to ground will create the time for an internal oscillator.

OSC OUT - is a pin that brings the deadtime oscillator out to be

connected through the timing resistor to R/C. This is not an

output to be used externally, but just for the timing circuit.

AV+,BV+,CV+ - are pins for connecting the tops of each half

bridge to the high voltage supply. Each pin must be connected

individually, as there is no internal connection across the three

half bridges. Proper power supply bypassing must be connected

to these pins and the V- pins as close to the hybrid as possible

for proper filtering.

AV-,BV-,CV- - are pins for connecting the bottoms of each half

bridge to the high voltage supply return. Each pin must be

connected individually, as there is no internal connection across

the three half bridges. Proper power supply bypassing must be

connected to these pins and the V+ pins as close to the hybrid

as possible for proper filtering.

Aÿ, Bÿ, Cÿ - are the pins connecting the 3 phase bridge switch

outputs.

APPLICATION NOTES

DEADTIME SELECTION

MSK4358 PIN DESCRIPTION

The amount of deadtime required is based on the propagation

delay of the input to actual completion of switching of the

output transistors. Not taking all this into account can possi-

bly allow the opposite transistor in a half bridge to turn on

before the active transistor can turn off. Excessive current will

flow through the half bridge because this creates a momentary

short across the power supply.

Once all these factors are taken into account, the deadtime can

be determined. Allow sufficient safety facor for changes in

components over temperature, and variations from system to

system in production.

Deadtime is exactly 8 R/C clock periods. Use the formula:

Max. Clock = 8/Min. Deadtime

For clock operation below 1MHz:

Clock Frequency =

For clock operation above 1MHz:

Clock Frequency =

As an alternative, the R/C pin can be driven directly with an

HCMOS compatible clock up to 24MHz.

PRELIMINARY Rev. B 11/01

3

0.95

C

OSC

x R

OSC

0.95

C

OSC

(R

OSC

+ 30) + 3x 10

8

RSENSE+ - is the pin for connecting to the internal sense resistor.

It has a value of 0.010 ohms, 20 watts. AV-,BV- and CV- should

connect to this point for sensing the current at the bottom of the

bridge.

RSENSE- - is the pin for connecting the internal sense resistor to

the high voltage return.

RKELVIN+ - is the pin for connecting to the sense resistor +KELVIN

connection. This is on the same side of the resistor as RSENSE+.

RKELVIN- - is the pin for connecting to the sense resistor -KELVIN

connection. This is on the same side of the resistor as RSENSE-.

TYPICAL SYSTEM OPERATION

The MSK4358 is designed to be used with a +270 volt high voltage bus, +15 volt low power bus, and +5 volt logic signals.

Proper derating should be applied when designing the MSK4358 into a system. High frequency layout techniques with ground

planes on a printed circuit board is the only method that should be used for circuit construction. This will prevent pulse jitter caused

by excessive noise pickup on the current sense signal or the error amp signal.

Ground planes for the low power circuitry and high power circuitry should be kept separate. The two sections of the hybrid are

completely isolated, and can float relative to each other without referencing one to the other. An RC filter will filter out the current

spikes and keep the detected noise for that circuit down to a minimum.

The logic signals coming from the typical motor controller IC are set up for driving N channel low side and P channel high side

switches directly, and are usually 15 volt levels. Provision should be made for getting 5 volt logic signals to the MSK4358 of the

correct assertion levels. Typically, the low side signals out of the controller are high active and the high side are low active.

Inverters are shown in the system schematic for the high side controller output.

PRELIMINARY Rev. B 11/01

5