NT6828

I

2

C Bus Controlled On-Screen Display

1

V2.1

Features

T

I

2

C Bus Interface with Slave Address $7A (Receiver

Only)

T

Horizontal Frequency Range: 30KHz ~ 120KHz

T

Flexible Display Resolution: up to 1524 dots per row

T

Internal PLL Generating a Stable and Wide-Ranged

System Clock (92.2 MHz)

T

OSD Screen Comprising of Character Arrays of 15

Rows by 30 Columns

T

12 X 18 Dot Matrix Per Character

T

Total of 256 Fonts Including 248 ROM Fonts and 8

RAM Fonts

T

Programmable Vertical and Horizontal Position

Adjustment for OSD Display Position

T

8-Color Selection for Each Character and 8-Color

Control on Each Row with Overlapped by Windows

T

Character Blinking, Shadowing & Bordering Display

Effects

T

Double Character Height and Width for Each Row

T

Programmable Height of Characters Display

T

Row To Row Spacing Control

T

Four Overlapping and Programmable Windows with 8-

Color Control

T

Hsync & Vsync Input Polarity Selectable

T

8 Channels PWM DAC with 8 bits resolution & Open-

Drain Output Structure

T

16 DIP and 24 Skinny DIP packages

General Description

NT6828 is designed for displaying symbols and

characters onto a CRT monitor. Its operation is controlled

by the micro-controller with I2C bus interface. By sending

the proper data and commands to NT6828, it can carry

out the full screen display automatically while the time

base is generated by the on-chip PLL circuit. There are

many functions provided on this chip to fully support

numerous user applications. These functions are:

adjustment of OSD windows position, built-in ROM &

RAM fonts, variable character height with row-to-row

spacing adjustment, 8 color selections for each character,

double height/width controls for each row, four available

overlapping windows with color & size controls, as well as

other I/O interfaces to compliment an external video

chipset.

NT6828 provides eight optional PWM channels with 8-bit

resolution for external digital to analog control.

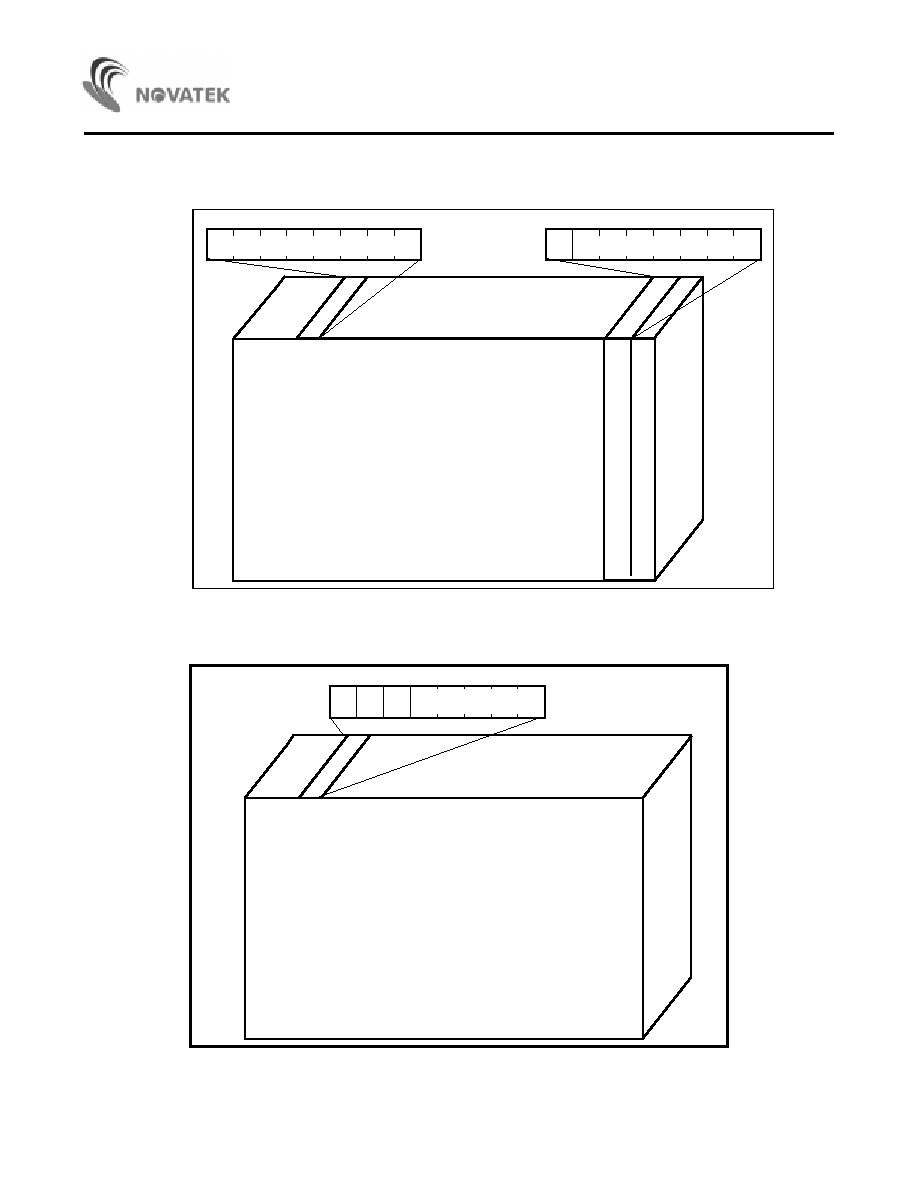

Pin Configurations

A G N D

V C O

A V C C

H F L B

N . C .

S D A

S C L

D V C C

P W M / H F T O N

F B K G

G

B

R

D G N D

V F L B

NT6828

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

R P

16 DIP

24 Skinny DIP

NT6828K

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

1 3

1 4

1 5

1 6

D V C C

P W M / H F T O N

F B K G

G

B

R

D G N D

V F L B

P W M 4

P W M 6

P W M 7

P W M 5

A G N D

V C O

A V

DD

H F L B

N . C .

S D A

S C L

R P

P W M 0

P W M 1

P W M 2

P W M 3

NT6828

3

Pin Description

Pin No.

16 Pin

24 Pin

Designation

I/O/P/R

Description

1

1

AGND

P

Analog Ground

2

2

VCO

-

Voltage I/P to Control Oscillator

3

3

RP

-

Bias Resistor. (To be used as a bias internal VCO to

resonate at the specific range of pixel clock)

4

4

AVCC

P

Analog Power Supply (5V Typ.)

5

5

HFLB

I

Horizontal Fly-back Input (Schmitt Trigger Buffer)

6

6

N.C.

-

-

7

7

SDA

I

SDA Pin Of I

2

C Bus (Schmitt Trigger Buffer) with internal

100K ohm pulled-high resistance

8

8

SCL

I

SCL Pin Of I

2

C Bus (Schmitt Trigger Buffer) with internal

100K ohm pulled-high resistance

9

PWM0

O

5V PWM Channel 0. Open-drain output structure

10

PWM1

O

5V PWM Channel 1. Open-drain output structure

11

PWM2

O

5V PWM Channel 2. Open-drain output structure

12

PWM3

O

5V PWM Channel 3. Open-drain output structure

12

PWM4

O

5V PWM Channel 4. Open-drain output structure

14

PWM5

O

5V PWM Channel 5. Open-drain output structure

15

PWM6

O

5V PWM Channel 6. Open-drain output structure

16

PWM7

O

5V PWM Channel 7. Open-drain output structure

9

17

DVCC

P

Digital Power Supply (5V Typ.)

10

18

VFLB

I

Vertical Fly-back Input (Schmitt Trigger Buffer)

11

19

PWM/

HFTON

O

PWM output or gain controlled of R,G,B channels.

12

20

FBKG

O

Fast Blanking Output. (To be used as switching signal for the

R,G,B OSD video signals.)

13

21

B

O

Blue Color Output with Push-Pull Output Structure

14

22

G

O

Green Color Output with Push-Pull Output Structure

15

23

R

O

Red Color Output with Push-Pull Output Structure

16

24

DGND

P

Digital Ground