| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 100352DC | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

100352

Low Power 8-Bit Buffer with Cut-Off Drivers

General Description

The 100352 contains an 8-bit buffer, individual inputs (Dn),

outputs (Qn), and a data output enable pin (OEN). A Q out-

put follows its D input when the OEN pin is LOW. A HIGH on

OEN holds the outputs in a cut-off state. The cut-off state is

designed to be more negative than a normal ECL LOW level.

This allows the output emitter-followers to turn off when the

termination supply is -2.0V, presenting a high impedance to

the data bus. This high impedance reduces termination

power and prevents loss of low state noise margin when sev-

eral loads share the bus.

The 100352 outputs are designed to drive a doubly termi-

nated 50

transmission line (25

load impedance). All in-

puts have 50 k

pull-down resistors.

Features

n

Cut-off drivers

n

Drives 25

load

n

Low power operation

n

2000V ESD protection

n

Voltage compensated operating range = -4.2V to -5.7V

n

Available to industrial grade temperature range

n

Available to MIL-STD-883

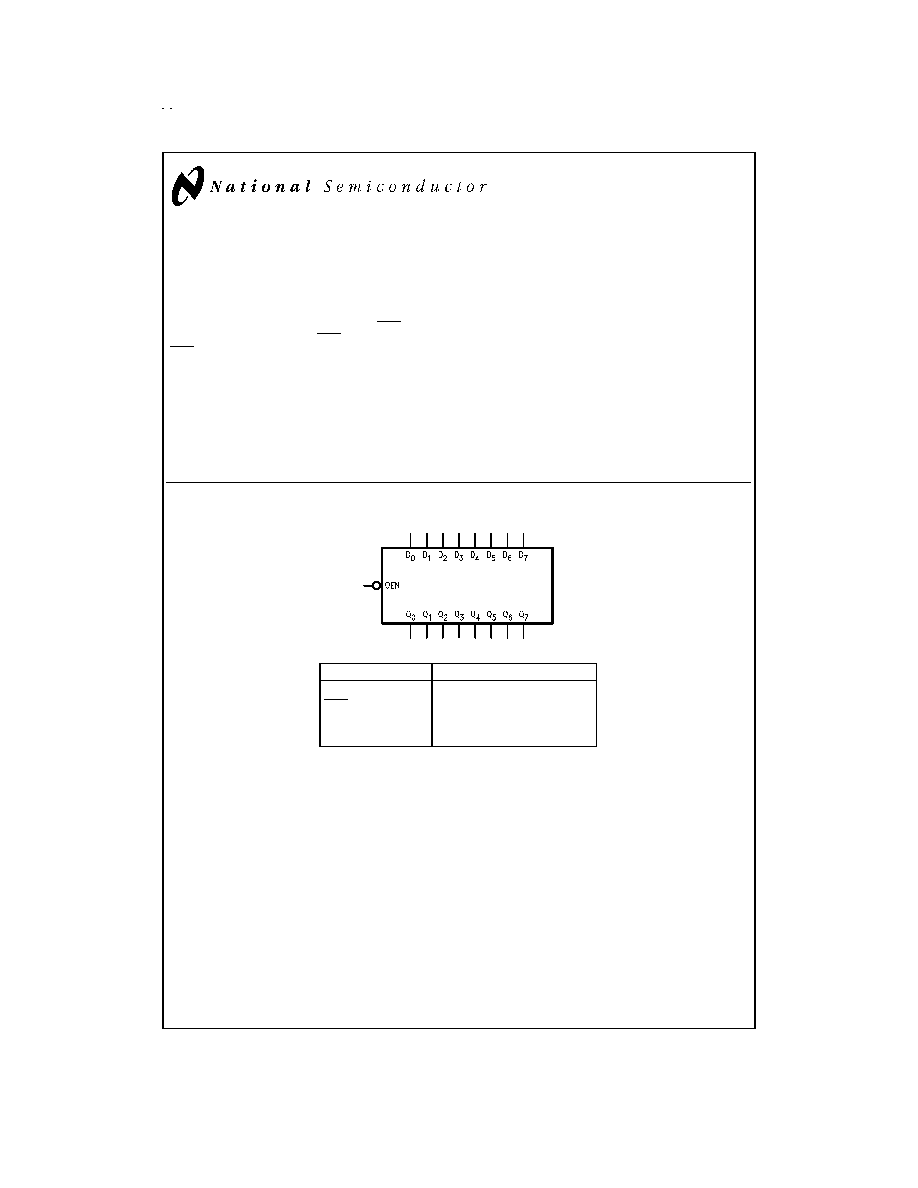

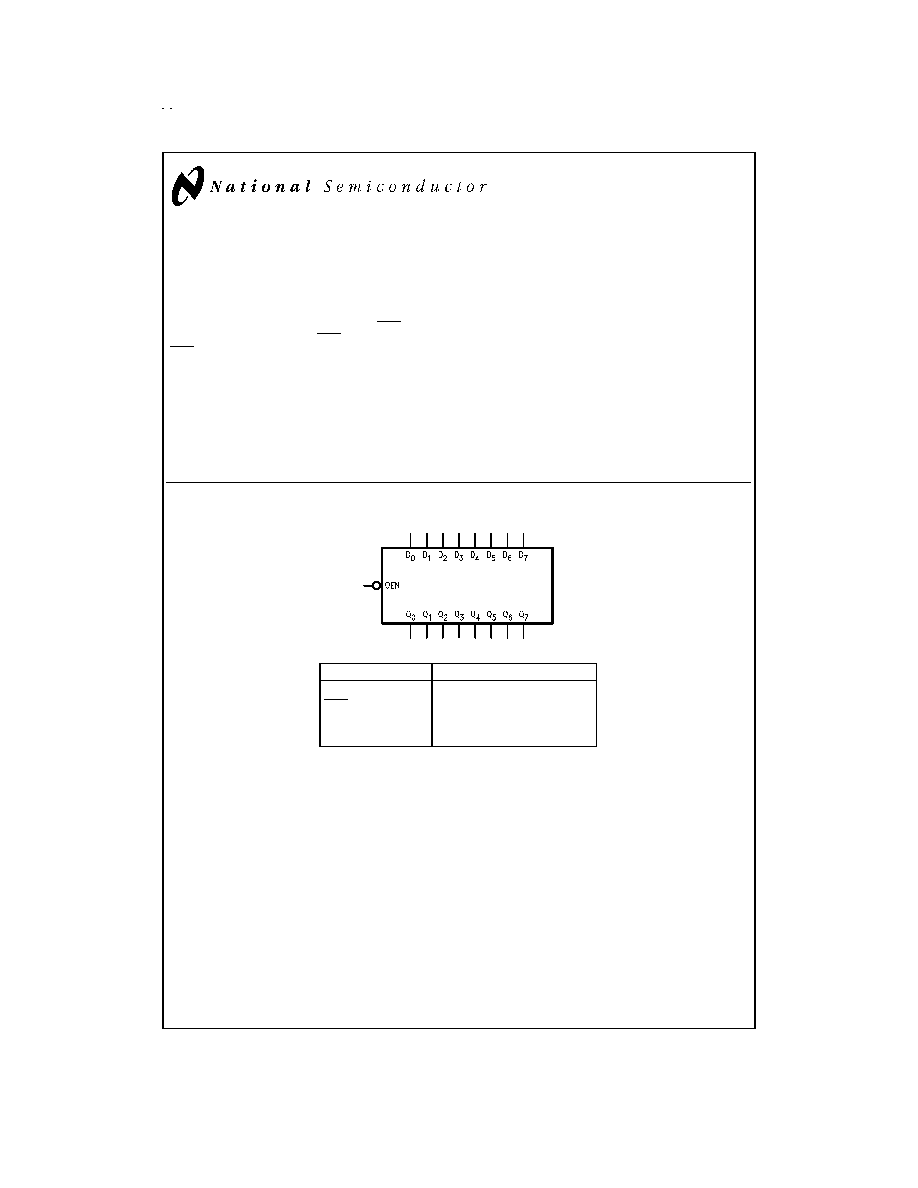

Logic Symbol

Pin Names

Description

D

0

≠D

7

Data Inputs

OEN

Output Enable Input

Q

0

≠Q

7

Data Outputs

NC

No Connect

DS100296-1

August 1998

100352

Low

Power

8-Bit

Buffer

with

Cut-Off

Drivers

© 1998 National Semiconductor Corporation

DS100296

www.national.com

Connection Diagrams

24-Pin DIP

DS100296-2

24-Pin Quad Cerpak

DS100296-3

www.national.com

2

Logic Diagram

Truth Table

Inputs

Outputs

Dn

OEN

Qn

L

L

L

H

L

H

X

H

Cutoff

H = HIGH Voltage Level

L = LOW Voltage Level

Cutoff = Lower-than-LOW State

X = Don't Care

DS100296-5

www.national.com

3

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Above which the useful life may be impaired

Storage Temperature (T

STG

)

-65∞C to +150∞C

Maximum Junction Temperature (T

J

)

Ceramic

+175∞C

V

EE

Pin Potential to

Ground Pin

-7.0V to +0.5V

Input Voltage (DC)

V

EE

to +0.5V

Output Current (DC Output HIGH)

-100 mA

ESD (Note 2)

2000V

Recommended Operating

Conditions

Case Temperature (T

C

)

Military

-55∞C to +125∞C

Supply Voltage (V

EE

)

-5.7V to -4.2V

Note 1: Absolute maximum ratings are those values beyond which the de-

vice may be damaged or have its useful life impaired. Functional operation

under these conditions is not implied.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

Military Version

DC Electrical Characteristics

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND, T

C

= -55∞C to +125∞C

Symbol

Parameter

Min

Max

Units

T

C

Conditions

Notes

V

OH

Output HIGH Voltage

-1025

-870

mV

0∞C to +125∞C

V

IN

= V

IH(Max)

or V

IL(Min)

Loading

with

25

to

-2.0V

(Notes 3,

4, 5)

-1085

-870

mV

-55∞C

V

OL

Output LOW Voltage

-1830

-1620

mV

0∞C to +125∞C

-1830

-1555

mV

-55∞C

V

OHC

Output HIGH Voltage

-1035

mV

0∞C to +125∞C

V

IN

= V

IH(Min)

or V

IL(Max)

Loading

with

25

to

-2.0V

(Notes 3,

4, 5)

-1085

mV

-55∞C

V

OLC

Output LOW Voltage

-1610

mV

0∞C to +125∞C

-1555

mV

-55∞C

V

OLZ

Cut-Off LOW Voltage

-1950

mV

0∞C to +125∞C

V

IN

= V

IH(Min),

or

V

IL(Max)

OEN

=HIGH

(Notes 3,

4, 5)

-1850

-55∞C

V

IH

Input HIGH Voltage

-1165

-870

mV

-55∞C to +125∞C

Guaranteed HIGH signal

1, 2, 3, 4

for All inputs

V

IL

Input LOW Voltage

-1830

-1475

mV

-55∞C to +125∞C

Guaranteed LOW signal

for All inputs

(Notes 3,

4, 5, 6)

I

IL

Input LOW Current

0.50

µA

-55∞C to +125∞C

V

EE

= 4.2V

(Notes 3,

4, 5)

V

IN

= V

IL(Min)

I

IH

Input HIGH Current

240

µA

0∞C to + 125∞C

V

EE

= -5.7V

(Notes 3,

4, 5)

340

µA

-55∞C

V

IN

= V

IH(Max)

I

EE

Power Supply Current

-55∞C to +125∞C

Inputs Open

(Notes 3,

4, 5)

-145

-55

mA

V

EE

= -4.2V to -4.8V

-150

V

EE

= -4.2V to -5.7V

Note 3: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55∞C), then testing immediately

without allowing for the junction temperature to stabilize due to heat dissipation after power-up. This provides "cold start" specs which can be considered a worst case

condition at cold temperatures.

Note 4: Screen tested 100% on each device at -55∞C, +25∞C, and +125∞C, Subgroups 1, 2, 3, 7, and 8.

Note 5: Sample tested (Method 5005, Table I) on each manufactured lot at -55∞C, +25∞C, and +125∞C, Subgroups A1, 2, 3, 7, and 8.

Note 6: Guaranteed by applying specified input condition and testing V

OH

/V

OL

.

AC Electrical Characteristics

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND

Symbol

Parameter

T

C

= -55∞C

T

C

= +25∞C

T

C

+125∞C

Units

Conditions

Notes

Min

Max

Min

Max

Min

Max

t

PLH

Propagation Delay

0.30

2.60

0.50

2.40

0.50

2.70

ns

Figures 1, 2

(Notes 7,

8, 10, 11)

t

PHL

Dn to Output

t

PZH

Propagation Delay

1.20

4.40

1.40

4.20

1.20

4.40

ns

Figures 1, 2

(Notes 7,

8, 9, 11)

t

PHZ

OEN to Output

0.70

3.00

0.70

2.80

0.70

3.20

www.national.com

4

AC Electrical Characteristics

(Continued)

V

EE

= -4.2V to -5.7V, V

CC

= V

CCA

= GND

Symbol

Parameter

T

C

= -55∞C

T

C

= +25∞C

T

C

+125∞C

Units

Conditions

Notes

Min

Max

Min

Max

Min

Max

t

TLH

Transition Time

0.40

2.50

0.40

2.40

0.40

2.70

ns

Figures 1, 2

(Note 10)

t

THL

20% to 80%, 80% to 20%

Note 7: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55∞C), then testing immediately

after power-up. This provides "cold start" specs which can be considered a worst case condition at cold temperatures.

Note 8: Screen tested 100% on each device at +25∞C temperature only, Subgroup A9.

Note 9: Sample tested (Method 5005, Table I) on each manufactured lot at +25∞C, Subgroup A9, and at +125∞C and -55∞C temperatures, Subgroups A10 and A11.

Note 10: Not tested at +25∞C, +125∞C, and -55∞C temperature (design characterization data).

Note 11: The propagation delay specified is for single output switching. Delays may vary up to 300 ps with multiple outputs switching.

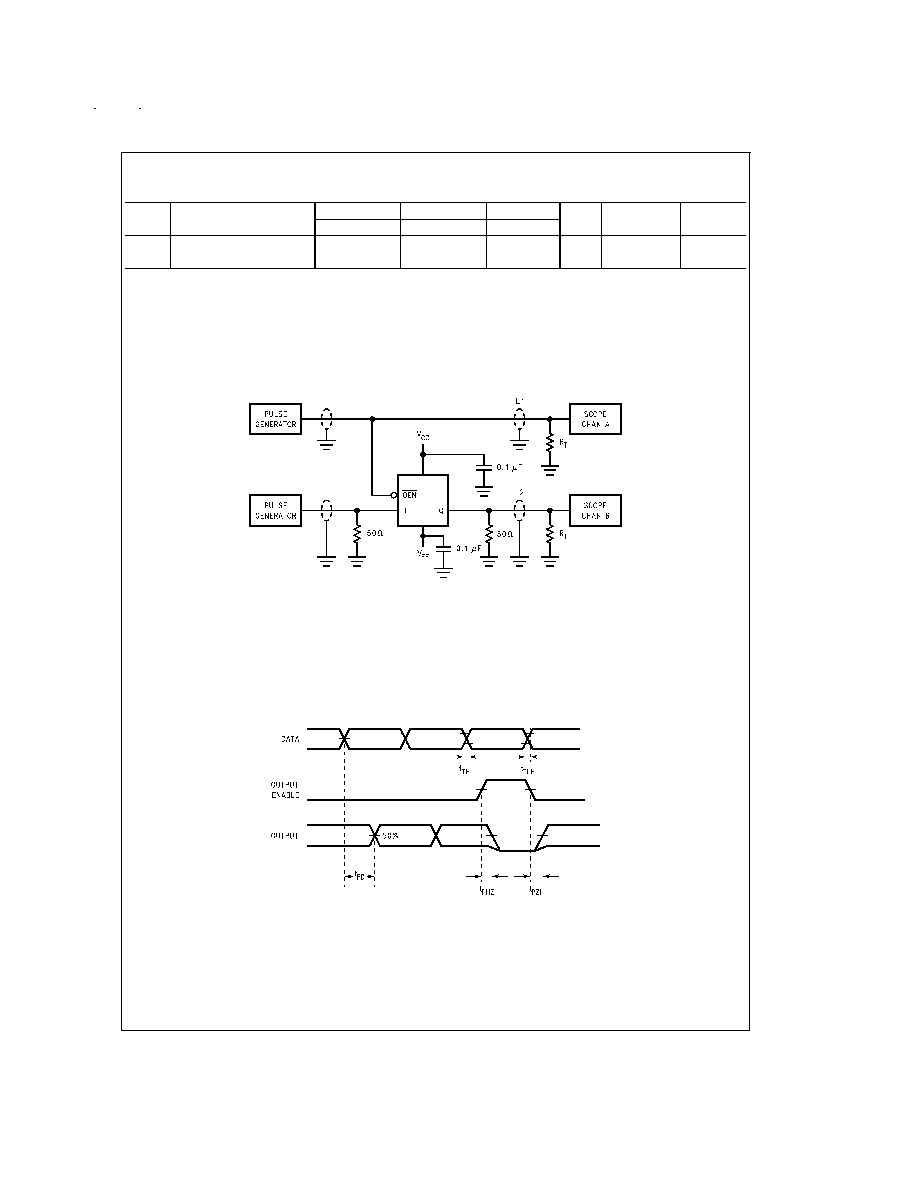

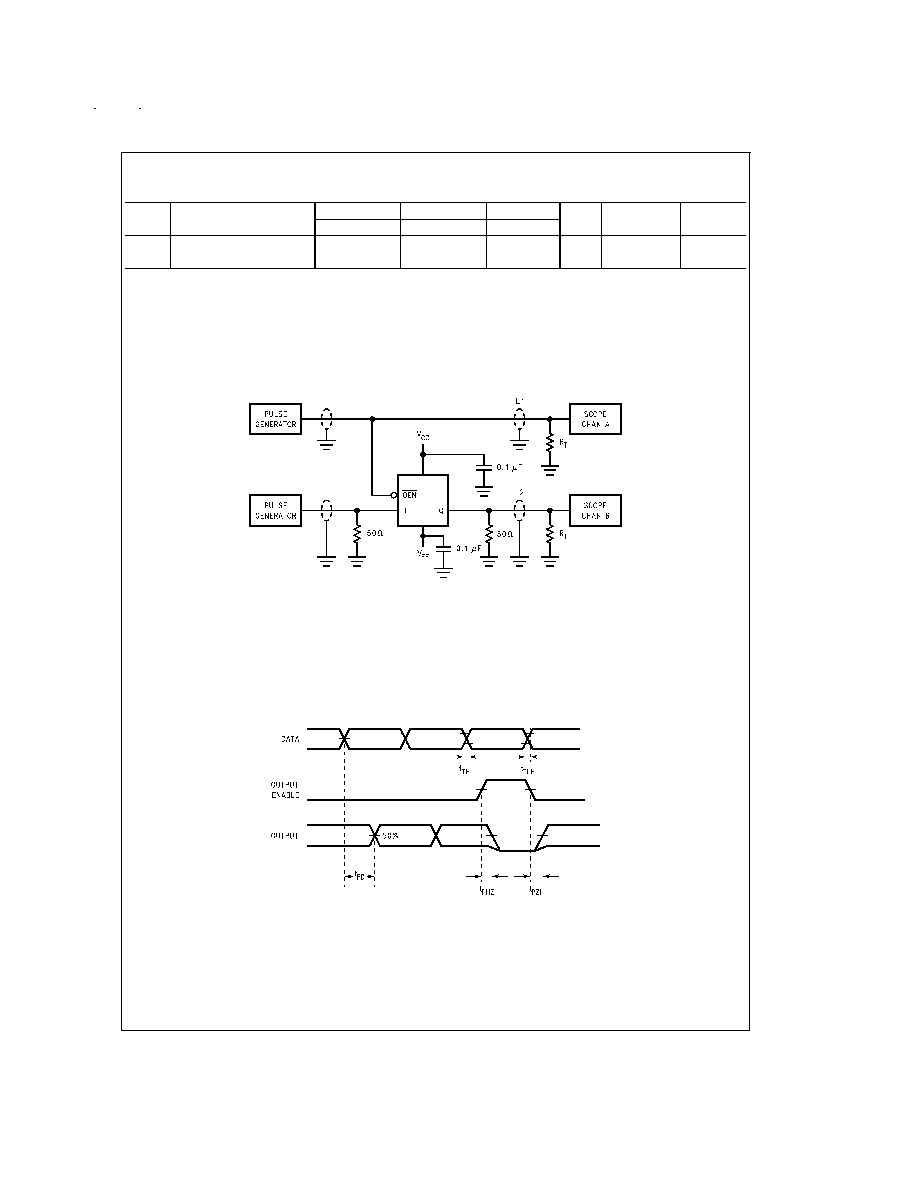

Test Circuitry

Switching Waveforms

DS100296-6

Notes:

V

CC

, V

CCA

= +2V, V

EE

= -2.5V

L1 and L2 = equal length 50

impedance lines

R

T

= 50

terminator internal to scope

Decoupling 0.1 µF from GND to V

CC

and V

EE

All unused outputs are loaded with 25

to GND

C

L

= Fixture and stray capacitance

3 pF

FIGURE 1. AC Test Circuit

DS100296-7

Note:

The output AC measurement point for cut-off propagation delay

testing = the 50% voltage point between active V

OL

and V

OH

.

FIGURE 2. Propagation Delay, Cut-Off and Transition Times

www.national.com

5