| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 16MV680WG | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- LM2727/LM2737

- General Description

- Features

- Applications

- Typical Application

- Connection Diagram

- Pin Description

- Absolute Maximum Ratings

- Operating Ratings

- Electrical Characteristics

- Typical Performance Characteristics

- Block Diagram

- Application Information

- Example Circuits

- FIGURE 2. 5V-16V to 3.3V, 10A, 300kHz

- FIGURE 3. 5V to 1.2V, 10A, 300kHz

- FIGURE 4. 5V to 1.8V, 3A, 600kHz

- FIGURE 5. 3.3V to 0.8V, 5A, 500kHz

- FIGURE 6. 1.8V and 3.3V, 1A, 1.4MHz, Simultaneous

- FIGURE 7. 12V Unregulated to 3.3V, 3A, 750kHz

- FIGURE 8. 12V to 5V, 1.8A, 100kHz

- TABLE 1. Bill of Materials for Typical Application Circuit

- TABLE 2. Bill of Materials for Circuit of (Identical to BOM for 1.5V except as noted below)

- TABLE 3. Bill of Materials for Circuit of

- TABLE 4. Bill of Materials for Circuit of

- TABLE 5. Bill of Materials for Circuit of

- TABLE 6. Bill of Materials for Circuit of

- TABLE 7. Bill of Materials for 3.3V Circuit of (Identical to BOM for 1.8V except as noted below)

- TABLE 8. Bill of Materials for Circuit of

- TABLE 9. Bill of Materials for Circuit of

- Physical Dimensions

LM2727/LM2737

N-Channel FET Synchronous Buck Regulator Controller

for Low Output Voltages

General Description

The LM2727 and LM2737 are high-speed, synchronous,

switching regulator controllers. They are intended to control

currents of 0.7A to 20A with up to 95% conversion efficien-

cies. The LM2727 employs output over-voltage and under-

voltage latch-off. For applications where latch-off is not de-

sired, the LM2737 can be used. Power up and down

sequencing is achieved with the power-good flag, adjustable

soft-start and output enable features. The LM2737 and

LM2737 operate from a low-current 5V bias and can convert

from a 2.2V to 16V power rail. Both parts utilize a fixed-

frequency, voltage-mode, PWM control architecture and the

switching frequency is adjustable from 50kHz to 2MHz by

adjusting the value of an external resistor. Current limit is

achieved by monitoring the voltage drop across the on-

resistance of the low-side MOSFET, which enhances low

duty-cycle operation. The wide range of operating frequen-

cies gives the power supply designer the flexibility to fine-

tune component size, cost, noise and efficiency. The adap-

tive, non-overlapping MOSFET gate-drivers and high-side

bootstrap structure helps to further maximize efficiency. The

high-side power FET drain voltage can be from 2.2V to 16V

and the output voltage is adjustable down to 0.6V.

Features

n

Input power from 2.2V to 16V

n

Output voltage adjustable down to 0.6V

n

Power Good flag, adjustable soft-start and output enable

for easy power sequencing

n

Output over-voltage and under-voltage latch-off

(LM2727)

n

Output over-voltage and under-voltage flag (LM2737)

n

Reference Accuracy: 1.5% (0∞C - 125∞C)

n

Current limit without sense resistor

n

Soft start

n

Switching frequency from 50 kHz to 2 MHz

n

TSSOP-14 package

Applications

n

Cable Modems

n

Set-Top Boxes/ Home Gateways

n

DDR Core Power

n

High-Efficiency Distributed Power

n

Local Regulation of Core Power

Typical Application

20049410

June 2003

LM2727/LM2737

N-Channel

FET

Synchronous

Buck

Regulator

Controller

for

Low

Output

V

oltages

© 2003 National Semiconductor Corporation

DS200494

www.national.com

Connection Diagram

20049411

14-Lead Plastic TSSOP

JA

= 155∞C/W

NS Package Number MTC14

Pin Description

BOOT (Pin 1) - Supply rail for the N-channel MOSFET gate

drive. The voltage should be at least one gate threshold

above the regulator input voltage to properly turn on the

high-side N-FET.

LG (Pin 2) - Gate drive for the low-side N-channel MOSFET.

This signal is interlocked with HG to avoid shoot-through

problems.

PGND (Pins 3, 13) - Ground for FET drive circuitry. It should

be connected to system ground.

SGND (Pin 4) - Ground for signal level circuitry. It should be

connected to system ground.

V

CC

(Pin 5) - Supply rail for the controller.

PWGD (Pin 6) - Power Good. This is an open drain output.

The pin is pulled low when the chip is in UVP, OVP, or UVLO

mode. During normal operation, this pin is connected to V

CC

or other voltage source through a pull-up resistor.

ISEN (Pin 7) - Current limit threshold setting. This sources a

fixed 50µA current. A resistor of appropriate value should be

connected between this pin and the drain of the low-side

FET.

EAO (Pin 8) - Output of the error amplifier. The voltage level

on this pin is compared with an internally generated ramp

signal to determine the duty cycle. This pin is necessary for

compensating the control loop.

SS (Pin 9) - Soft start pin. A capacitor connected between

this pin and ground sets the speed at which the output

voltage ramps up. Larger capacitor value results in slower

output voltage ramp but also lower inrush current.

FB (Pin 10) - This is the inverting input of the error amplifier,

which is used for sensing the output voltage and compen-

sating the control loop.

FREQ (Pin 11) - The switching frequency is set by connect-

ing a resistor between this pin and ground.

SD (Pin 12) - IC Logic Shutdown. When this pin is pulled low

the chip turns off the high side switch and turns on the low

side switch. While this pin is low, the IC will not start up. An

internal 20µA pull-up connects this pin to V

CC

.

HG (Pin 14) - Gate drive for the high-side N-channel MOS-

FET. This signal is interlocked with LG to avoid shoot-

through problems.

LM2727/LM2737

www.national.com

2

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

V

CC

7V

BOOTV

21V

Junction Temperature

150∞C

Storage Temperature

-65∞C to 150∞C

Soldering Information

Lead Temperature

(soldering, 10sec)

260∞C

Infrared or Convection (20sec)

235∞C

ESD Rating

2 kV

Operating Ratings

Supply Voltage (V

CC

)

4.5V to 5.5V

Junction Temperature Range

-40∞C to +125∞C

Thermal Resistance (

JA

)

155∞C/W

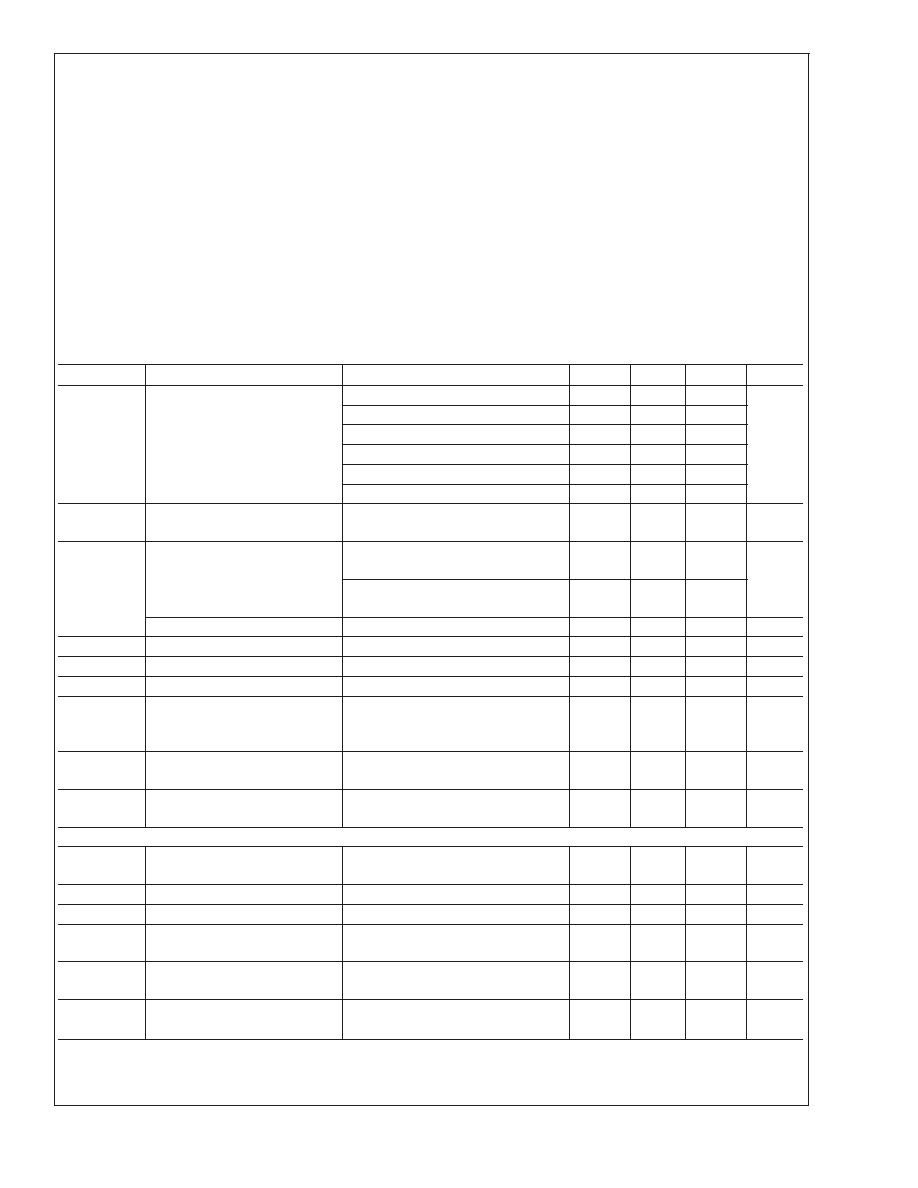

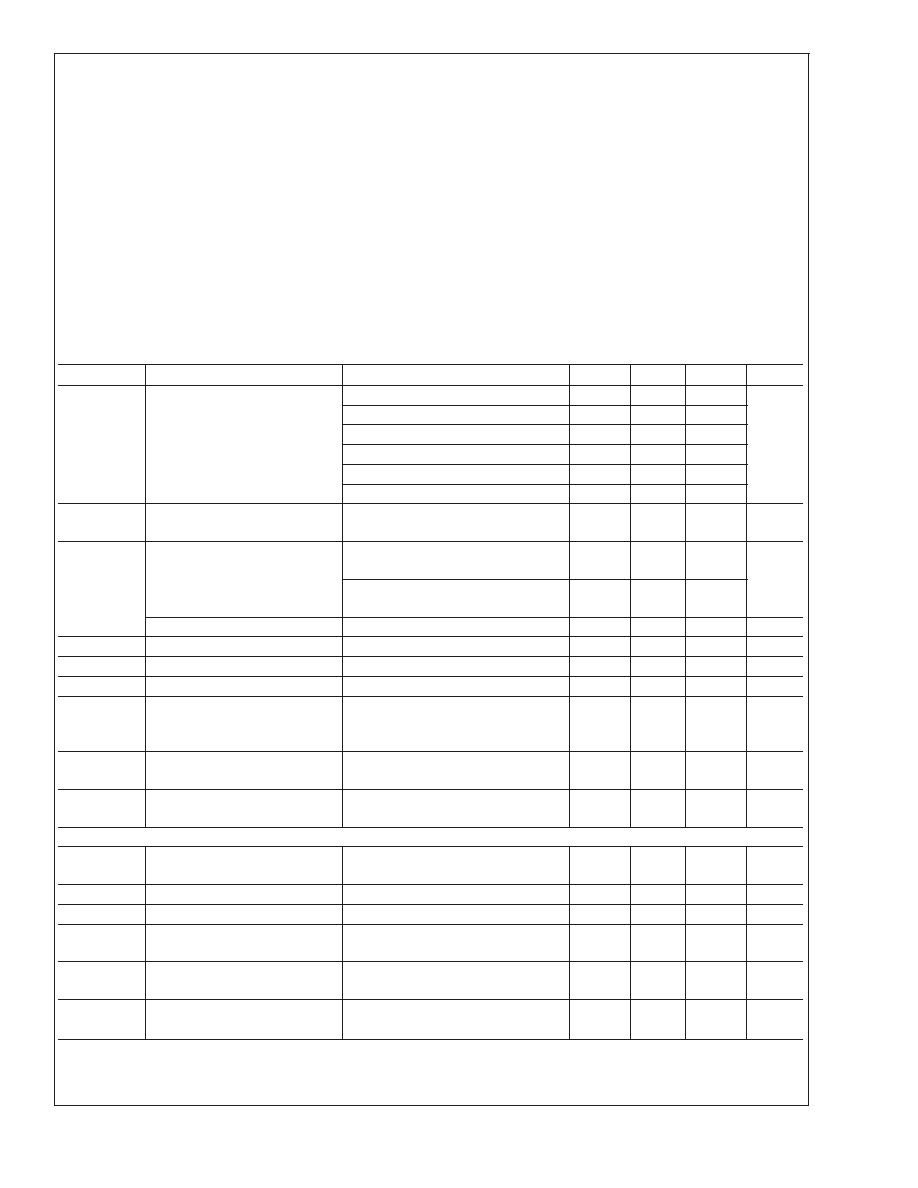

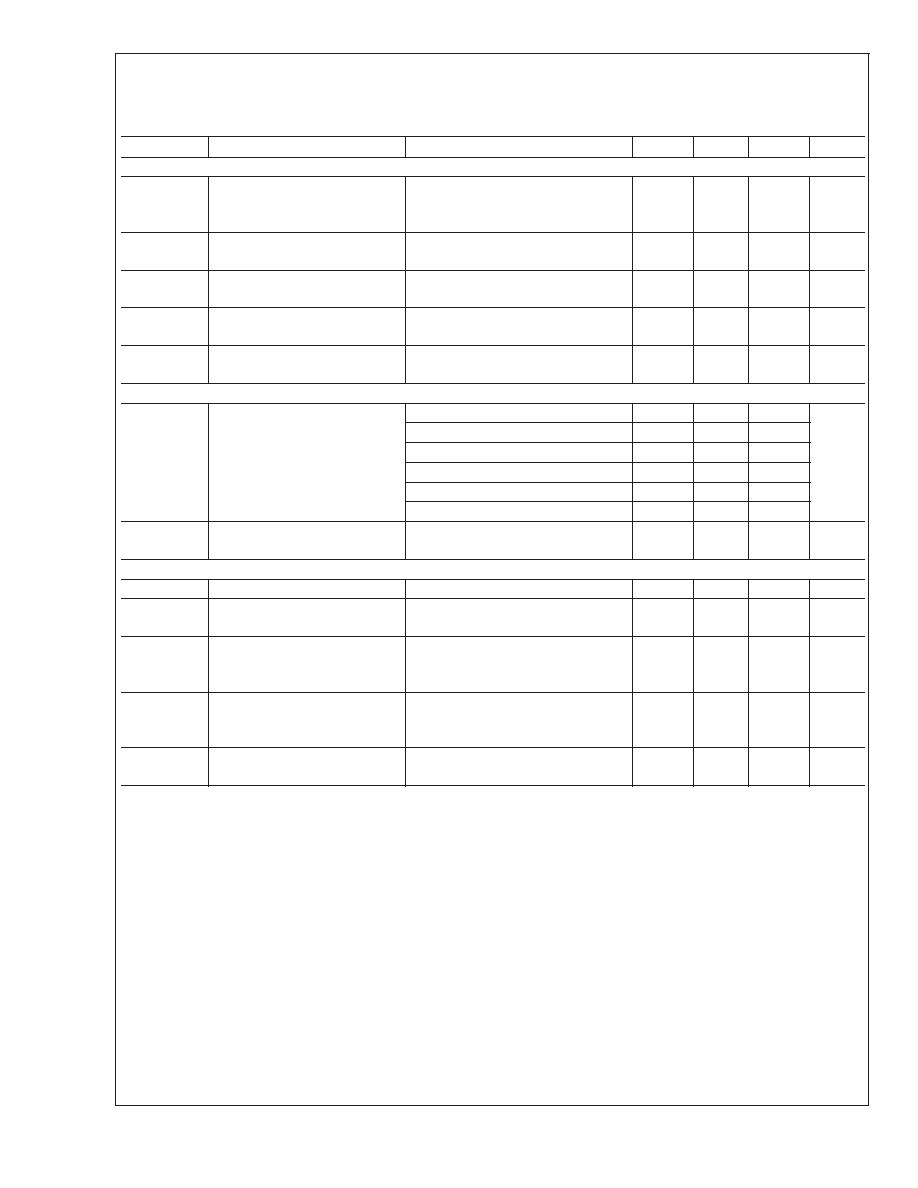

Electrical Characteristics

V

CC

= 5V unless otherwise indicated. Typicals and limits appearing in plain type apply for T

A

=T

J

=+25∞C. Limits appearing in

boldface type apply over full Operating Temperature Range. Datasheet min/max specification limits are guaranteed by design,

test, or statistical analysis.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

V

FB_ADJ

FB Pin Voltage

V

CC

= 4.5V, 0∞C to +125∞C

0.591

0.6

0.609

V

V

CC

= 5V, 0∞C to +125∞C

0.591

0.6

0.609

V

CC

= 5.5V, 0∞C to +125∞C

0.591

0.6

0.609

V

CC

= 4.5V, -40∞C to +125∞C

0.589

0.6

0.609

V

CC

= 5V, -40∞C to +125∞C

0.589

0.6

0.609

V

CC

= 5.5V, -40∞C to +125∞C

0.589

0.6

0.609

V

ON

UVLO Thresholds

Rising

Falling

4.2

3.6

V

I

Q-V5

Operating V

CC

Current

SD = 5V, FB = 0.55V

Fsw = 600kHz

1

1.5

2

mA

SD = 5V, FB = 0.65V

Fsw = 600kHz

0.8

1.7

2.2

Shutdown V

CC

Current

SD = 0V

0.15

0.4

0.7

mA

t

PWGD1

PWGD Pin Response Time

FB Voltage Going Up

6

µs

t

PWGD2

PWGD Pin Response Time

FB Voltage Going Down

6

µs

I

SD

SD Pin Internal Pull-up Current

20

µA

I

SS-ON

SS Pin Source Current

SS Voltage = 2.5V

0∞C to +125∞C

-40∞C to +125∞C

8

5

11

11

15

15

µA

I

SS-OC

SS Pin Sink Current During Over

Current

SS Voltage = 2.5V

95

µA

I

SEN-TH

I

SEN

Pin Source Current Trip

Point

0∞C to +125∞C

-40∞C to +125∞C

35

28

50

50

65

65

µA

ERROR AMPLIFIER

GBW

Error Amplifier Unity Gain

Bandwidth

5

MHz

G

Error Amplifier DC Gain

60

dB

SR

Error Amplifier Slew Rate

6

V/µA

I

FB

FB Pin Bias Current

FB = 0.55V

FB = 0.65V

0

0

15

30

100

155

nA

I

EAO

EAO Pin Current Sourcing and

Sinking

V

EAO

= 2.5, FB = 0.55V

V

EAO

= 2.5, FB = 0.65V

2.8

0.8

mA

V

EA

Error Amplifier Maximum Swing

Minimum

Maximum

1.2

3.2

V

LM2727/LM2737

www.national.com

3

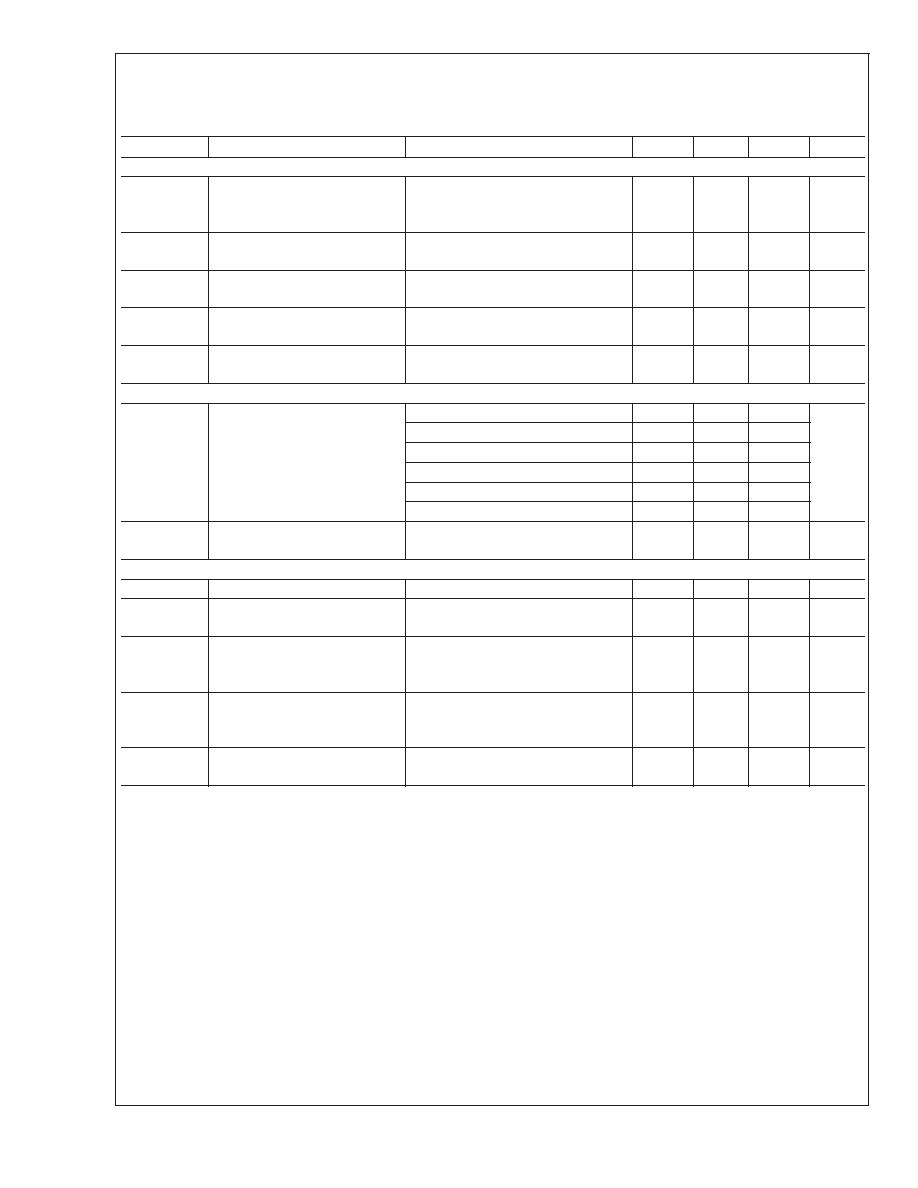

Electrical Characteristics

(Continued)

V

CC

= 5V unless otherwise indicated. Typicals and limits appearing in plain type apply for T

A

=T

J

=+25∞C. Limits appearing in

boldface type apply over full Operating Temperature Range. Datasheet min/max specification limits are guaranteed by design,

test, or statistical analysis.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

GATE DRIVE

I

Q-BOOT

BOOT Pin Quiescent Current

BOOTV = 12V, EN = 0

0∞C to +125∞C

-40∞C to +125∞C

95

95

160

215

µA

R

DS1

Top FET Driver Pull-Up ON

resistance

BOOT-SW = 5V

@

350mA

3

R

DS2

Top FET Driver Pull-Down ON

resistance

BOOT-SW = 5V

@

350mA

2

R

DS3

Bottom FET Driver Pull-Up ON

resistance

BOOT-SW = 5V

@

350mA

3

R

DS4

Bottom FET Driver Pull-Down

ON resistance

BOOT-SW = 5V

@

350mA

2

OSCILLATOR

f

OSC

PWM Frequency

R

FADJ

= 590k

50

kHz

R

FADJ

= 88.7k

300

R

FADJ

= 42.2k

, 0∞C to +125∞C

500

600

700

R

FADJ

= 42.2k

, -40∞C to +125∞C

490

600

700

R

FADJ

= 17.4k

1400

R

FADJ

= 11.3k

2000

D

Max Duty Cycle

f

PWM

= 300kHz

f

PWM

= 600kHz

90

88

%

LOGIC INPUTS AND OUTPUTS

V

SD-IH

SD Pin Logic High Trip Point

2.6

3.5

V

V

SD-IL

SD Pin Logic Low Trip Point

0∞C to +125∞C

-40∞C to +125∞C

1.3

1.25

1.6

1.6

V

V

PWGD-TH-LO

PWGD Pin Trip Points

FB Voltage Going Down

0∞C to +125∞C

-40∞C to +125∞C

0.413

0.410

0.430

0.430

0.446

0.446

V

V

PWGD-TH-HI

PWGD Pin Trip Points

FB Voltage Going Up

0∞C to +125∞C

-40∞C to +125∞C

0.691

0.688

0.710

0.710

0.734

0.734

V

V

PWGD-HYS

PWGD Hysteresis (LM2737 only) FB Voltage Going Down FB Voltage

Going Up

35

110

mV

Note 1: Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device

operates correctly. Opearting Ratings do not imply guaranteed performance limits.

Note 2: The human body model is a 100pF capacitor discharged through a 1.5k resistor into each pin.

LM2727/LM2737

www.national.com

4

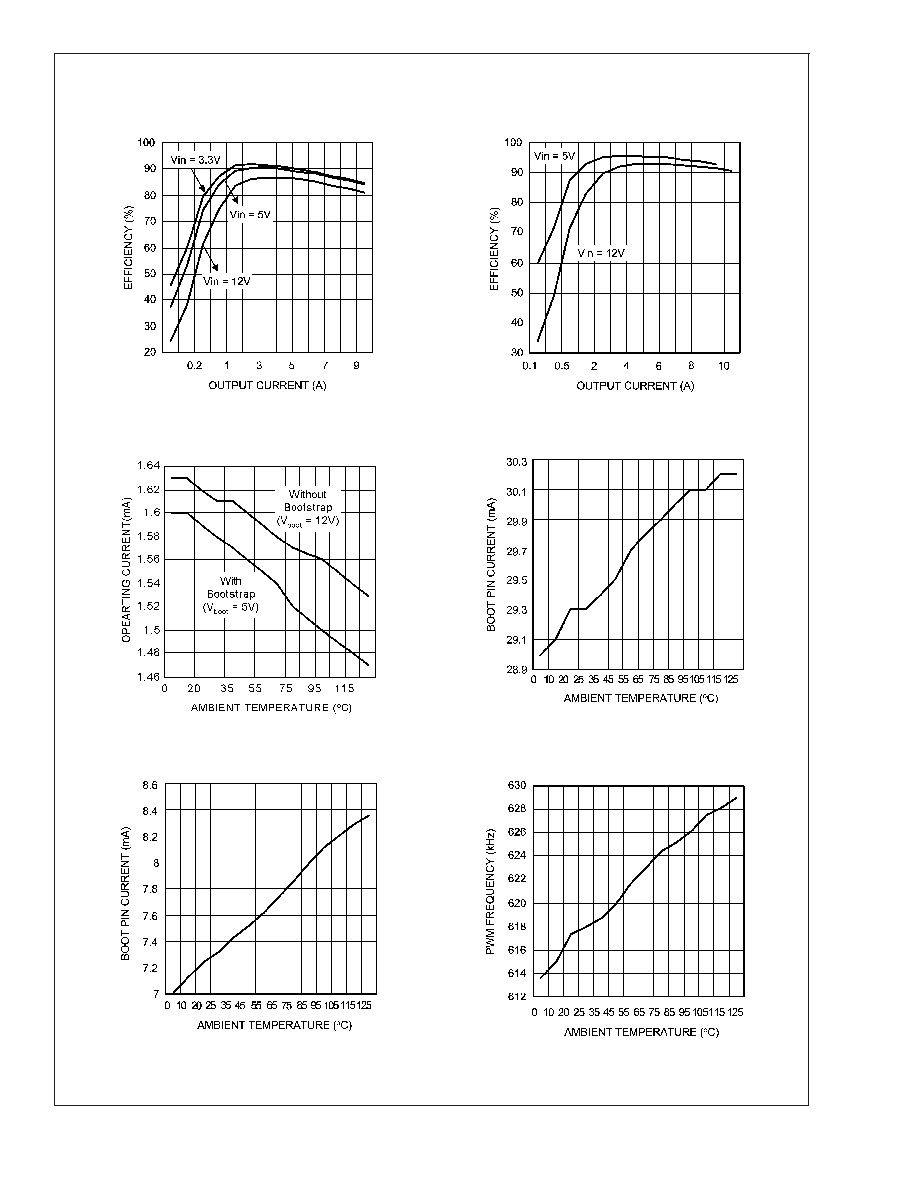

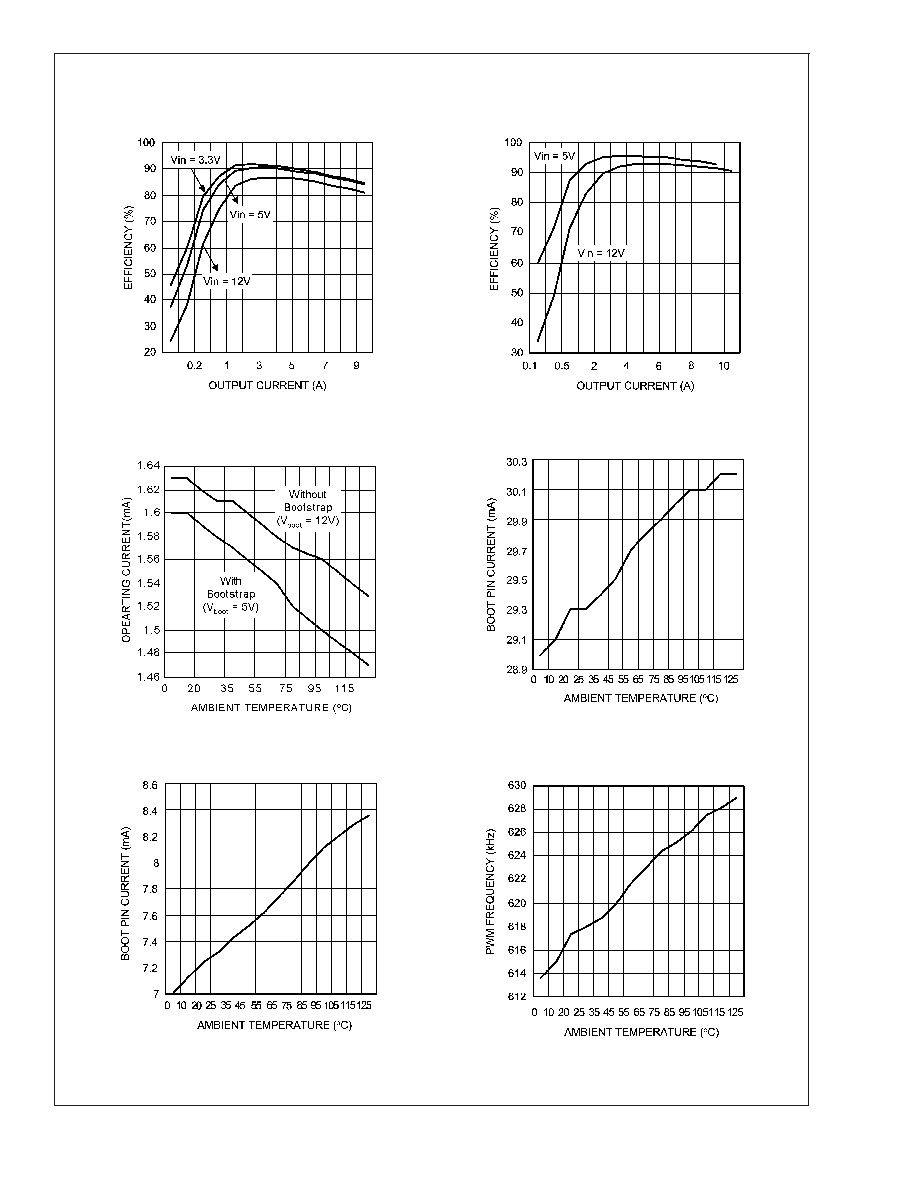

Typical Performance Characteristics

Efficiency (V

O

= 1.5V)

F

SW

= 300kHz, T

A

= 25∞C

Efficiency (V

O

= 3.3V)

F

SW

= 300kHz, T

A

= 25∞C

20049412

20049413

V

CC

Operating Current vs Temperature

F

SW

= 600kHz, No-Load

Bootpin Current vs Temperature for BOOTV = 12V

F

SW

= 600kHz, Si4826DY FET, No-Load

20049414

20049415

Bootpin Current vs Temperature with 5V Bootstrap

F

SW

= 600kHz, Si4826DY FET, No-Load

PWM Frequency vs Temperature

for R

FADJ

= 43.2k

20049416

20049417

LM2727/LM2737

www.national.com

5