| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 54ACTQ657 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

54ACTQ657

Quiet Series Octal Bidirectional Transceiver with 8-Bit

Parity Generator/Checker and TRI-STATE

Æ

Outputs

General Description

The ACTQ657 contains eight non-inverting buffers with

TRI-STATE outputs and an 8-bit parity generator/checker. In-

tended for bus oriented applications, the device combines

the '245 and the '280 functions in one package.

The ACTQ utilizes NSC Quiet Series technology to guaran-

tee quiet output switching and improved dynamic threshold

performance. FACT Quiet Series

TM

features GTO

TM

output

control and undershoot corrector in addition to a split ground

bus for superior performance.

Features

n

Guaranteed simultaneous switching noise level and

dynamic threshold performance

n

Combines the '245 and the '280 functions in one

package

n

Outputs source/sink 24 mA

n

'ACTQ has TTL-compatible inputs

n

Standard Microcircuit Drawing (SMD)

5962-92197

Logic Symbols

GTO

TM

is a trademark of National Semiconductor Corporation.

TRI-STATE

Æ

is a registered trademark of National Semiconductor Corporation.

FACT Quiet Series

TM

is a trademark of Fairchild Semiconductor Corporation.

IEEE/IEC

DS100244-1

DS100244-4

September 1998

54ACTQ657

Quiet

Series

Octal

Bidirectional

T

ransceiver

with

8-Bit

Parity

Generator/Checker

and

TRI-ST

A

T

E

Outputs

© 1998 National Semiconductor Corporation

DS100244

www.national.com

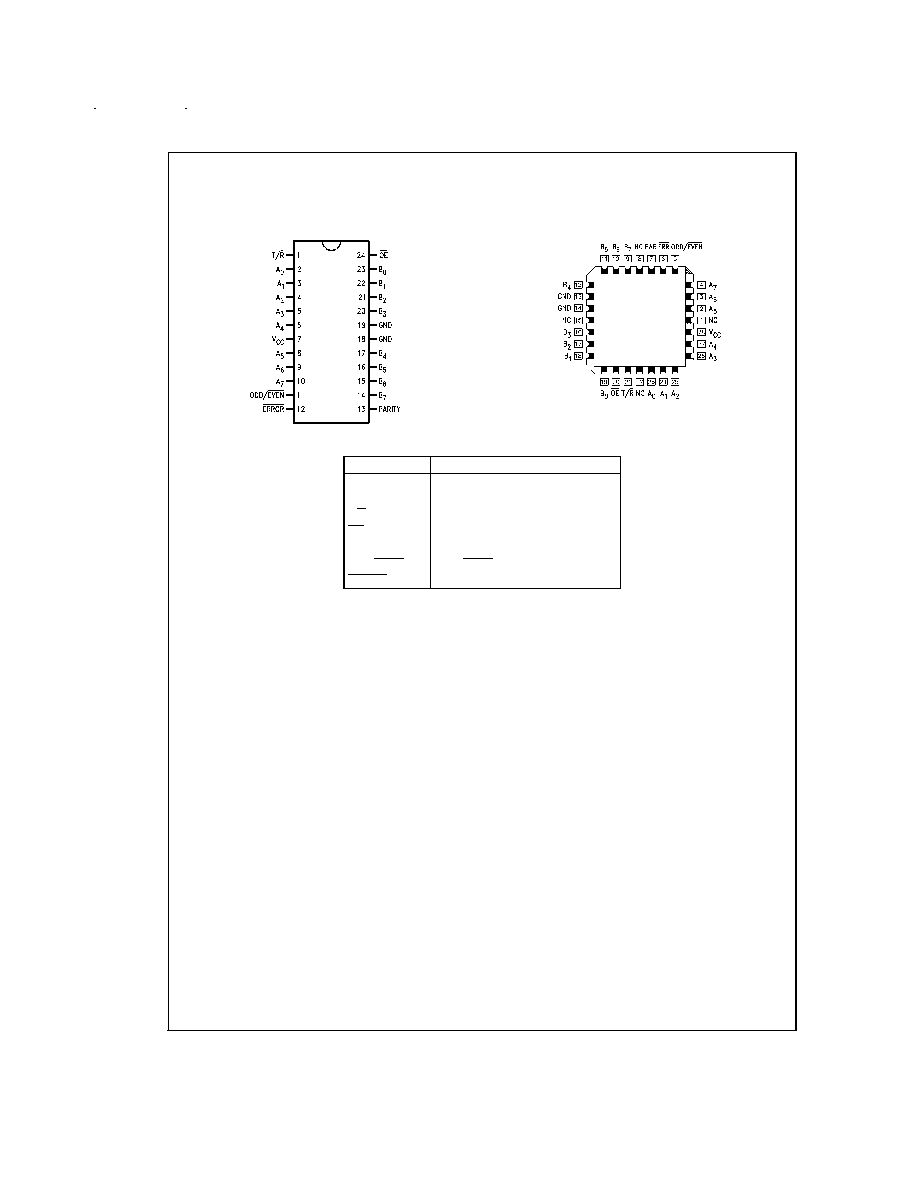

Connection Diagrams

Pin Names

Description

A

0

≠A

7

Data Inputs/TRI-STATE Outputs

B

0

≠B

7

Data Inputs/TRI-STATE Outputs

T/R

Transmit/Receive Input

OE

Enable Input

PARITY

Parity Input/TRI-STATE Output

ODD/EVEN

ODD/EVEN Parity Input

ERROR

Error TRI-STATE Output

Pin Assignment

for DIP and Flatpak

DS100244-2

Pin Assignment

for LCC

DS100244-3

www.national.com

2

Functional Description

The Transmit/Receive (T/R) input determines the direction of

the data flow through the bidirectional transceivers. Transmit

(active HIGH) enables data from the A port to the B port; Re-

ceive (active LOW) enables data from the B port to the A

port.

The Output Enable (OE) input disables the parity and

ERROR outputs and both the A and B ports by placing them

in a HIGH-Z condition when the Output Enable input is

HIGH.

When transmitting (T/R HIGH), the parity generator detects

whether an even or odd number of bits on the A port are

HIGH and compares these with the condition of the parity se-

lect (ODD/EVEN). If the Parity Select is HIGH and an even

number of A inputs are HIGH, the Parity output is HIGH.

In receiving mode (T/R LOW), the parity select and number

of HIGH inputs on port B are compared to the condition of

the Parity input. If an even number of bits on the B port are

HIGH, the parity select is HIGH, and the PARITY input is

HIGH, then ERROR will be HIGH to indicate no error. If an

odd number of bits on the B port are HIGH, the parity select

is HIGH, and the PARITY input is HIGH, the ERROR will be

LOW indicating an error.

www.national.com

3

Functional Description

(Continued)

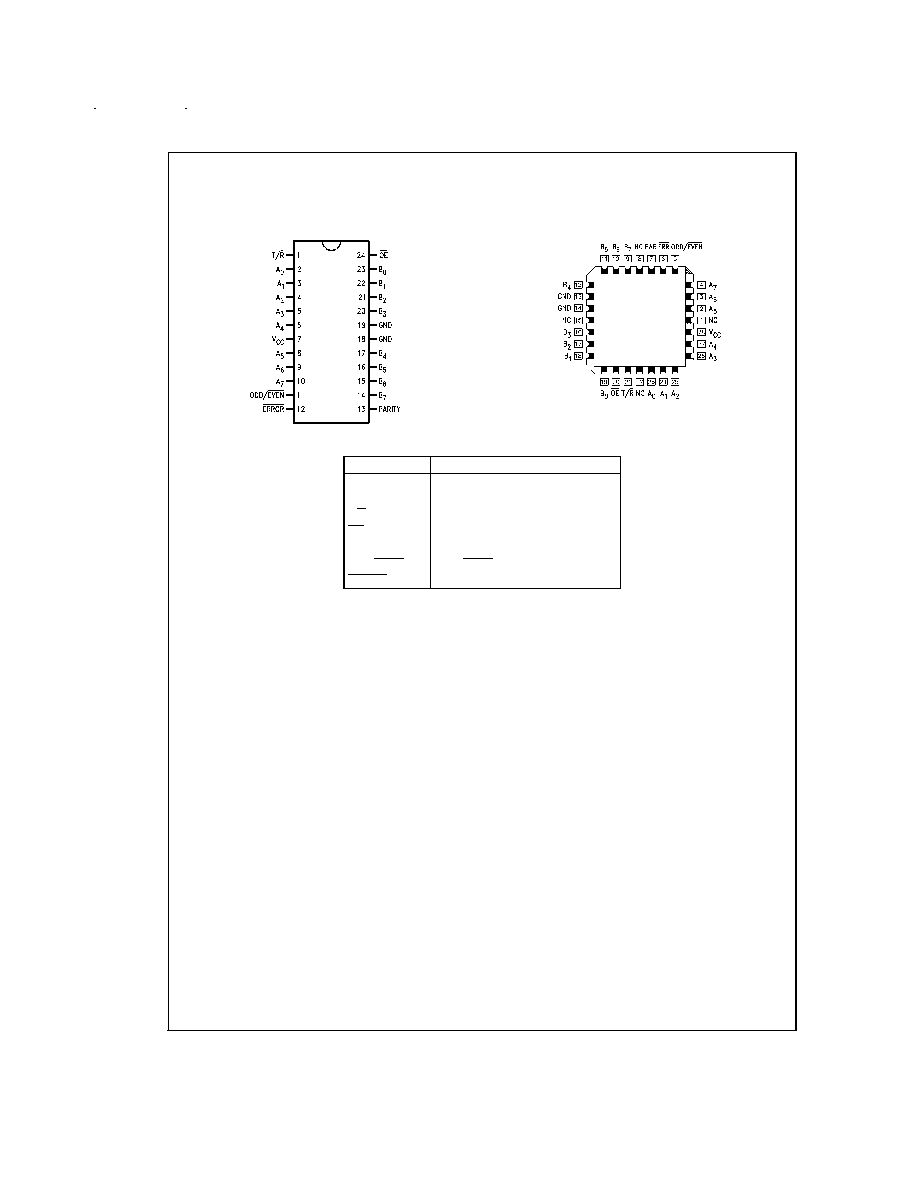

Function Table

Number of

Inputs

Input/

Outputs

Inputs That

Output

Are High

OE

T/R

ODD/EVEN

Parity

ERROR

Outputs Mode

0, 2, 4, 6, 8

L

H

H

H

Z

Transmit

L

H

L

L

Z

Transmit

L

L

H

H

H

Receive

L

L

H

L

L

Receive

L

L

L

H

L

Receive

L

L

L

L

H

Receive

1, 3, 5, 7

L

H

H

L

Z

Transmit

L

H

L

H

Z

Transmit

L

L

H

H

L

Receive

L

L

H

L

H

Receive

L

L

L

H

H

Receive

L

L

L

L

L

Receive

Immaterial

H

X

X

Z

Z

Z

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = High Impedance

Function Table

Inputs

Outputs

OE

T/R

L

L

Bus B Data to Bus A

L

H

Bus A Data to Bus B

H

X

High-Z State

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

www.national.com

4

Functional Block Diagram

DS100244-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com

5

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

)

-0.5V to +7.0V

DC Input Diode Current (I

IK

)

V

I

= -0.5V

-20 MA

V

I

= V

CC

+ 0.5V

+20 mA

DC Input Voltage (V

I

)

-0.5V to V

CC

+ 0.5V

DC Output Diode Current (I

OK

)

V

O

= -0.5V

-20 mA

V

O

= V

CC

+ 0.5V

+20 mA

DC Output Voltage (V

O

)

-0.5V to V

CC

+ 0.5V

DC Output Source

or Sink Current (I

O

)

±

50 mA

DC V

CC

or Ground Current

per Output Pin (I

CC

or I

GND

)

±

50 mA

Storage Temperature (T

STG

)

-65∞C to +150∞C

DC Latch-up Source or

Sink Current

±

300 mA

Junction Temperature (T

J

)

CDIP

175∞C

Recommended Operating

Conditions

Supply Voltage (V

CC

)

'ACTQ

4.5V to 5.5V

Input Voltage (V

I

)

0V to V

CC

Output Voltage (V

O

)

0V to V

CC

Operating Temperature (T

A

)

54ACTQ

-55∞C to +125∞C

Minimum Input Edge Rate

V/

t

'ACTQ Devices

V

IN

from 0.8V to 2.0V

V

CC

@

4.5V, 5.5V

125 mV/ns

Note 1: Absolute maximum ratings are those values beyond which damage

to the device may occur. The databook specifications should be met, without

exception, to ensure that the system design is reliable over its power supply,

temperature, and output/input loading variables. National does not recom-

mend operation of FACT circuits outside databook specifications.

DC Characteristics for 'ACTQ Family Devices

54ACTQ

Symbol

Parameter

V

CC

T

A

=

Units

Conditions

(V)

-55∞C to +125∞C

Guaranteed

Limits

V

IH

Minimum High Level

4.5

2.0

V

V

OUT

= 0.1V

Input Voltage

5.5

2.0

or V

CC

- 0.1V

V

IL

Maximum Low Level

4.5

0.8

V

V

OUT

= 0.1V

Input Voltage

5.5

0.8

or V

CC

- 0.1V

V

OH

Minimum High Level

4.5

4.4

V

I

OUT

= -50 µA

Output Voltage

5.5

5.4

(Note 2)

V

IN

= V

IL

or V

IH

4.5

3.70

V

I

OH

= -24 mA

5.5

4.70

I

OH

= -24 mA

V

OL

Maximum Low Level

4.5

0.1

V

I

OUT

= 50 µA

Output Voltage

5.5

0.1

(Note 2)

V

IN

= V

IL

or V

IH

4.5

0.50

V

I

OL

= 24 mA

5.5

0.50

I

OL

= 24 mA

I

IN

Maximum Input

V

I

= V

CC

, GND

Leakage Current

5.5

±

1.0

µA

(T/R, OE, ODD/EVEN

Inputs)

I

OZT

Maximum I/O

V

I

= V

IL

, V

IH

Leakage Current

5.5

±

11.0

µA

V

O

= V

CC

, GND

(A

n

, B

n

Inputs)

I

CCT

Maximum I

CC

/Input

5.5

1.6

mA

V

I

= V

CC

- 2.1V

www.national.com

6

DC Characteristics for 'ACTQ Family Devices

(Continued)

54ACTQ

Symbol

Parameter

V

CC

T

A

=

Units

Conditions

(V)

-55∞C to +125∞C

Guaranteed

Limits

I

OLD

Minimum Dynamic

Output Current

(Note 3)

5.5

50

mA

V

OLD

= 1.65V Max

I

OHD

5.5

-50

mA

V

OHD

= 3.85V Min

I

CC

Maximum

V

IN

= V

CC

Quiescent Supply

5.5

160.0

µA

or GND (Note 4)

Current

V

OLP

Quiet Output Maximum

5.0

1.5

V

(Note 5)

Dynamic V

OL

V

OLV

Quiet Output Minimum

5.0

-1.2

V

(Note 5)

Dynamic V

OL

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

Note 4: I

CC

for 54ACTQ

@

25∞C is identical to 74ACTQ

@

25∞C.

Note 5: Max number of outputs defined as (n). n-1 Data Inputs are driven 0V to 3V; one output

@

GND.

www.national.com

7

AC Electrical Characteristics

Symbol

Parameter

V

CC

(V)

(Note 6)

54ACTQ

Units

T

A

= -55∞C to +125∞C

C

L

= 50 pF

Min

Max

t

PLH

,

Propagation Delay

5.0

1.5

9.0

ns

t

PHL

A

n

to B

n

, B

n

to A

n

t

PLH

,

Propagation Delay

5.0

1.5

13.5

ns

t

PHL

A

n

to Parity

t

PLH

,

Propagation Delay

5.0

1.5

10.5

ns

t

PHL

ODD/EVEN to PARITY

t

PLH

,

Propagation Delay

5.0

1.5

11.0

ns

t

PHL

ODD/EVEN to ERROR

t

PLH

,

Propagation Delay

5.0

1.5

13.5

ns

t

PHL

B

n

to ERROR

t

PLH

,

Propagation Delay

5.0

1.5

10.5

ns

t

PHL

PARITY to ERROR

t

PZH

,

Output Enable Time

5.0

1.5

11.5

ns

t

PZL

OE to A

n

/B

n

t

PHZ

,

Output Disable Time

5.0

1.5

9.0

ns

t

PLZ

OE to A

n

/B

n

t

PZH

,

Output Enable Time

5.0

1.5

11.5

ns

t

PZL

OE to ERROR (Note 7)

t

PHZ

,

Output Disable Time

5.0

1.5

9.0

ns

t

PLZ

OE to ERROR

t

PZH

,

Output Enable Time

5.0

1.5

11.5

ns

t

PZL

OE to PARITY

t

PHZ

,

Output Disable Time

5.0

1.5

8.5

ns

t

PLZ

OE to PARITY

Note 6: Voltage Range 5.0 is 5.0V

±

0.5V

Note 7: These delay times reflect the TRI-STATE recovery time only and not the signal time through the buffers or the parity check circuitry. To assure VALID infor-

mation at the ERROR pin, time must be allowed for the signal to propagate through the drivers (B to A), through the parity check circuitry (same as A to PARITY),

and to the ERROR output after the ERROR pin has been enabled (Output Enable times). VALID data at the ERROR pin

(A to PARITY) + (Output Enable Time).

Capacitance

Symbol

Parameter

Typ

Units

Conditions

C

IN

Input Capacitance

4.5

pF

V

CC

= 5.0V

C

PD

Power Dissipation

160.0

pF

V

CC

= 5.0V

Capacitance

www.national.com

8

Physical Dimensions

inches (millimeters) unless otherwise noted

28-Terminal Ceramic Leadless Chip Carrier (L)

NS Package Number E28A

24-Lead Slim Ceramic (0.300" Wide)

Dual-In-Line Package (SD)

NS Package Number J24F

www.national.com

9

Physical Dimensions

inches (millimeters) unless otherwise noted (Continued)

LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-

VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-

CONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or sys-

tems which, (a) are intended for surgical implant into

the body, or (b) support or sustain life, and whose fail-

ure to perform when properly used in accordance

with instructions for use provided in the labeling, can

be reasonably expected to result in a significant injury

to the user.

2. A critical component in any component of a life support

device or system whose failure to perform can be rea-

sonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English

Tel: +49 (0) 1 80-532 78 32

FranÁais Tel: +49 (0) 1 80-532 93 58

Italiano

Tel: +49 (0) 1 80-534 16 80

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5620-6175

Fax: 81-3-5620-6179

24-Lead Ceramic Flatpak (F)

NS Package Number W24C

54ACTQ657

Quiet

Series

Octal

Bidirectional

T

ransceiver

with

8-Bit

Parity

Generator/Checker

and

TRI-ST

A

T

E

Outputs

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.