DS90C031

LVDS Quad CMOS Differential Line Driver

General Description

The DS90C031 is a quad CMOS differential line driver de-

signed for applications requiring ultra low power dissipation

and high data rates. The device is designed to support data

rates in excess of 155.5 Mbps (77.7 MHz) utilizing Low Volt-

age Differential Signaling (LVDS) technology.

The DS90C031 accepts TTL/CMOS input levels and trans-

lates them to low voltage (350 mV) differential output sig-

nals. In addition the driver supports a TRI-STATE

Æ

function

that may be used to disable the output stage, disabling the

load current, and thus dropping the device to an ultra low idle

power state of 11 mW typical.

The DS90C031 and companion line receiver (DS90C032)

provide a new alternative to high power psuedo-ECL devices

for high speed point-to-point interface applications.

Features

n

>

155.5 Mbps (77.7 MHz) switching rates

n

±

350 mV differential signaling

n

Ultra low power dissipation

n

400 ps maximum differential skew (5V, 25∞C)

n

3.5 ns maximum propagation delay

n

Industrial operating temperature range

n

Military operating temperature range option

n

Available in surface mount packaging (SOIC) and (LCC)

n

Pin compatible with DS26C31, MB571 (PECL) and

41LG (PECL)

n

Compatible with IEEE 1596.3 SCI LVDS standard

n

Conforms to ANSI/TIA/EIA-644 LVDS standard

n

Available to Standard Microcircuit Drawing (SMD)

5962-95833

Connection Diagrams

TRI-STATE

Æ

is a registered trademark of National Semiconductor Corporation.

Dual-In-Line

DS011946-1

Order Number DS90C031TM

See NS Package Number M16A

LCC Package

DS011946-33

Order Number DS90C031E-QML

See NS Package Number E20A

For Complete Military Specifications,

refer to appropriate SMD or MDS.

June 1998

DS90C031

L

VDS

Quad

CMOS

Differential

Line

Driver

© 1998 National Semiconductor Corporation

DS011946

www.national.com

Functional Diagram

Truth Table

DRIVER

Enables

Input

Outputs

EN

EN*

D

IN

D

OUT+

D

OUT-

L

H

X

Z

Z

All other combinations

L

L

H

of ENABLE inputs

H

H

L

DS011946-2

www.national.com

2

Absolute Maximum Ratings

(Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

)

-0.3V to +6V

Input Voltage (D

IN

)

-0.3V to (V

CC

+ 0.3V)

Enable Input Voltage (EN, EN*)

-0.3V to (V

CC

+ 0.3V)

Output Voltage (D

OUT+

, D

OUT-

)

-0.3V to (V

CC

+ 0.3V)

Short Circuit Duration

(D

OUT+

, D

OUT-

)

Continuous

Maximum Package Power Dissipation

@

+25∞C

M Package

1068 mW

E Package

1900 mW

Derate M Package

8.5 mW/∞C above +25∞C

Derate E Package

12.8 mW/∞C above +25∞C

Storage Temperature Range

-65∞C to +150∞C

Lead Temperature Range

Soldering (4 sec.)

+260∞C

Maximum Junction Temperature

(DS90C031T)

+150∞C

Maximum Junction Temperature

(DS90C031E)

+175∞C

ESD Rating (Note 7)

(HBM, 1.5 k

, 100 pF)

3,500V

(EIAJ, 0

, 200 pF)

250V

Recommended Operating

Conditions

Min

Typ

Max

Units

Supply Voltage (V

CC

)

+4.5

+5.0

+5.5

V

Operating Free Air Temperature (T

A

)

DS90C031T

-40

+25

+85

∞C

DS90C031E

-55

+25

+125

∞C

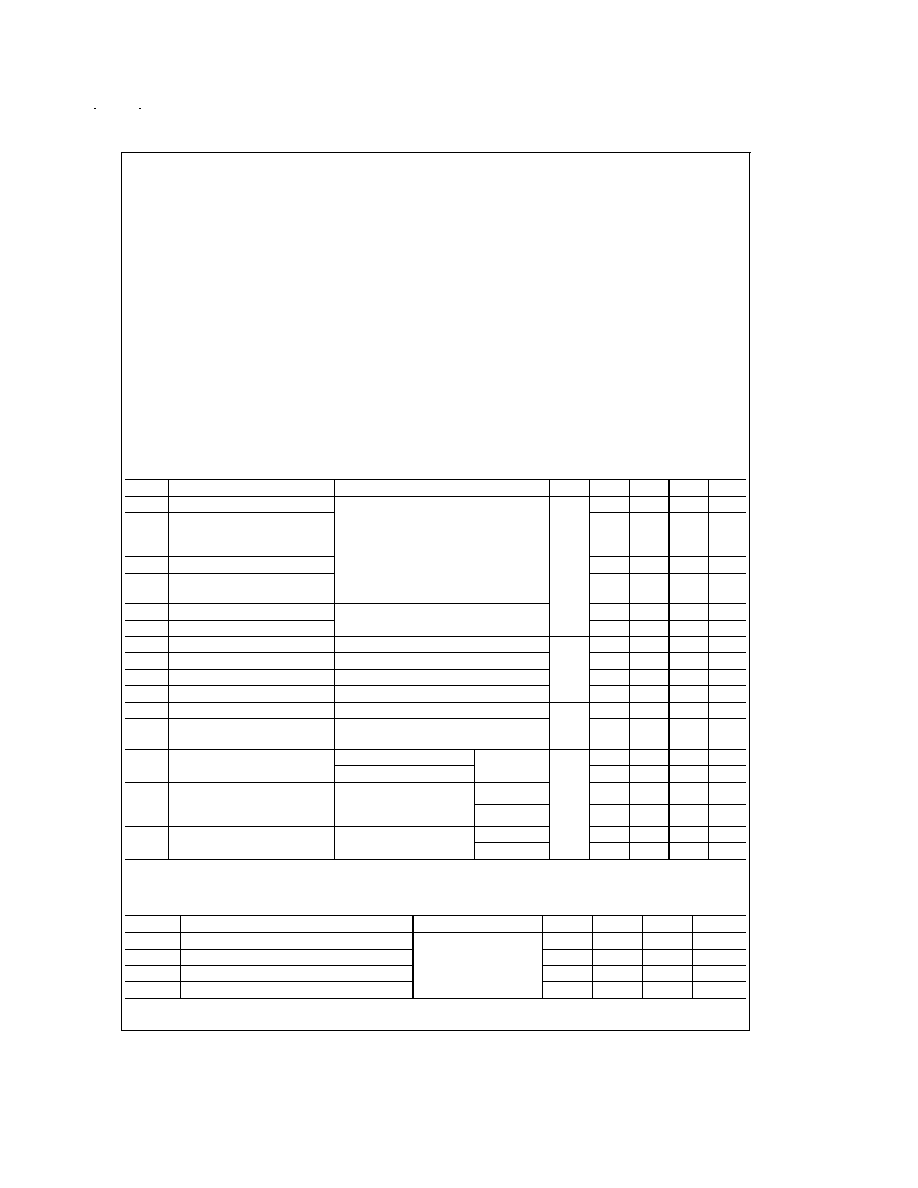

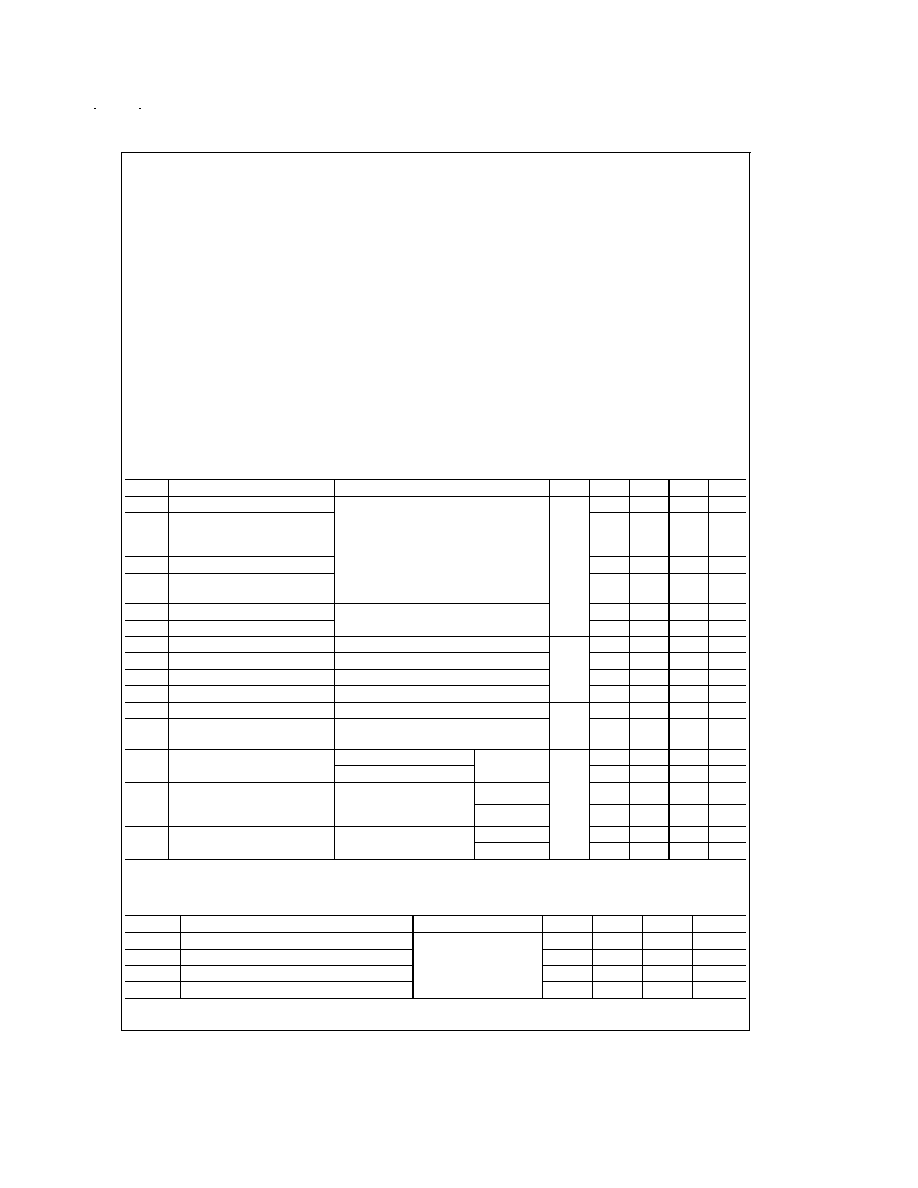

Electrical Characteristics

Over supply voltage and operating temperature ranges, unless otherwise specified. (Notes 2, 3)

Symbol

Parameter

Conditions

Pin

Min

Typ

Max

Units

V

OD1

Differential Output Voltage

R

L

= 100

(

Figure 1)

D

OUT-

,

D

OUT+

250

345

450

mV

V

OD1

Change in Magnitude of V

OD1

for Complementary Output

States

4

35

|mV|

V

OS

Offset Voltage

1.125

1.25

1.375

V

V

OS

Change in Magnitude of V

OS

for

Complementary Output States

5

25

|mV|

V

OH

Output Voltage High

R

L

= 100

1.41

1.60

V

V

OL

Output Voltage Low

0.90

1.07

V

V

IH

Input Voltage High

D

IN

,

EN,

EN*

2.0

V

CC

V

V

IL

Input Voltage Low

GND

0.8

V

I

I

Input Current

V

IN

= V

CC

, GND, 2.5V or 0.4V

-10

±

1

+10

µA

V

CL

Input Clamp Voltage

I

CL

= -18 mA

-1.5

-0.8

V

I

OS

Output Short Circuit Current

V

OUT

= 0V (Note 8)

D

OUT-

,

D

OUT+

-3.5

-5.0

mA

I

OZ

Output TRI-STATE Current

EN = 0.8V and EN* = 2.0V,

V

OUT

= 0V or V

CC

-10

±

1

+10

µA

I

CC

No Load Supply Current

Drivers Enabled

D

IN

= V

CC

or GND

DS90C031T

V

CC

1.7

3.0

mA

D

IN

= 2.5V or 0.4V

4.0

6.5

mA

I

CCL

Loaded Supply Current

Drivers Enabled

R

L

= 100

All Channels

V

IN

= V

CC

or GND

(all inputs)

DS90C031T

15.4

21.0

mA

DS90C031E

15.4

25.0

mA

I

CCZ

No Load Supply Current

Drivers Disabled

D

IN

= V

CC

or GND

EN = GND, EN* = V

CC

DS90C031T

2.2

4.0

mA

DS90C031E

2.2

10.0

mA

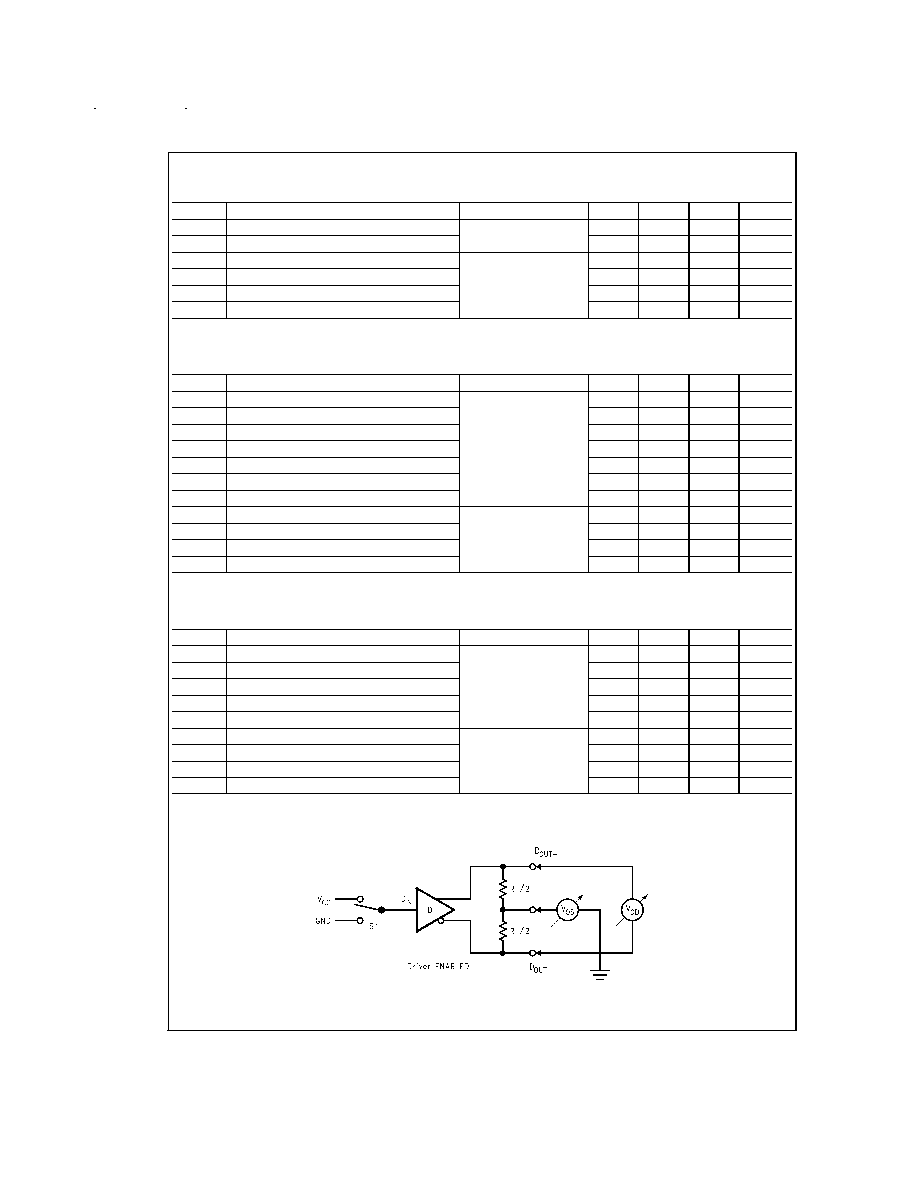

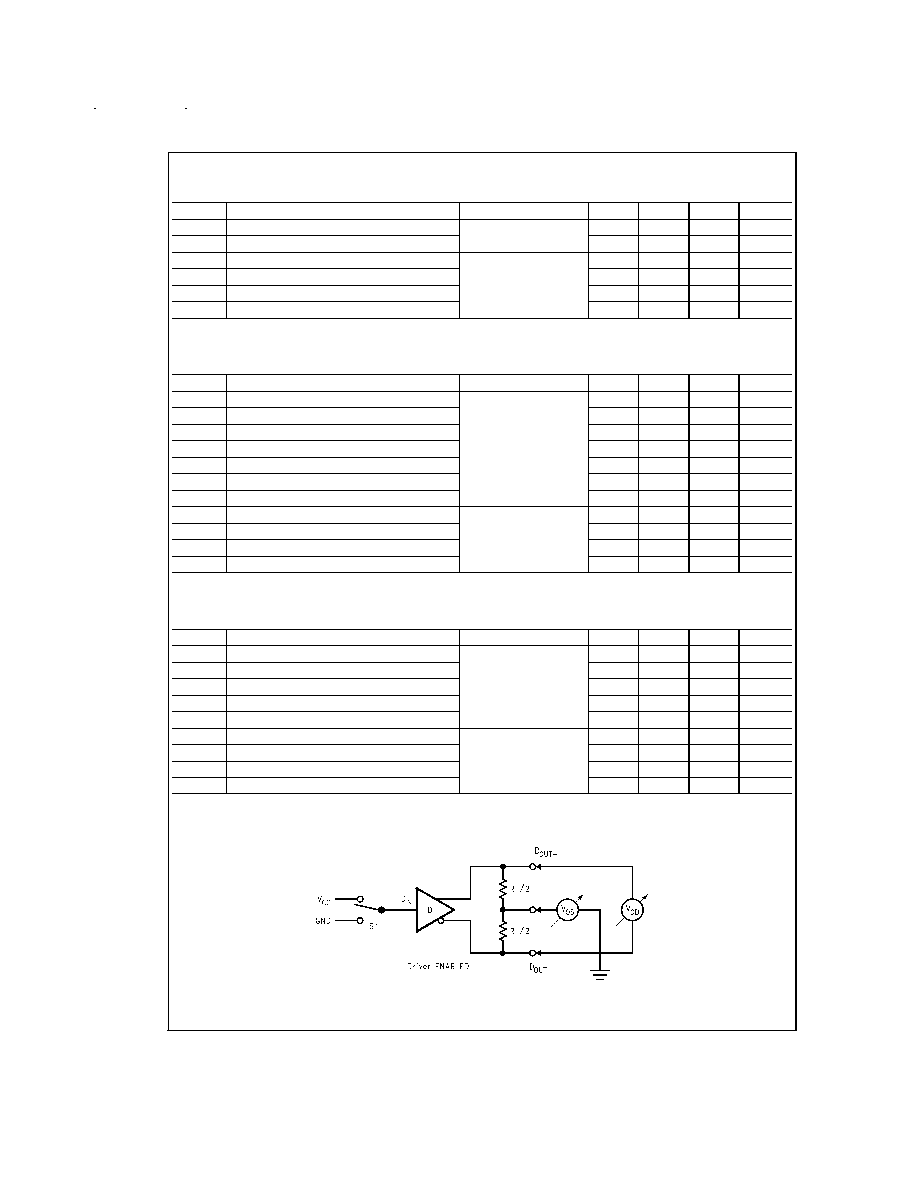

Switching Characteristics

V

CC

= +5.0V, T

A

= +25∞C DS90C031T. (Notes 3, 4, 6, 9)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

PHLD

Differential Propagation Delay High to Low

R

L

= 100

, C

L

= 5 pF

(

Figure 2 and Figure 3)

1.0

2.0

3.0

ns

t

PLHD

Differential Propagation Delay Low to High

1.0

2.1

3.0

ns

t

SKD

Differential Skew |t

PHLD

≠ t

PLHD

|

0

80

400

ps

t

SK1

Channel-to-Channel Skew (Note 4)

0

300

600

ps

www.national.com

3

Switching Characteristics

(Continued)

V

CC

= +5.0V, T

A

= +25∞C DS90C031T. (Notes 3, 4, 6, 9)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

TLH

Rise Time

0.35

1.5

ns

t

THL

Fall Time

0.35

1.5

ns

t

PHZ

Disable Time High to Z

R

L

= 100

,

C

L

= 5 pF

(

Figure 4 and Figure 5)

2.5

10

ns

t

PLZ

Disable Time Low to Z

2.5

10

ns

t

PZH

Enable Time Z to High

2.5

10

ns

t

PZL

Enable Time Z to Low

2.5

10

ns

Switching Characteristics

V

CC

= +5.0V

±

10%, T

A

= -40∞C to +85∞C DS90C031T. (Notes 3, 4, 5, 6, 9)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

PHLD

Differential Propagation Delay High to Low

R

L

= 100

, C

L

= 5 pF

(

Figure 2 and Figure 3)

0.5

2.0

3.5

ns

t

PLHD

Differential Propagation Delay Low to High

0.5

2.1

3.5

ns

t

SKD

Differential Skew |t

PHLD

≠ t

PLHD

|

0

80

900

ps

t

SK1

Channel-to-Channel Skew (Note 4)

0

0.3

1.0

ns

t

SK2

Chip to Chip Skew (Note 5)

3.0

ns

t

TLH

Rise Time

0.35

2.0

ns

t

THL

Fall Time

0.35

2.0

ns

t

PHZ

Disable Time High to Z

R

L

= 100

,

C

L

= 5 pF

(

Figure 4 and Figure 5)

2.5

15

ns

t

PLZ

Disable Time Low to Z

2.5

15

ns

t

PZH

Enable Time Z to High

2.5

15

ns

t

PZL

Enable Time Z to Low

2.5

15

ns

Switching Characteristics

V

CC

= +5.0V

±

10%, T

A

= -55∞C to +125∞C DS90C031E. (Notes 3, 4, 5, 6, 9, 10)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

PHLD

Differential Propagation Delay High to Low

R

L

= 100

, C

L

= 20 pF

(

Figure 3)

C

L

Connected between

each Output and GND

0.5

2.0

5.0

ns

t

PLHD

Differential Propagation Delay Low to High

0.5

2.1

5.0

ns

t

SKD

Differential Skew |t

PHLD

≠ t

PLHD

|

0

0.08

3.0

ns

t

SK1

Channel-to-Channel Skew (Note 4)

0

0.3

3.0

ns

t

SK2

Chip to Chip Skew (Note 5)

4.5

ns

t

PHZ

Disable Time High to Z

R

L

= 100

,

C

L

= 5 pF

(

Figure 4 and Figure 5)

2.5

20

ns

t

PLZ

Disable Time Low to Z

2.5

20

ns

t

PZH

Enable Time Z to High

2.5

20

ns

t

PZL

Enable Time Z to Low

2.5

20

ns

Parameter Measurement Information

DS011946-3

FIGURE 1. Driver V

OD

and V

OS

Test Circuit

www.national.com

4

Parameter Measurement Information

(Continued)

DS011946-4

FIGURE 2. Driver Propagation Delay and Transition Time Test Circuit

DS011946-5

FIGURE 3. Driver Propagation Delay and Transition Time Waveforms

DS011946-6

FIGURE 4. Driver TRI-STATE Delay Test Circuit

www.national.com

5