TL F 11675

74VHC4046

CMOS

Phase

Lock

Loop

October 1995

74VHC4046

CMOS Phase Lock Loop

General Description

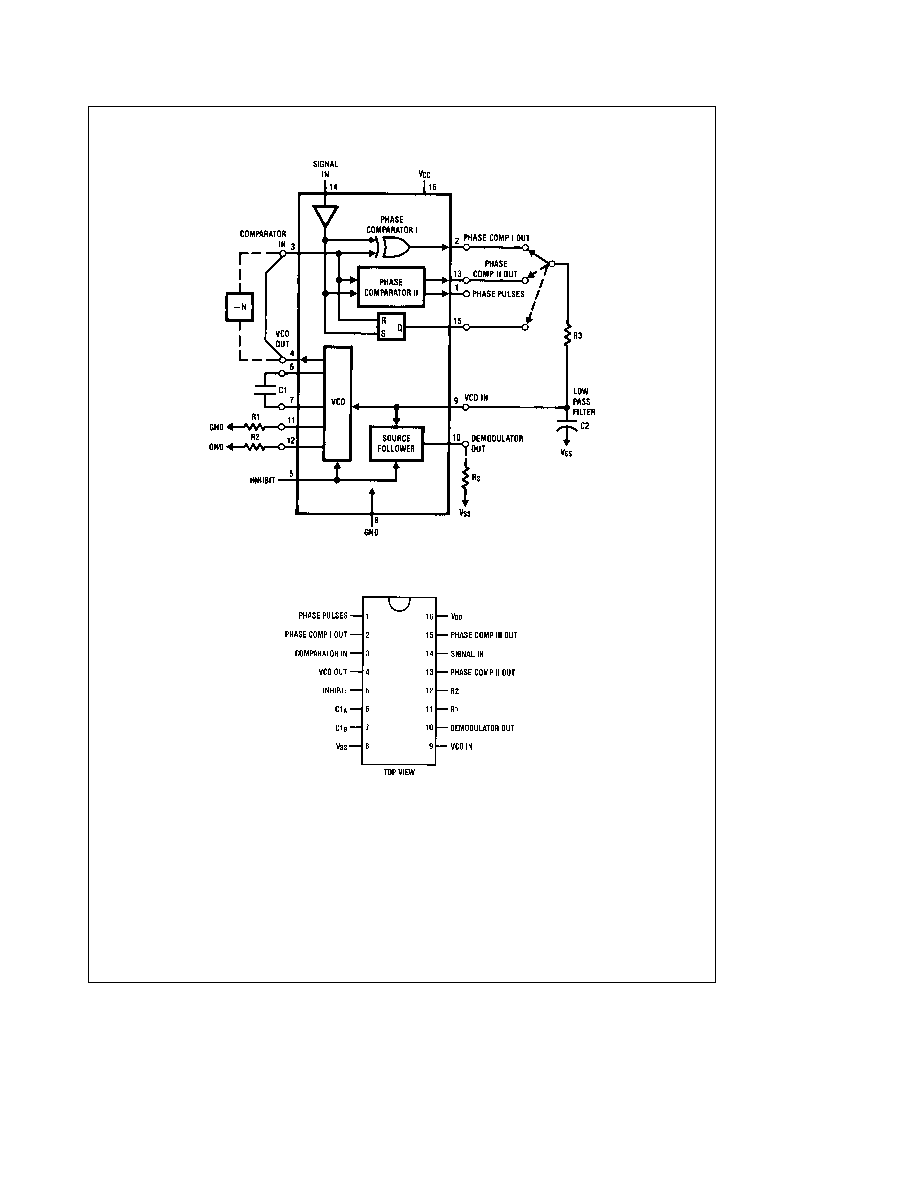

The 74VHC4046 is a low power phase lock loop utilizing

advanced silicon-gate CMOS technology to obtain high fre-

quency operation both in the phase comparator and VCO

sections This device contains a low power linear voltage

controlled oscillator (VCO) a source follower and three

phase comparators The three phase comparators have a

common signal input and a common comparator input The

signal input has a self biasing amplifier allowing signals to

be either capacitively coupled to the phase comparators

with a small signal or directly coupled with standard input

logic levels This device is similar to the CD4046 except that

the Zener diode of the metal gate CMOS device has been

replaced with a third phase comparator

Phase Comparator I is an exclusive OR (XOR) gate It pro-

vides a digital error signal that maintains a 90 phase shift

between the VCO's center frequency and the input signal

(50% duty cycle input waveforms) This phase detector is

more susceptible to locking onto harmonics of the input fre-

quency than phase comparator I but provides better noise

rejection

Phase comparator III is an SR flip-flop gate It can be used

to provide the phase comparator functions and is similar to

the first comparator in performance

Phase comparator II is an edge sensitive digital sequential

network Two signal outputs are provided a comparator out-

put and a phase pulse output The comparator output is a

TRI-STATE

output that provides a signal that locks the

VCO output signal to the input signal with 0 phase shift be-

tween them This comparator is more susceptible to noise

throwing the loop out of lock but is less likely to lock onto

harmonics than the other two comparators

In a typical application any one of the three comparators

feed an external filter network which in turn feeds the VCO

input This input is a very high impedance CMOS input

which also drives the source follower The VCO's operating

frequency is set by three external components connected to

the C1A C1B R1 and R2 pins An inhibit pin is provided to

disable the VCO and the source follower providing a meth-

od of putting the IC in a low power state

The source follower is a MOS transistor whose gate is con-

nected to the VCO input and whose drain connects the De-

modulator output This output normally is used by tying a

resistor from pin 10 to ground and provides a means of

looking at the VCO input without loading down modifying the

characteristics of the PLL filter

Features

Y

Low dynamic power consumption

(V

CC

e

4 5V)

Y

Maximum VCO operating frequency

12 MHz

(V

CC

e

4 5V)

Y

Fast comparator response time (V

CC

e

4 5V)

Comparator I

25 ns

Comparator II

30 ns

Comparator III

25 ns

Y

VCO has high linearity and high temperature stability

Y

Pin and function compatible with the 74HC4046

Commercial

Package

Package Description

Number

74VHC4046M

M16A

16-Lead Molded JEDEC SOIC

74VHC4046N

N16E

16-Lead Molded DIP

Note

Surface mount packages are also available on Tape and Reel Specify by appending the suffix letter ``X'' to the ordering code

TRI-STATE

is a registered trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation

RRD-B30M125 Printed in U S A

Absolute Maximum Ratings

(Notes 1

2)

Supply Voltage (V

CC

)

b

0 5 to

a

7 0V

DC Input Voltage (V

IN

)

b

1 5 to V

CC

a

1 5V

DC Output Voltage (V

OUT

)

b

0 5 to V

CC

a

0 5V

Clamp Diode Current (I

IK

I

OK

)

g

20 mA

DC Output Current per pin (I

OUT

)

g

25 mA

DC V

CC

or GND Current per pin (I

CC

)

g

50 mA

Storage Temperature Range (T

STG

)

b

65 C

a

150 C

Power Dissipation (P

D

)

(Note 3)

600 mW

S O Package only

500 mW

Lead Temperature (T

L

)

(Soldering 10 seconds)

260 C

Operating Conditions

Min

Max

Units

Supply Voltage (V

CC

)

2

6

V

DC Input or Output Voltage

0

V

CC

V

(V

IN

V

OUT

)

Operating Temp Range (T

A

)

74VHC

b

40

a

85

C

Input Rise or Fall Times

(t

r

t

f

)

V

CC

e

2 0V

1000

ns

V

CC

e

4 5V

500

ns

V

CC

e

6 0V

400

ns

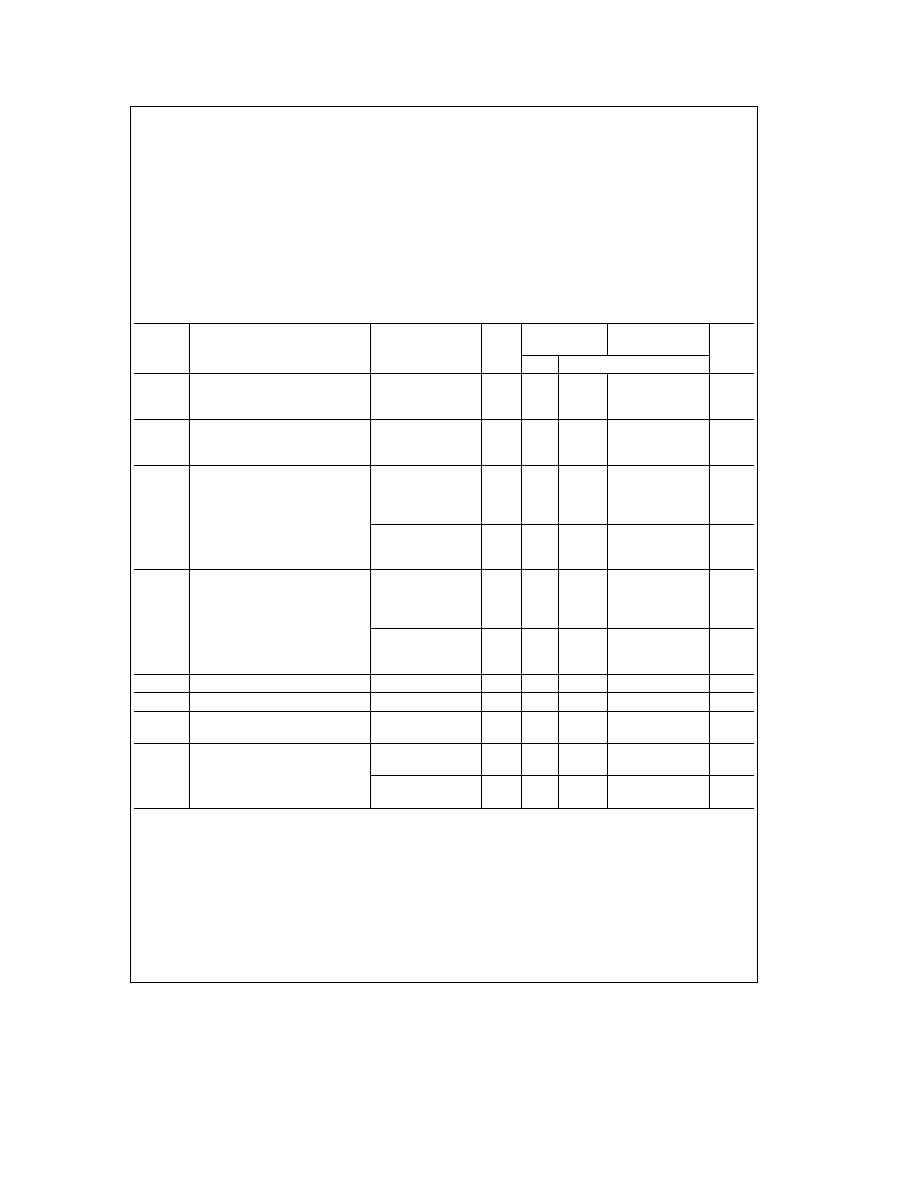

DC Electrical Characteristics

(Note 4)

T

A

e

25 C

74VHC

Symbol

Parameter

Conditions

V

CC

T

A

e b

40 to 85 C

Units

Typ

Guaranteed Limits

V

IH

Minimum High Level Input

2 0V

1 5

1 5

V

Voltage

4 5V

3 15

3 15

V

6 0V

4 2

4 2

V

V

IL

Maximum Low Level Input

2 0V

0 5

0 5

V

Voltage

4 5V

1 35

1 35

V

6 0V

1 8

1 8

V

V

OH

Minimum High Level Output

V

IN

e

V

IH

or V

IL

Voltage

l

I

OUT

l

s

20 mA

2 0V

2 0

1 9

1 9

V

4 5V

4 5

4 4

4 4

V

6 0V

6 0

5 9

5 9

V

V

IN

e

V

IH

or V

IL

l

I

OUT

l

s

4 0 mA

4 5V

4 2

3 98

3 84

V

l

I

OUT

l

s

5 2 mA

6 0V

5 7

5 48

5 34

V

V

OL

Maximum Low Level Output

V

IN

e

V

IH

or V

IL

Voltage

l

I

OUT

l

s

20 mA

2 0V

0

0 1

0 1

V

4 5V

0

0 1

0 1

V

6 0V

0

0 1

0 1

V

V

IN

e

V

IH

or V

IL

l

I

OUT

l

s

4 0 mA

4 5V

0 2

0 26

0 33

V

l

I

OUT

l

s

5 2 mA

6 0V

0 2

0 26

0 33

V

I

IN

Maximum Input Current (Pins 3 5 9)

V

IN

e

V

CC

or GND

6 0V

g

0 1

g

1 0

m

A

I

IN

Maximum Input Current (Pin 14)

V

IN

e

V

CC

or GND

6 0V

20

50

80

m

A

I

OZ

Maximum TRI-STATE Output

V

OUT

e

V

CC

or GND

6 0V

g

0 25

g

2 5

m

A

Leakage Current (Pin 13)

I

CC

Maximum Quiescent Supply

V

IN

e

V

CC

or GND

6 0V

30

40

65

m

A

Current

I

OUT

e

0 mA

V

IN

e

V

CC

or GND

6 0V

600

750

1200

m

A

Pin 14 Open

Note 1

Maximum Ratings are those values beyond which damage to the device may occur

Note 2

Unless otherwise specified all voltages are referenced to ground

Note 3

Power Dissipation temperature derating

plastic ``N'' package

b

12 mW C from 65 C to 85 C

Note 4

For a power supply of 5V

g

10% the worst case output voltages (V

OH

and V

OL

) occur for VHC at 4 5V Thus the 4 5V values should be used when

designing with this supply Worst case V

IH

and V

IL

occur at V

CC

e

5 5V and 4 5V respectively (The V

IH

value at 5 5V is 3 85V ) The worst case leakage current (I

IN

I

CC

and I

OZ

) occur for CMOS at the higher voltage and so the 6 0V values should be used

3

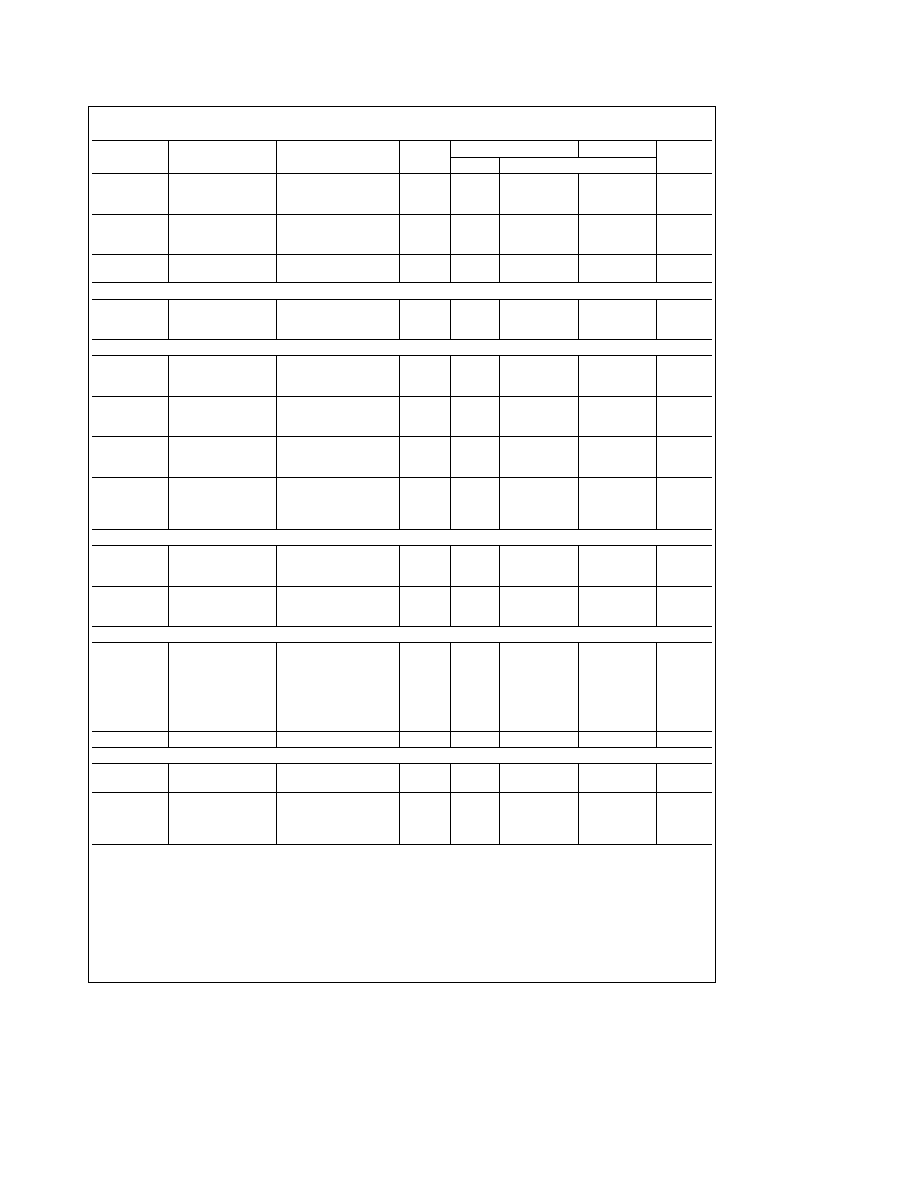

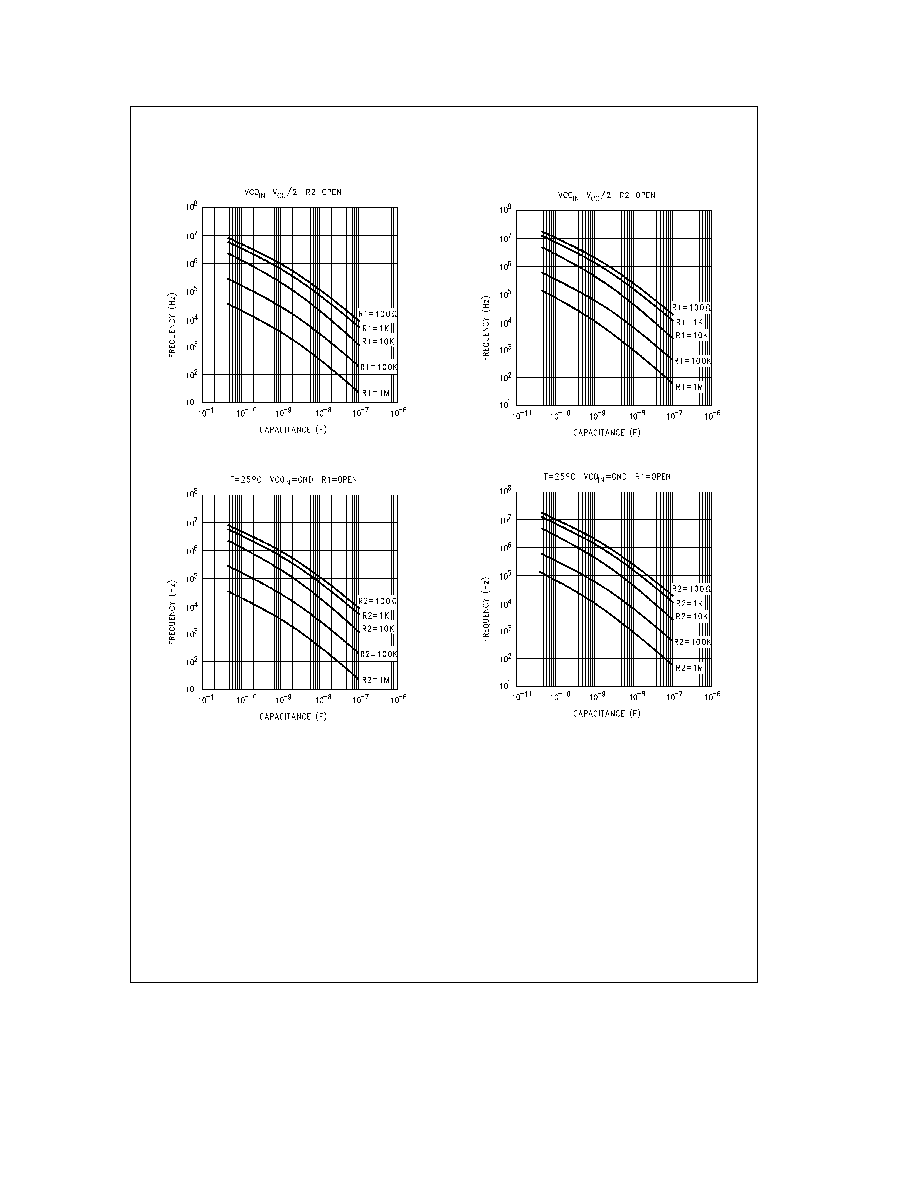

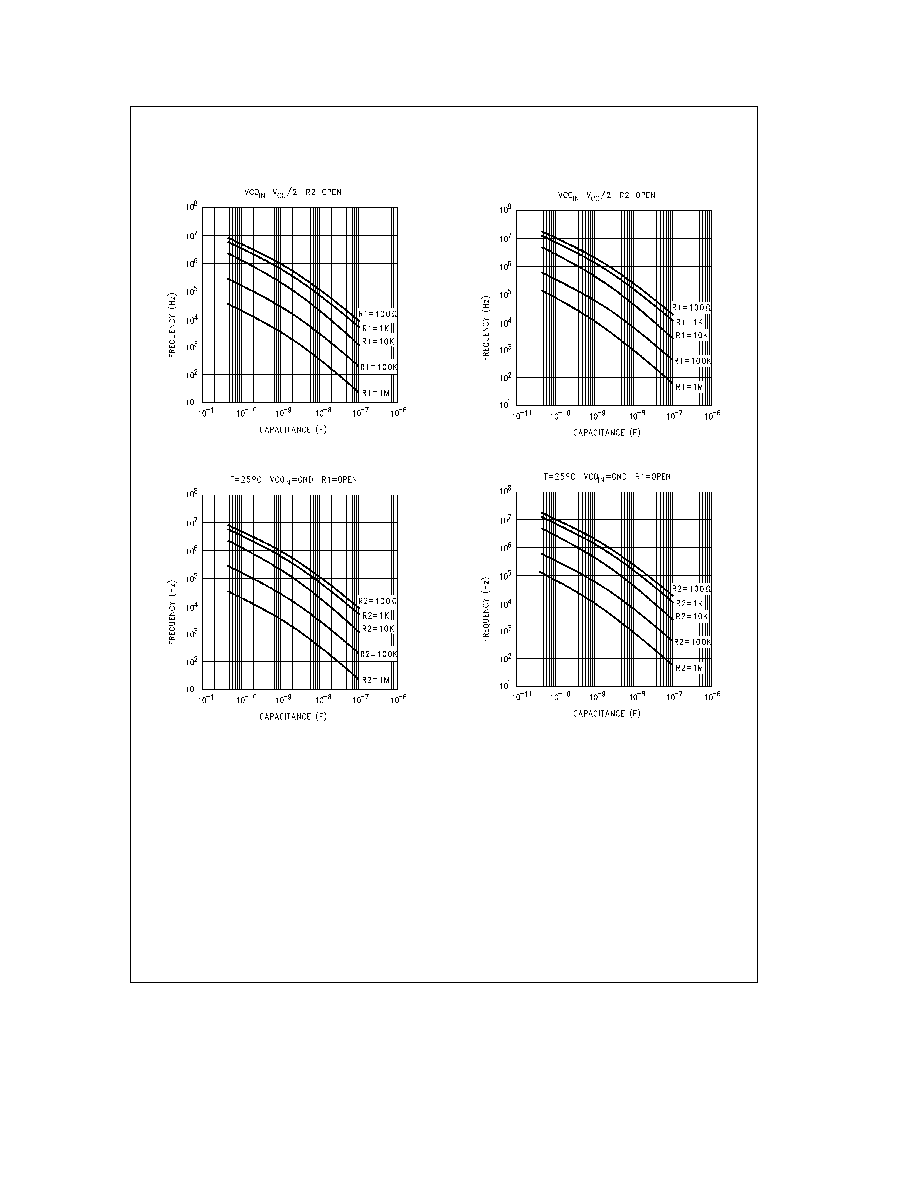

Typical Performance Characteristics

Typical Center Frequency

vs R1 C1

V

CC

e

4 5V

TL F 11675 ≠ 3

Typical Center Frequency

vs R1 C1

V

CC

e

6V

TL F 11675 ≠ 4

Typical Offset Frequency

vs R2 C1

V

CC

e

4 5V

TL F 11675 ≠ 5

Typical Offset Frequency

vs R2 C1

V

CC

e

6V

TL F 11675 ≠ 6

5