COP8SA Family

8-Bit CMOS ROM Based and One-Time Programmable

(OTP) Microcontroller with 1k to 4k Memory, Power On

Reset, and Very Small Packaging

General Description

Note: COP8SAx devices are instruction set and pin com-

patible supersets of the COP800 Family devices, and are

replacements for these in new designs when possible.

The COPSAx Rom based and OTP microcontrollers are

highly integrated COP8

TM

feature core devices, with 1k to 4k

memory and advanced features including low EMI. These

single-chip CMOS devices are suited for low cost applica-

tions requiring a full featured controller, low EMI, and POR.

100% form-fit-function compatible OTP versions are avail-

able with 1k, 2k, and 4k memory, and in a variety of pack-

ages including 28-pin CSP. Erasable windowed versions are

available for use with a range of COP8 software and hard-

ware development tools.

Family features include an 8-bit memory mapped architec-

ture, 10 MHz CKI with 1 µs instruction cycle, one multi-

function

16-bit

timer/counter

with

PWM

output,

MICROWIRE/PLUS

TM

serial I/O, two power saving HALT/

IDLE modes, MIWU, idle timer, on-chip R/C oscillator, 12

high current outputs, user selectable options (WATCH-

DOG

TM

, 4 clock/oscillator modes, power-on-reset), low EMI

2.7V to 5.5V operation, and 16/20/28/40/44 pin packages.

Devices included in this datasheet are:

Device

Memory

(bytes)

RAM

(bytes)

I/O Pins

Packages

Temperature

COP8SAA5

1k ROM

64

12/16/24

16/20/28 DIP/SOIC

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAB5

2k ROM

128

16/24

20/28 DIP/SOIC

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAC5

4k ROM

128

16/24/36/40

20/28 DIP/SOIC, 28 CSP,

40 DIP, 44 PLCC/QFP

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAA7

1k OTP EPROM

64

12/16/24

16/20/28 DIP/SOIC

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAB7

2k OTP EPROM

128

16/24

20/28 DIP/SOIC

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAC7

4k OTP EPROM

128

16/24

20/28 DIP/SOIC, 28 CSP,

40 DIP, 44 PLCC/QFP

0 to +70∞C, -40 to +85∞C,

-40 to +125∞C

COP8SAA7SLB9

1k OTP EPROM

64

24

28 CSP

0 to +70∞C

COP8SAB7SLB9

2k OTP EPROM

128

24

28 CSP

0 to +70∞C

COP8SAC7SLB9

4k OTP EPROM

128

24

28 CSP

0 to +70∞C

COP8SAC7-Q3

4k EPROM

128

16/24/36

20/28/40 DIP

Room Temp. Only

COP8SAC7-J3

4k EPROM

128

40

44 PLCC

Room Temp. Only

Key Features

n

Low cost 8-bit OTP microcontroller

n

OTP program space with read/write protection (fully

secured)

n

Quiet Design (low radiated emissions)

n

Multi-Input Wakeup pins with optional interrupts

(4 to 8 pins)

n

8 bytes of user storage space in EPROM

n

User selectable clock options

-- Crystal/Resonator options

-- Crystal/Resonator option with on-chip bias resistor

-- External oscillator

-- Internal R/C oscillator

n

Internal Power-On Reset -- user selectable

n

WATCHDOG and Clock Monitor Logic -- user selectable

n

Up to 12 high current outputs

TRI-STATE

Æ

is a registered trademark of National Semiconductor Corporation.

MICROWIRE/PLUS

TM

, COP8

TM

, MICROWIRE

TM

and WATCHDOG

TM

are trademarks of National Semiconductor Corporation.

iceMASTER

Æ

is a registered trademark of MetaLink Corporation.

PRELIMINARY

July 1999

COP8SA

Family,

8-Bit

CMOS

ROM

Based

and

One-T

ime

Programmable

(OTP)

Microcontroller

with

1k

to

4k

Memory,

Power

On

Reset,

and

V

ery

Small

Packaging

© 1999 National Semiconductor Corporation

DS012838

www.national.com

CPU Features

n

Versatile easy to use instruction set

n

1 µs instruction cycle time

n

Eight multi-source vectored interrupts servicing

-- External interrupt

-- Idle Timer T0

-- One Timer (with 2 interrupts)

-- MICROWIRE/PLUS Serial Interface

-- Multi-Input Wake Up

-- Software Trap

-- Default VIS (default interrupt)

n

8-bit Stack Pointer SP (stack in RAM)

n

Two 8-bit Register Indirect Data Memory Pointers

n

True bit manipulation

n

Memory mapped I/O

n

BCD arithmetic instructions

Peripheral Features

n

Multi-Input Wakeup Logic

n

One 16-bit timer with two 16-bit registers supporting:

-- Processor Independent PWM mode

-- External Event counter mode

-- Input Capture mode

n

Idle Timer

n

MICROWIRE/PLUS Serial Interface (SPI Compatible)

I/O Features

n

Software selectable I/O options

-- TRI-STATE

Æ

Output

-- Push-Pull Output

-- Weak Pull Up Input

-- High Impedance Input

n

Schmitt trigger inputs on ports G and L

n

Up to 12 high current outputs

n

Pin efficient (i.e., 40 pins in 44-pin package are devoted

to useful I/O)

Fully Static CMOS Design

n

Low current drain (typically

<

4 µA)

n

Single supply operation: 2.7V to 5.5V

n

Two power saving modes: HALT and IDLE

Temperature Ranges

0∞C to +70∞C, -40∞C to +85∞C, and -40∞C to +125∞C

Development Support

n

Windowed packages for DIP and PLCC

n

Real time emulation and full program debug offered by

MetaLink Development System

Block Diagram

DS012838-1

FIGURE 1. COP8SAx Block Diagram

www.national.com

2

General Description

(Continued)

Key features include an 8-bit memory mapped architecture,

a 16-bit timer/counter with two associated 16-bit registers

supporting three modes (Processor Independent PWM gen-

eration, External Event counter, and Input Capture capabili-

ties),

two

power

saving

HALT/IDLE

modes

with

a

multi-sourced wakeup/interrupt capability, on-chip R/C oscil-

lator, high current outputs, user selectable options such as

WATCHDOG, Oscillator configuration, and power-on-reset.

1.1 EMI REDUCTION

The COP8SAx family of devices incorporates circuitry that

guards against electromagnetic interference -- an increasing

problem in today's microcontroller board designs. National's

patented EMI reduction technology offers low EMI clock cir-

cuitry, gradual turn-on output drivers (GTOs) and internal I

CC

smoothing filters, to help circumvent many of the EMI issues

influencing

embedded

control

designs.

National

has

achieved 15 dB≠20 dB reduction in EMI transmissions when

designs have incorporated its patented EMI reducing cir-

cuitry.

1.2 ARCHITECTURE

The COP8SAx family is based on a modified Harvard archi-

tecture, which allows data tables to be accessed directly

from program memory. This is very important with modern

microcontroller-based applications, since program memory

is usually ROM or EPROM, while data memory is usually

RAM. Consequently data tables usually need to be con-

tained in ROM or EPROM, so they are not lost when the mi-

crocontroller is powered down. In a modified Harvard archi-

tecture, instruction fetch and memory data transfers can be

overlapped with a two stage pipeline, which allows the next

instruction to be fetched from program memory while the

current instruction is being executed using data memory.

This is not possible with a Von Neumann single-address bus

architecture.

The COP8SAx family supports a software stack scheme that

allows the user to incorporate many subroutine calls. This

capability is important when using High Level Languages.

With a hardware stack, the user is limited to a small fixed

number of stack levels.

1.3 INSTRUCTION SET

In today's 8-bit microcontroller application arena cost/

performance, flexibility and time to market are several of the

key issues that system designers face in attempting to build

well-engineered products that compete in the marketplace.

Many of these issues can be addressed through the manner

in which a microcontroller's instruction set handles process-

ing tasks. And that's why COP8 family offers a unique and

code-efficient instruction set -- one that provides the flexibil-

ity, functionality, reduced costs and faster time to market that

today's microcontroller based products require.

Code efficiency is important because it enables designers to

pack more on-chip functionality into less program memory

space (ROM/OTP). Selecting a microcontroller with less pro-

gram memory size translates into lower system costs, and

the added security of knowing that more code can be packed

into the available program memory space.

1.3.1 Key Instruction Set Features

The COP8SAx family incorporates a unique combination of

instruction set features, which provide designers with opti-

mum code efficiency and program memory utilization.

Single Byte/Single Cycle Code Execution

The efficiency is due to the fact that the majority of instruc-

tions are of the single byte variety, resulting in minimum pro-

gram space. Because compact code does not occupy a sub-

stantial amount of program memory space, designers can

integrate additional features and functionality into the micro-

controller program memory space. Also, the majority instruc-

tions executed by the device are single cycle, resulting in

minimum program execution time. In fact, 77% of the instruc-

tions are single byte single cycle, providing greater code and

I/O efficiency, and faster code execution.

1.3.2 Many Single-Byte, Multifunction Instructions

The COP8SAx instruction set utilizes many single-byte, mul-

tifunction instructions. This enables a single instruction to ac-

complish multiple functions, such as DRSZ, DCOR, JID, and

LOAD/EXCHANGE instructions with post-incrementing and

post-decrementing, to name just a few examples. In many

cases, the instruction set can simultaneously execute as

many as three functions with the same single-byte instruc-

tion.

JID: (Jump Indirect); Single byte instruction; decodes exter-

nal events and jumps to corresponding service routines

(analogous to "DO CASE" statements in higher level lan-

guages).

LAID: (Load Accumulator-Indirect); Single byte look up table

instruction provides efficient data path from the program

memory to the CPU. This instruction can be used for table

lookup and to read the entire program memory for checksum

calculations.

RETSK: (Return Skip); Single byte instruction allows return

from subroutine and skips next instruction. Decision to

branch can be made in the subroutine itself, saving code.

AUTOINC/DEC: (Auto-Increment/Auto-Decrement); These

instructions use the two memory pointers B and X to effi-

ciently process a block of data (analogous to "FOR NEXT" in

higher level languages).

1.3.3 Bit-Level Control

Bit-level control over many of the microcontroller's I/O ports

provides a flexible means to ease layout concerns and save

board space. All members of the COP8 family provide the

ability to set, reset and test any individual bit in the data

memory address space, including memory-mapped I/O ports

and associated registers. Three memory-mapped pointers

handle register indirect addressing and software stack

pointer functions. The memory data pointers allow the option

of post-incrementing or post-decrementing with the data

movement

instructions

(LOAD/EXCHANGE).

And

15

memory-maped registers allow designers to optimize the

precise implementation of certain specific instructions.

1.4 PACKAGING/PIN EFFICIENCY

Real estate and board configuration considerations demand

maximum space and pin efficiency, particularly given today's

high integration and small product form factors. Microcontrol-

ler users try to avoid using large packages to get the I/O

needed. Large packages take valuable board space and in-

creases device cost, two trade-offs that microcontroller de-

signs can ill afford.

The COP8 family offers a wide range of packages and do not

waste pins: up to 90.9% (or 40 pins in the 44-pin package)

are devoted to useful I/O.

www.national.com

3

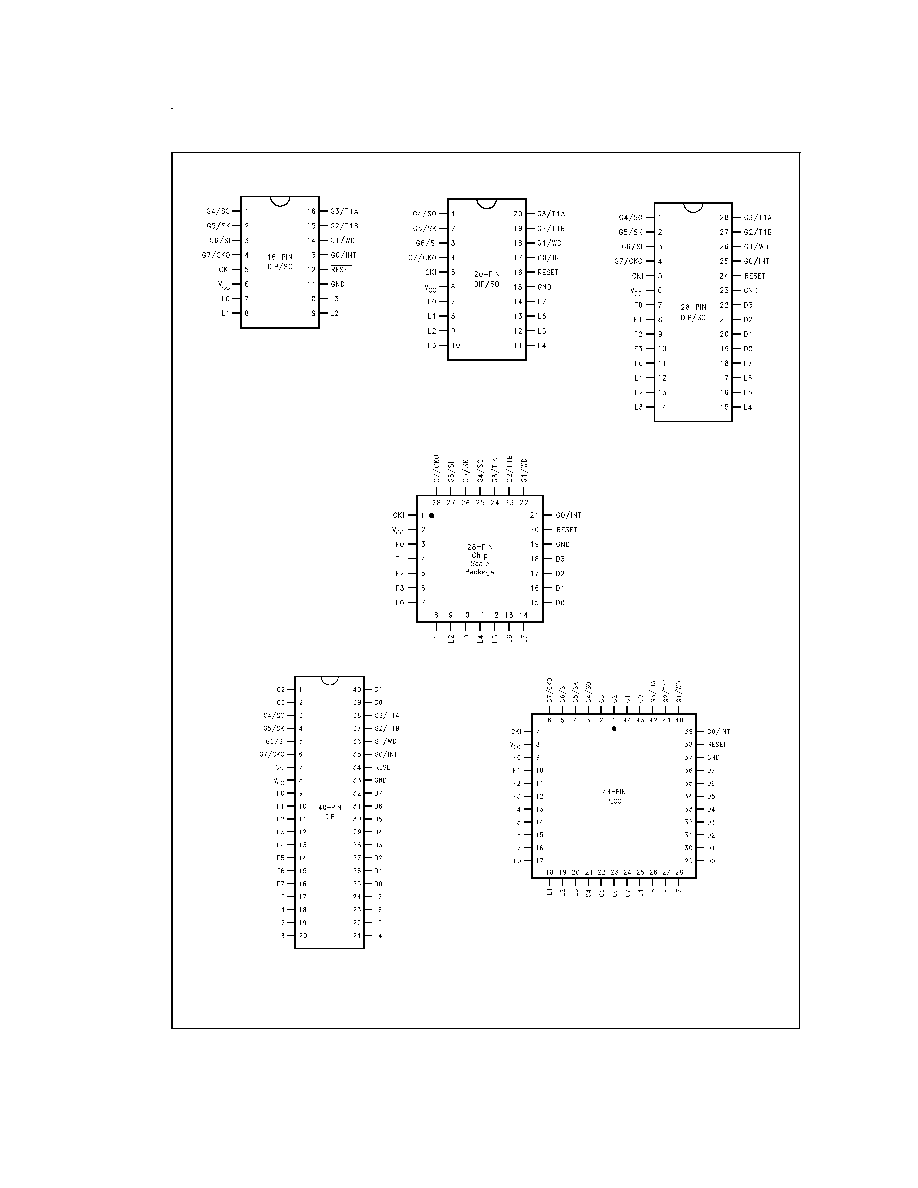

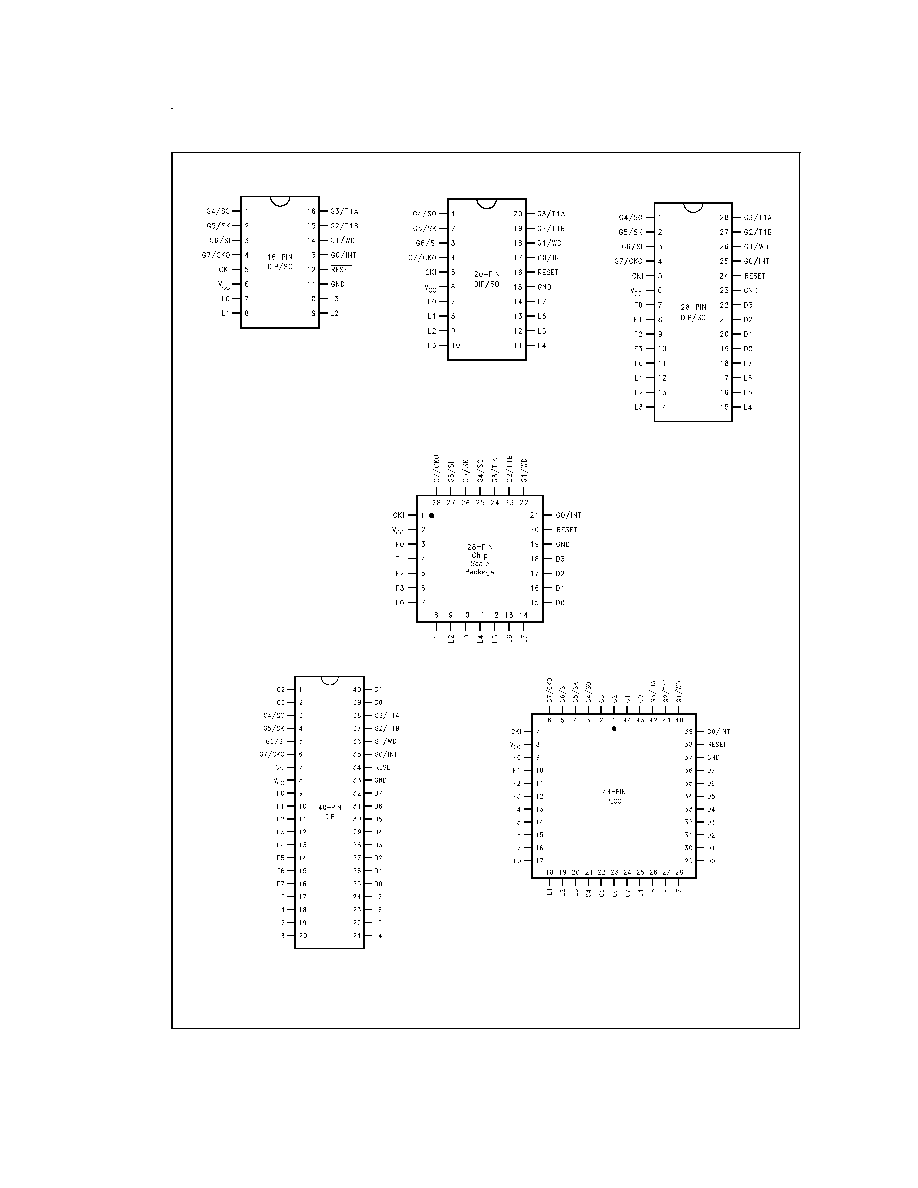

Connection Diagrams

DS012838-2

Top View

DS012838-3

Top View

DS012838-4

Top View

DS012838-39

Top View

DS012838-5

Top View

DS012838-6

Top View

FIGURE 2. Connection Diagrams

www.national.com

4

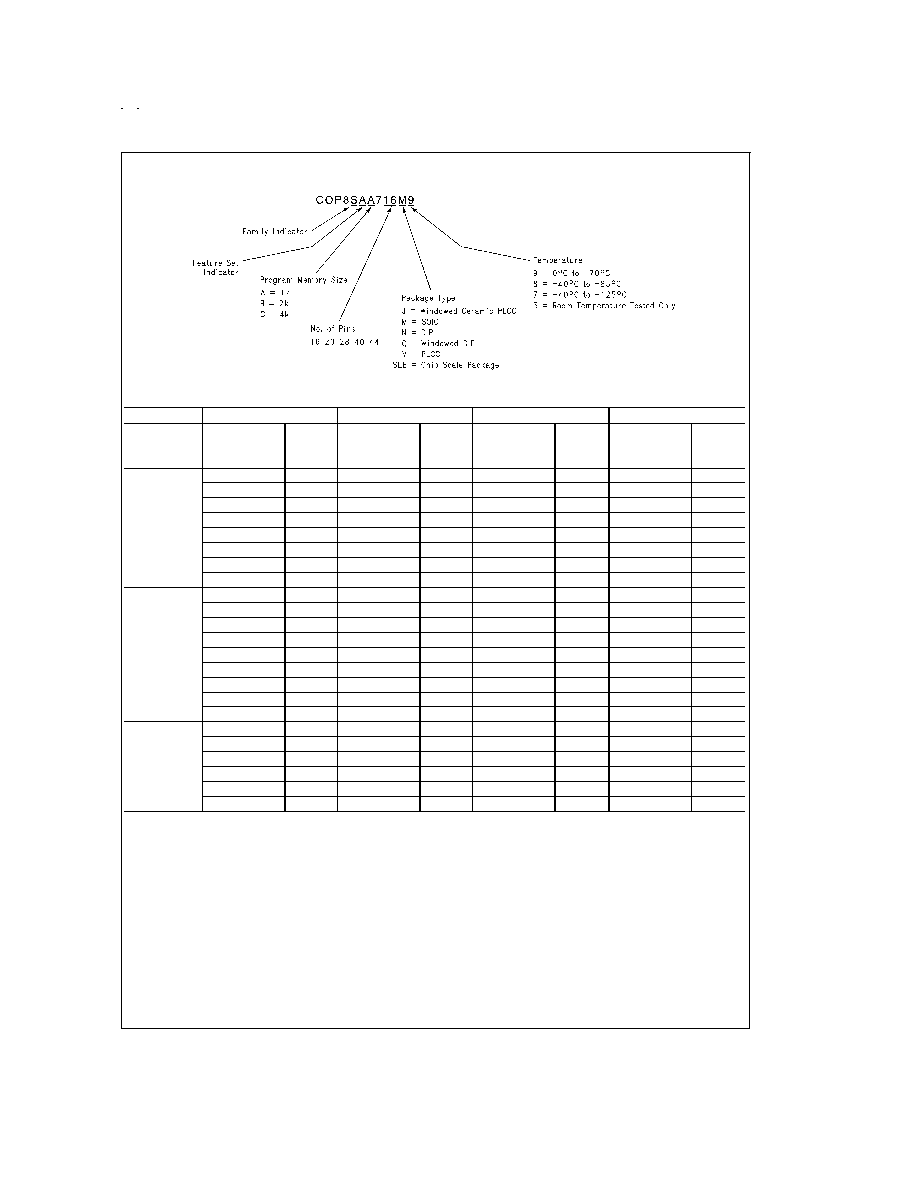

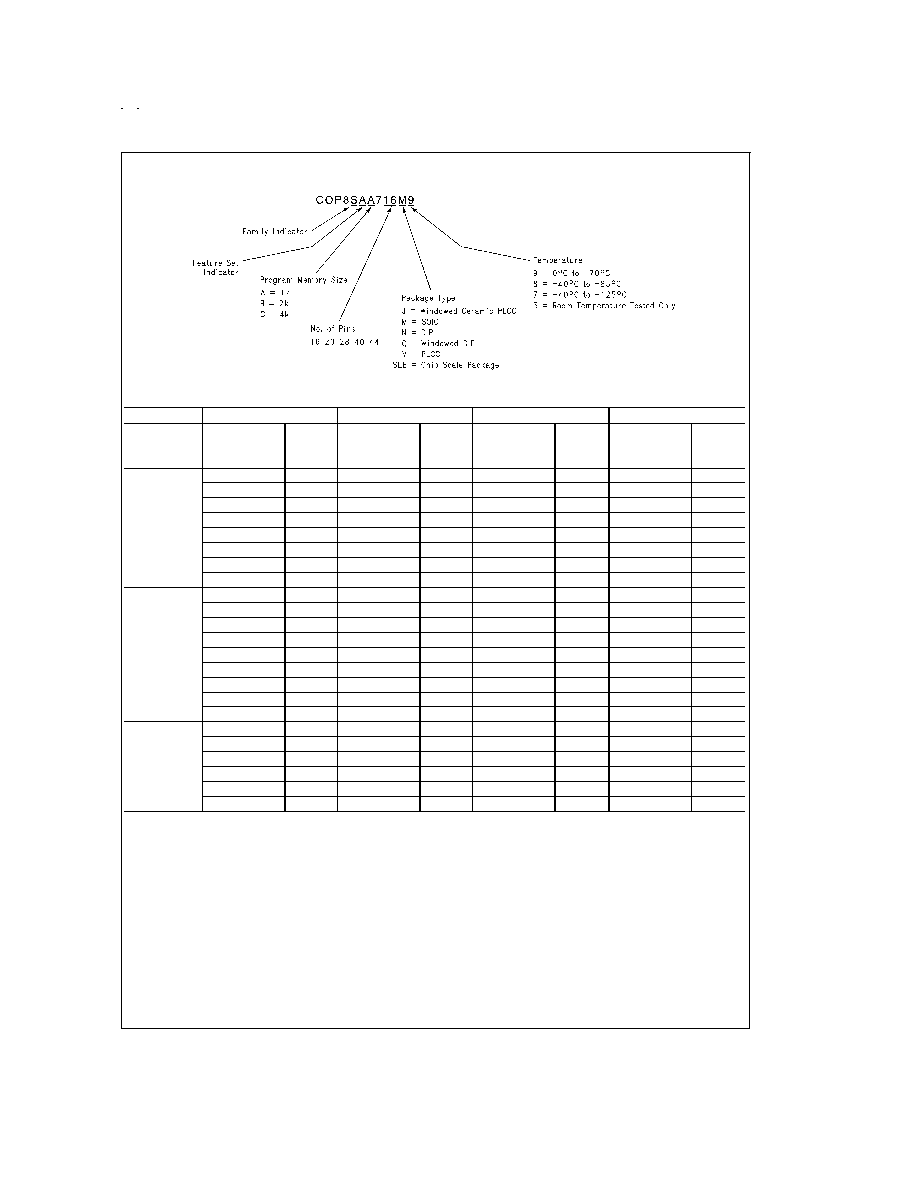

Ordering Information

1k EPROM

2k EPROM

4k EPROM

4k EPROM

Windowed

Device

Temperature

Order Number

Package

Order Number

Package

Order Number

Package

Order Number

Package

0∞C to +70∞C

COP8SAA716M9

16M

COP8SAA720M9

20M

COP8SAB720M9

20M

COP8SAC720M9

20M

COP8SAA728M9

28M

COP8SAB728M9

28M

COP8SAC728M9

28M

COP8SAA716N9

16N

COP8SAA720N9

20N

COP8SAB720N9

20N

COP8SAC720N9

20N

COP8SAC720Q3

20Q

COP8SAA728N9

28N

COP8SAB728N9

28N

COP8SAC728N9

28N

COP8SAC728Q3

28Q

COP8SAC740N9

40N

COP8SAC740Q3

40Q

COP8SAC744V9

44V

COP8SAC744J3

44J

-40∞C to +85∞C

COP8SAA716M8

16M

COP8SAA720M8

20M

COP8SAB720M8

20M

COP8SAC720M8

20M

COP8SAA728M8

28M

COP8SAB728M8

28M

COP8SAC728M8

28M

COP8SAA716N8

16N

COP8SAA720N8

20N

COP8SAB720N8

20N

COP8SAC720N8

20N

COP8SAA728N8

28N

COP8SAB728N8

28N

COP8SAC728N8

28N

COP8SAC740N8

40N

COP8SAC744V8

44V

COP8SAA7SLB8

SLB

COP8SAB7SLB8

SLB

COP8SAC7SLB8

SLB

-40∞C to

+125∞C

COP8SAC720M7

20M

COP8SAC728M7

28M

COP8SAC720N7

20N

COP8SAC728N7

28N

COP8SAC740N7

40N

COP8SAC744V7

44V

DS012838-8

FIGURE 3. Part Numbering Scheme

www.national.com

5