| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: DS1649J | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

TL F 7515

DS1649DS3649DS1679DS3679

Hex

TRI-STATE

TTL

to

MOS

Drivers

March 1986

DS1649 DS3649 DS1679 DS3679 Hex TRI-STATE

TTL

to MOS Drivers

General Description

The DS1649 DS3649 and DS1679 DS3679 are Hex

TRI-STATE MOS drivers with outputs designed to drive

large capacitive loads up to 500 pF associated with MOS

memory systems PNP input transistors are employed to re-

duce input currents allowing the large fan-out to these driv-

ers needed in memory systems The circuit has Schottky-

clamped transistor logic for minimum propagation delay

and TRI-STATE outputs for bus operation

The DS1649 DS3649 has a 15X resistor in series with the

outputs to dampen transients caused by the fast-switching

TRI-STATE

is a registered trademark of National Semiconductor Corp

output The DS1679 DS3679 has a direct low impedance

output for use with or without an external resistor

Features

Y

High speed capabilities

Typ 9 ns driving 50 pF

Typ 30 ns driving 500 pF

Y

TRI-STATE outputs for data bussing

Y

Built-in 15X damping resistor (DS1649 DS3649)

Y

Same pin-out as DM8096 and DM74366

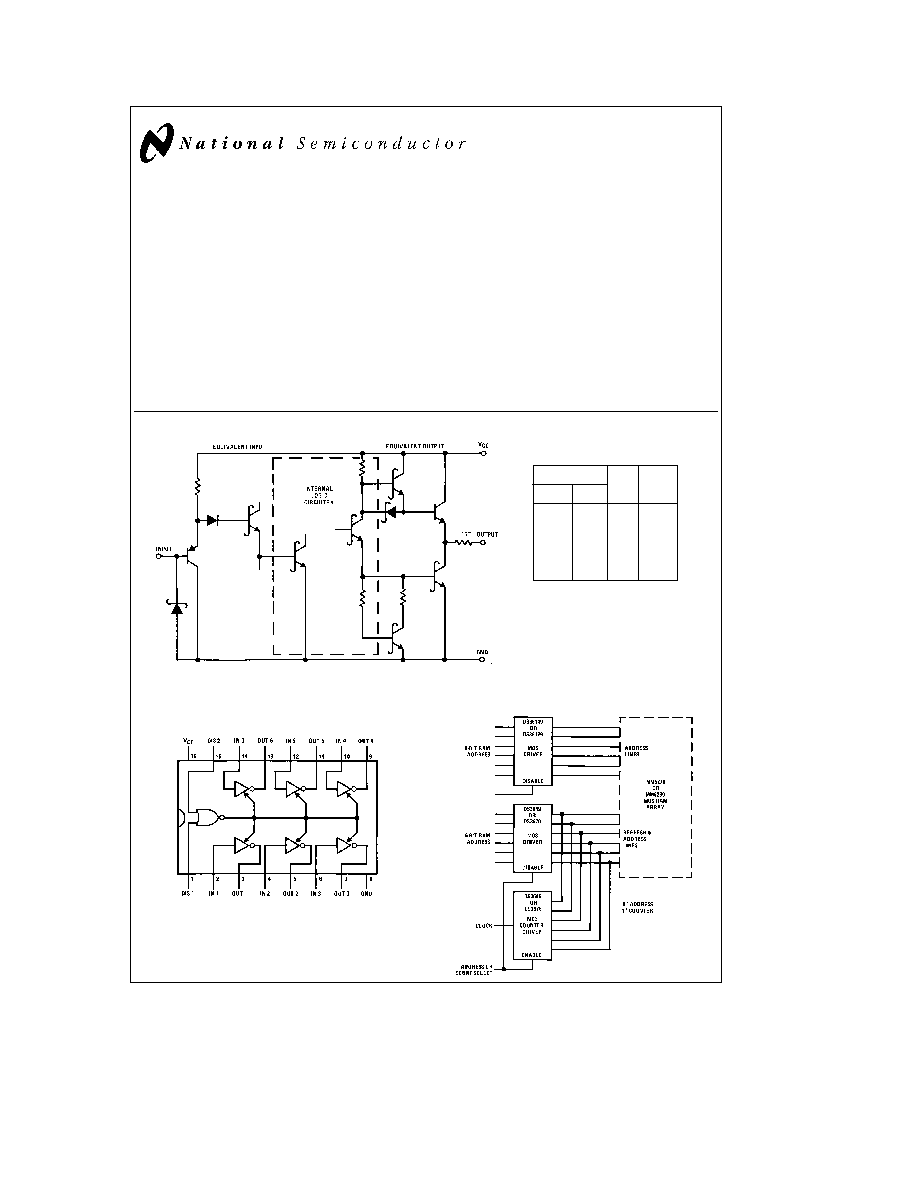

Schematic Diagram

DS1649 DS3649 only

TL F 7515 ≠ 1

Truth Table

Disable Input

Input Output

DIS 1

DIS 2

0

0

0

1

0

0

1

0

0

1

X

Hi-Z

1

0

X

Hi-Z

1

1

X

Hi-Z

X

e

Don't care

Hi-Z

e

TRI-STATE mode

Connection Diagram

Dual-In-Line Package

TL F 7515 ≠ 2

Top View

Order Number DS1649J DS3649J

DS1679J DS3679J DS3649N or DS3679N

See NS Package Number J16A or N16A

Typical Application

TL F 7515 ≠ 3

C1995 National Semiconductor Corporation

RRD-B30M105 Printed in U S A

Absolute Maximum Ratings

(Note 1)

If Military Aerospace specified devices are required

please contact the National Semiconductor Sales

Office Distributors for availability and specifications

Supply Voltage

7 0V

Logical ``1'' Input Voltage

7 0V

Logical ``0'' Input Voltage

b

1 5V

Storage Temperature Range

b

65 C to

a

150 C

Maximum Power Dissipation at 25 C

Cavity Package

1371 mW

Molded Package

1280 mW

Lead Temperature (Soldering 10 sec )

300 C

Operating Conditions

Min

Max

Units

Supply Voltage (V

CC

4 5

5 5

V

Temperature (T

A

)

DS1649 DS1679

b

55

a

125

C

DS3649 DS3679

0

a

70

C

Derate cavity package 9 1 mW C above 25 C derate molded package

10 2 mW C above 25 C

Electrical Characteristics

(Note 2 and 3)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

V

IN(1)

Logical ``1'' Input Voltage

2 0

V

V

IN(0)

Logical ``0'' Input Voltage

0 8

V

I

IN(1)

Logical ``1'' Input Current

V

CC

e

5 5V V

IN

e

5 5V

0 1

40

m

A

I

IN(0)

Logical ``0'' Input Current

V

CC

e

5 5V V

IN

e

0 5V

b

50

b

250

m

A

V

CLAMP

Input Clamp Voltage

V

CC

e

4 5V I

IN

e b

18 mA

b

0 75

b

1 2

V

V

OH

Logical ``1'' Output Voltage

V

CC

e

4 5V I

OH

e b

10 mA

DS1649 DS1679

2 7

3 6

V

(No Load)

DS3649 DS3679

2 8

3 6

V

OL

Logical ``0'' Output Voltage

V

CC

e

4 5V I

OL

e

10 mA

DS1649 DS1679

0 25

0 4

V

(No Load)

DS3649 DS3679

0 25

0 35

V

V

OH

Logical ``1'' Output Voltage

V

CC

e

4 5V I

OH

e b

1 0 mA

DS1649

2 4

3 5

V

(With Load)

DS1679

2 5

3 5

V

DS3649

2 6

3 5

V

DS3679

2 7

3 5

V

V

OL

Logical ``0'' Output Voltage

V

CC

e

4 5V I

OL

e

20 mA

DS1649

0 6

1 1

V

(With Load)

DS1679

0 4

0 5

V

DS3649

0 6

1 0

V

DS3679

0 4

0 5

V

I

1D

Logical ``1'' Drive Current

V

CC

e

4 5V V

OUT

e

0V (Note 4)

b

250

mA

I

0D

Logical ``0'' Drive Current

V

CC

e

4 5V V

OUT

e

4 5V (Note 4)

150

mA

Hi-Z

TRI-STATE Output Current

V

OUT

e

0 4V to 2 4V DIS1 or DIS2

e

2 0V

b

40

40

m

A

I

CC

Power Supply Current

V

CC

e

5 5V

One DIS Input

e

3 0V

42

75

mA

All Other Inputs

e

X

All Inputs

e

0V

11

20

mA

2

Switching Characteristics

(V

CC

e

5V T

A

e

25 C) (Note 4)

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

S

g

Storage Delay Negative Edge

(

Figure 1 )

C

L

e

50 pF

4 5

7

ns

C

L

e

500 pF

7 5

12

ns

t

S

g

Storage Delay Positive Edge

(

Figure 1 )

C

L

e

50 pF

5

8

ns

C

L

e

500 pF

8

13

ns

t

F

Fall Time

(

Figure 1 )

C

L

e

50 pF

5

8

ns

C

L

e

500 pF

22

35

ns

t

R

Rise Time

(

Figure 1 )

C

L

e

50 pF

6

9

ns

C

L

e

500 pF

21

35

ns

t

ZL

Delay from Disable Input to Logical ``0''

C

L

e

50 pF

10

15

ns

Level (from High Impedance State)

R

L

e

2 kX to V

CC

(

Figure 2 )

t

ZH

Delay from Disable Input to Logical ``1''

C

L

e

50 pF

8

15

ns

Level (from High Impedance State)

R

L

e

2 kX to GND (

Figure 2 )

t

LZ

Delay from Disable Input to High Impedance

C

L

e

50 pF

15

25

ns

State (from Logical ``0'' Level)

R

L

e

400X to V

CC

(

Figure 3 )

t

HZ

Delay from Disable Input to High Impedance

C

L

e

50 pF

10

25

ns

State (from Logical ``1'' Level)

R

L

e

400X to GND (

Figure 3 )

Note 1

``Absolute Maximum Ratings'' are those values beyond which the safety of the device cannot be guaranteed Except for ``Operating Temperature Range''

they are not meant to imply that the devices should be operated at these limits The table of ``Electrical Characteristics'' provides conditions for actual device

operation

Note 2

Unless otherwise specified min max limits apply across the

b

55 C to

a

125 C temperature range for the DS1649 and DS1679 and across the 0 C to

a

70 C range for the DS3649 and DS3679 All typical values are for T

A

e

25 C and V

CC

e

5V

Note 3

All currents into device pins shown as positive out of device pins as negative all voltages referenced to ground unless otherwise noted All values shown

as max or min on absolute value basis

Note 4

When measuring output drive current and switching response for the DS1679 and DS3679 a 15X resistor should be placed in series with each output This

resistor is internal to the DS1649 DS3649 and need not be added

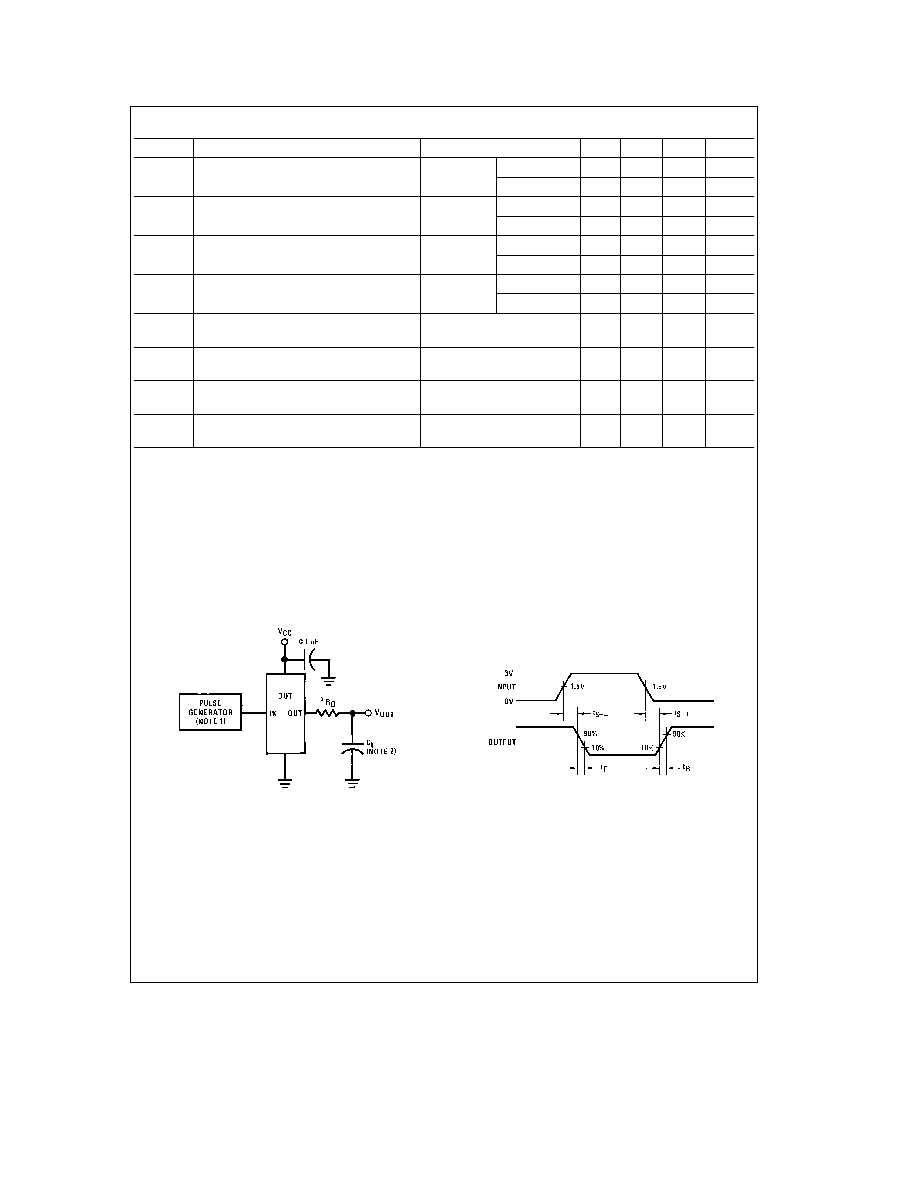

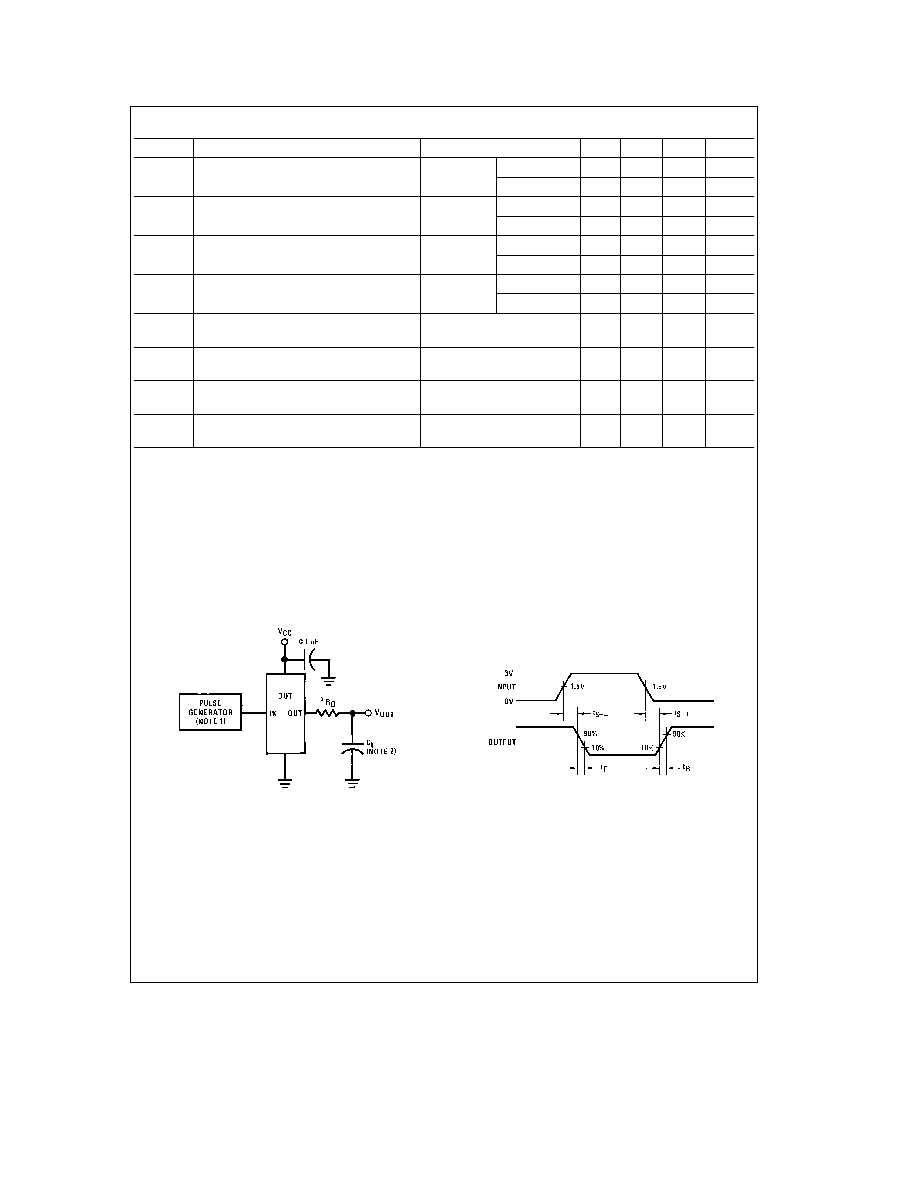

AC Test Circuits and Switching Time Waveforms

t

S

g

t

S

'

t

R

t

F

TL F 7515 ≠ 4

TL F 7515 ≠ 5

FIGURE 1

3

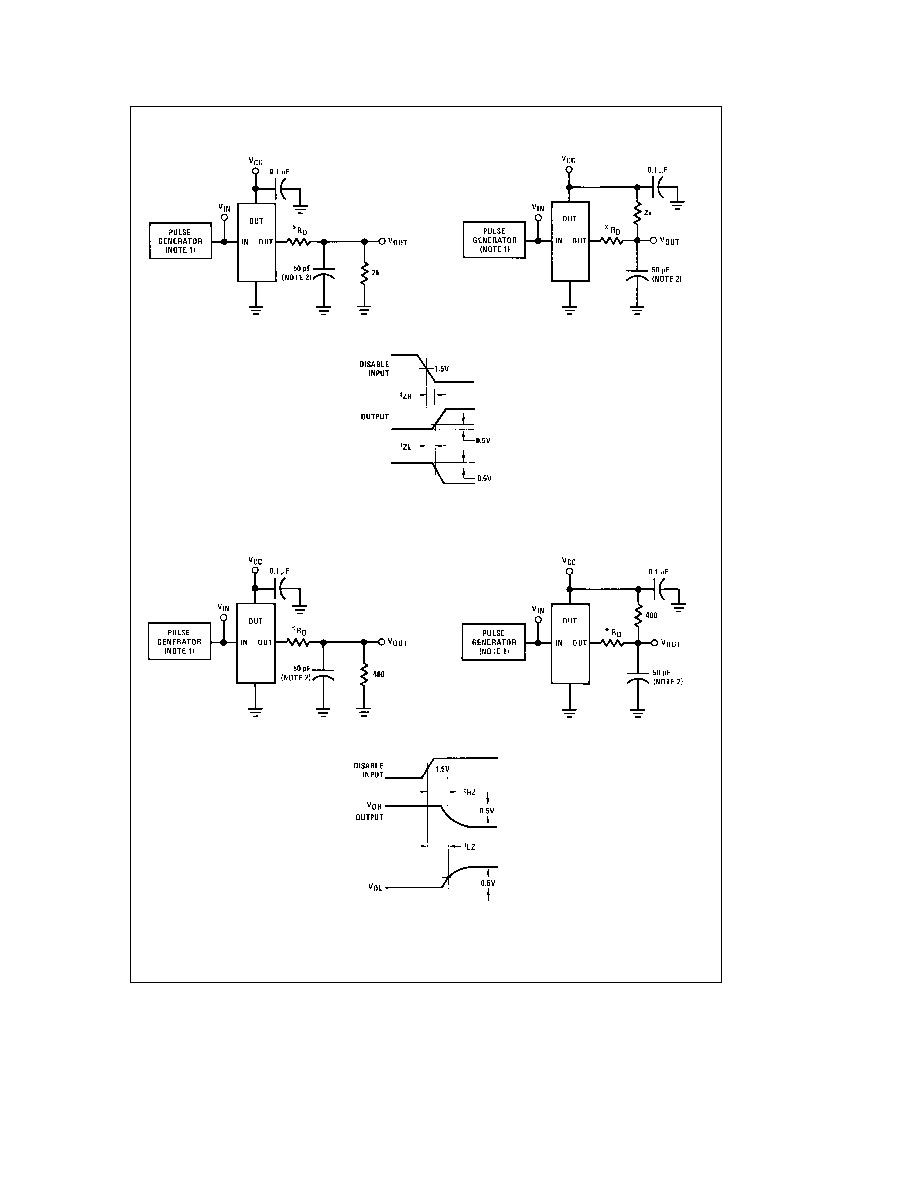

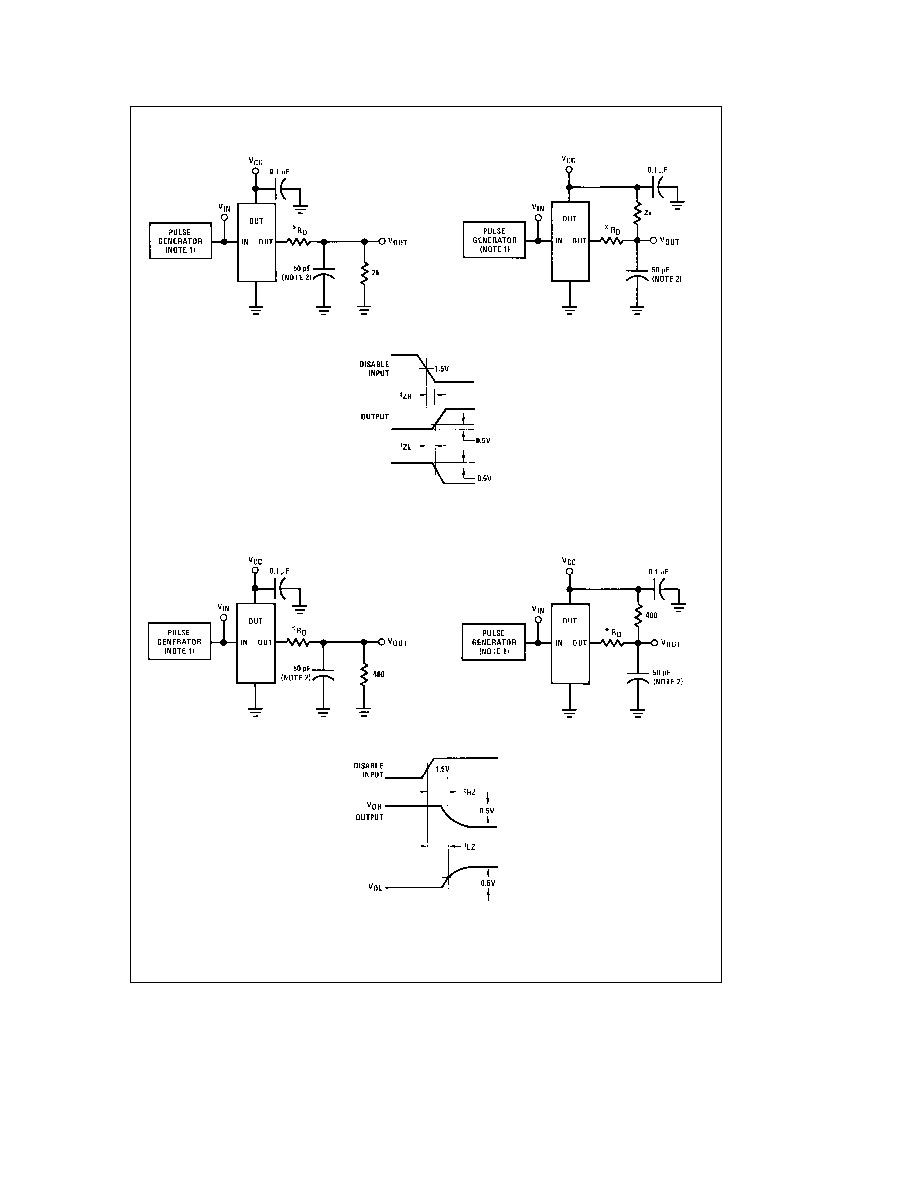

AC Test Circuits and Switching Time Waveforms

(Continued)

t

ZH

TL F 7515 ≠ 6

t

ZL

TL F 7515 ≠ 7

TL F 7515 ≠ 8

FIGURE 2

t

HZ

TL F 7515 ≠ 9

t

LZ

TL F 7515 ≠ 10

TL F 7515 ≠ 11

FIGURE 3

Internal on DS1649 and DS3649

Note 1

The pulse generator has the following characteristics Z

OUT

e

50X and PRR

s

1 MHz Rise and fall times between 10% and 90% points

s

5 ns

Note 2

C

L

includes probe and jig capacitance

4

Physical Dimensions

inches (millimeters)

Ceramic Dual-In-Line Package (J)

Order Number DS1649J DS3649J

DS1679J or DS3679J

NS Package Number J16A

5