| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: LM1262 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

LM1262

200 MHz I

2

C Compatible RGB Video Amplifier System

with OSD and DACs

General Description

The LM1262 pre-amp is an integrated CMOS CRT pre-amp.

The IC is I

2

C compatible, and allows control of all the pa-

rameters necessary to directly setup and adjust the gain and

contrast in the CRT display. Brightness and bias can be

controlled through the DAC outputs, and is well matched to

the LM2479 and LM2480 integrated bias clamp IC.

The LM1262 pre-amp is designed to work in cooperation

with the LM246X high gain driver family.

Black level clamping of the signal is carried out directly on

the AC coupled input signal into the high impedance pream-

plifier input, thus eliminating the need for additional black

level clamp capacitors.

The IC is packaged in an industry standard 24-lead DIP

molded plastic package.

Features

n

I

2

C compatible interface

n

4 external 8-bit DACs for bus controlled Bias and

Brightness

n

Vertical blank from sandcastle or input at pin 13 OR'ed

with horz. blank signal, option selected by I

2

C

n

Contrast and brightness updates synchronous with

vertical blank, enabled by I

2

C

n

Video set to black level through I

2

C

n

Suitable for use with discrete or integrated clamp, with

software configurable Brightness mixer

n

Power Save (Green) Mode, 80% power reduction

n

Matched to 11-lead LM246X driver

Applications

n

High end 19" and 21" bus controlled monitors with OSD

n

1600 X 1200, 85 Hz or higher applications

n

Low cost and high performance system with LM246X

driver

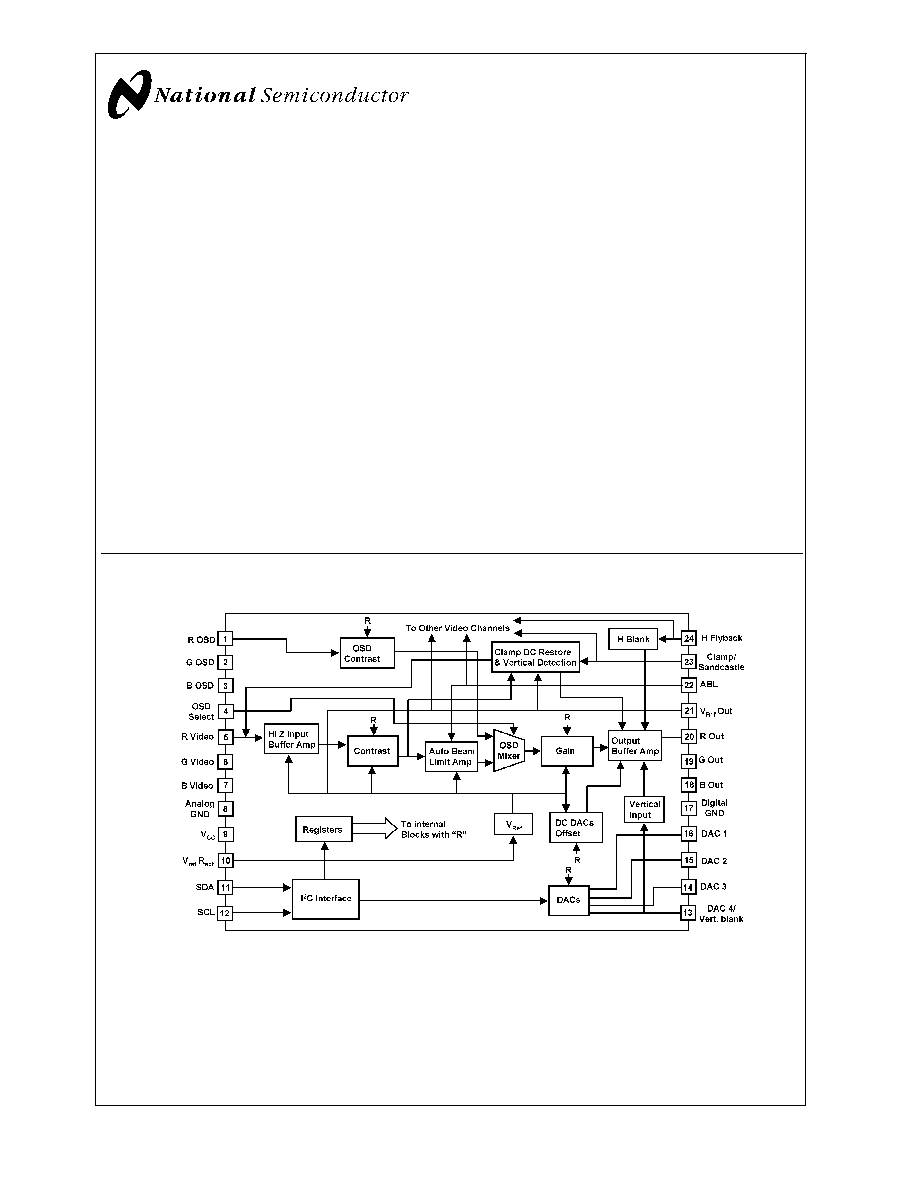

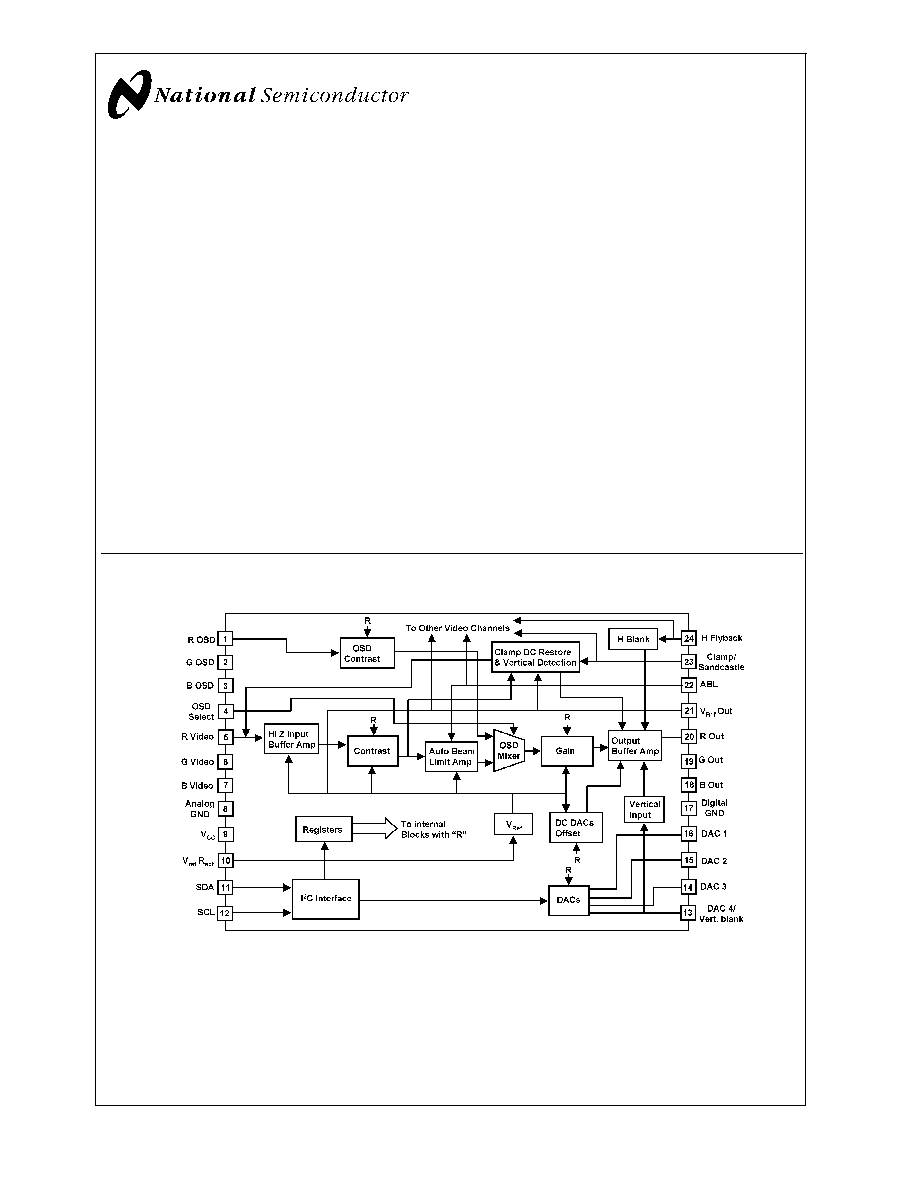

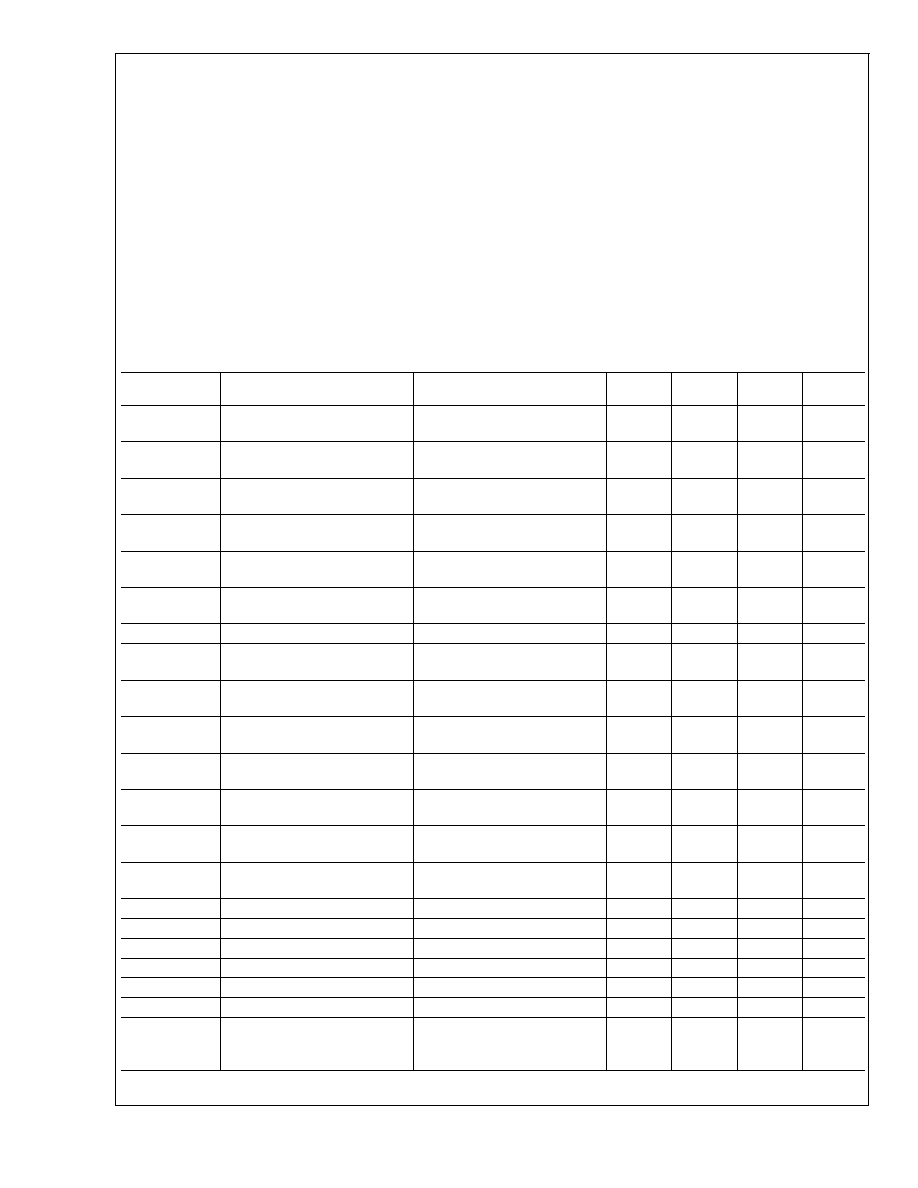

Block and Connection Diagram

DS200404-1

FIGURE 1. Order Number LM1262NA

See NS Package Number N24D

March 2002

LM1262

200

MHz

I

2

C

Compatible

RGB

V

ideo

Amplifier

System

with

OSD

and

DACs

© 2002 National Semiconductor Corporation

DS200404

www.national.com

Absolute Maximum Ratings

(Notes 1, 3)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage, Pin 9

6.0V

Peak Video Output Source Current

(Any One Amp)

Pins 18, 19, or 20

28 mA

Voltage at Any

Input Pin (V

IN

)

V

CC

+0.5

>

V

IN

>

-0.5V

Power Dissipation (P

D

)

(Above 25∞C Derate based on

JA

and T

J

)

2.4W

Thermal Resistance to Ambient (

JA

)

51∞C/W

Thermal Resistance to Case (

JC

)

32∞C/W

Junction Temperature (T

J

)

150∞C

ESD Susceptibility (Note 4)

3.5 kV

ESD Machine Model (Note 5)

350V

Storage Temperature

-65∞C to +150∞C

Lead Temperature

(Soldering, 10 sec.)

265∞C

Operating Ratings

(Note 2)

Temperature Range

0∞C to 70∞C

Supply Voltage (V

CC

)

4.75V

<

V

CC

<

5.25V

Video Inputs

0.0V

<

V

IN

<

1.0V

p-p

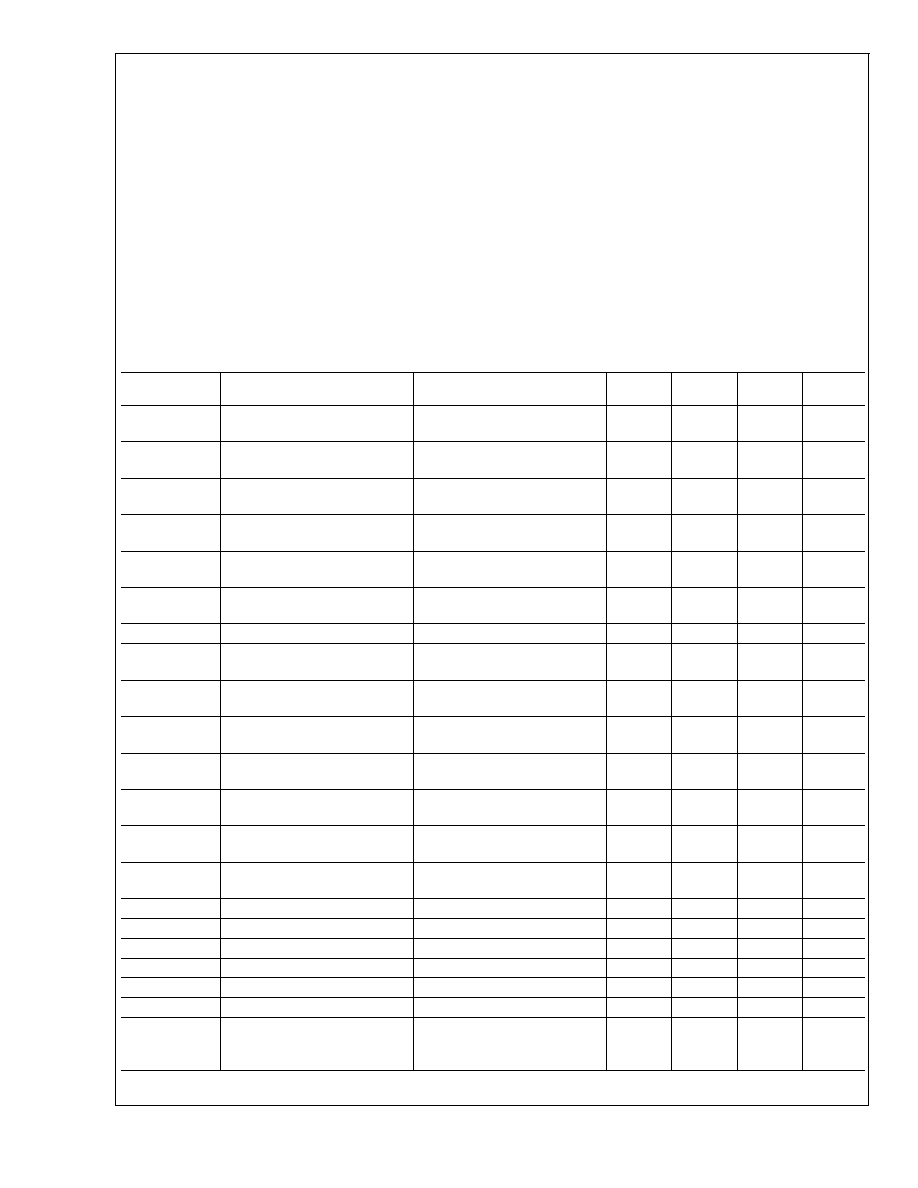

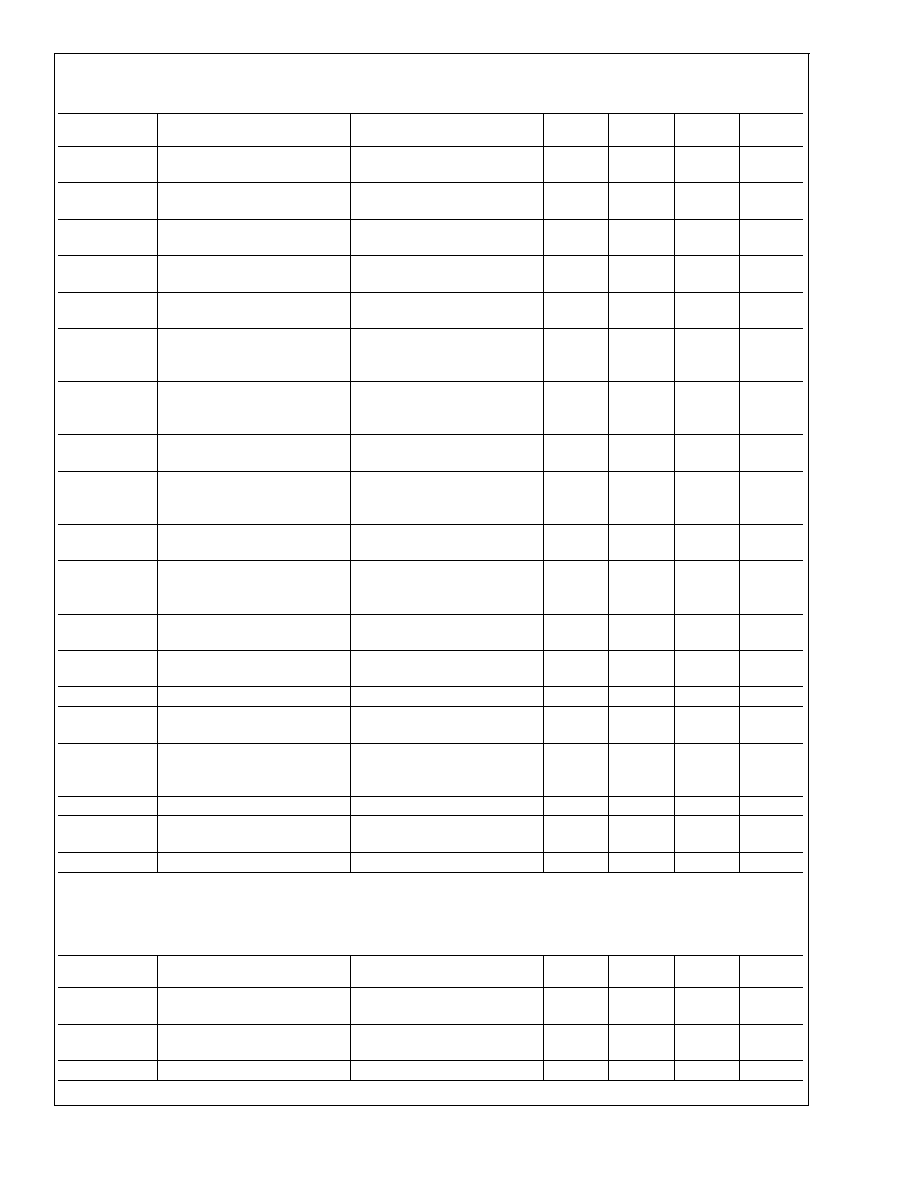

Active Video Signal Electrical Characteristics

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Signal Output = 2V

P-P

.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

I

S

Maximum Supply Current

Test Setting 1, R

L

=

(Note

8)

170

230

mA

I

S-PS

Maximum Supply Current,

Power Save Mode

Test Setting 1, R

L

=

, Bit 1 of

Reg. 9 = 1 (Note 8)

45

mA

LE

Linearity Error

Test Setting 4, Triangular

signal input source (Note 9)

5

%

V

O Blk Typ

Typical Video Black Level

Output

Test Setting 4, No AC Input

Signal

0.9

1.1

1.3

VDC

V

O Blk Step

Video Black Level Step Size

Test Setting 4, No AC Input

Signal

80

110

140

mV

V

O White-Max

White Level Video Output

Voltage

Test Setting 3, Video in = 0.7V

4.0

4.3

V

V

Blank

Blanked Output Level

Test Setting 4, AC Input Signal

0

0.05

0.2

V

t

r

Rise Time

10% to 90%, Test Setting 4,

AC Input Signal (Note 10)

1.9

ns

OS

R

Overshoot (Rising Edge)

Test Setting 4, AC Input Signal

(Note 10)

6

%

t

f

Fall Time

90% to 10%, Test Setting 4,

AC Input Signal (Note 10)

2.0

ns

OS

F

Overshoot (Falling Edge)

Test Setting 4, AC Input Signal

(Note 10)

8

%

f(-3 dB)

Video Amplifier Bandwidth

(Note 13)

Test Setting 4, V

O

=2V

P-P

200

MHz

V

sep

10kHz

Video Amplifier 10 kHz

Isolation

Test Setting 8 (Note 14)

-70

dB

V

sep

10MHz

Video Amplifier 10 MHz

Isolation

Test Setting 8 (Note 14)

-50

dB

A

V Max

Maximum Voltage Gain

Test Setting 8, AC Input Signal

3.90

4.15

4.40

V/V

A

V 1/2

Contrast

@

50% Level

Test Setting 5, AC Input Signal

-10

dB

A

V Min

Maximum Contrast Attenuation

Test Setting 2, AC Input Signal

-20

dB

A

V Gain 1/2

Gain

@

50% Level

Test Setting 6, AC Input Signal

-5

dB

A

V Gain Min

Maximum Gain Attenuation

Test Setting 7, AC Input Signal

-10

dB

A

V Match

Absolute Gain Match

@

A

V Max

Test Setting 3, AC Input Signal

±

0.5

dB

A

V Track

Gain Change between

Amplifiers

Tracking when changing from

Test Setting 8 to Test Setting 5

(Note 11)

±

0.5

dB

LM1262

www.national.com

2

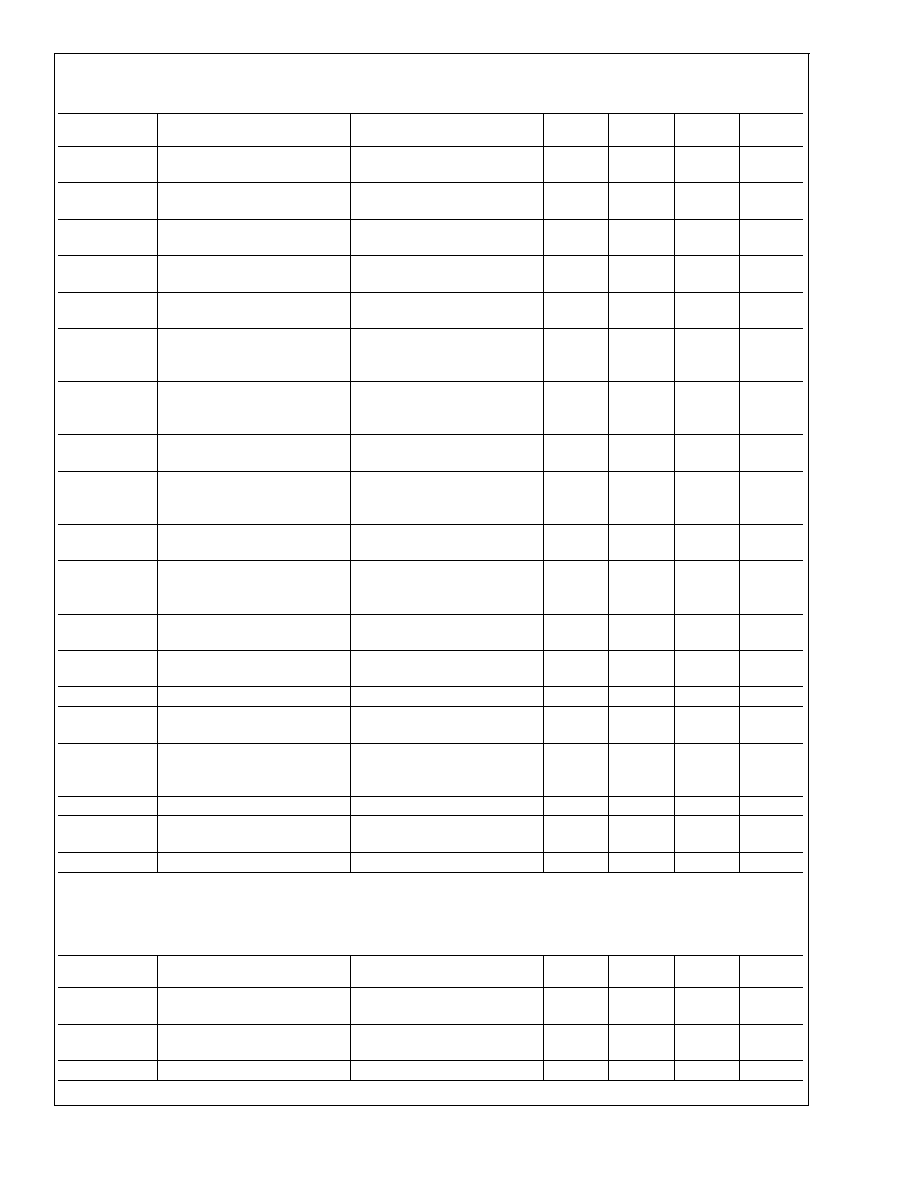

Active Video Signal Electrical Characteristics

(Continued)

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Signal Output = 2V

P-P

.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

V

ABL TH

ABL Control Upper Limit

Test Setting 4, AC Input Signal

(Note 12)

5

V

V

ABL Range

ABL Active Range Control

Voltage

Test Setting 4, AC Input Signal

(Note 12)

2.7

V

A

ABL

ABL Control Range

Test Setting 4, AC Input Signal

(Note 12)

-6

-8

dB

I

ABL Active

ABL Input Bias Current during

ABL

Test Setting 4, AC Input

Signal, V

ABL

= 2V (Note 12)

0

10

µA

I

ABL Max

ABL Input Current Clamp Sink

Capability

Test Setting 4, AC Input Signal

(Note 12)

1

mA

V

Vert Bnk Off

Vertical Blank Gate Low

Input Voltage at pin 13

Vertical Blank Comparators Off

Register B set to 0x02 (Note

18)

1.0

V

V

Vert Bnk On

Vertical Blank Gate High

Input Voltage at pin 13

Vertical Blank Comparators On

Register B set to 0x02 (Note

18)

2.6

V

I

Vert Bnk Low

Vertical Blank Gate Low

Input Current at pin 13

V

13

= 0V, Register B set to

0x02 (Note 18)

-4.0

µA

I

Vert Bnk High

Vertical Blank Gate High

Input Current at pin 13

V

13

= V

CC

, Register B set to

0x02 (Note 18)

(internal 50k resistor to ground)

100

µA

V

Vert Bnk Off

Vertical Blank Gate Low

Input Voltage at pin 23

Vertical Blank Comparators Off

Register B set to 0x06

0.7

V

V

Vert Bnk On

Vertical Blank Gate High

Input Voltage at pin 23

Vertical Blank Comparators On

Register B set to 0x06 (Note

16)

1.2

3.2

V

V

Clamp Min

Horizontal Clamp Gate High

Input Voltage

Horizontal Clamp Comparators

On

3.8

V

I

Clamp

Clamp Gate Input Current

V

23

= 0V to V

CC

- 1V,

Register B set to 0x06

-5

0.1

10

µA

t

PW Clamp

Back Porch Clamp Pulse Width

(Note 15)

200

ns

t

Clamp-Video

End of Clamp Pulse to Start of

Active Video

Limit is guaranteed by design

200

ns

t

PW SandClamp

Sandcastle Clamp Pulse Width

Horizontal Clamp Comparators

On Register B set to 0x06

(Note 16)

0.20

1.20

µsec

R

In-Video

Input Resistance

Test Setting (4)

20

M

V

Ref

Out

V

Ref

Output Voltage

10 k

, 1% Resistor; Pin 10 to

GND

1.25

1.40

1.55

V

V

Spot

Spot Killer Voltage

V

CC

Adjusted to Activate

3.4

4.0

4.25

V

OSD Electrical Characteristics

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Signal Output = 2V

P-P

, Test Set-

ting 8.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

V

OSD-L

OSD Input Low Input

Operating Range

OSD Inputs are Selected

1.2

V

V

OSD-H

OSD Input High Input

Operating Range

OSD Inputs are Selected

2.5

V

I

OSD

OSD Input Current

V

OSD

= 0V to V

CC

- 1V

-5

0.1

10

µA

LM1262

www.national.com

3

OSD Electrical Characteristics

(Continued)

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Signal Output = 2V

P-P

, Test Set-

ting 8.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

V

OSD-Sel-L

OSD Select Low Input

Operating Range

Video Inputs are Selected

1.2

V

V

OSD-Sel-H

OSD Select High Input

Operating Range

OSD Inputs are Selected

3.5

V

I

OSD-Sel

OSD Select Input Current

V

OSD-Sel

= 0V to V

CC

- 1V

-5

0.1

10

µA

V

O-OSD(Blk)

OSD

Black Level Output

Voltage, Difference from Video

Output

Register 08 = 18, Minimum

Video Black Level

±

45

±

150

mV

V

O-OSD(Blk)

Range of OSD Black Level

Output Voltage between the 3

Channels

Register 08 = 18, Minimum

Video Black Level

-100

0

+100

mV

V

OSD-out

OSD Output Voltage, Percent

of Maximum Video Out

Register 08 = 18, Minimum

Video Black Level

85

95

105

%

V

OSD-out

OSD Output V

P-P

Attenuation

Register 08 = 08

52

57

62

%

V

OSD-out

(Match)

Output Match between

Channels

Register 08 = 18

±

5.0

%

V

OSD-out

(Track)

Output Variation between

Channels

Register 08 Changed from 18

to 08

±

3.0

±

5.0

%

t

OSD/OSD S

Output Skew Time between

OSD and OSD Select

Measured from 50% Point on

all Waveforms

±

2.0

ns

V

feed

10 kHz

Video Feedthrough into OSD

OSD Inputs = 0V

-70

dB

V

feed

10 MHz

Video Feedthrough into OSD

OSD Inputs = 0V

-60

dB

External DAC Signals Electrical Characteristics

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Signal Output = 2V

P-P

. The follow-

ing apply for all four external DACs.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

V

Min DAC

Min DAC Output Voltage

Value = 00h

0.5

0.75

V

V

Max DAC

Mode 00

Max DAC Output Voltage

Value = FFh, DCF[1:0] = 00h

(no load)

3.6

4.2

V

V

Max DAC

Mode 11

Max Output Voltage of DACs

1≠3 in DCF Mode 11

Value = FFh, DCF[1:0] = 11h,

DAC4 Value = 00h

2.05

2.40

2.75

V

V

Max DAC

(Temp)

Variation of any DAC output

voltage with temperature

0∞C

<

T

<

70∞C ambient

±

0.5

mV/deg

V

Max DAC

(V

CC

)

Variation of any DAC output

voltage with V

CC

4.75V

<

V

CC

<

5.25V

±

50

mV/V

Linearity

Linearity of DAC Over its

Range

5

%

Monotonicity

Monotonicity of the DAC

Excluding dead zones at limits

of DAC

±

0.5

LSB

External Interface Signals Electrical Characteristics

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Output = 2V

P-P

.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

V

l

(I

2

C)

I

2

C Low Input Voltage

SDA or SCL Inputs

1.5

V

V

h

(I

2

C)

I

2

C High Input Voltage

SDA or SCL Inputs

3.0

V

LM1262

www.national.com

4

External Interface Signals Electrical Characteristics

(Continued)

Unless otherwise noted: T

A

= 25∞C, V

CC

= +5V, V

IN

= 0.7V, V

ABL

= V

CC

, C

L

= 5 pF, Video Output = 2V

P-P

.

Symbol

Parameter

Conditions

Min

(Note 7)

Typ

(Note 6)

Max

(Note 7)

Units

t

H-Blank on

H-Blank Time Delay from Zero

Crossing Point of H Flyback

Rising Edge of the Flyback

Signal

50

ns

t

H-Blank off

H-Blank Time Delay from Zero

Crossing Point of H Flyback

Falling Edge of the Flyback

Signal

50

ns

I

In Threshold

I

In

H-Blank Detection

Threshold

-20

µA

I

In-Operating

Minimum -- Insure Normal

Operation

Maximum -- Should Not

Exceed in Normal Operation

Lowest Operating Horizontal

Frequency in Given Application

(Note 17)

-30

-300

µA

I

In Flyback

Peak Current during Flyback

Period, Recommended Design

Range

Operating Range for all

Horizontal Scan Frequencies,

Maximum Current Should Not

Exceed 2 mA (Note 17)

0.5

1.5

2.0

mA

Note 1: Limits of Absolute Maximum Ratings indicate limits below which damage to the device must not occur.

Note 2: Limits of operating ratings indicate required boundaries of conditions for which the device is functional, but may not meet specific performance limits.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: Human body model, 100 pF discharged through a 1.5 k

resistor.

Note 5: Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200 pF cap is charged to the specified voltage, then discharged directly into the

IC with no external series resistor (resistance of discharge path must be under 50

).

Note 6: Typical specifications are specified at +25∞C and represent the most likely parametric norm.

Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

Note 8: The supply current specified is the quiescent current for V

CC

with R

L

=

. Load resistors are not required and are not used in the test circuit, therefore all

the supply current is used by the pre-amp.

Note 9: Linearity Error is the variation in step height of a 16 step staircase input signal waveform with 0.7 V

P-P

level at the input, subdivided into 16 equal steps,

with each step approximately 100 ns in width.

Note 10: Input from signal generator: t

r

, t

f

<

1 ns. Scope and generator response used for testing: t

r

= 1.1 ns, t

f

= 0.9 ns. Using the RSS technique the scope and

generator response have been removed from the output rise and fall times.

Note 11:

A

V

track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three gain stages. It is the difference in

gain change between any two amplifiers with the contrast set to A

V 1/2

and measured relative to the A

V

max condition. For example, at A

V

max the three amplifiers'

gains might be 12.1 dB, 11.9 dB, and 11.8 dB and change to 2.2 dB, 1.9 dB and 1.7 dB respectively for contrast set to A

V 1/2

. This yields a typical gain change of

10.0 dB with a tracking change of

±

0.2 dB.

Note 12: ABL should provide smooth decrease in gain over the operational range of 0 dB to ≠6 dB

A

ABL

= A(V

ABL

= V

ABL Max Gain

) - A(V

ABL

= V

ABL Min Gain

)

Beyond ≠6 dB the gain characteristics, linearity, pulse response, and/or behavior may depart from normal values.

Note 13: Adjust input frequency from 10 MHz (A

V

max reference level) to the -3 dB corner frequency (f

-3 dB

).

Note 14: Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier

inputs to simulate generator loading. Repeat test at f

IN

= 10 MHz for V

sep 10 MHz

.

Note 15: A minimum pulse width of 200 ns is guaranteed for a horizontal line of 15 kHz. This limit is guaranteed by design. If a lower line rate is used then a longer

clamp pulse may be required.

Note 16: The internal circuit detects the vertical blank only when this signal is present in the sandcastle input. There is typically an 800 nsec delay in detecting the

vertical blank signal. If only the horizontal clamp is present the vertical blank will not be activated. Rise and fall times of the sandcastle input signal should be 10 nsec

or faster.

Note 17: Limits met by matching the external resistor going to pin 24 to the H Flyback voltage.

Note 18: A 4.7 k

resistor must be in series with pin 13 when this pin is the input for vertical blanking. When the LM1262 is first turned on the default condition for

pin 13 is for the DAC4 output. Under this condition pin 13 will be damaged by the vertical blanking input if a series resistor is not used.

LM1262

www.national.com

5