1/18

MSC7110-01/7112-01

° Semiconductor

FEDL7110-03

GENERAL DESCRIPTION

The MSC7110-01/MSC7112-01 is a display controller to display the timer of video tape recorder,

channel operation, and other infomaiton by a vaccum fluorescent display tube.

Display data is input by serial transfer from microcontroller.

FEATURES

∑ Provides the interface with a microcontroller by three signal lines. : DATA IN, CLOCK, and LOAD

∑ Driver output can directly be connected to a vaccum fluorescent display tube without a

pull-down resistor.

∑ Display is turned on by dynamic drive mode.

∑ The number of display digits are programmable in the range of : 1 to 12 digits (MSC7112-01)

1 to 16 digits (MSC7110-01)

∑ 12-segment driver output

: 16 driver outputs (MSC7112-01)

12 driver outputs (MSC7110-01)

∑ The LED drivers can turn on 5 outputs statically.

∑ RAM data can directly be displayed.

∑ The brightness adjustment is programmable and brightness can be adjusted every 1/15

step.

∑ Built-in power-on-reset circuit

∑ The vacuum fluorescent display tube driver outputs high withstand voltage : V

DD

-V

EE

=45V (max).

∑ Logic supply voltage

: V

DD

=5V

±

10%

∑ Package options:

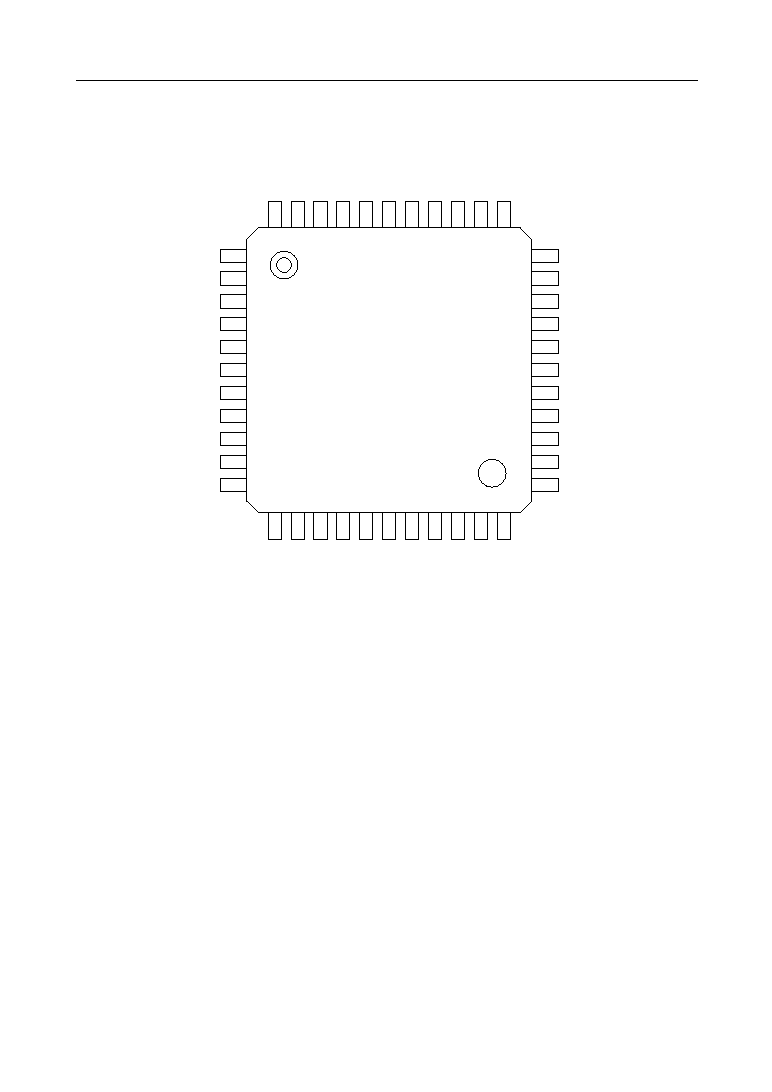

42-pin plastic SDIP (SDIP42-P-600-1.778) : (Product name : MSC7112-01SS)

44-pin plastic QFP (QFP44-P-910-0.80-2K) : (Product name : MSC7110-01GS-2K/MSC7112-01GS-2K)

° Semiconductor

MSC7110-01/7112-01

12-Segment

• 16-Digit or 16-Segment • 12-Digit Display Controller/Driver

FEDL7110-03

This version: Sep. 2000

Previous version: Nov. 1997