1

Oki Semiconductor

KGL4215

10-Gbps GaAs Decision Circuit

INTRODUCTION

Oki Semiconductor's KGL4215 is a 10-Gbps Decision Circuit with Limiting Amplifier and Flip Flop that

is designed for ultra high-speed digital communications systems. The KGL415 uses 0.2-µm gate length

GaAs MESFET and Oki's unique MCFF ( Memory Cell type Flip Flop ) technology to achieve operating

speeds of 10-Gbps or more. The KGL4215 is available as a 24-pin ceramic packaged device. Due to the

KGL4215's high sensitivity, capacitive coupling is recommended for the IC's interface.

FEATURES

∑ High-speed operation: 10-Gbps data rate (min)

∑ Low-power dissipation: 600 mW (typ.) using 2-V power-supply

∑ 0.2-µm gate length GaAs MESFET process

∑ MCFF ( Memory Cell type Flip Flop ) technology

∑ 24-pin ceramic package

APPLICATION

∑ High-speed optical communication systems: 10 Gbps

∑ High-speed test equipment

s

KGL4215

s

≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠≠

2

Oki Semiconductor

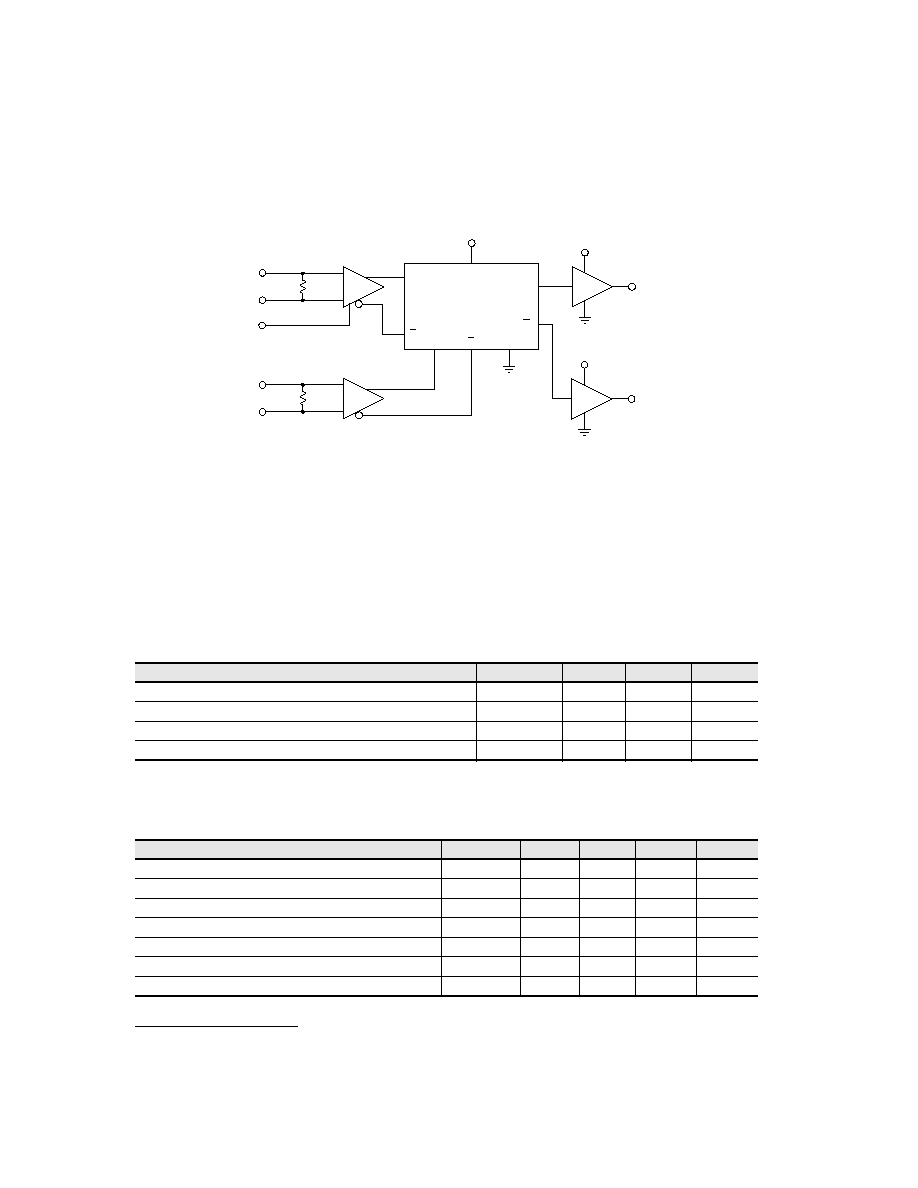

BLOCK DIAGRAM

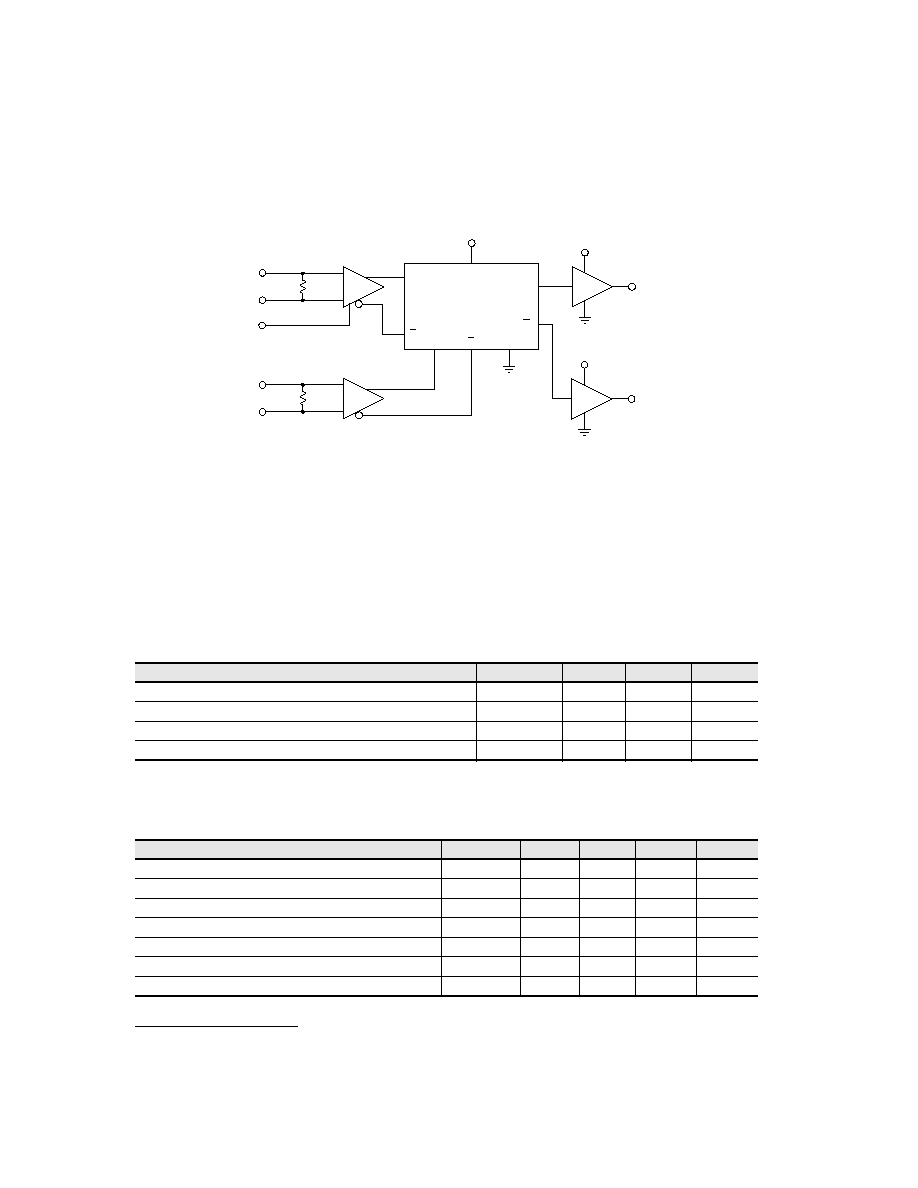

ELECTRICAL CHARACTERISTICS

Exceeding these maximum ratings could cause immediate damage or lead to permanent deterioration of the device.

Absolute Maximum Ratings

Parameter

Symbol

Min.

Max.

Units

Supply Voltage

V

DD

-0.3

2.3

V

Data Input Voltage

V

DI

, V

CI

-0.3

1.5

V

Temperature at Package Base under Bias

Ts

-45

100

∞C

Storage Temperature

Tst

-45

125

∞C

Electrical Characteristics

V

DD

= 2 V ± 0.1 V, Ts = 0∞C to 70∞C

Parameter

Symbol

Min.

Typ.

Max.

Units

Maximum Operating Data Bit Rate

DAR

10

Gbps

Power Dissipation

PW

0.6

0.75

W

Clock Input Voltage Swing

CIS

0.4

0.9

Vpp

Data Input Voltage Swing

DIS

0.1

0.9

Vpp

Output Voltage Swing

DOS

0.8

1.0

1.2

Vpp

Output ( Q, QN ) Rise Time and Fall Time

TRF

30

40

ps

Phase Margin @ 10 Gbps (2

23

-1 PRBS)

TPM

250

degree

DR1

DA

50

CR

CK

50

QN

V

DD

V

DD

DA

Data Input Terminal

CK

Clock Input Terminal

DR1, CR

Reference Voltage Terminals. Usually D1R and DR are connected to ground through a capacitor (0.1 µF).

DR2

Reference Voltage Bias Terminal

Q, QN

Complimentary Data Output Terminals

VDD

Power Supply of Internal Circuit

Q

V

DD

C

C

D

D

Q

Q

MCFF

DR2