| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ML2201 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

FEDL2201-01

1Semiconductor

This version: Mar. 2000

ML2201-XXX

Speech Synthesizer LSI with on-chip 384K Mask ROM

1/20

GENERAL DESCRIPTION

The ML2201 is a PCM-based speech synthesizer LSI having an on-chip 384K Mask ROM, D/A Converter and

Low Pass Filter. Utilizing the serial interface enables smaller footprint packaging, which makes the chip an ideal

choice for a pre-recorded message subsystem used with today's size-critical applications.

FEATURES

∑

Sampling Frequency (Selectable for each single phrase)

4.0/5.3/6.4/8.0/10.6/12.8/16.0 kHz

∑

On-chip 384 Kbit Mask ROM

∑

Maximum Playback Time (At f

EXTCLK

= 4.096 MHz)

12.0 sec

At f

SAM

= 4.0 kHz

6.0 sec

At f

SAM

= 8.0 kHz

3.0 sec

At f

SAM

= 16.0 kHz

∑

External Clock Frequency Range *

f

EXTCLK

= 3.5 to 4.096 MHz (Typ.) to 17.0 MHz

∑

On-chip Phrase Control Table

∑

Maximum Number of Phrases:

31 Phrases

∑

Built-in 10-bit Current-Output Type D/A Converter

∑

Built-in LPF

∑

Packaging:

8-pin Plastic SSOP (SSOP8-P-44-0.65-K)

(Product Code: ML2201-XXX MBZ060)

∑

Power Supply Voltage:

+2.0 to +5.5 V

* Note:

As of February 2000, ceramic oscillation on this chip is under development and thus the chip is not

functional with a ceramic oscillator. The manufacturer intends to add a ceramic oscillation option to the

chip. For more information on availability in commercial quantity, contact your sales representative.

FEDL2201-01

1Semiconductor

ML2201≠XXX

2/20

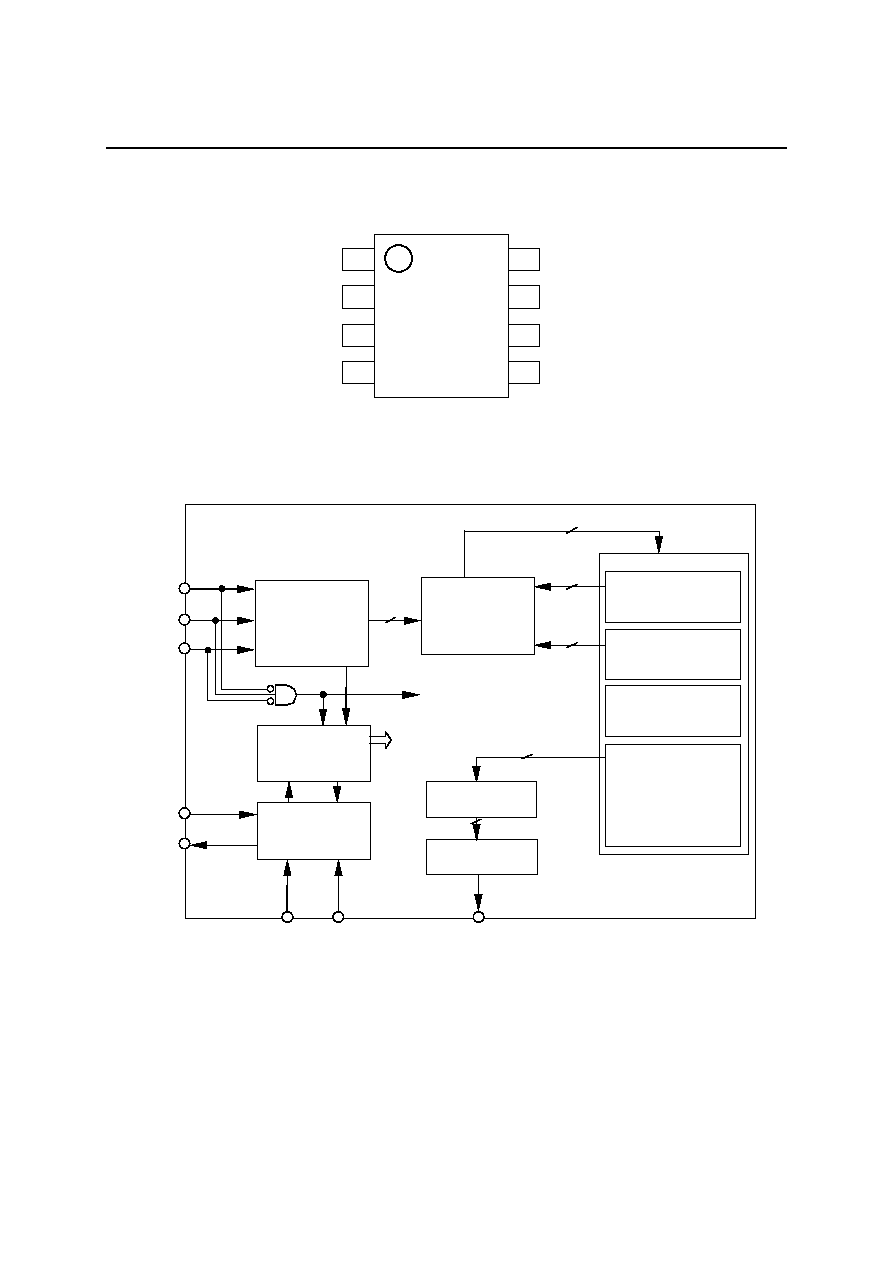

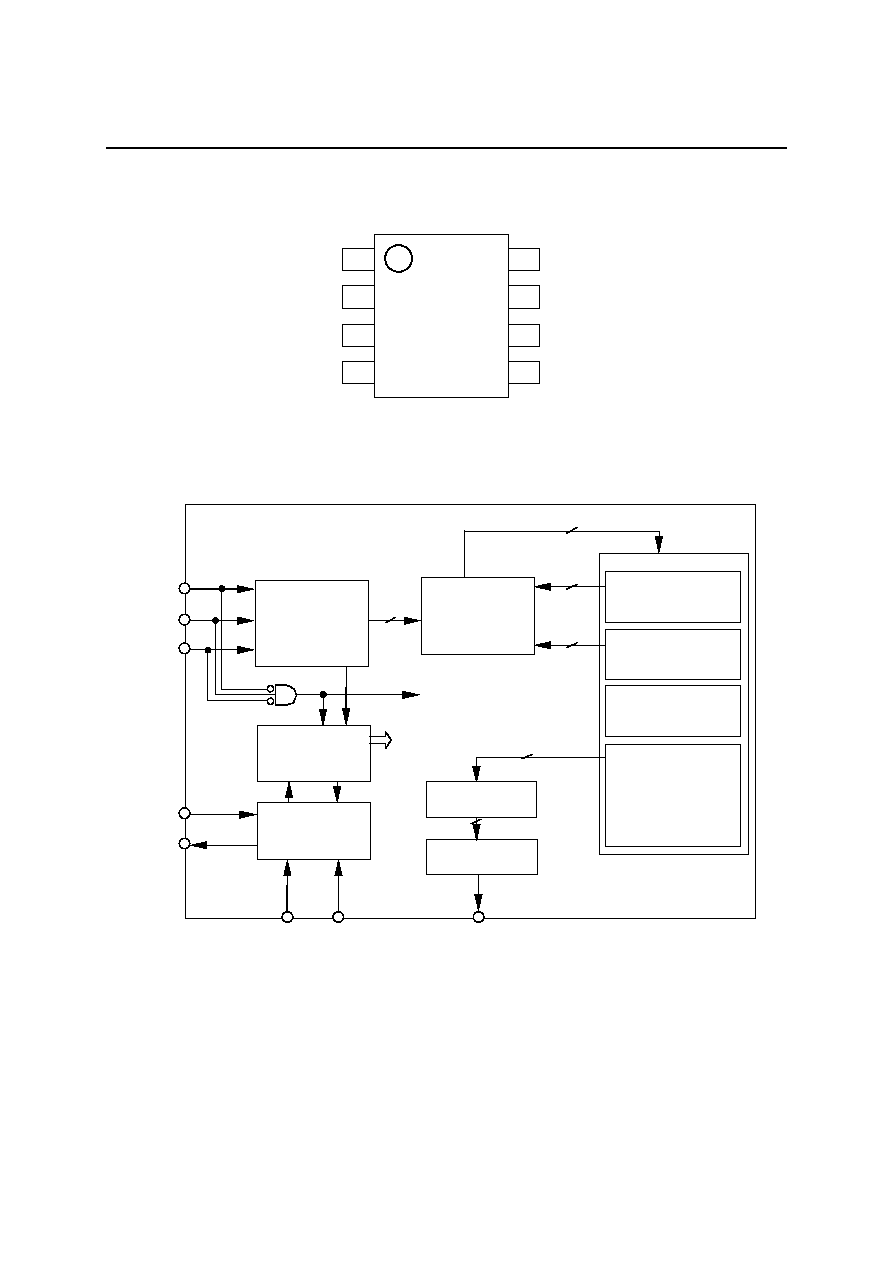

PIN LAYOUT (TOP VIEW)

GND

AOUT

XT

V

DD

1

2

3

4

8

7

6

5

PDWN

XT

ST

PI

8-Pin Plastic SSOP

BLOCK DIAGRAM

AOUT

GND

V

DD

PDWN

384 Kbit ROM

10 bit DAC

LPF

XT

16 bit Address

controller

XT

ST

PI

OSC

Circuit

10

Timing

Controller

Serial

Interface

8

8

PCM data Area

378 Kbit

Edit ROM 2 Kbit

(Phrase Control Table)

Address ROM 2 Kbit

(Phrase Address Table)

Test ROM 2 Kbit

8

5

Reset, Power Down

16

PCM

Synthesizer

FEDL2201-01

1Semiconductor

ML2201≠XXX

3/20

PIN DESCRIPTION

Pin No.

Pin Name

I/O

Description

1

ST

I

The playback trigger pin.

The number of pulses input to the

PI

pin, while this pin is held "L",

determines the Phrase Address for playback. At the

ST

's rising edge, the

phrase address data is loaded into the LSI and playback starts. When no

pulse input to

PI

occurs while this pin is held "L", the LSI recognizes it as the

"Stop Code" that results in stopping playback.

2

PI

I

The address input pin.

The number of pulses input to this pin, while the

ST

pin is held "L",

determines the Phrase Address for playback.

When 32 pulses are input, the internal counter returns to its initial value, "0".

3

GND

--

The ground pin.

4

AOUT

O

The analog output pin.

Configured as N-MOS open drain, analog signal is output in the form of

change in output (attraction) current. While the

PDWN

pin being held "H",

this pin is sustained at 1/2 level and thus the current keeps on flowing.

When shifting to standby state and shifting back to ready state from

standby, the pop-noise canceller is put to work.

5

V

DD

--

The power supply pin.

Insert a 0.1

µ

F bypass capacitor between this pin and the GND pin.

6

XT

I

The external clock input pin.

The ceramic resonator connection pin for ceramic oscillation option under

development.

7

XT

O

Keep this pin open.

The LSI's operations may become unstable if this pin includes any

capacitive component.

The ceramic resonator connection pin for ceramic oscillation option under

development.

8

PDWN

I

The power down pin.

The LSI stays standby state while the pin being held "L".

FEDL2201-01

1Semiconductor

ML2201≠XXX

4/20

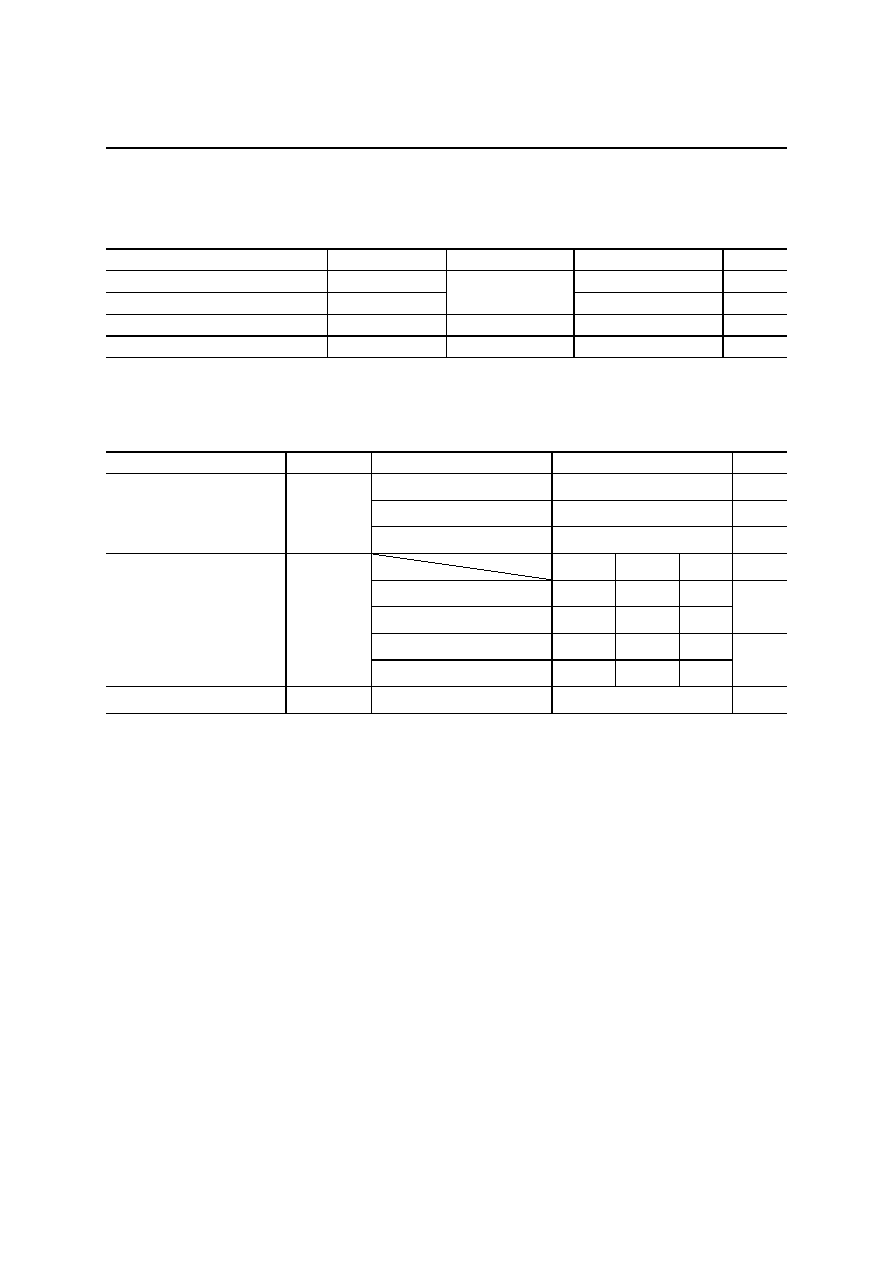

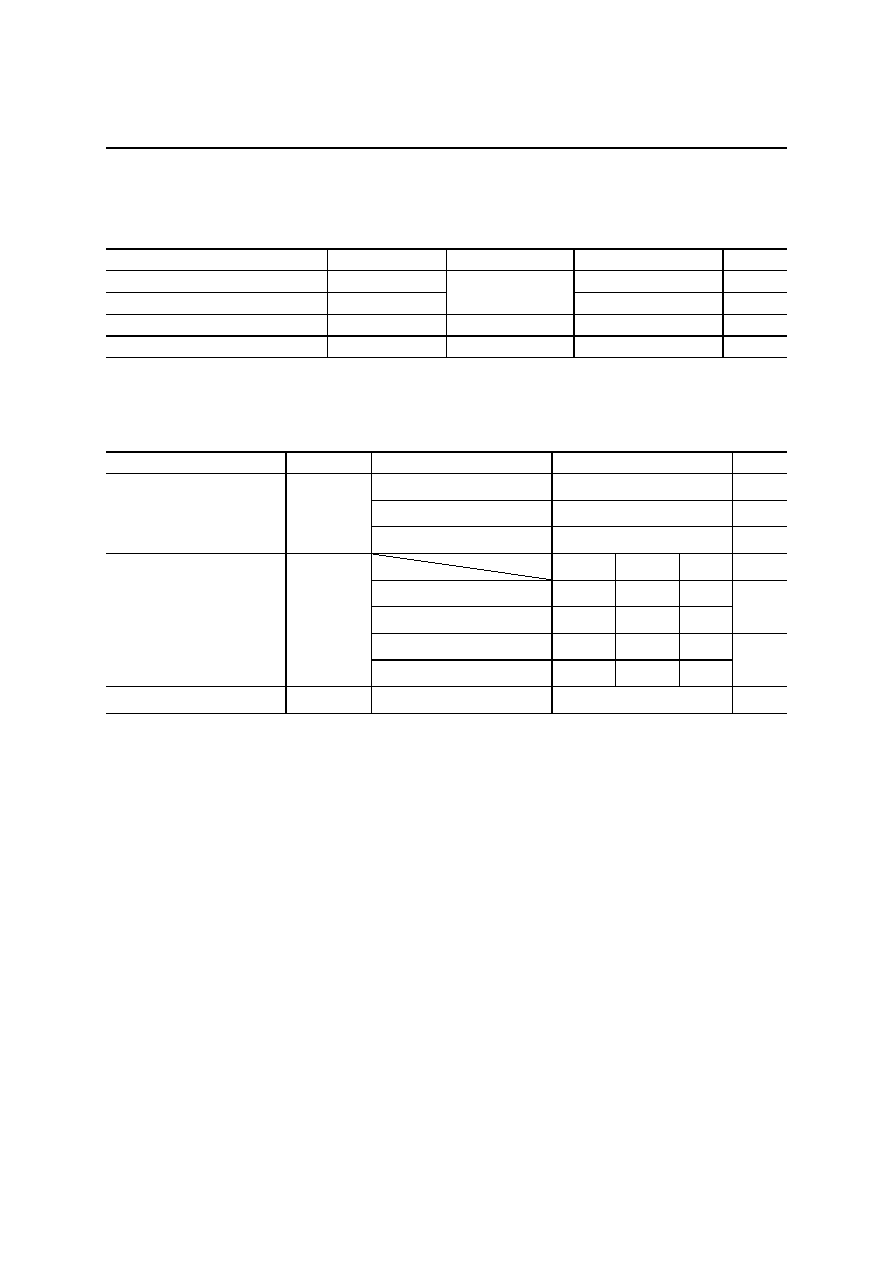

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V)

Parameter

Symbol

Condition

Rating

Unit

Power Supply Voltage

V

DD

≠0.3 to +7.0

V

Input Voltage

V

IN

Ta = 25∞C

≠0.3 to V

DD

+0.3

V

Storage Temperature

T

STG

--

≠55 to +150

∞C

Power Drain Allowance

Pd

Ta = 25∞C

250

mW

RECOMMENDED OPERATING CONDITIONS

(GND = 0 V)

Parameter

Symbol

Condition

Range

Unit

f

EXTCLK

= 3.5 to 4.5 MHz

+2.0 to +5.5

V

f

EXTCLK

= 3.5 to 13.5 MHz

+2.6 to +5.5

V

Power Supply Voltage

V

DD

f

EXTCLK

= 3.5 to 17.0 MHz

+3.0 to +5.5

V

Min.

Typ.

Max.

MHz

V

DD

= 2.0 to 5.5 V

3.5

4.096

4.5

V

DD

= 2.6 to 5.5 V

3.5

--

13.5

V

DD

= 2.7 to 5.5 V

3.5

--

14.5

External Clock Frequency

f

EXTCLK

V

DD

= 3.0 to 5.5 V

3.5

--

17.0

Operating Temperature

T

OP

--

≠40 to +85

∞C

FEDL2201-01

1Semiconductor

ML2201≠XXX

5/20

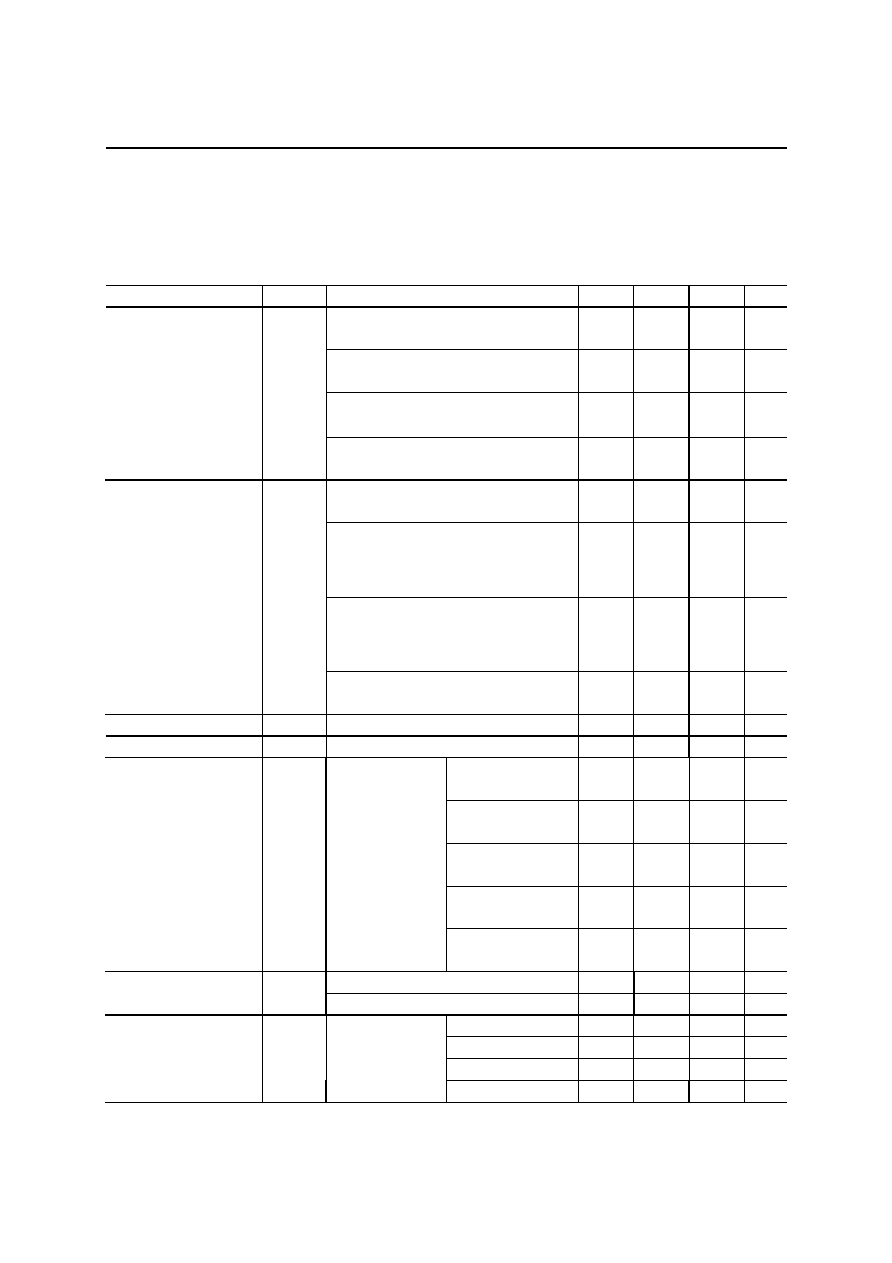

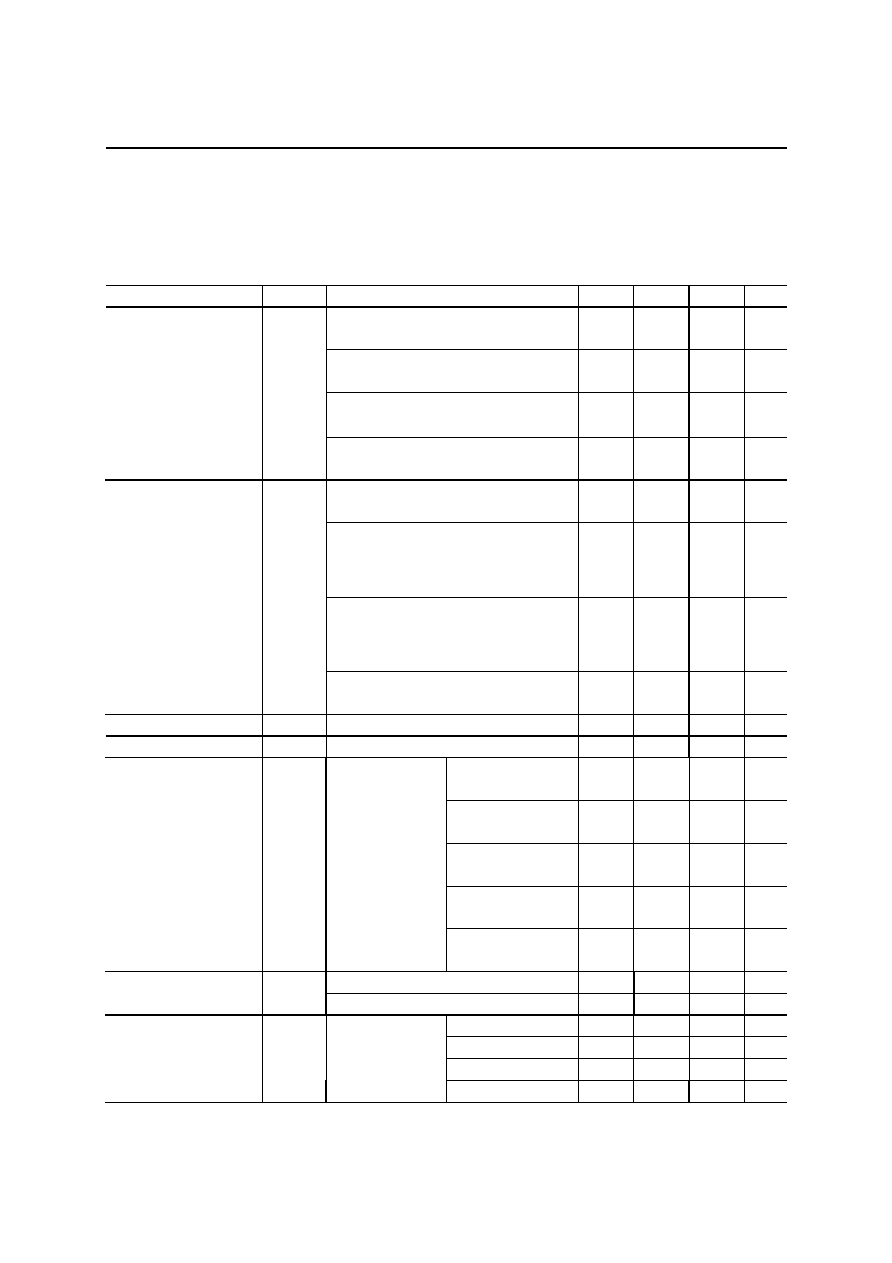

ELECTRICAL CHARACTERISTICS

DC Characteristics

V

DD

= 2.0 to 5.5 V, GND = 0 V, f

EXTCLK

= 4.096 MHz, Ta = ≠40 to +85∞C (unless otherwise specified)

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

F

EXTCLK

>

14.5 MHz

V

DD

= 3.0 to 5.5 V

V

DD

◊

0.85

--

--

V

f

EXTCLK

14.5 MHz

V

DD

= 2.7 to 5.5 V

V

DD

◊

0.8

--

--

V

f

EXTCLK

13.5 MHz

V

DD

= 2.6 to 2.7 V

V

DD

◊

0.85

--

--

V

"H" Input Voltage

V

IH

f

EXTCLK

4.5 MHz

V

DD

= 2.0 to 5.5 V

V

DD

◊

0.8

--

--

V

F

EXTCLK

>

14.5 MHz

V

DD

= 3.0 to 5.5 V

--

--

V

DD

◊

0.15

V

f

EXTCLK

14.5 MHz

V

DD

= 2.7 to 5.5 V

--

--

V

DD

◊

0.2

V

f

EXTCLK

13.5 MHz

V

DD

= 2.6 to 2.7 V

--

--

V

DD

◊

0.15

V

"L" Input Voltage

V

IL

f

EXTCLK

4.5 MHz

V

DD

= 2.0 to 5.5 V

--

--

V

DD

◊

0.2

V

"H" Input Current

I

IH

V

IH

= V

DD

--

--

10

µ

A

"L" Input Current

I

IL

V

IL

= GND

≠10

--

--

µ

A

V

DD

= 5.5 V

f

EXTCLK

= 4.096 MHz

--

1.7

3.9

mA

V

DD

= 3.0 V

f

EXTCLK

= 4.096 MHz

--

0.9

2.1

mA

V

DD

= 2.0 V

f

EXTCLK

= 4.096 MHz

--

0.5

1.4

mA

V

DD

= 5.5 V

f

EXTCLK

= 16 MHz

--

4.6

12.0

mA

Supply Current

I

DD

Except AOUT

output current

V

DD

= 3.0 V

f

EXTCLK

= 16 MHz

--

1.8

6.5

mA

Ta = ≠40 to +70

∞

C

--

--

10

µ

A

Standby Current

I

DS

Ta = ≠40 to +85∞C

--

--

50

µ

A

V

DD

= 2.0 to 5.5 V

0.5

--

10.0

mA

V

DD

= 5.5 V

4.3

6.8

10.0

mA

V

DD

= 3.0 V

1.4

2.7

3.9

mA

AOUT Output Current

I

AOUT

At max.

output current

V

DD

= 2.0 V

0.5

1.2

2.2

mA

FEDL2201-01

1Semiconductor

ML2201≠XXX

6/20

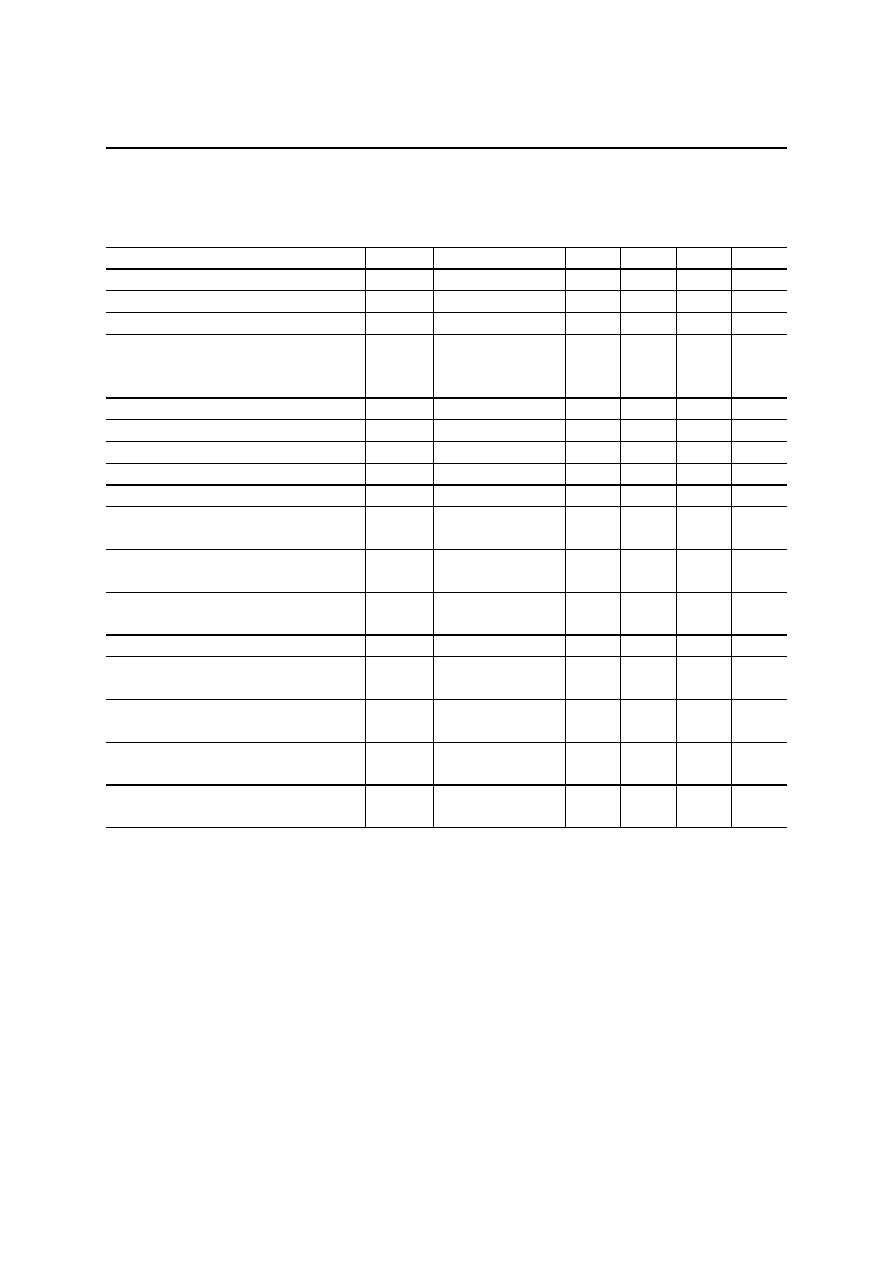

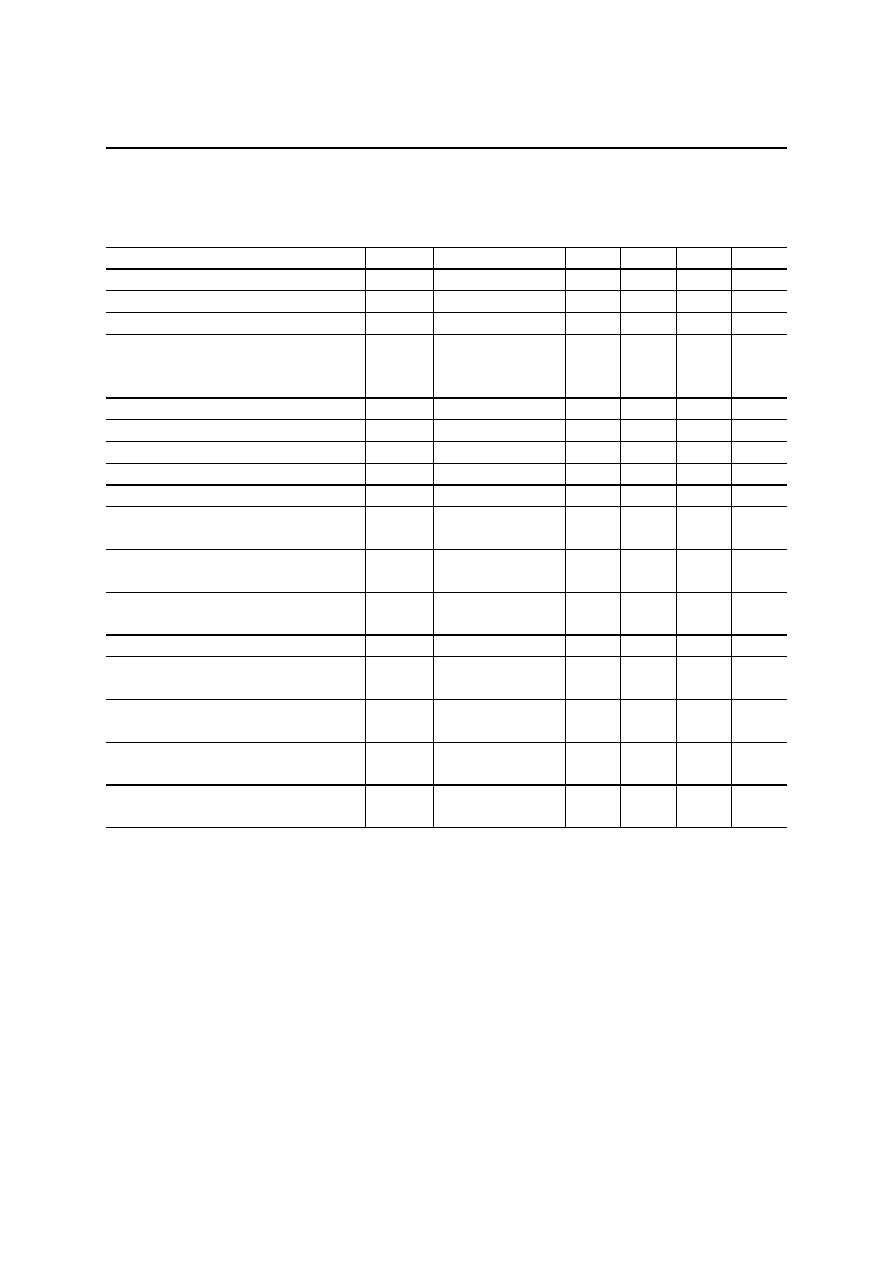

AC Characteristics

V

DD

= 2.0 to 5.5 V, GND = 0 V, f

EXTCLK

= 4.096 MHz, Ta = ≠40 to +85∞C (unless otherwise specified)

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Clock Oscillation Duty Cycle

f

DUTY

--

40

50

60

%

Reset Input Time after Powering Up

t

RST

--

10

--

--

µ

s

PDWN

Hold Time after Reset Input

t

PDH

--

10

--

--

µ

s

D/A Converter Transit Time

(Pop-Noise Canceller Work Time)

Note *1

t

DAR

, t

DAF

--

60

64

68

ms

PDWN

≠

ST

Setup Time

t

PDSS

--

1

--

--

µ

s

ST

≠

PI

Setup Time

t

SPS

--

1

--

--

µ

s

PI

Pulse Width

t

PW

--

0.35

--

2000

µ

s

PI

Cycle Time

t

PC

--

0.7

--

4000

µ

s

ST

≠

PI

Hold Time

t

SPH

--

1

--

--

µ

s

ST

≠ AOUT Setup Time

Note *2

t

SAS

At f

SAM

= 8.0 kHz

--

1050

µ

s

Phrase Stop Time

Note *2

t

DPS

At f

SAM

= 8.0 kHz

--

700

µ

s

Silence Time between Phrases

Note *2

t

BLN

At f

SAM

= 8.0 kHz

--

700

µ

s

Stop

ST

Pulse Width

t

SSW

--

0.35

--

2000

µ

s

Phrase

ST

≠ Phrase

ST

Pulse Duration

Note *2

t

PP

At f

SAM

= 8.0 kHz

1050

--

--

µ

s

Phrase

ST

≠ Stop

ST

Pulse Duration

Note *2

t

PS

At f

SAM

= 8.0 kHz

1050

--

--

µ

s

Stop

ST

≠ Phrase

ST

Pulse Duration

Note *2

t

SP

At f

SAM

= 8.0 kHz

500

--

--

µ

s

Sampling Frequency

Note *3

f

SAM

--

3.9

--

28.0

kHz

Note *1: The value changes in proportion to the external clock frequency, f

EXTCLK

.

Note *2: The value changes in proportion to the sampling frequency, f

SAM

.

Note *3: The sampling frequency is determined by the external clock frequency, f

EXTCLK

, and the dividing

factor that is selected for each phrase.

FEDL2201-01

1Semiconductor

ML2201≠XXX

7/20

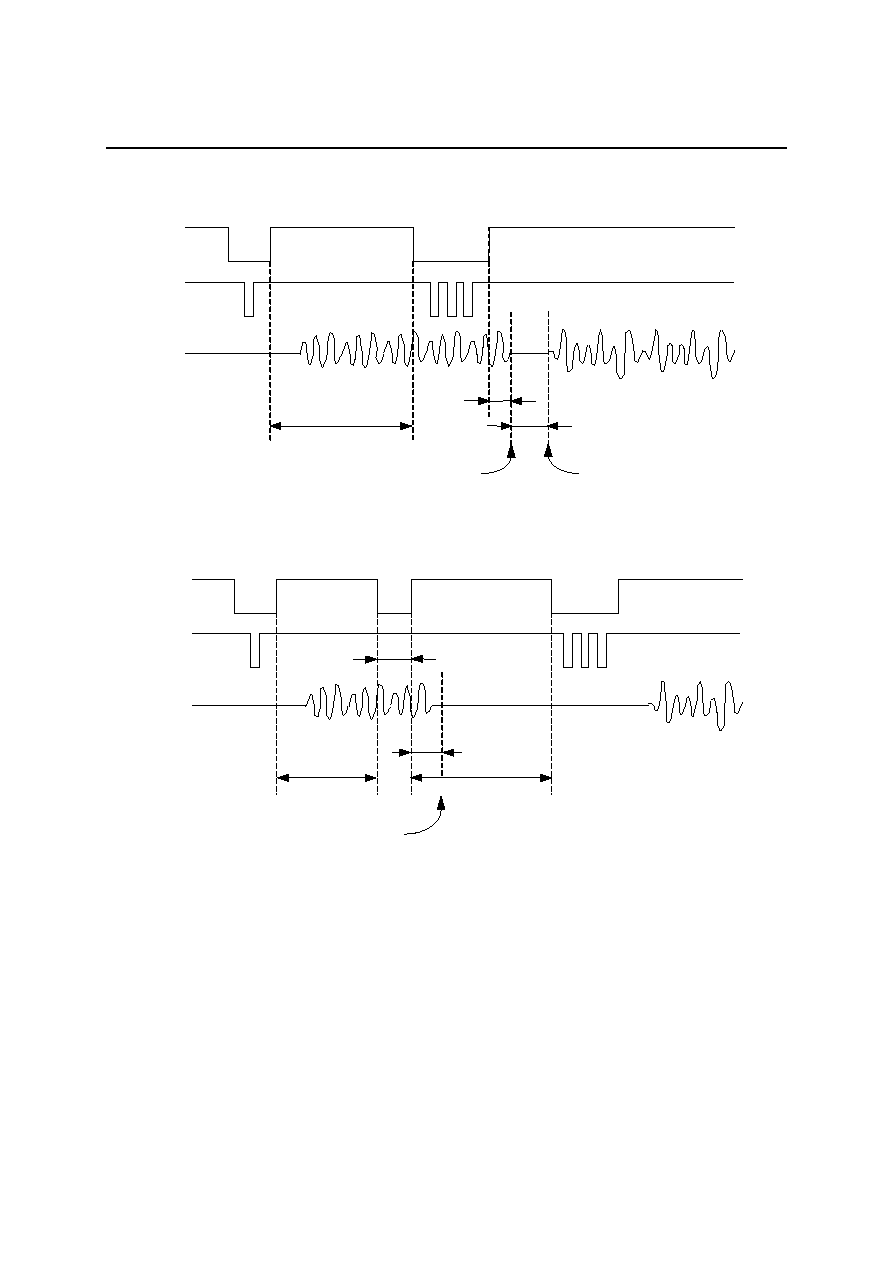

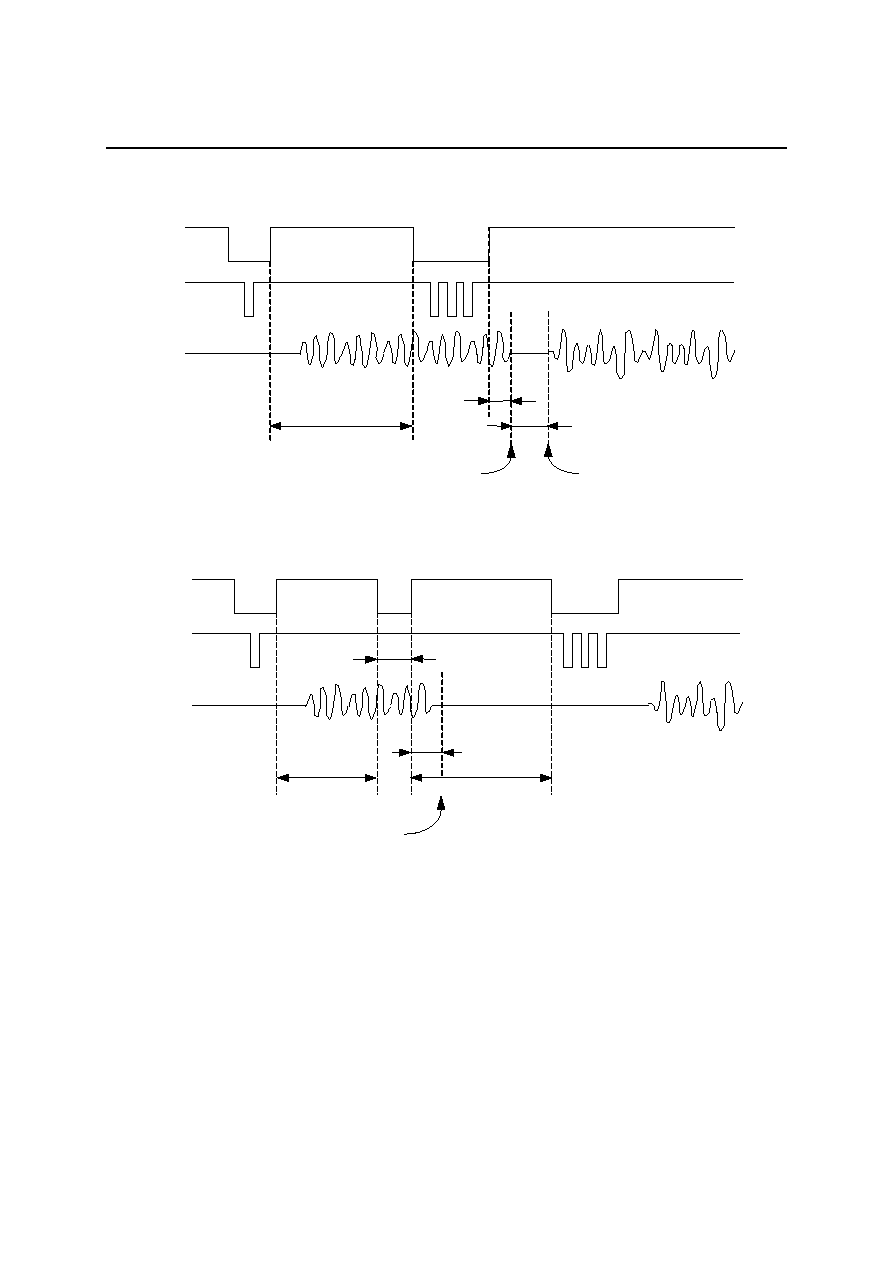

TIMING DIAGRAMS

Timing Diagram at Powering On

V

DD

PDWN

t

RST

t

PDH

ST

PI

Reset

Power Down

NOTE: The LSI's reset operation can be performed by using a level input combination of

PDWN

= "L",

ST

= "L" and

PI

= "H". After powering on, the initial reset operation is required at the above timing.

Timing Diagram at Powering Up and Standby State

PDWN

AOUT

1/2 I

AOUT

t

DAR

t

DAF

Timing Diagram for Playback

PDWN

ST

PI

......

t

PDSS

t

SPS

AOUT

t

SPH

t

SAS

t

PW

t

PC

FEDL2201-01

1Semiconductor

ML2201≠XXX

8/20

Timing Diagram on Re-addressing while Playing

ST

PI

t

DPS

t

BLN

AOUT

Stop playing the current phrase

Start playing the next phrase

t

PP

Timing Diagram on Stop Code Input

ST

PI

t

DPS

AOUT

Stop playing the current phrase

t

PS

t

SP

t

SSW

FEDL2201-01

1Semiconductor

ML2201≠XXX

9/20

FUNCTIONAL DESCRIPTION

Sampling Frequency

You can select a sampling frequency for each phrase address from the following list while you are working on

sound data. Select a sampling frequency that satisfies f

SAM

= 3.9 to 28.0 kHz from the values obtained with the

dividing factors as shown in the Table 1 below.

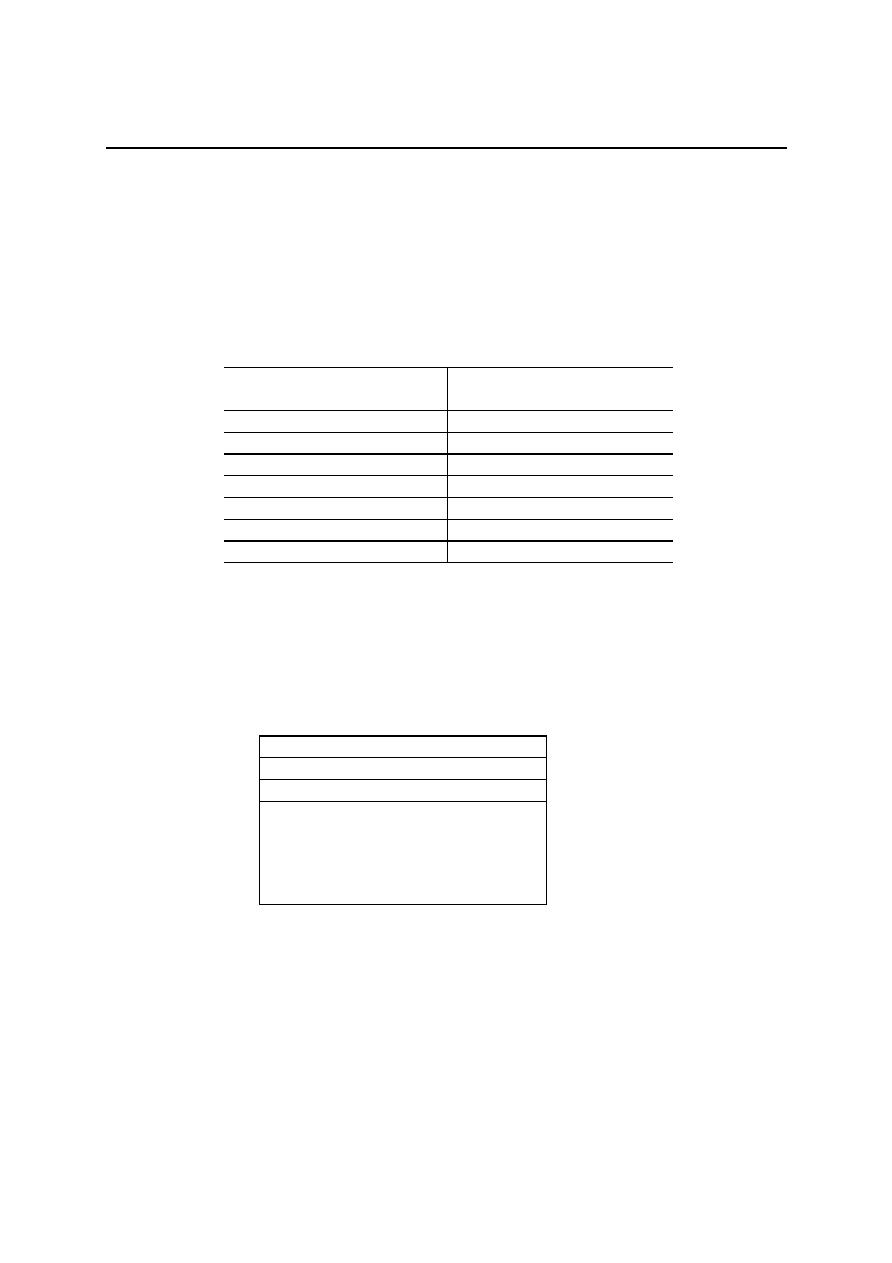

Table 1 Sampling Frequency

Sampling Frequency

At f

EXTCLK

= 4.096 MHz

Dividing Factor

4.0 kHz

f

EXTCLK

/1024

5.3 kHz

f

EXTCLK

/768

6.4 kHz

f

EXTCLK

/640

8.0 kHz

f

EXTCLK

/512

10.6 kHz

f

EXTCLK

/384

12.8 kHz

f

EXTCLK

/320

16.0 kHz

f

EXTCLK

/256

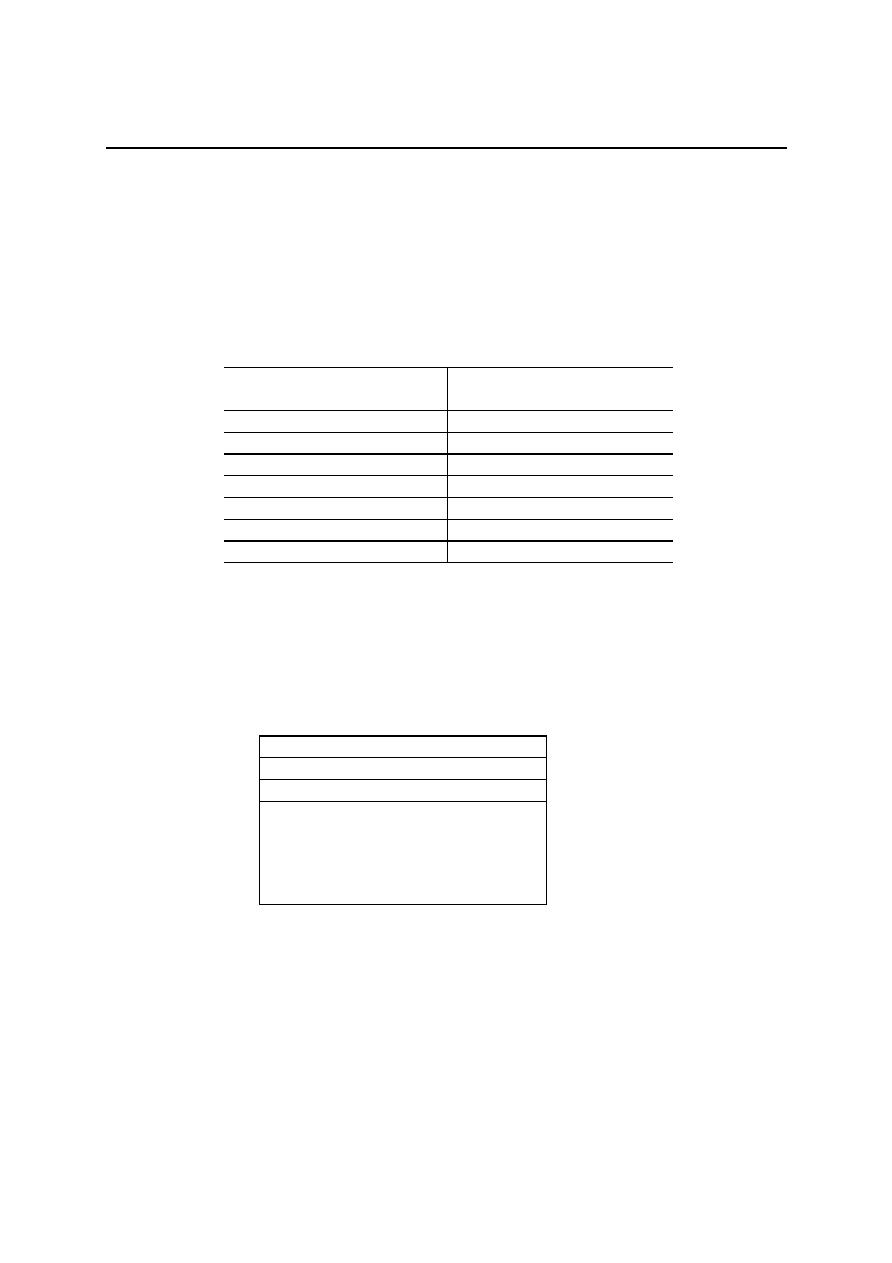

Memory Allocation and Playback Time Length

As shown in the Figure 1, the on-chip Mask ROM of ML2201 is partitioned into four areas, Phrase Control Table,

Address Control Table, Test Data area and User's Data area. The actual data area where user's sound data can be

stored is 378 Kbit, that is the total on-chip Mask ROM capacity minus 6 Kbit.

Phrase Control Table Area

Address Control Table Area

Test Data Area

User's Sound Data Area

2 Kbit

2 Kbit

2 Kbit

378 Kbit

Figure 1 On-chip Mask ROM (384 Kbit) Memory Allocation

FEDL2201-01

1Semiconductor

ML2201≠XXX

10/20

You can calculate playback time length with memory size divided by a bit rate. The following formula can be used

for 8-bit PCM-based ML2201;

Playback Time (sec) =

=

For example, when you store all phrases at 8.0 kHz Sampling Frequency, the maximum playback time is

calculated as follows;

Playback Time (sec) =

6.0 sec

Playback Algorithm

ML2201 uses

OKI

Non-Linear PCM algorithm, an advanced variation of PCM.

In mid-range wave-form, this algorithm has precision and quality equivalent to those of 10-bit Straight PCM.

Inserting Silence

In addition to playing normal recorded sound phrases, ML2201 allows you to insert silence (a silent phrase) . You

can define time length of silence freely in 32 ms steps, within the range of minimum 32 ms and maximum 992 ms

at f

EXTCLK

= 4.096 MHz. Those time length vary in proportion to the external clock frequency, f

EXTCLK

.

Phrase Control Table

The user-definable on-chip Phrase Control Table feature enables you to play back multiple phrases in a single

continuous session with just the same simple control as in a regular single phrase playback. You can assign up to 8

phrases including a silent phrase (s) to a single address. This allows you to get the most out of limited memory

space because you can eliminate duplicate sound data.

As an example, let's assume you want to create several similar phrases like "It will be xxxxx today". "xxxxx" can

be "sunny", "rainy" or "cloudy". The common words such as "It", "will be" and "today" are created separately as

an independent phrase, and phrasing order information is stored in the Phrase Control Table, as shown in the Table

2 and Figure 2.1. From the external control, simply selecting an X address causes the LSI to play multiple phrases

continuously. In this example shown in the Table 2, selecting [01] address starts to play "It will be fine today,

while selecting [02] "It will be rainy today".

You can also insert a silent phrase to the Phrase Control Table without consuming any memory space.

Minimum Time Length of Silence

32 ms

Maximum Time length of Silence

992 ms

Incremental Step

32 ms

Memory Size (Bit)

Bit Rate (bps)

Memory Size (Bit)

Ext. Clock Frequency (Hz)

◊

8

(384 ≠ 6)

◊

1024 Bit

8000 (Hz)

◊

8 Bit

FEDL2201-01

1Semiconductor

ML2201≠XXX

11/20

Table 2 Phrase Control Table Data

No.

X Address

(HEX)

Y Address (Phrasing Order)

(Up to 8 phrases)

Playback

1

01

[01]

[02]

Silence

[04]

[03]

It will be (Silence) fine today.

2

02

[01]

[02]

Silence

[05]

[03]

It will be (Silence) rainy today.

3

03

[01]

[02]

[04]

[09]

[06]

[0A]

[05]

[03]

It will be fine, later cloudy,

occasionally rainy.

:

:

:

30

1 E

31

1 F

Phrase Control Table Data

Address Control Table Data

No.

X Address

Phrasing Order

No.

Y Address

Phrase

1

01

1

[01] "It"

1

01

It

2

02

2

[02] "Will be"

2

02

will be

3

03

3

Silence (64 ms)

3

03

today

4

04

4

[05] "rainy"

4

04

fine

5

05

5

[03] "today"

5

05

rainy

6

06

6

--

6

06

cloudy

7

07

7

--

7

07

snowy

8

08

8

--

8

08

occasionally

9

09

later

10

0A

in some area

Set length of silence

(32 ms

◊

n)

n

Length of

Silence

1

32 ms

2

64 ms

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

31

1F

31

992 ms

31

1F

--

Time unit of silence varies

in proportion to the dividing

factor of f

EXTCLK

.

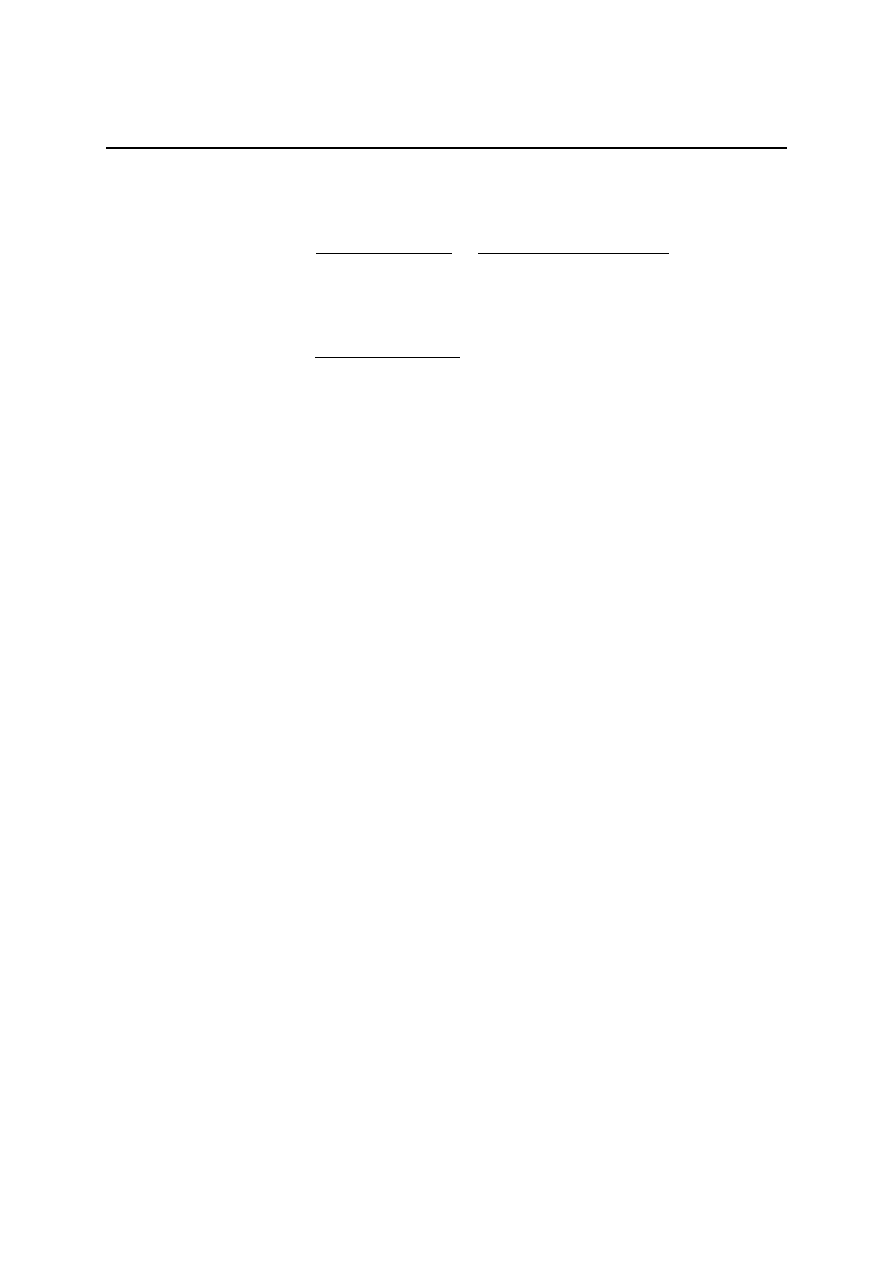

Figure 2.1 Phrase Data Combination for Use with Phrase Control Table

FEDL2201-01

1Semiconductor

ML2201≠XXX

12/20

Figur

e

2

.

2

T

i

ming Dia

g

ra

m for

P

l

a

y

ba

c

k

w

i

th P

h

r

a

s

e

Contr

o

l T

a

ble

Func

tion

S

T

P

I

AOU

T

V

DD

PDW

N

I

t

wi

ll

be f

i

ne t

oday,

la

te

r o

cca

sio

n

a

lly

...

It wil

l

b

e

..........

Res

e

t

P

o

we

r

D

o

wn

S

h

i

f

t

i

ng t

o

S

t

andby

Pla

y

in

g

Pla

y

in

g

Pla

y

in

g

1

s

t P

h

r

a

se

Pla

y

in

g

S

t

op pl

ayi

n

g

t

h

e

earl

i

e

r phras

e

S

t

op pl

ayi

n

g

Stop Cod

e

P

o

we

r

D

o

wn

1st Phr

a

se

3rd Phra

se

2nd Phr

a

se

1st Phr

a

se

3rd Phra

s

e

2nd Phra

s

e

1

s

t P

h

r

a

se

It w

i

l

l

b

e

ra

in

y

t

oday

It w

i

l

l

b

e

fin

e

t

oday

Sh

if

tin

g

to

S

t

andby

FEDL2201-01

1Semiconductor

ML2201≠XXX

13/20

External Clock Input

The Figure 3 shows wiring of an external timing source.

(A type of the external clock should be determined at selecting chip options.)

XT

An external

timing source

Keep this

pin open

XT

Figure 3 External Clock Input

* Note:

As of July 1999, ceramic oscillation on this chip is under development and thus the chip is not

functional with a ceramic oscillator. The manufacturer intends to add a ceramic oscillation option to the

chip. For more information on availability in commercial quantity, contact your sales representative.

FEDL2201-01

1Semiconductor

ML2201≠XXX

14/20

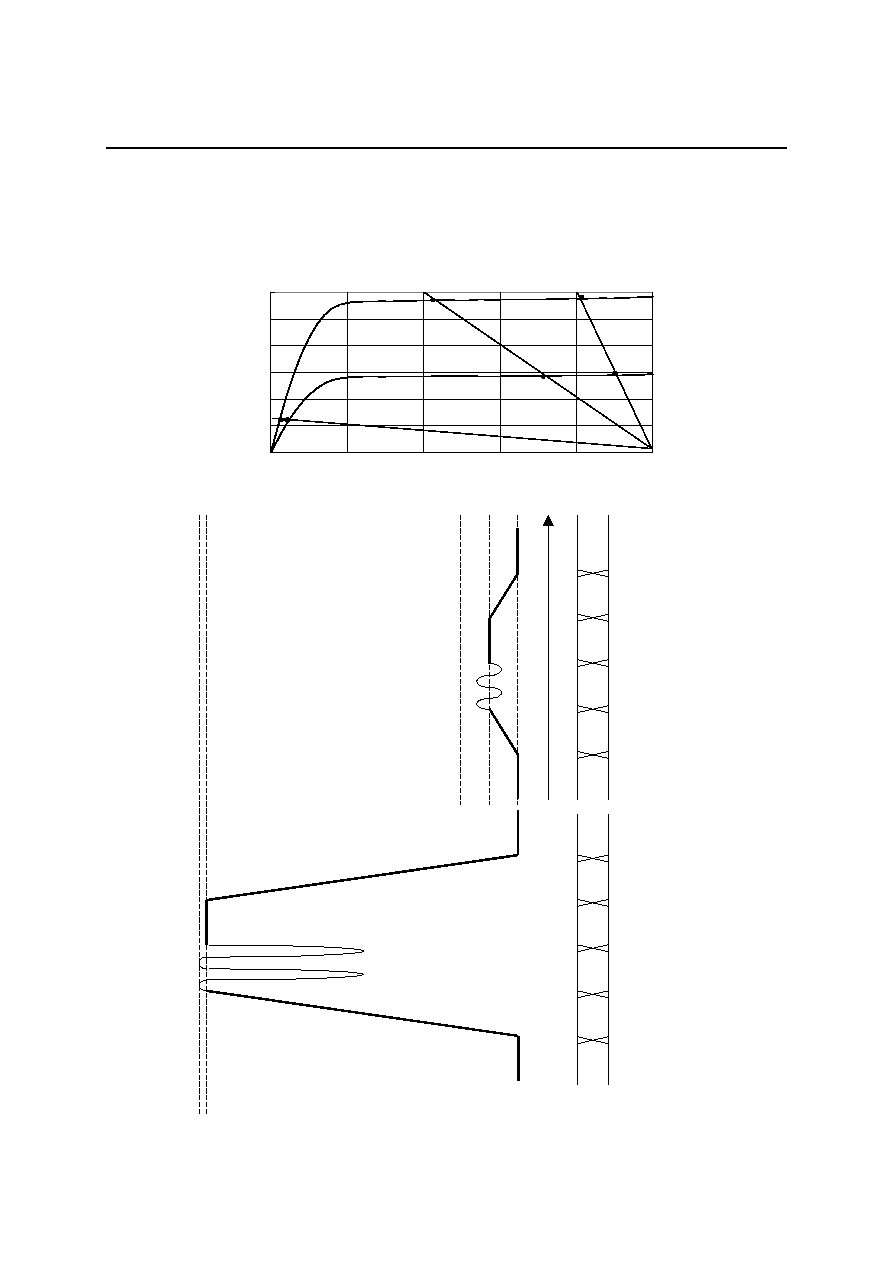

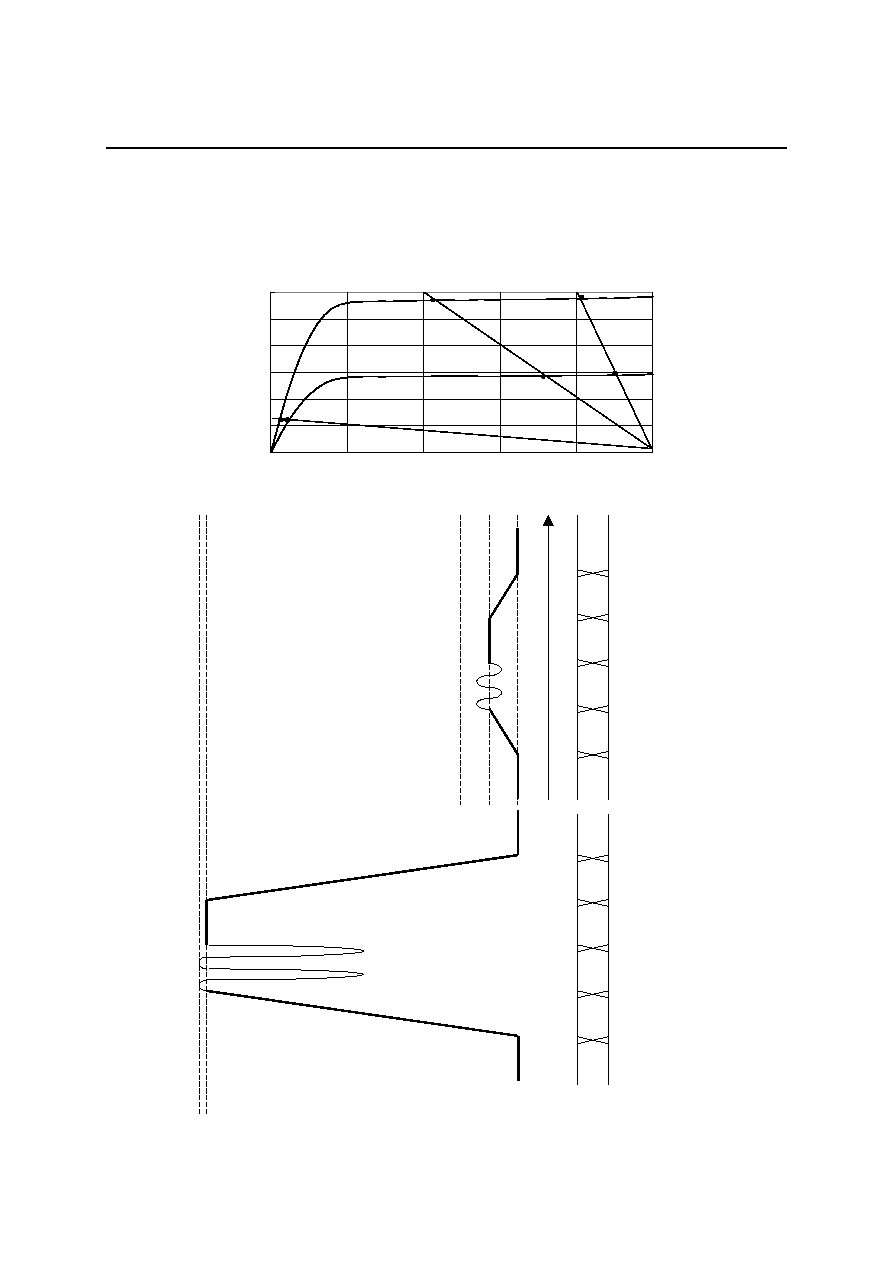

Low Pass Filter

ML2201's analog output goes through the built-in Low Pass Filter. The Figure 4 below shows Frequency

Characteristics and the Table 3 shows Cut-Off Frequency of the LPF.

The LPF's Frequency Characteristics and Cut-Off Frequency change in proportion to the sampling frequency. No

analog output directly from the D/A converter is unavailable on this chip.

20

10

0

≠10

≠20

≠30

≠40

≠50

≠60

≠70

≠80

10

100

1 k

10 k

[Hz]

[dB]

Figure 4 LPF Frequency Characteristics (f

SAM

= 8.0 kHz)

Table 3 LPF Cut-Off Frequency

Sampling Frequency (kHz)

(f

SAM

)

Cut-Off Frequency (kHz)

(f

CUT

)

4.0

1.2

5.3

1.6

6.4

2.0

8.0

2.5

10.6

3.2

12.8

4.0

16.0

5.0

FEDL2201-01

1Semiconductor

ML2201≠XXX

15/20

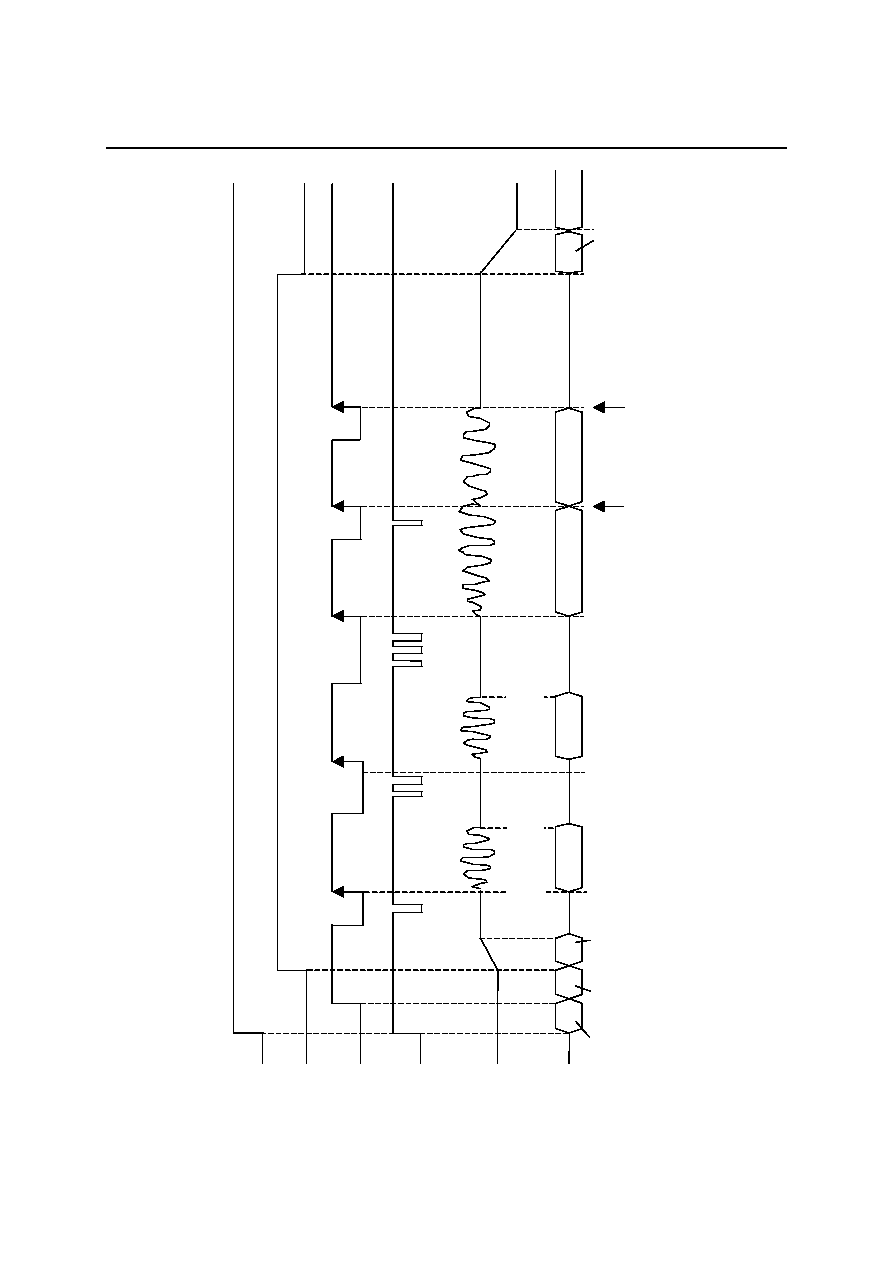

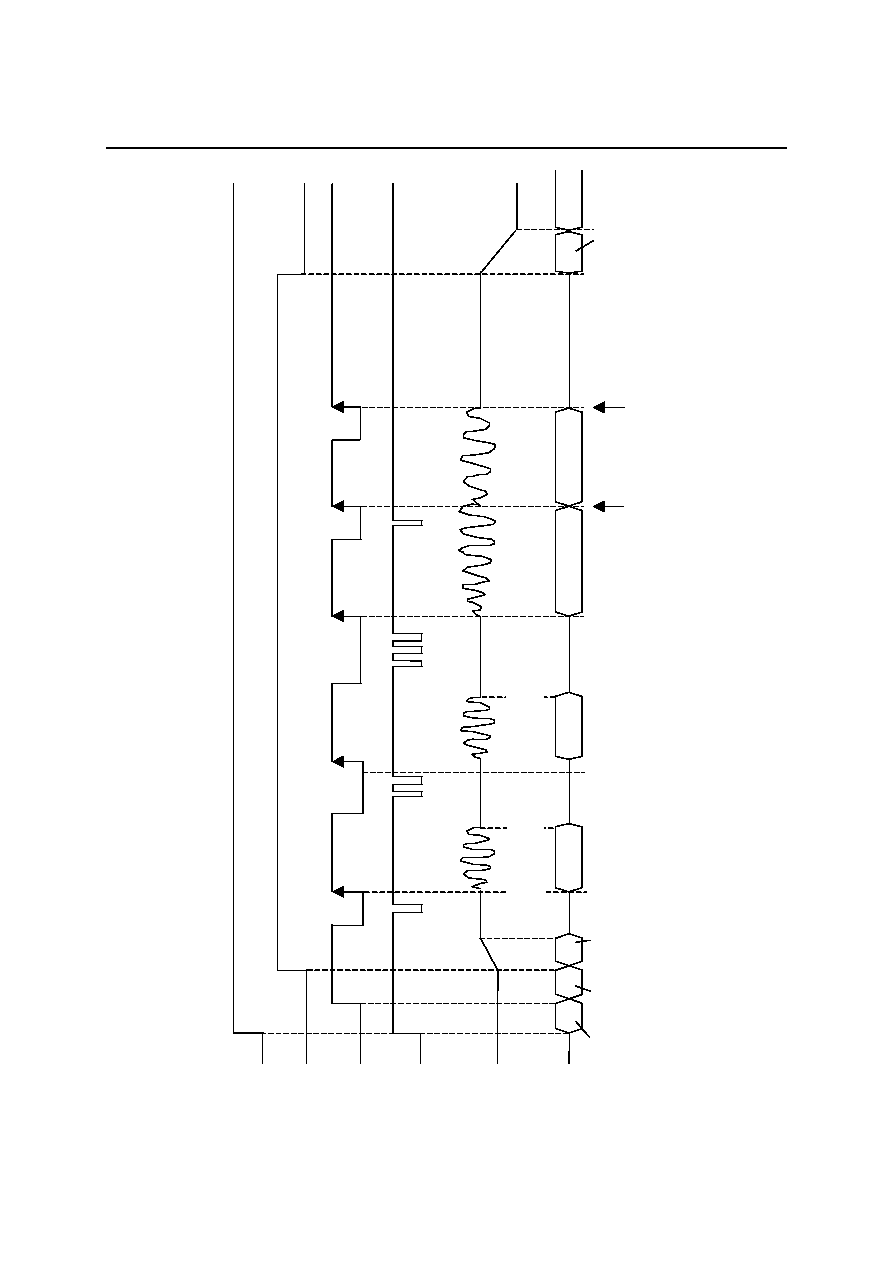

CONNECTING ML2201 TO A SPEAKER DRIVER

ML2201 uses a D/A converter of current-output type.

To connect ML2201 to a voltage-input type speaker driver, you should convert "Changes in Current" output to

"Changes in Voltage" signal. The following samples show connections of ML2201 and MSC1157 (OKI Speaker

Driver Amplifier) using a resistor (RL) for conversion.

SAMPLE CIRCUIT 1: AT V

DD

= 5.0 V, MSC1157'S Ain AMPLIFICATION = 2.5 V

P-P

MCU

ML2201

MSC1157

P1.2

P1.1

P1.0

PDWN

ST

PI

V

DD

AOUT

V

CC

Ain

430

0.1

µ

F

GND

GND

0.1

µ

F

10

µ

F

47

µ

F

XT

STBY

SEL

VR

4.7

µ

F

SP

SP

+5 V

+5 V

CLK

XT

SAMPLE CIRCUIT 2: AT V

DD

= 3.0 V, MSC1157'S Ain AMPLIFICATION = 1.5 V

P-P

MCU

ML2201

MSC1157

P1.2

P1.1

P1.0

PDWN

ST

PI

V

DD

AOUT

V

CC

Ain

510

0.1

µ

F

GND

GND

0.1 µF

10

µ

F

47

µ

F

XT

STBY

SEL

VR

4.7

µ

F

SP

SP

+3 V

+3 V

CLK

XT

FEDL2201-01

1Semiconductor

ML2201≠XXX

16/20

Co-relationship between output voltage and the value of a resistor for current-voltage conversion is shown in the

figure below. You may want to use the figure as a reference in determining a proper value for the resistor.

AOUT Voltage VS. AOUT Output Current at V

DD

= 5.0 V

RL = 500

0

1

2

3

4

5

6

0

1

2

3

4

5

VAOUT (V)

IA

O

U

T

(m

A

)

RL = 200

RL = 5 k

Po

w

e

r

Do

w

n

Po

w

e

r

Do

w

n

Re

ad

y

Pl

ay

i

n

g

S

h

i

f

ti

n

g

to

St

a

ndb

y

S

h

i

f

ti

n

g

to

St

a

ndb

y

Po

w

e

r

Do

w

n

Po

w

e

r

Do

w

n

Re

ad

y

Pl

ay

i

n

g

S

h

i

f

ti

n

g

to

St

a

ndb

y

S

h

i

f

ti

n

g

to

St

a

ndb

y

(1)

A

t

RL =

200

Pr

o

p

er

w

a

vefor

m

o

u

t

p

u

t

show

n.

(2)

A

t

R

L

=

5 k

Dis

tor

t

ed w

a

v

e

form a

nd o

b

v

i

ou

s

p

o

p

-

n

o

i

se sh

ow

n.

FEDL2201-01

1Semiconductor

ML2201≠XXX

17/20

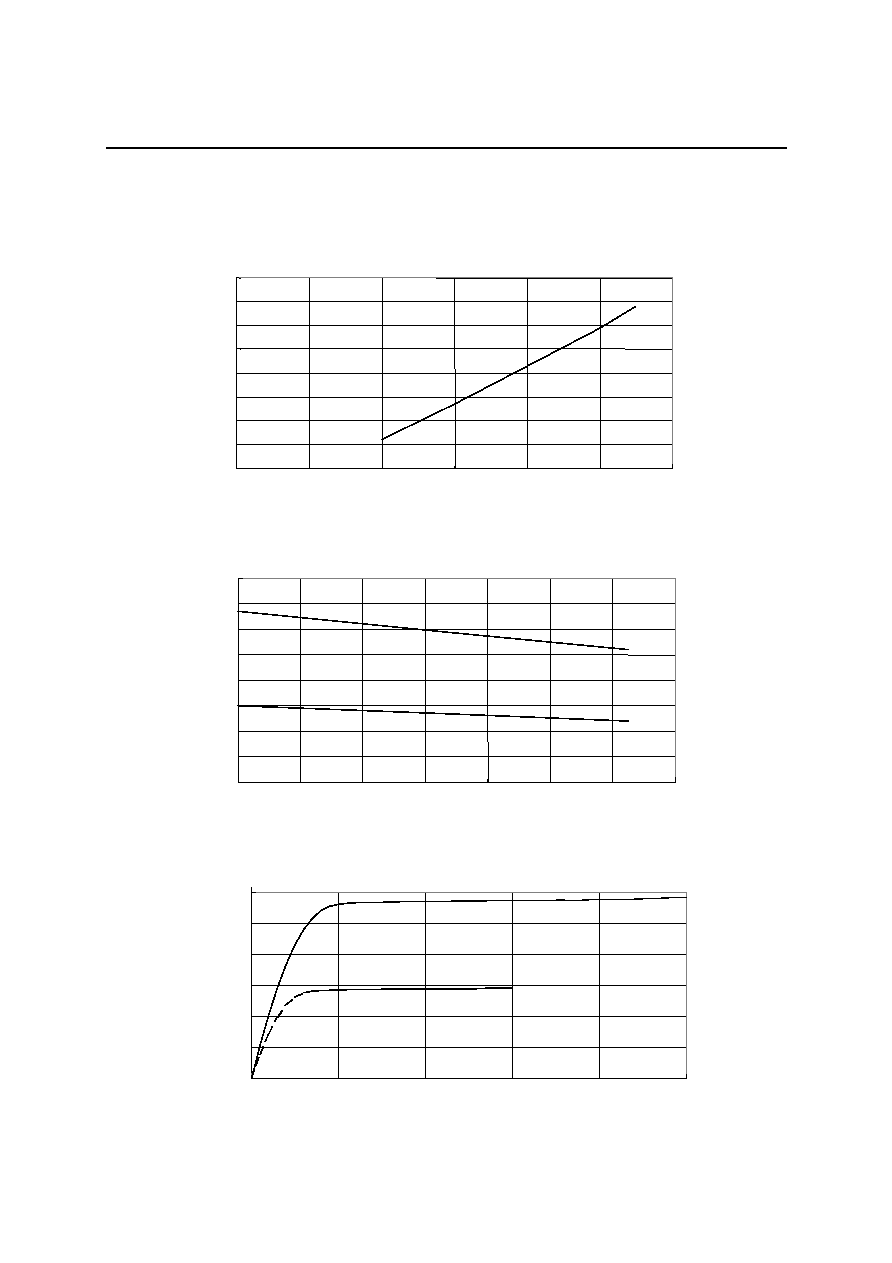

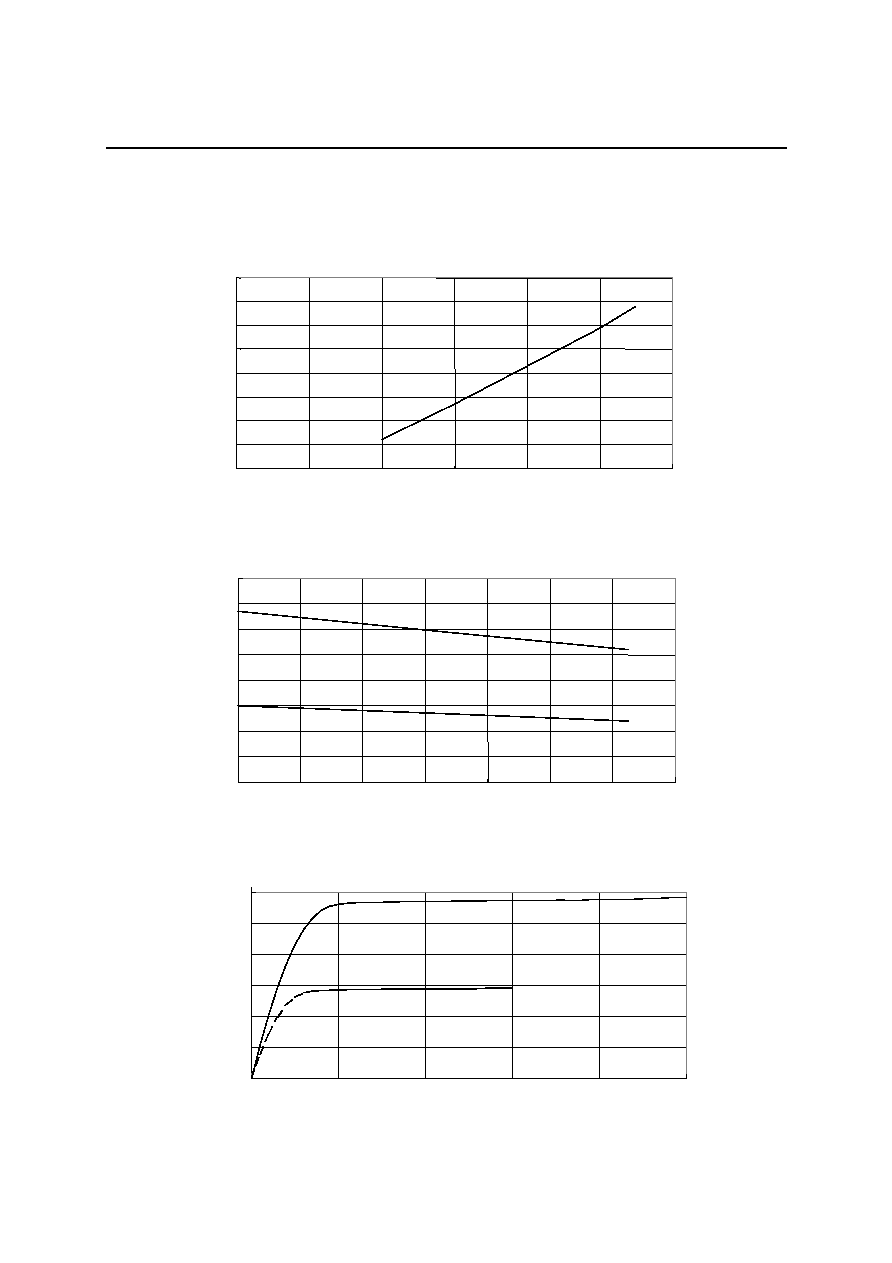

A SAMPLE CHARACTERISTICS OF D/A CONVERTER OUTPUT CURRENT

0

1

2

3

4

5

6

7

8

0

1

2

3

4

5

6

V

DD

(V)

IA

O

U

T

(m

A)

A Sample Characteristics : Power Supply Voltage VS. AOUT Output Current

(Ta = 25∞C, VAOUT = V

DD

, PCM at Max. level)

0

1

2

3

4

5

6

7

8

≠40

≠20

0

20

40

60

80

100

A Sample Characteristics : Operating Temperature VS. AOUT Output Current

(VAOUT = V

DD

, PCM at Max. level)

Ta (∞C)

IA

O

U

T

(m

A)

V

DD

= 5 V

V

DD

= 3 V

0

1

2

3

4

5

6

0

1

2

3

4

5

A Sample Characteristics: Voltage on AOUT Pin VS. AOUT Output Current

(Ta = 25∞C, PCM at Max. level)

VAOUT (V)

IA

O

U

T

(m

A)

V

DD

= 5 V

V

DD

= 3 V

FEDL2201-01

1Semiconductor

ML2201≠XXX

18/20

NOTES ON USAGE

Type of the Built-in D/A Converter

ML2201 has the built-in current-output type D/A converter and thus the design of analog output circuit is different

from the one with a voltage-output type D/A converter (e.g. MSM6650 family).

ML2201's D/A converter is designed as current attraction type with the same circuit configuration with the one

used on MSM9831. So, the analog output circuit is different from MSM9800 family that uses a current discharge

type D/A converter. (See the table below)

Product

D/A Converter Type

D/A Converter Output Circuit

ML2201

Current Output

N-MOS Open Drain

MSM9831

Current Output

N-MOS Open Drain

MSM9800 Family

Current Output

P-MOS Open Drain

MSM6650 Family

Voltage Output

--

A sample circuit of connecting ML2201 and an amplifier chip

D/A Converter

V

DD

GND

AOUT

ML2201

A resistor for converting current to voltage

AMP

Direction of flowing current

A sample circuit of connecting MSM9800 family and an amplifier chip

D/A Converter

V

DD

GND

AOUT

MSM9800 Family

A resistor for converting current to voltage

AMP

Direction of flowing current

FEDL2201-01

1Semiconductor

ML2201≠XXX

19/20

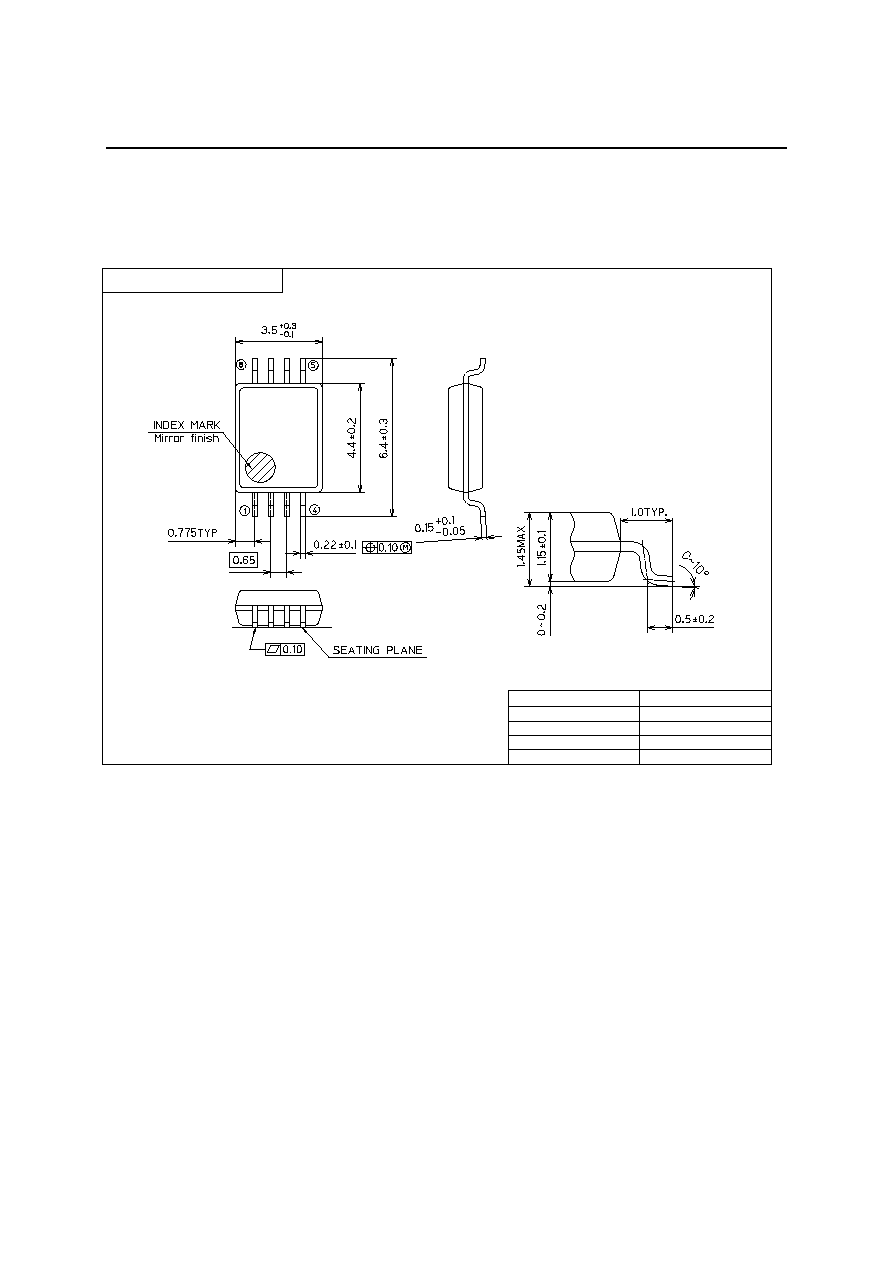

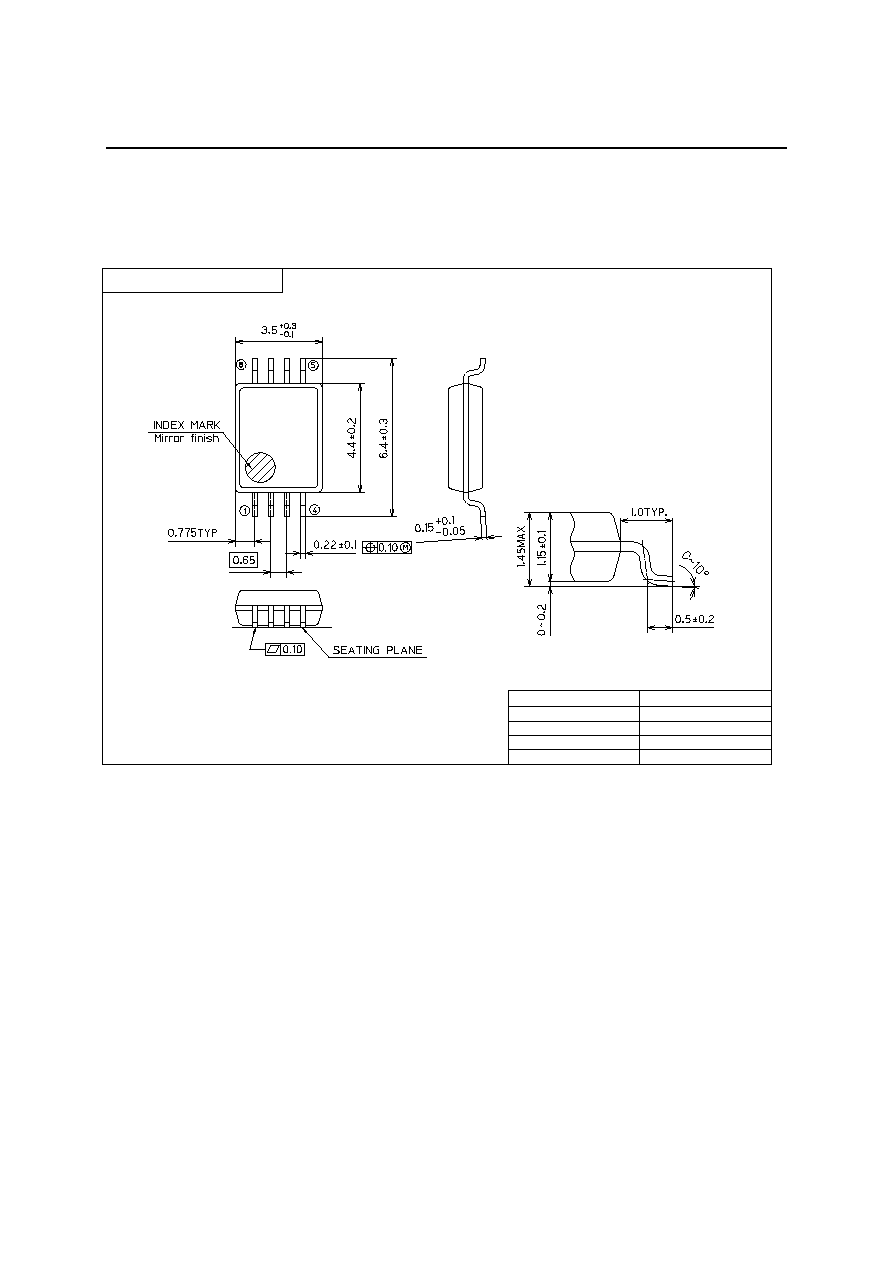

PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Packages

The surface mount type packages are very susceptible to heat in reflow mounting and humidity

absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person on the product

name, package name, pin number, package code and desired mounting conditions (reflow method,

temperature and times).

SSOP8-P-44-0.65-K

5

Package material

Lead frame material

Pin treatment

Package weight (g)

Rev. No./Last Revised

Epoxy resin

42 alloy

Solder plating (

5µm)

0.044 TYP.

1/May.12,1999

(Unit: mm)

FEDL2201-01

1Semiconductor

ML2201≠XXX

20/20

NOTICE

1.

The information contained herein can change without notice owing to product and/or technical improvements.

Before using the product, please make sure that the information being referred to is up-to-date.

2.

The outline of action and examples for application circuits described herein have been chosen as an

explanation for the standard action and performance of the product. When planning to use the product, please

ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

3.

When designing your product, please use our product below the specified maximum ratings and within the

specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating

temperature.

4.

Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation

resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or

unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified

maximum ratings or operation outside the specified operating range.

5.

Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is

granted by us in connection with the use of the product and/or the information and drawings contained herein.

No responsibility is assumed by us for any infringement of a third party's right which may result from the use

thereof.

6.

The products listed in this document are intended for use in general electronics equipment for commercial

applications (e.g., office automation, communication equipment, measurement equipment, consumer

electronics, etc.). These products are not authorized for use in any system or application that requires special

or enhanced quality and reliability characteristics nor in any system or application where the failure of such

system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace

equipment, nuclear power control, medical equipment, and life-support systems.

7.

Certain products in this document may need government approval before they can be exported to particular

countries. The purchaser assumes the responsibility of determining the legality of export of these products

and will take appropriate and necessary steps at their own expense for these.

8.

No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2000 Oki Electric Industry Co., Ltd.