ML63187/189B/193

User's Manual

NOTICE: ML63187 is replaced by ML63189B. Order stop for new masks for ML63187

FIRST EDITION

ISSUE DATE: Mar. 2000

FEUL63193-01

°

NOTICE

1.

The information contained herein can change without notice owing to product and/or

technical improvements. Before using the product, please make sure that the information

being referred to is up-to-date.

2.

The outline of action and examples for application circuits described herein have been

chosen as an explanation for the standard action and performance of the product. When

planning to use the product, please ensure that the external conditions are reflected in the

actual circuit, assembly, and program designs.

3.

When designing your product, please use our product below the specified maximum

ratings and within the specified operating ranges including, but not limited to, operating

voltage, power dissipation, and operating temperature.

4.

Oki assumes no responsibility or liability whatsoever for any failure or unusual or

unexpected operation resulting from misuse, neglect, improper installation, repair, alteration

or accident, improper handling, or unusual physical or electrical stress including, but not

limited to, exposure to parameters beyond the specified maximum ratings or operation

outside the specified operating range.

5.

Neither indemnity against nor license of a third party's industrial and intellectual property

right, etc. is granted by us in connection with the use of the product and/or the information

and drawings contained herein. No responsibility is assumed by us for any infringement

of a third party's right which may result from the use thereof.

6.

The products listed in this document are intended for use in general electronics equipment

for commercial applications (e.g., office automation, communication equipment,

measurement equipment, consumer electronics, etc.). These products are not authorized

for use in any system or application that requires special or enhanced quality and reliability

characteristics nor in any system or application where the failure of such system or

application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety

devices, aerospace equipment, nuclear power control, medical equipment, and life-support

systems.

7.

Certain products in this document may need government approval before they can be

exported to particular countries. The purchaser assumes the responsibility of determining

the legality of export of these products and will take appropriate and necessary steps at their

own expense for these.

8.

No part of the contents contained herein may be reprinted or reproduced without our prior

permission.

9.

MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.

Printed in Japan

E2Y0002-2X-13

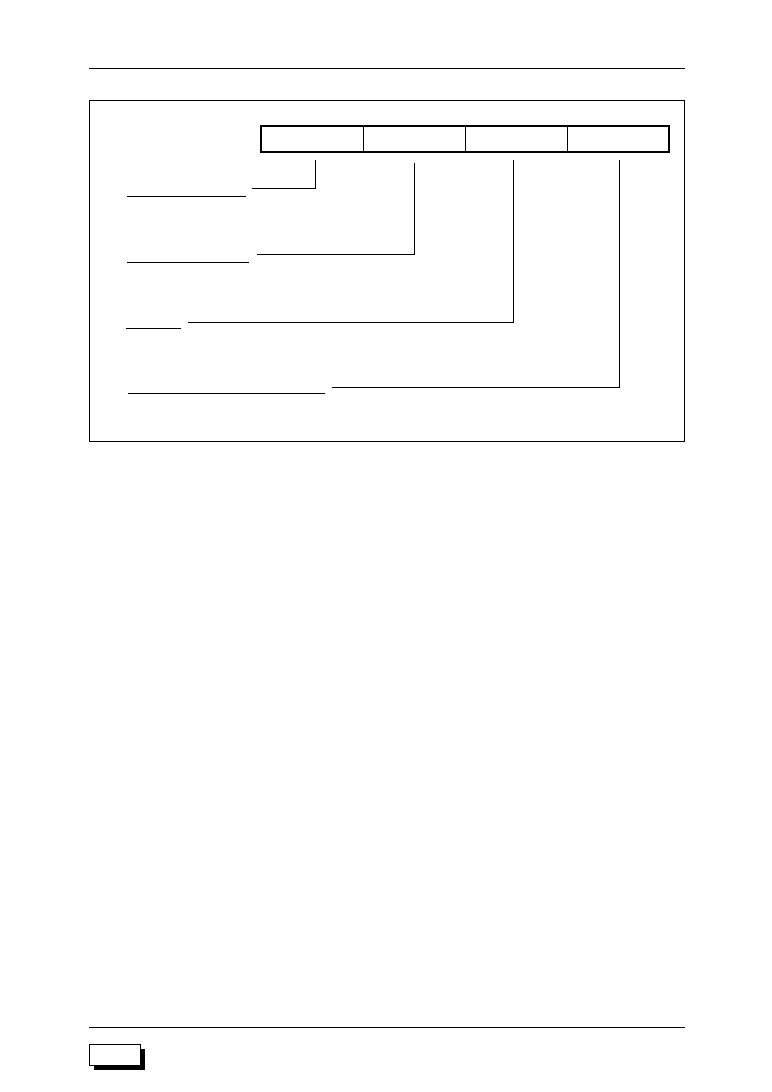

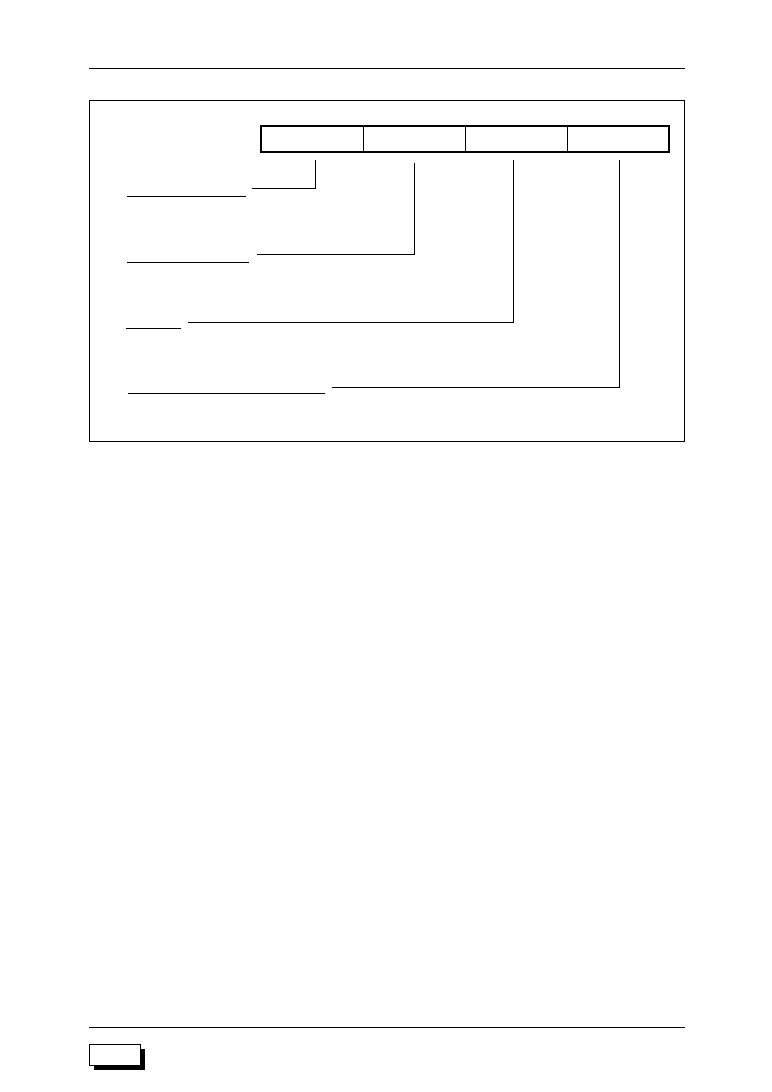

Preface

This manual describes the hardware of Oki's original CMOS 4-bit microcontrollers ML63187,

ML63189B, and ML63193.

Refer to the "nX-4/250 Core Instruction Manual" for details of the 4-bit CPU core nX-4/250

which is built in the ML63187, ML63189B, and ML63193.

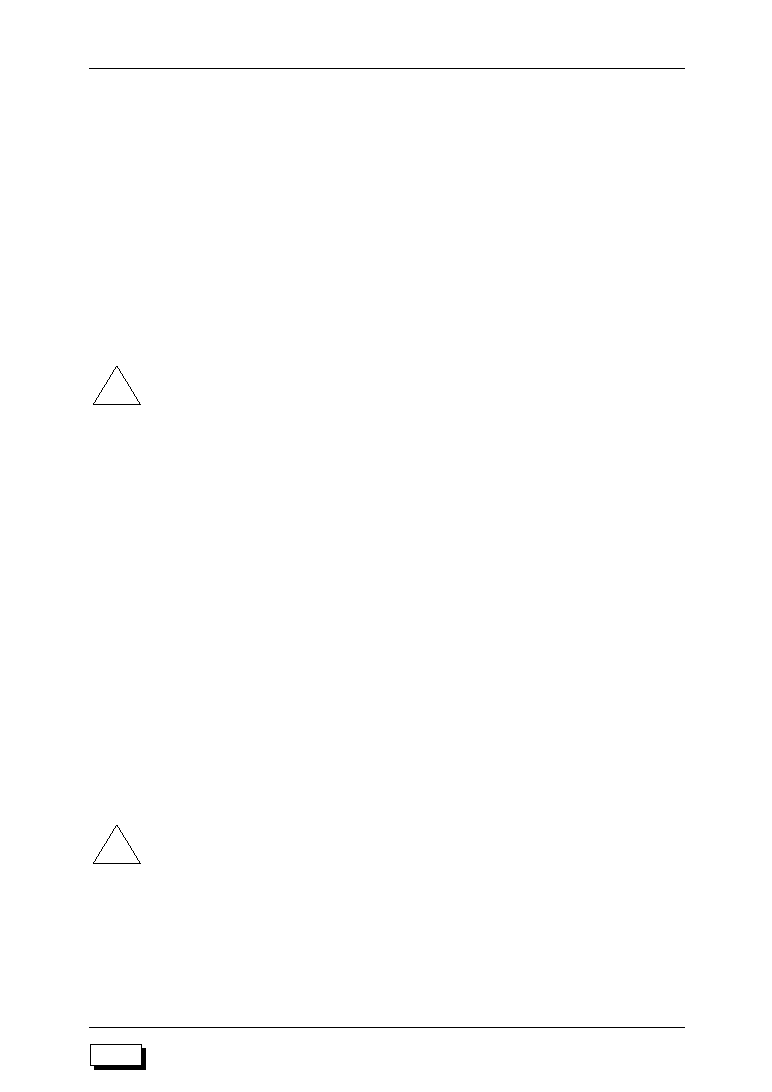

The manuals related to the ML63187, ML63189B, and ML63193 are shown below.

∑ nX-4/250 Core Instruction Manual:

Describes the base architecture and instruction set of nX-4/250 core.

∑ SASM63K User's Manual:

Describes the structured assembler operation and assembler language specifica-

tion.

∑ EASE63180 User's Manual:

Describes the hardware of the emulator.

∑ DT63K Debugger/DTS63K Simulator User's Manual:

Describes the debugger commands and the hardware of the simulator.

This document is subject to change without notice.

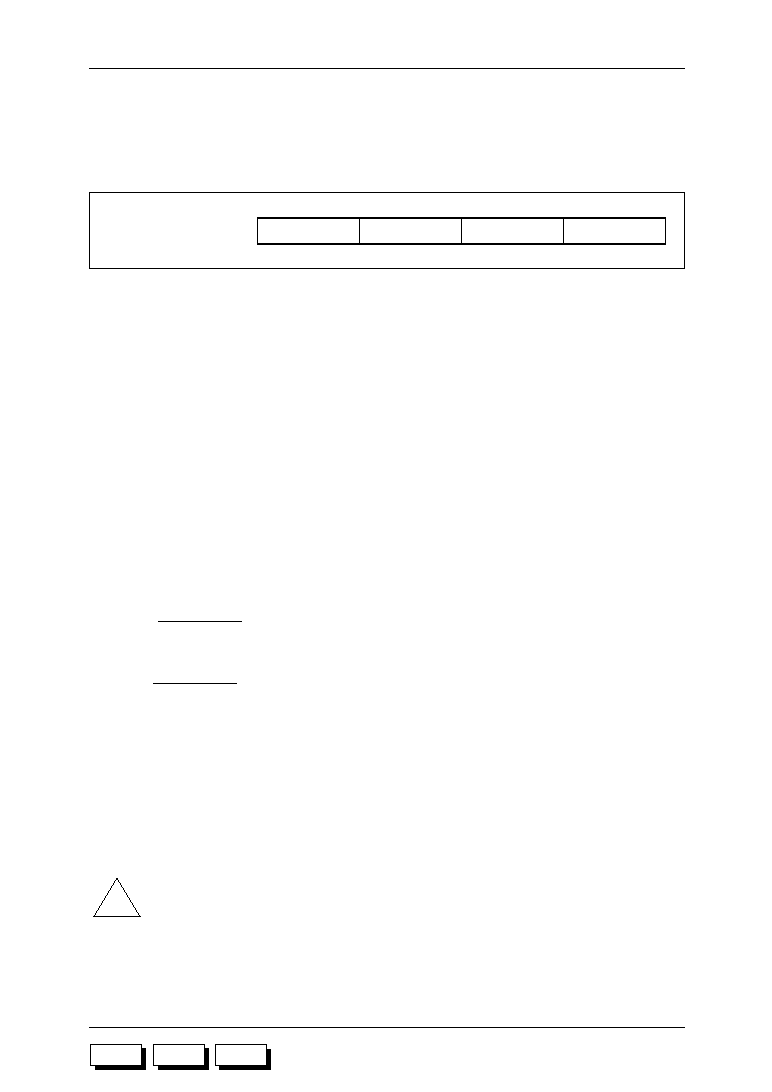

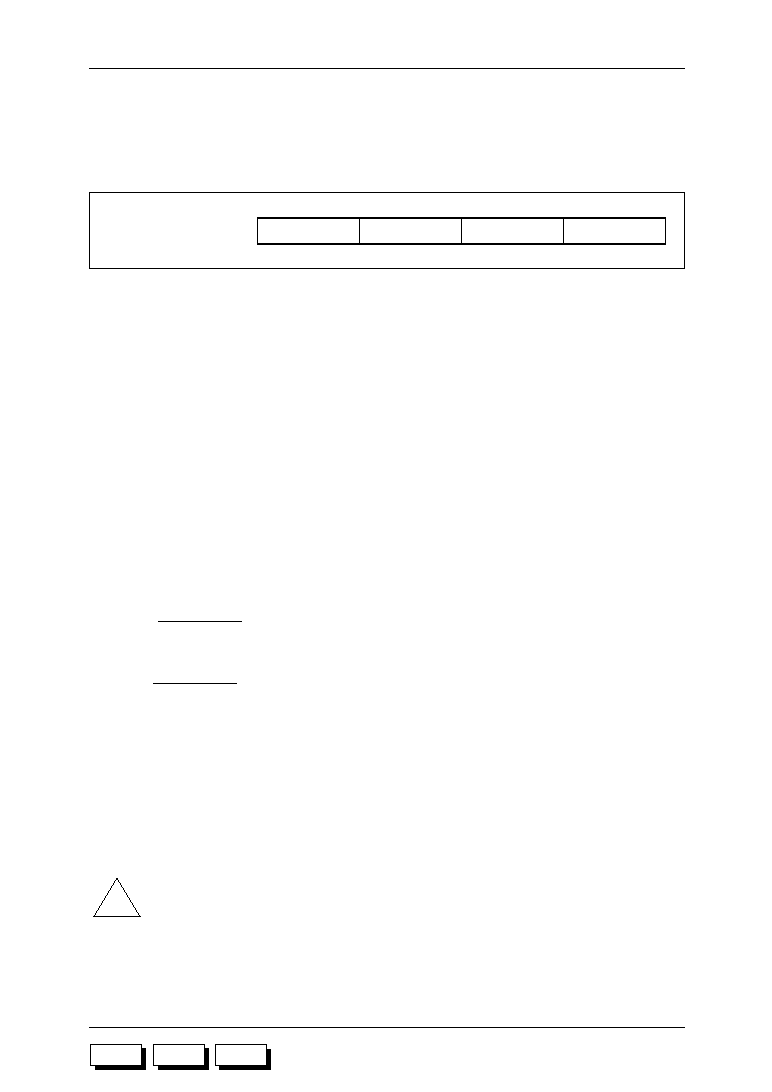

Notation

Classification

Notation

Description

n Numeric value

xxh, xxH

Represents a hexadecimal number.

xxb

Represents a binary number.

n Unit

word, W

1 word = 16 bits

byte, B

1 byte = 2 nibbles = 8 bits

nibble, N

1 nibble = 4 bits

mega-, M

10

6

kilo-, K

2

10

= 1024

kilo-, k

10

3

= 1000

milli-, m

10

-3

micro-,

m

10

-6

nano-, n

10

-9

second, s (lower case)

second

KB

1 KB = 1 kilobyte = 1024 bytes

MB

1 MB = 1 megabyte = 2

20

bytes

= 1,048,576 bytes

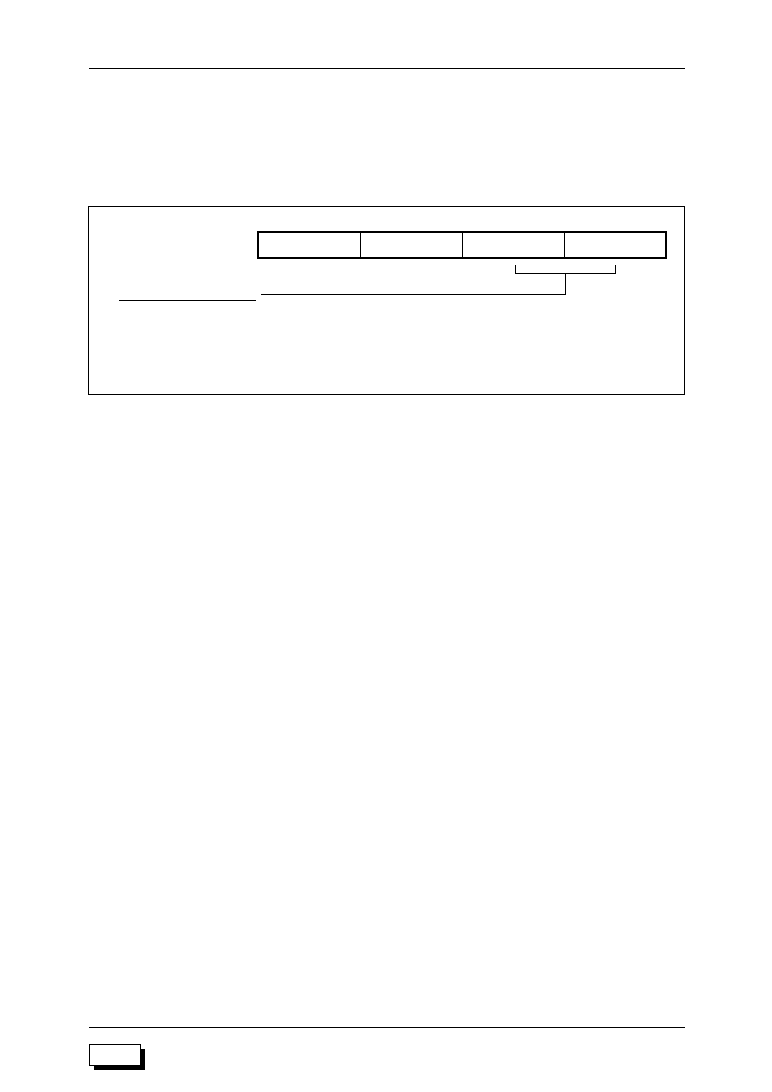

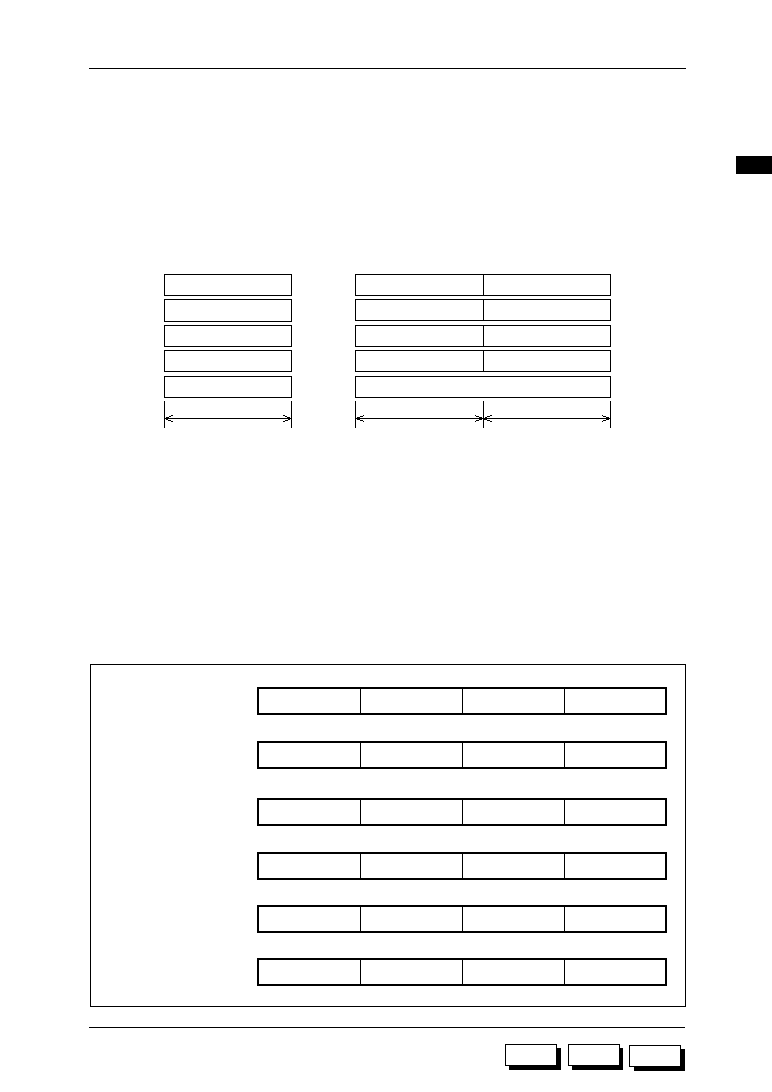

n Symbol

Note:

Gives more information about mistakable items.

A chapter or page with this symbol describes the ML63187.

A chapter or page with this symbol describes the ML63189B.

A chapter or page with this symbol describes the ML63193.

n Terminology

"H" level

Indicates high side voltage signal levels V

IH

and

V

OH

as specified by the electrical characteristics.

"L" level

Indicates low side voltage signal levels V

IL

and

V

OL

as specified by the electrical characteristics.

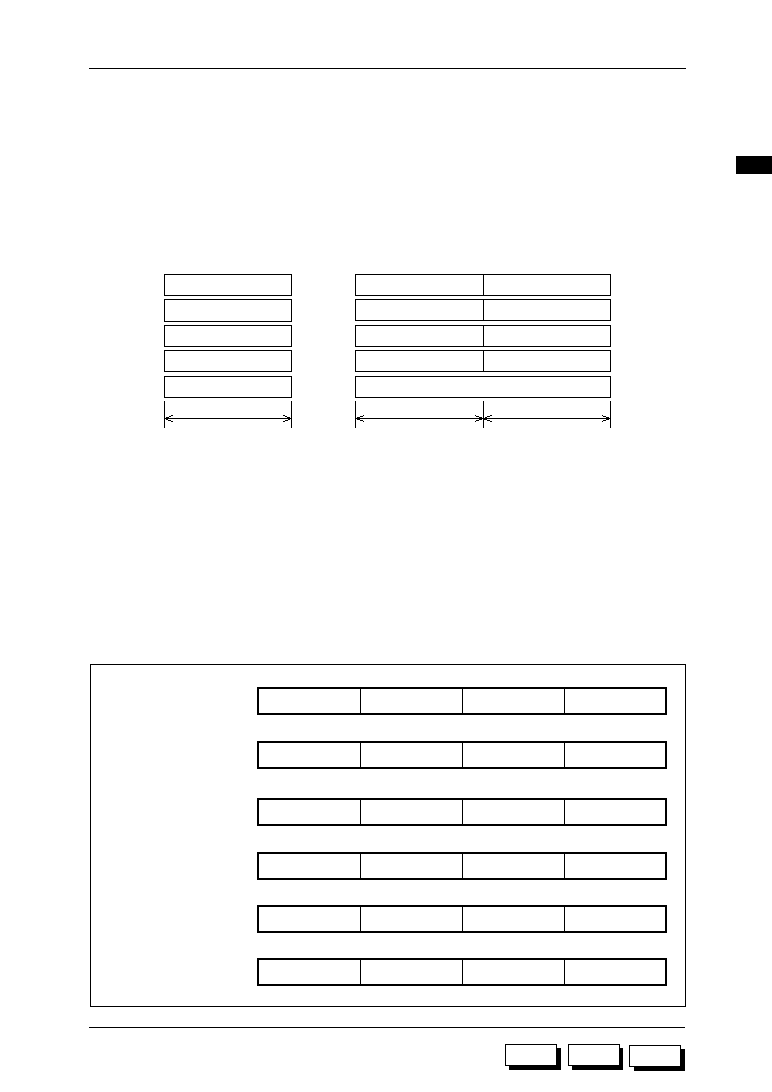

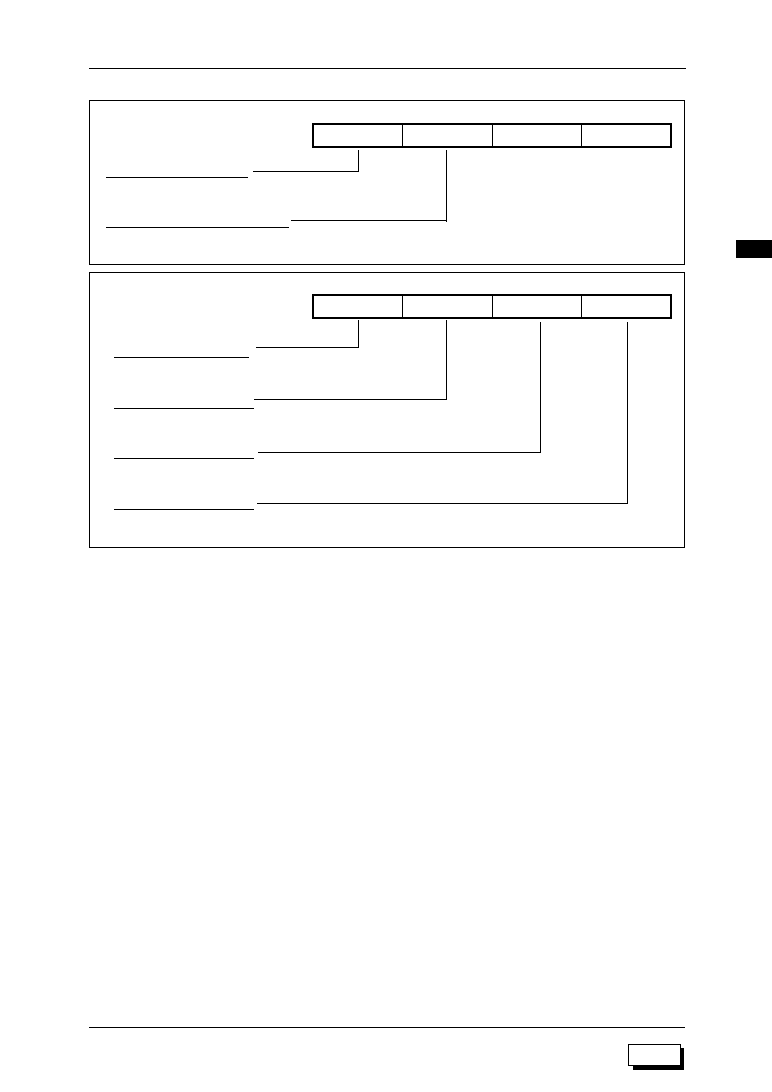

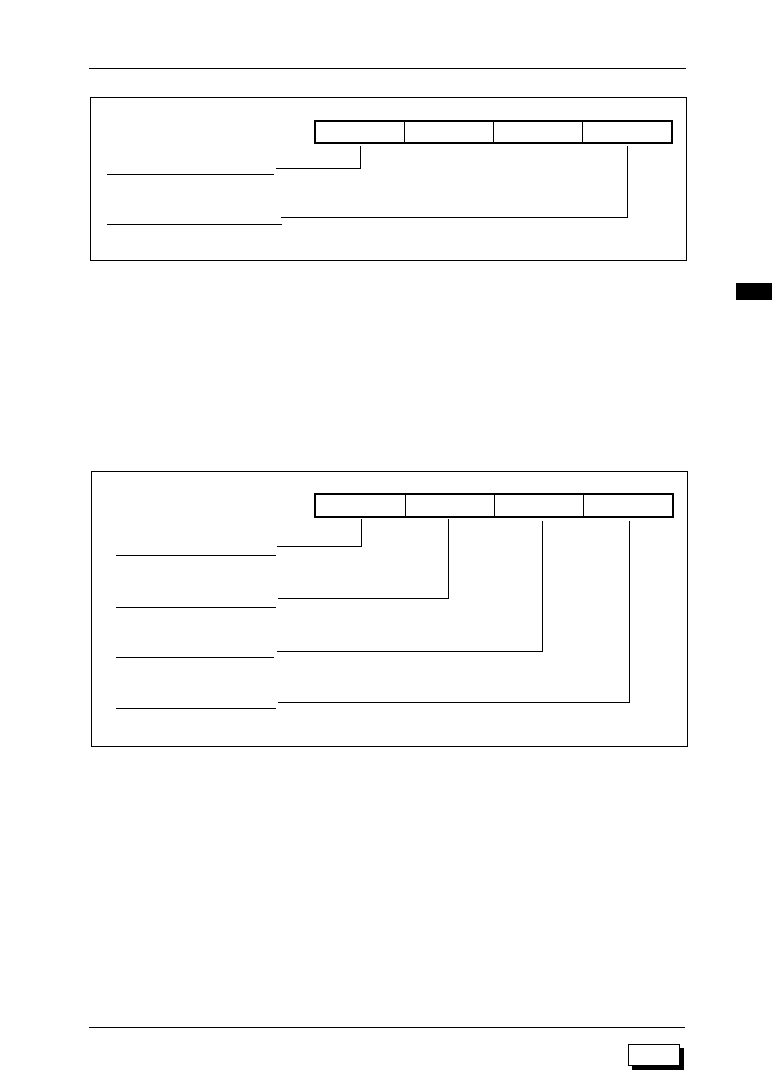

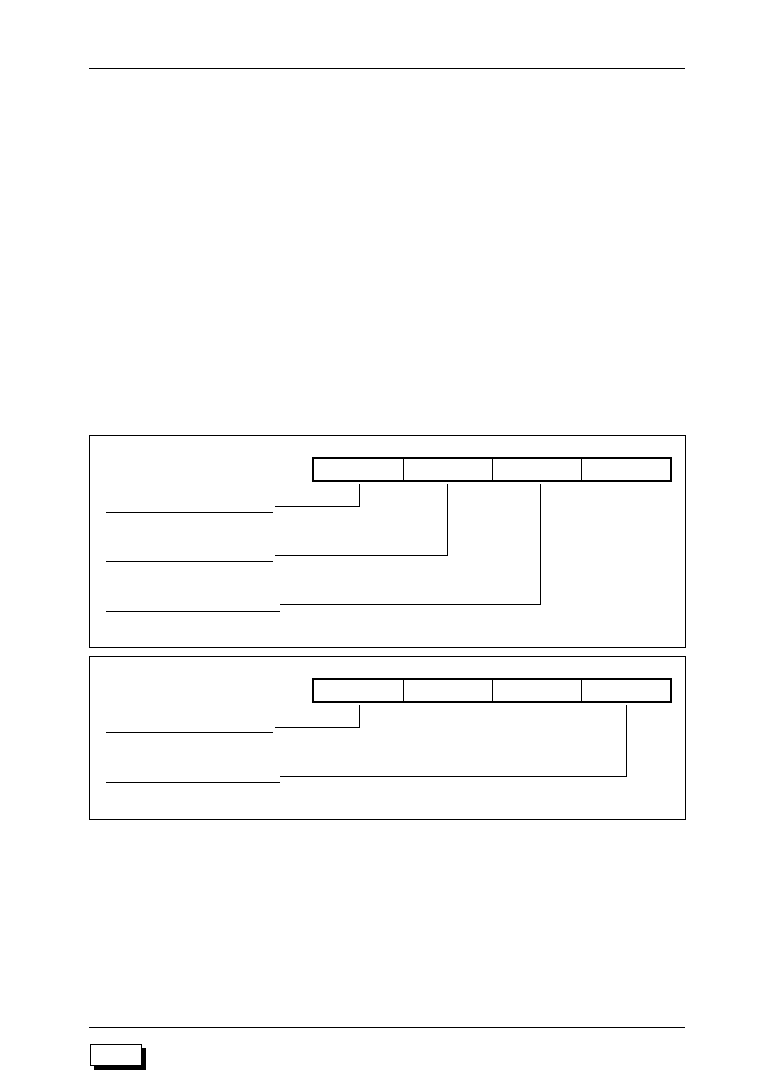

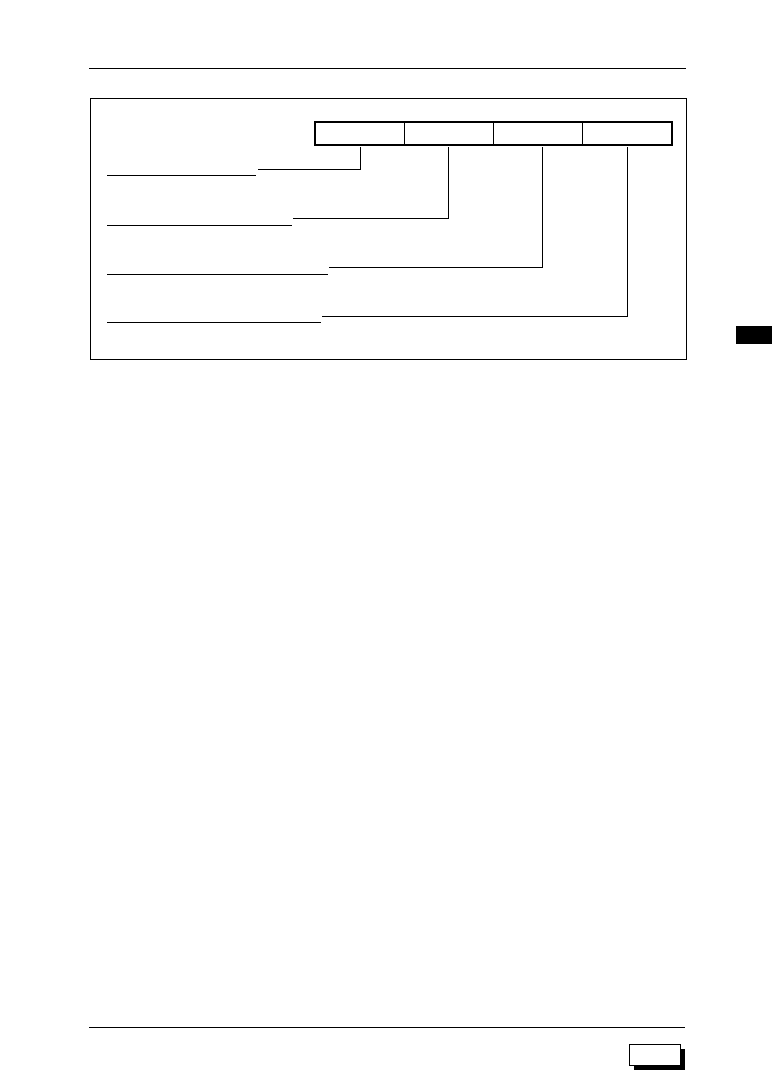

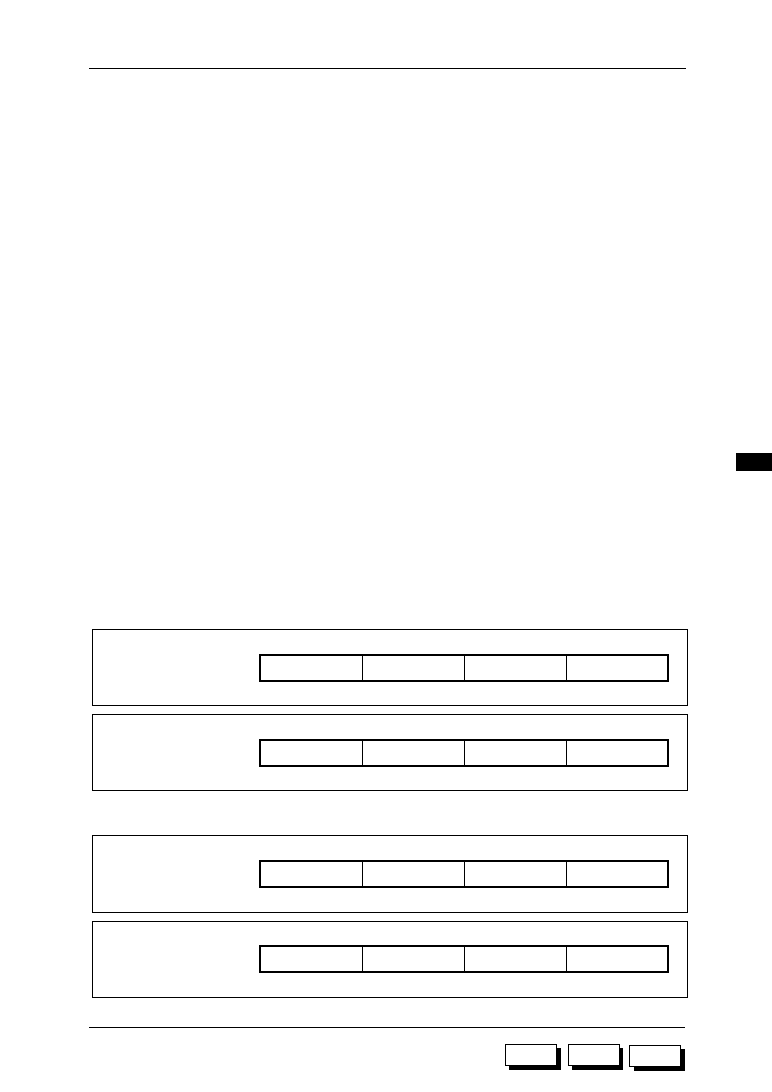

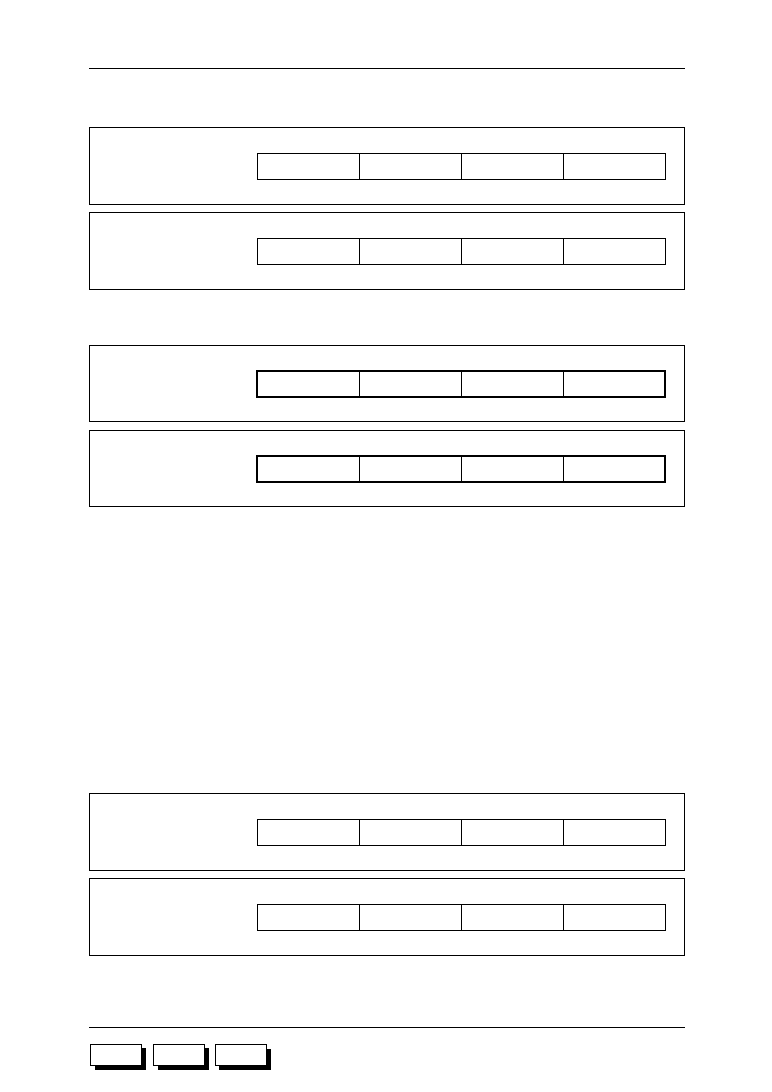

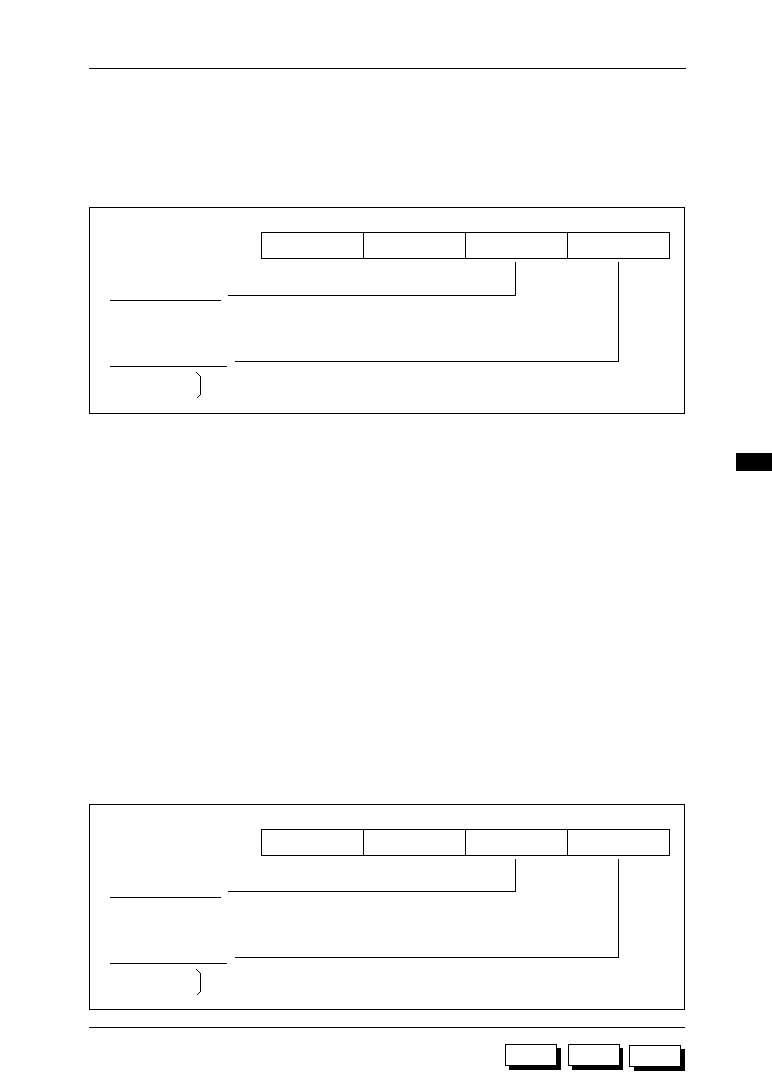

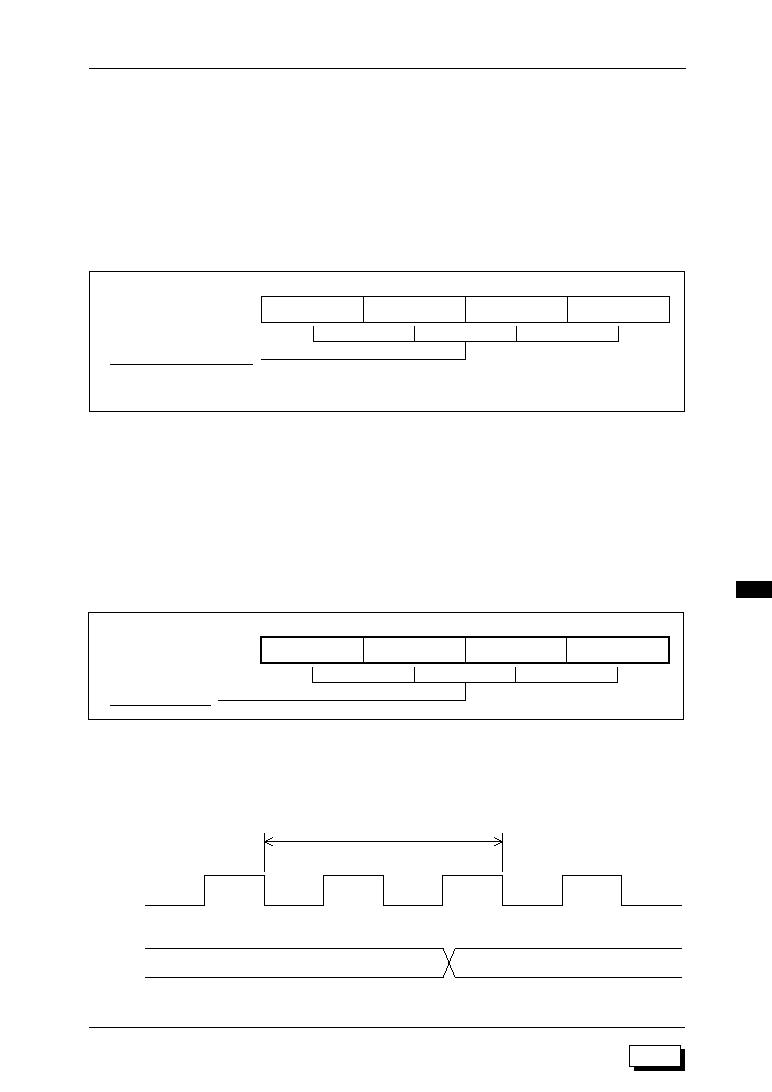

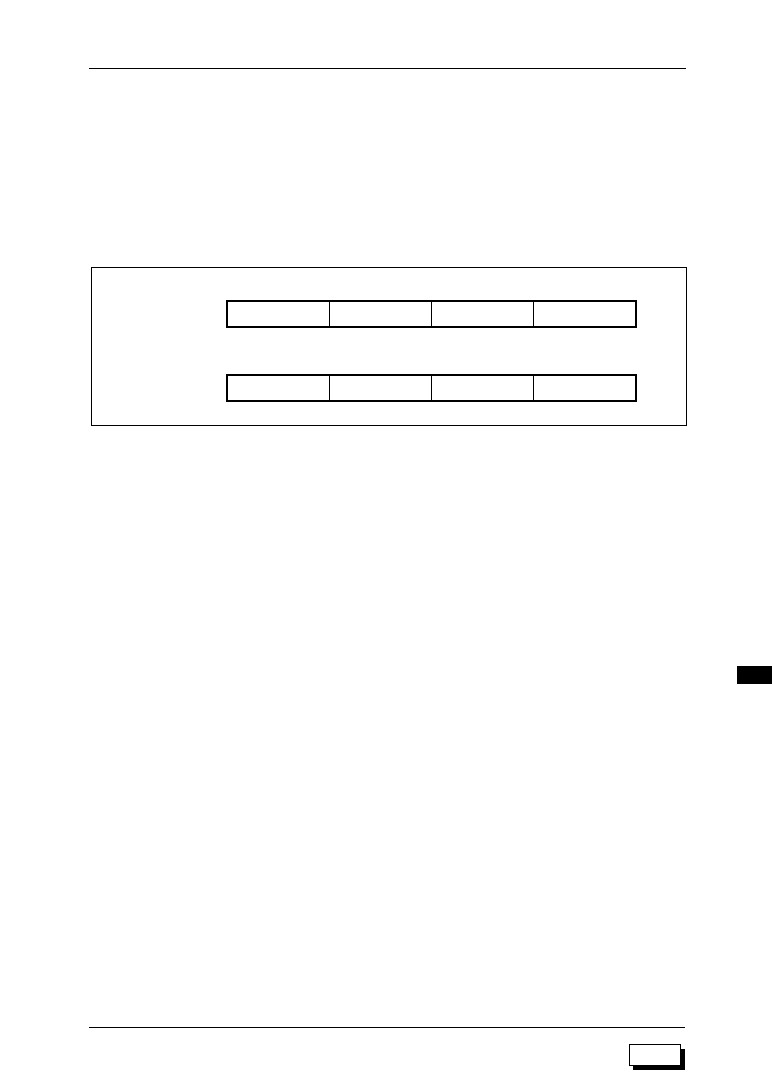

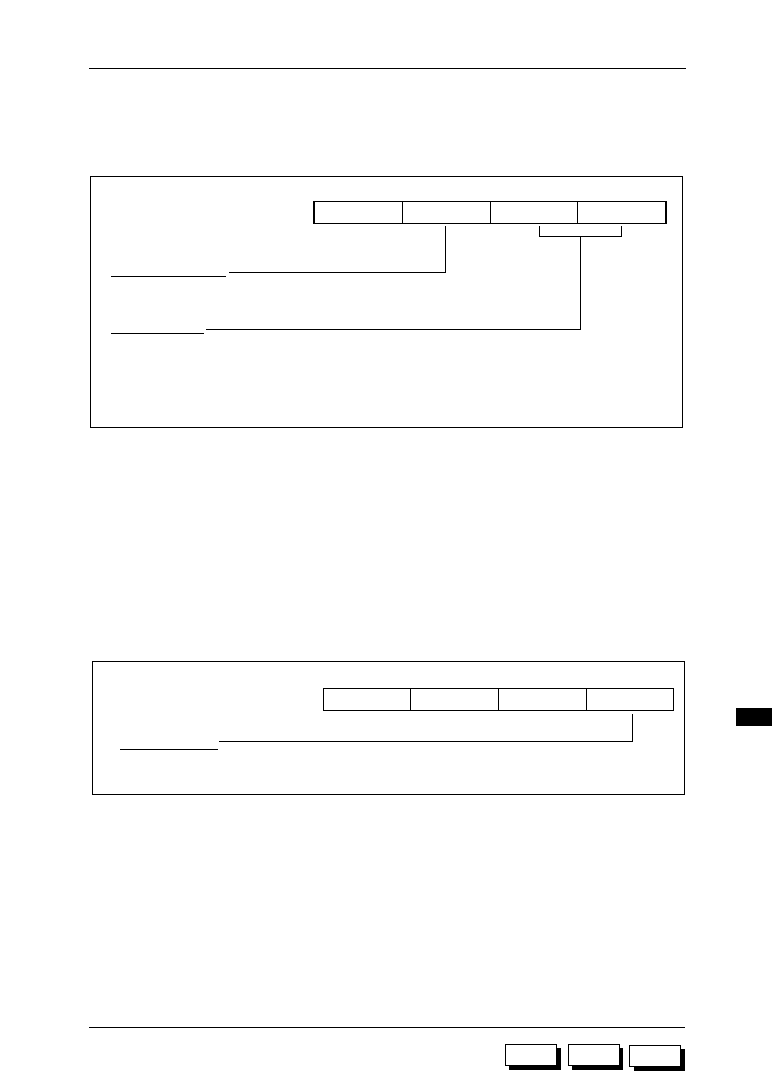

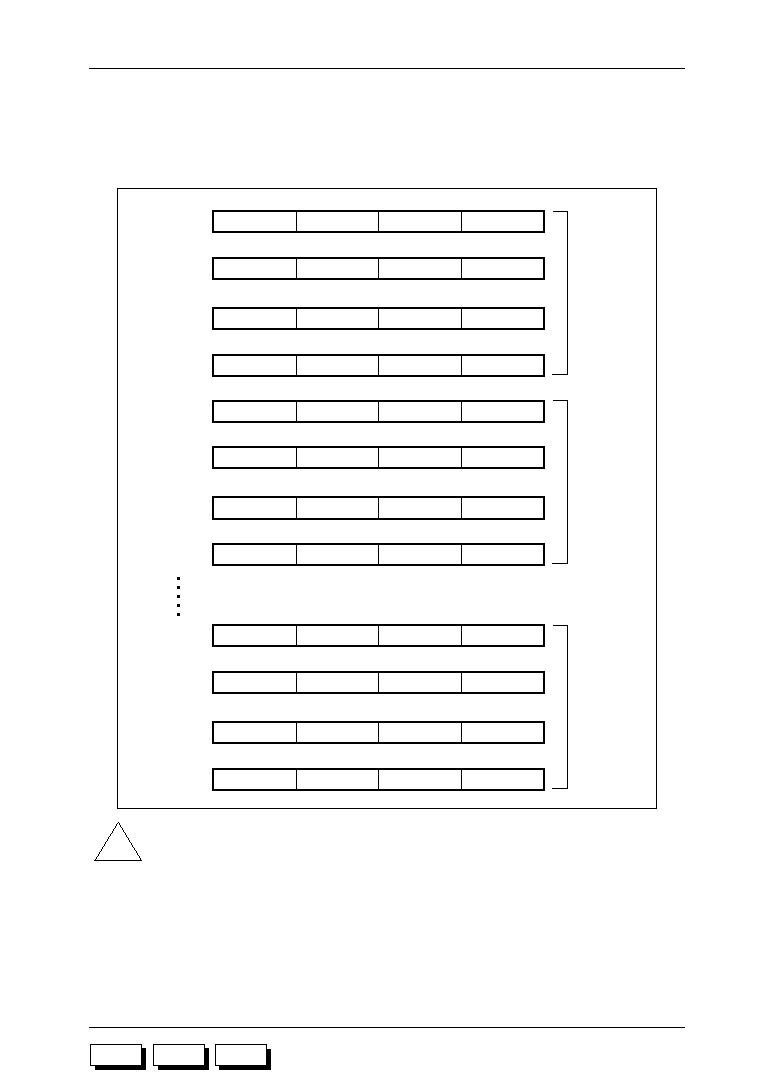

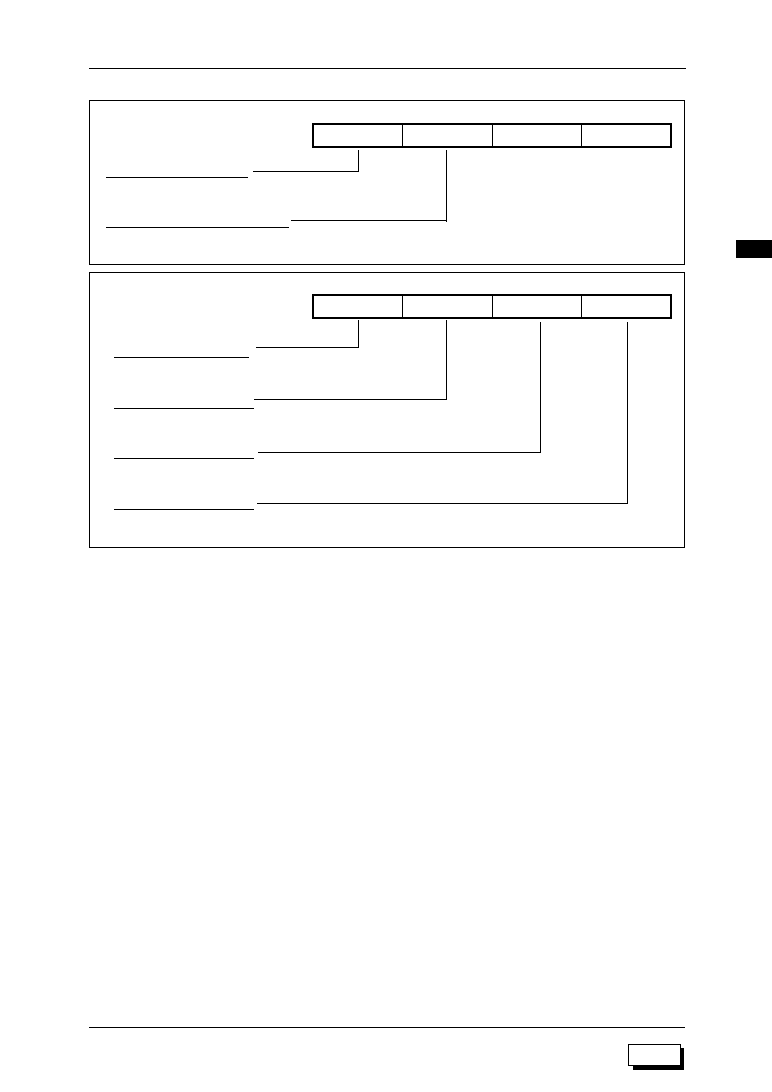

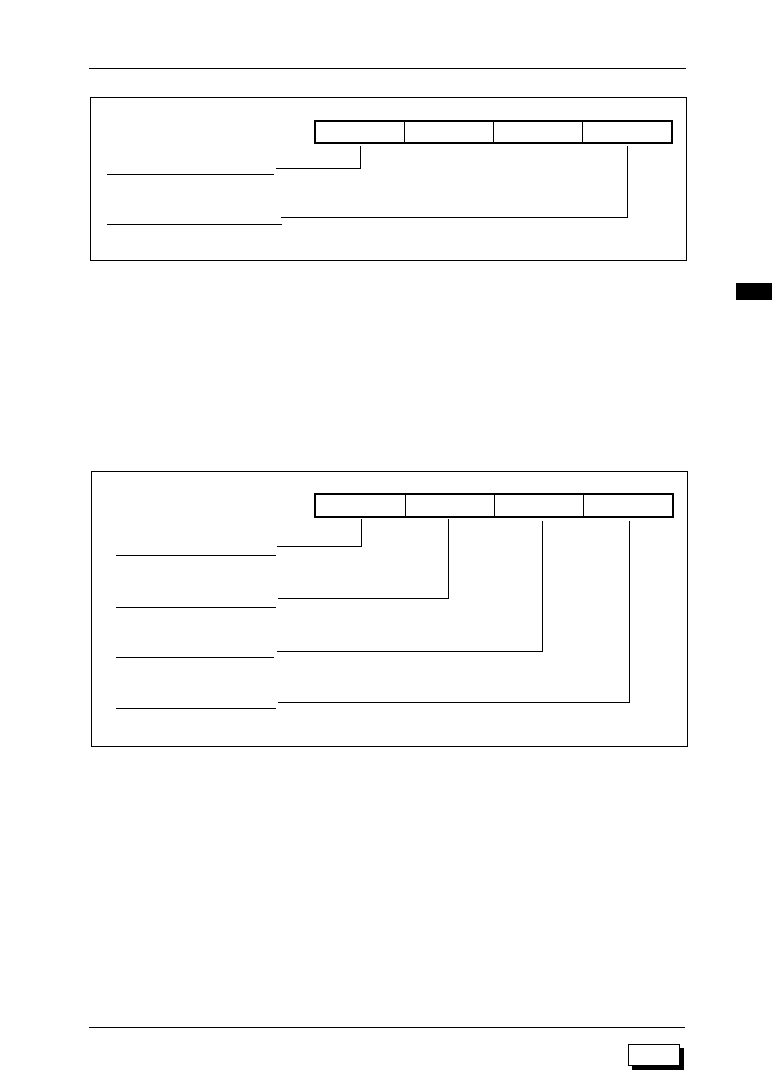

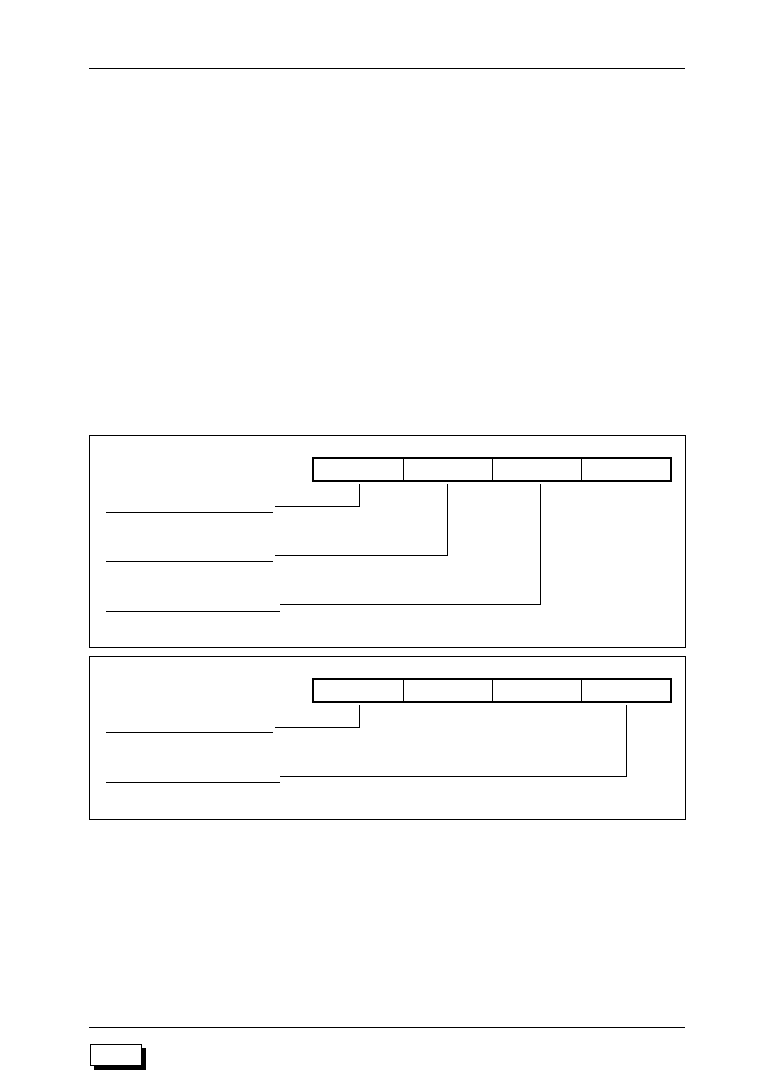

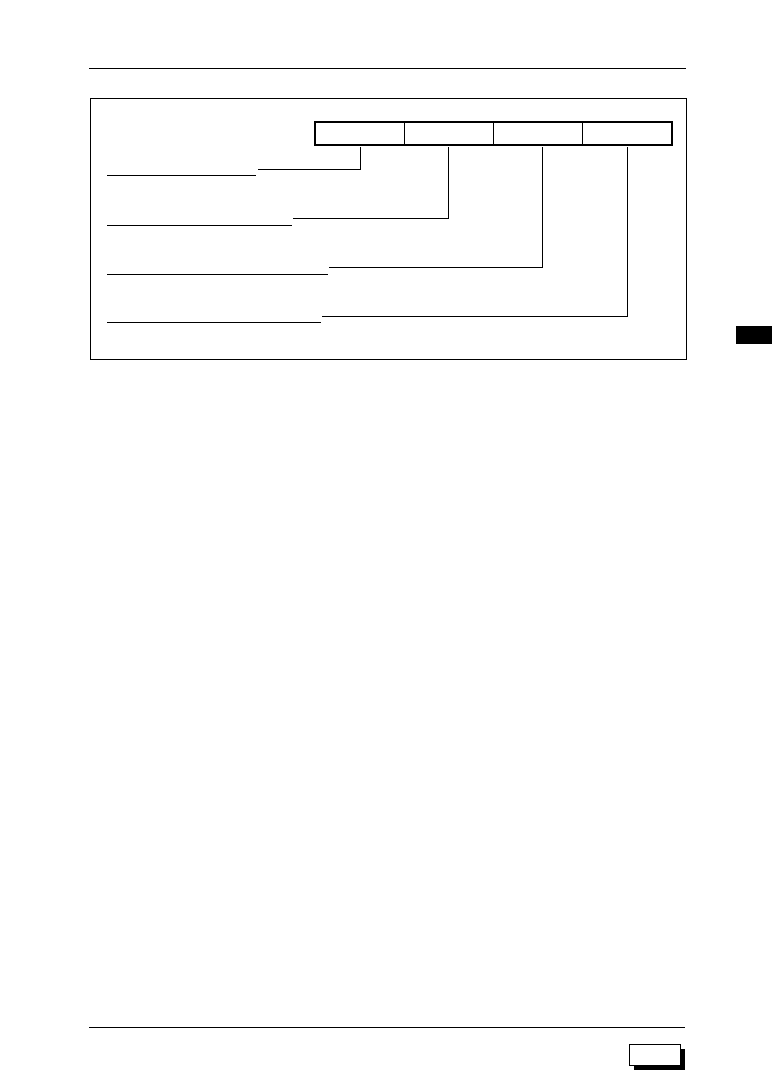

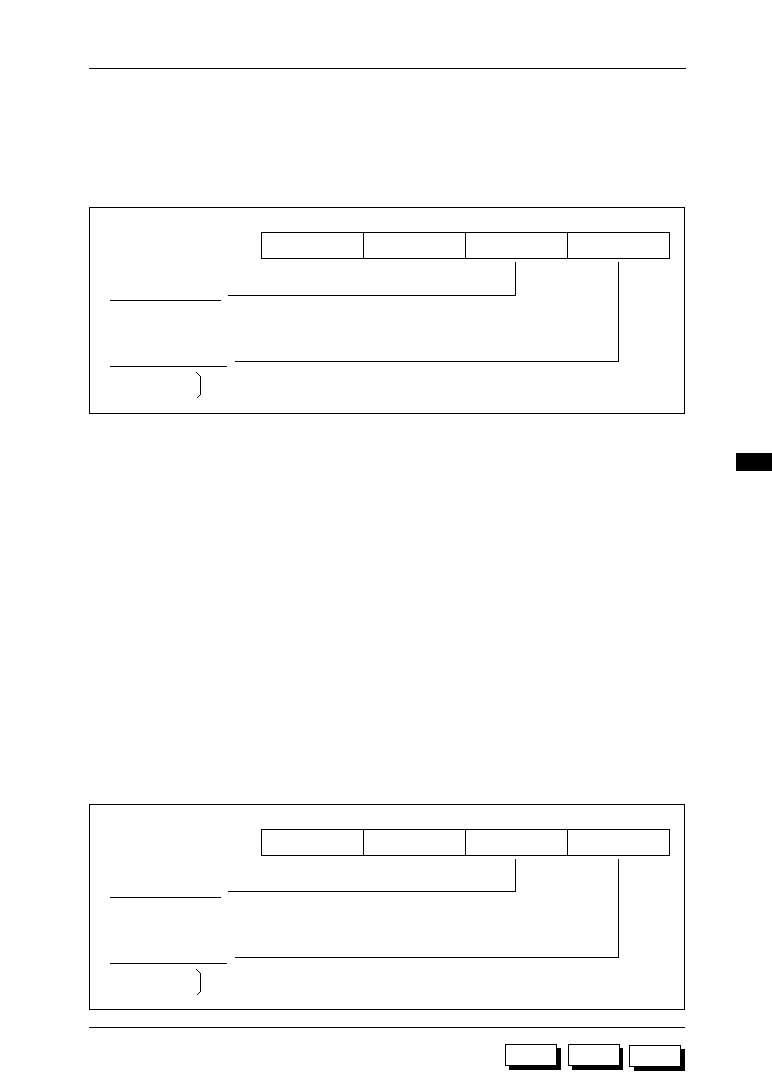

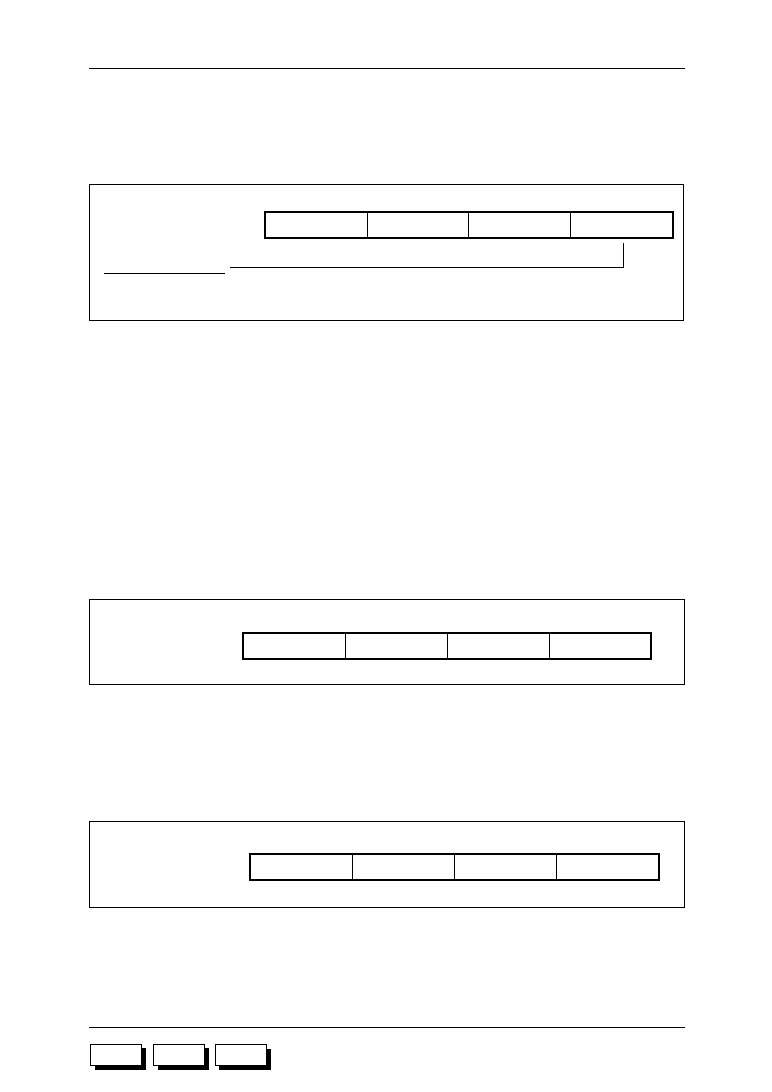

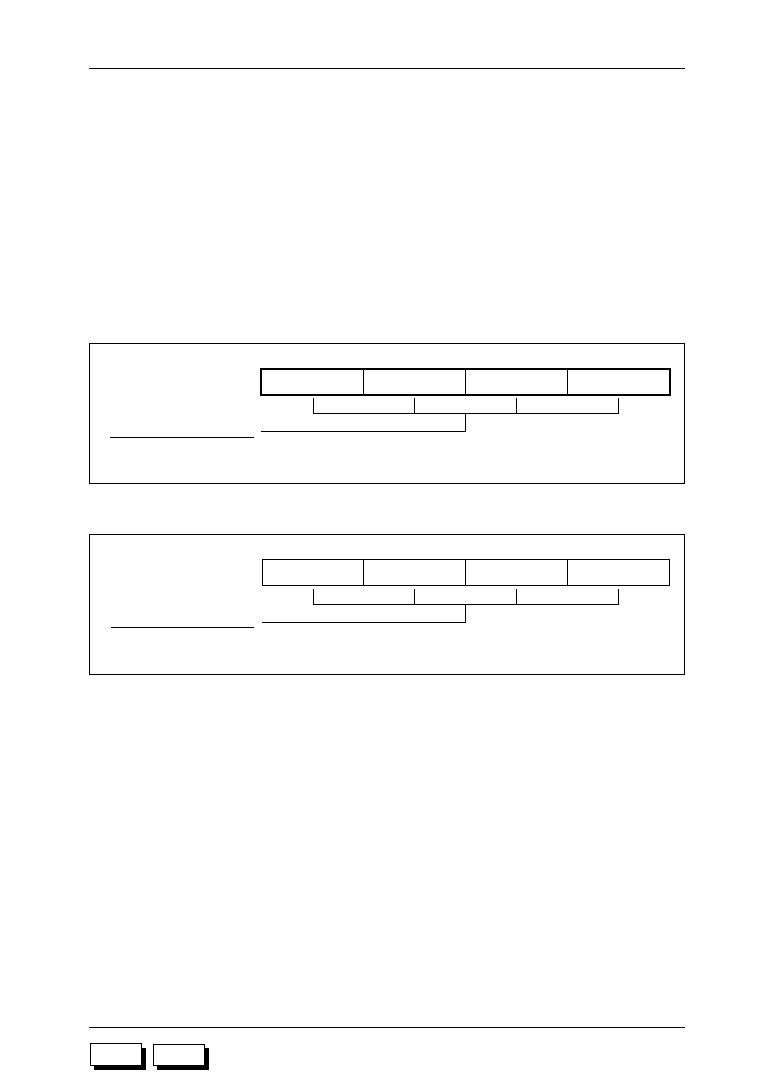

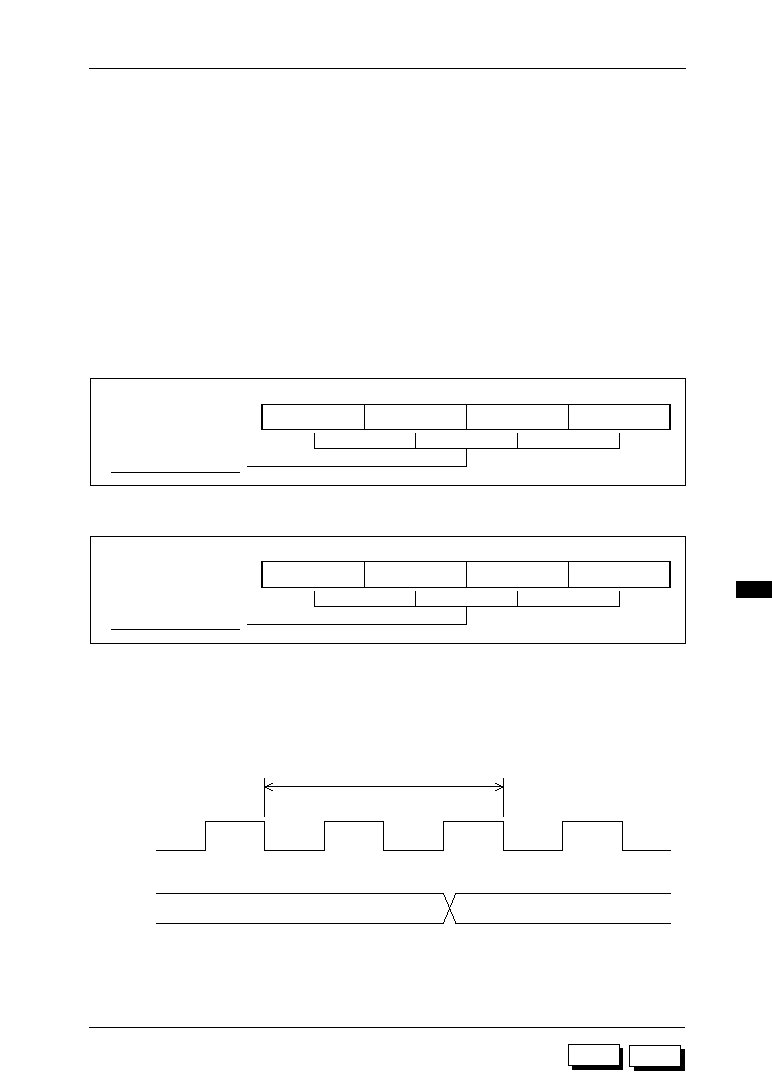

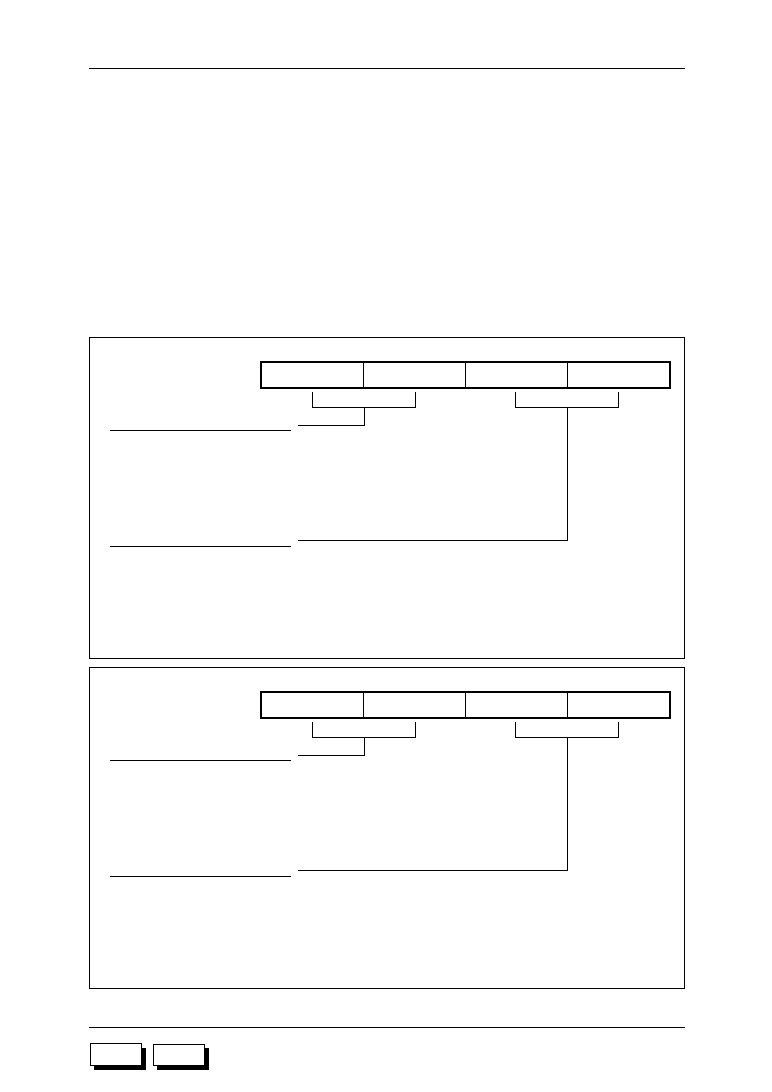

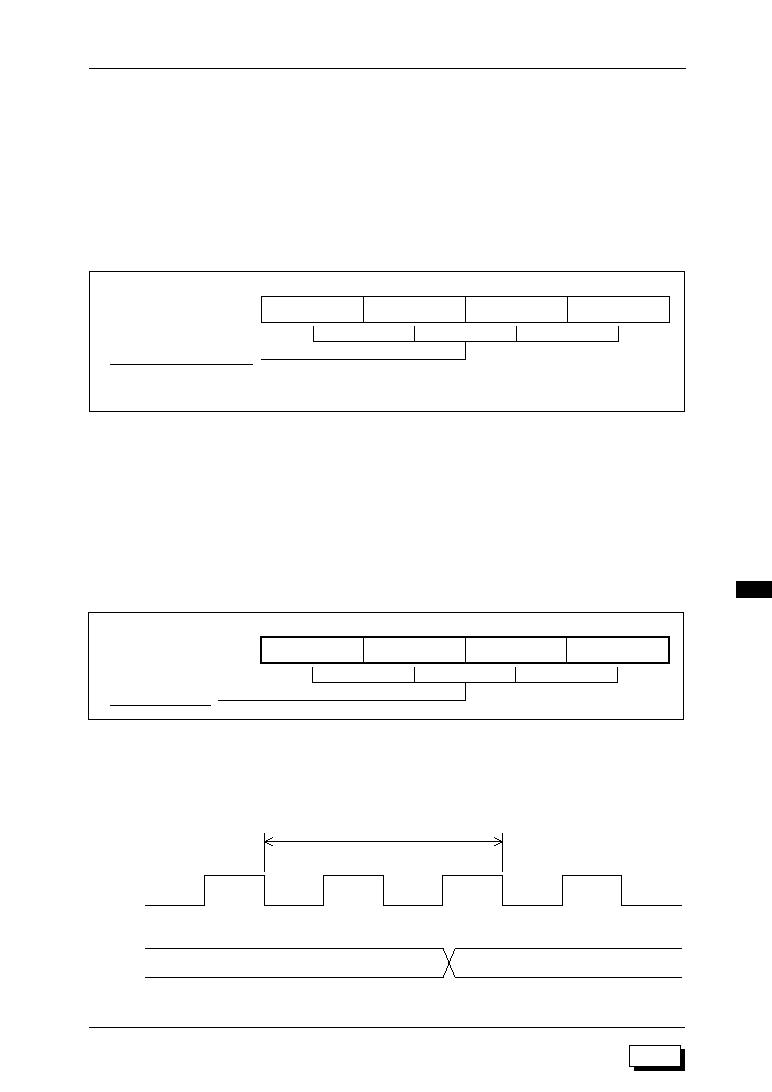

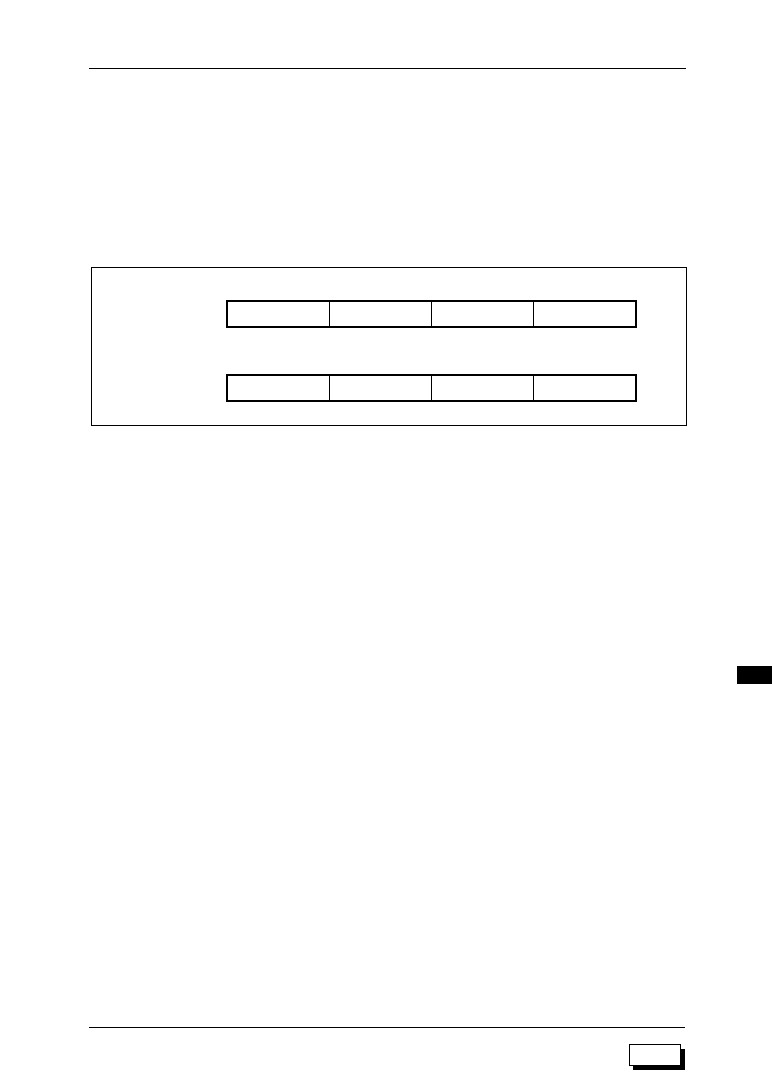

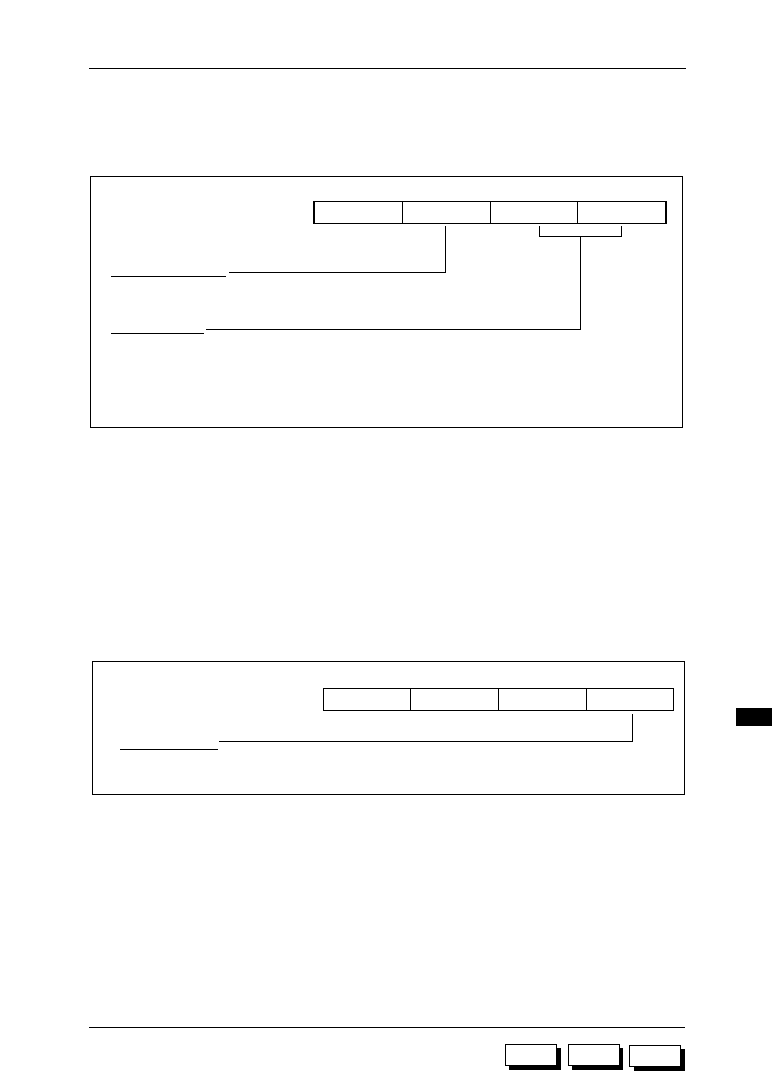

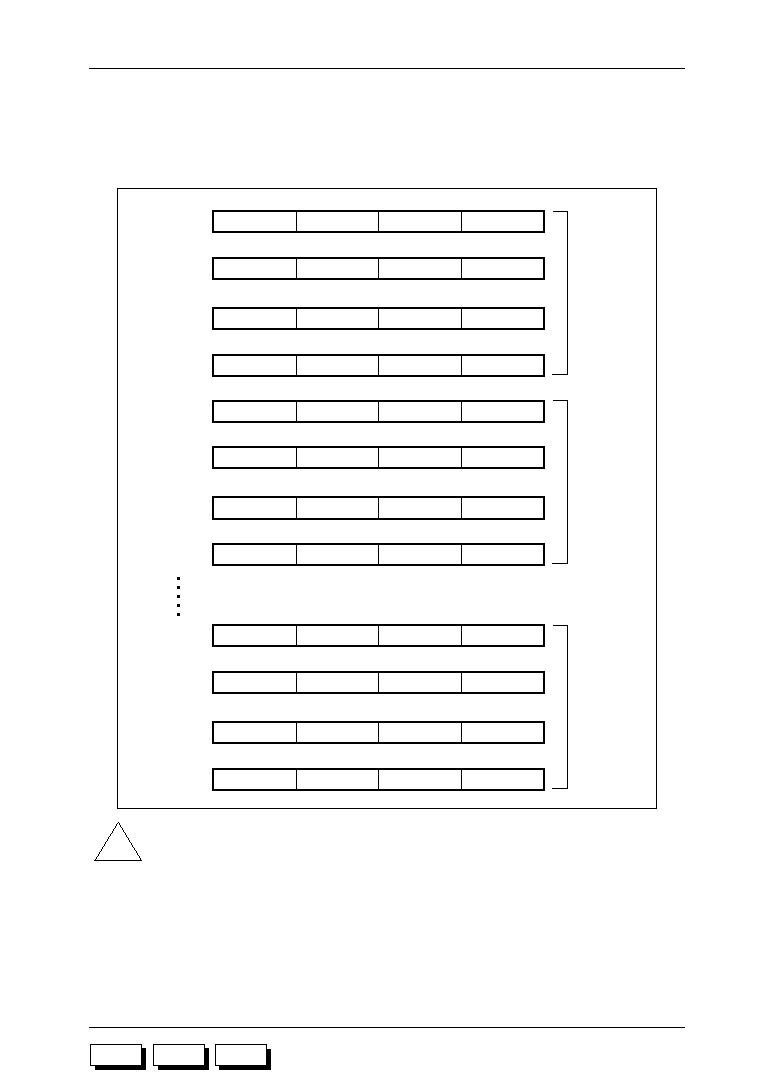

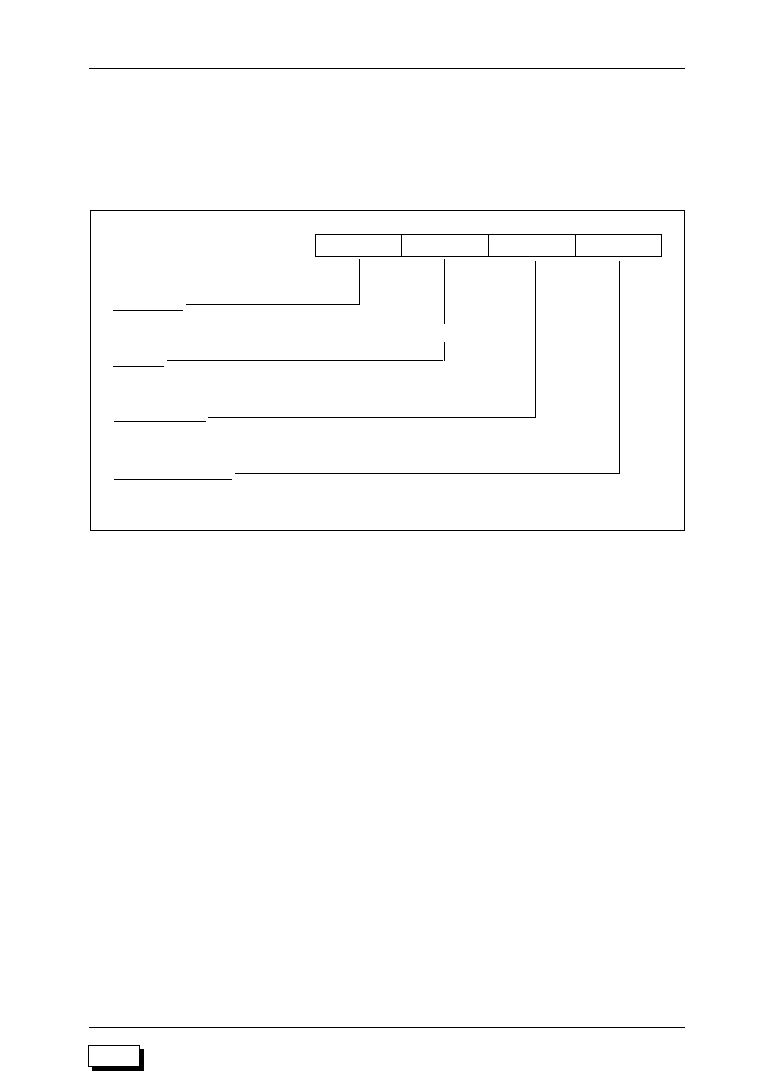

n Register description

Invalid bit

:

When read, a value of "1" is always obtained. Write operations are invalid.

R/W attribute

:

"R" indicates data can be read and "W" indicates data can be written.

!

M187

M189B

Bit name

Invalid bit

Address

R/W attribute

Register name

PBF

--

PB1MOD

PB0MOD

bit 3

bit 2

bit 1

bit 0

PBMOD0

(032H)

(R/W)

M193

- i -

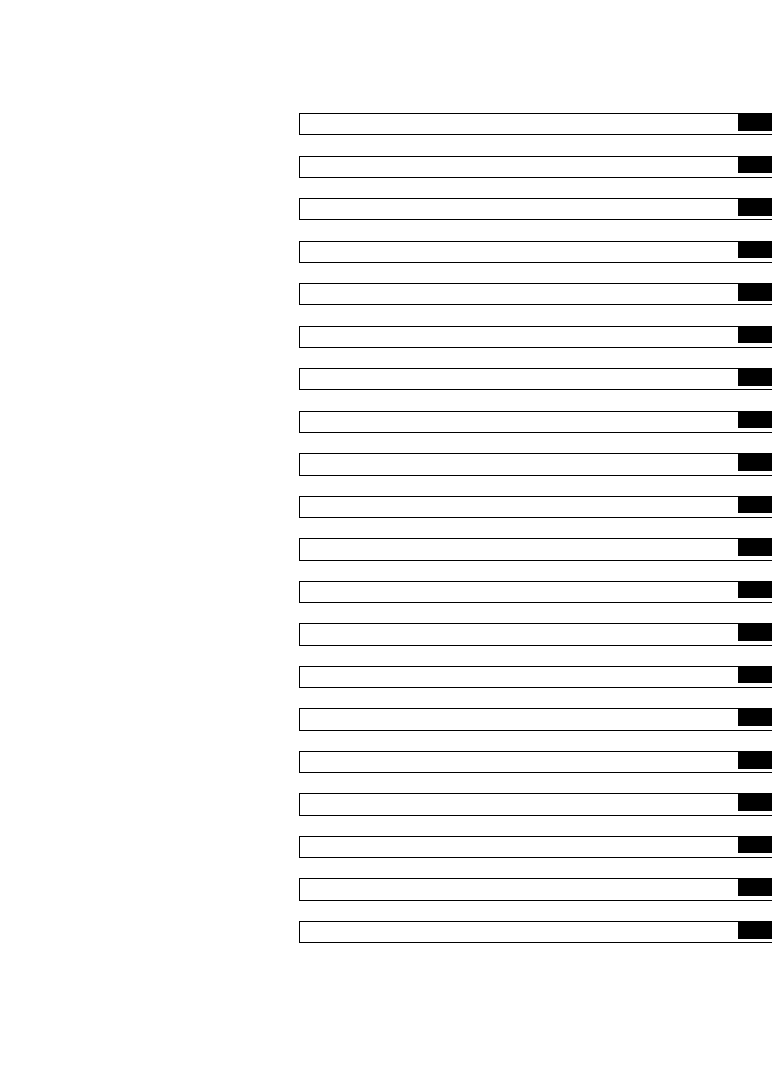

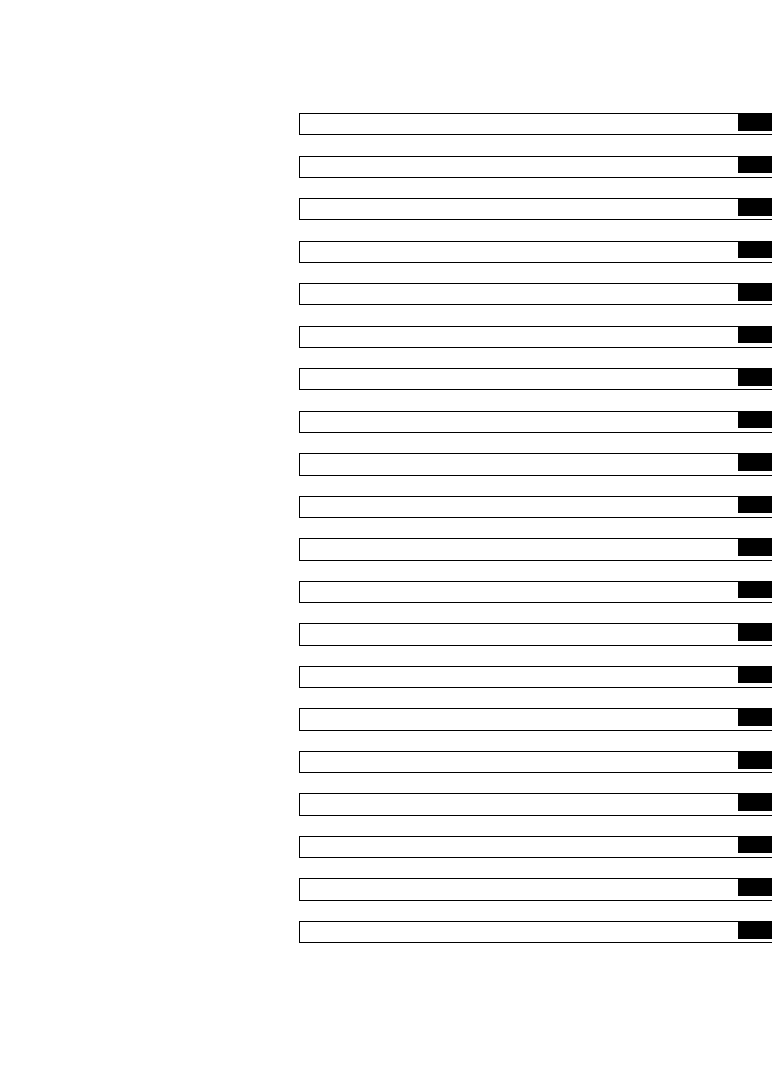

Table of Contents

Chapter 1 Overview

1.1 Overview ........................................................................................................ 1-1

1.2 Features ......................................................................................................... 1-1

1.3 Function List .................................................................................................. 1-5

1.4 Block Diagram ................................................................................................ 1-6

1.5 Pin Configuration ........................................................................................... 1-9

1.5.1 ML63187 Pin Configuration ................................................................ 1-9

1.5.2 ML63189B Pin Configuration .............................................................. 1-13

1.5.3 ML63193 Pin Configuration ................................................................ 1-17

1.6 Pin Descriptions ............................................................................................. 1-21

1.6.1 Descriptions of the Basic Functions of Each Pin ................................ 1-21

1.6.2 Descriptions of the Secondary Functions of Each Pin ........................ 1-26

1.6.3 Handling of Unused Pins .................................................................... 1-28

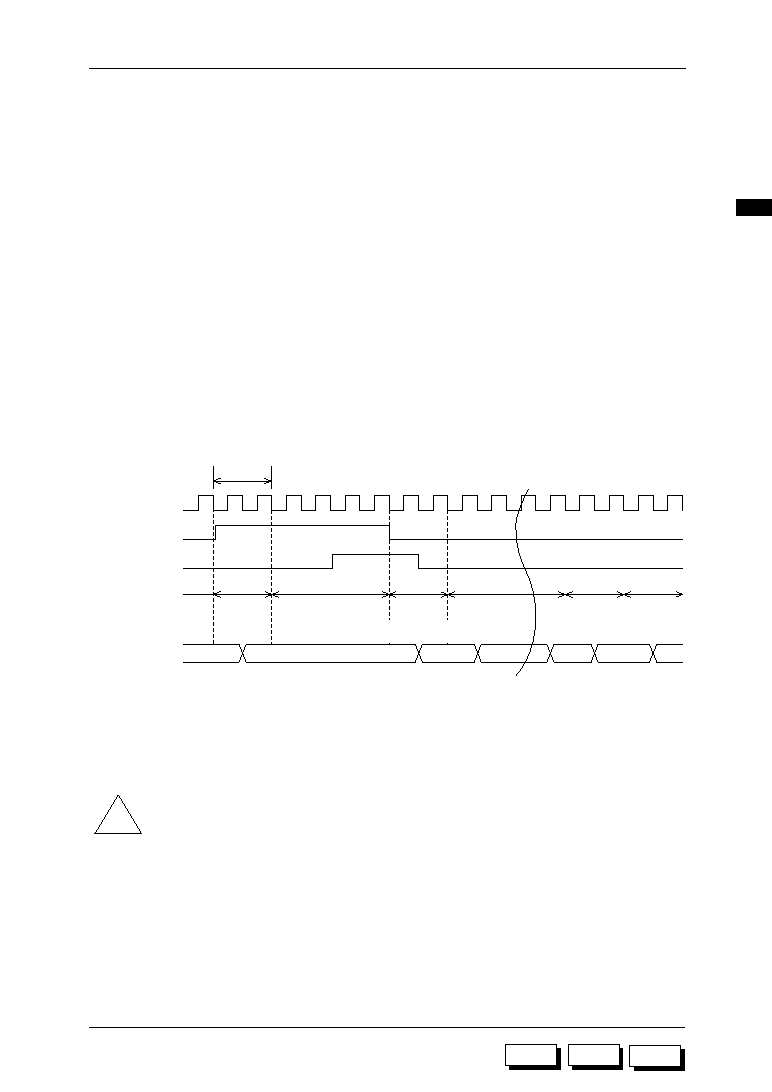

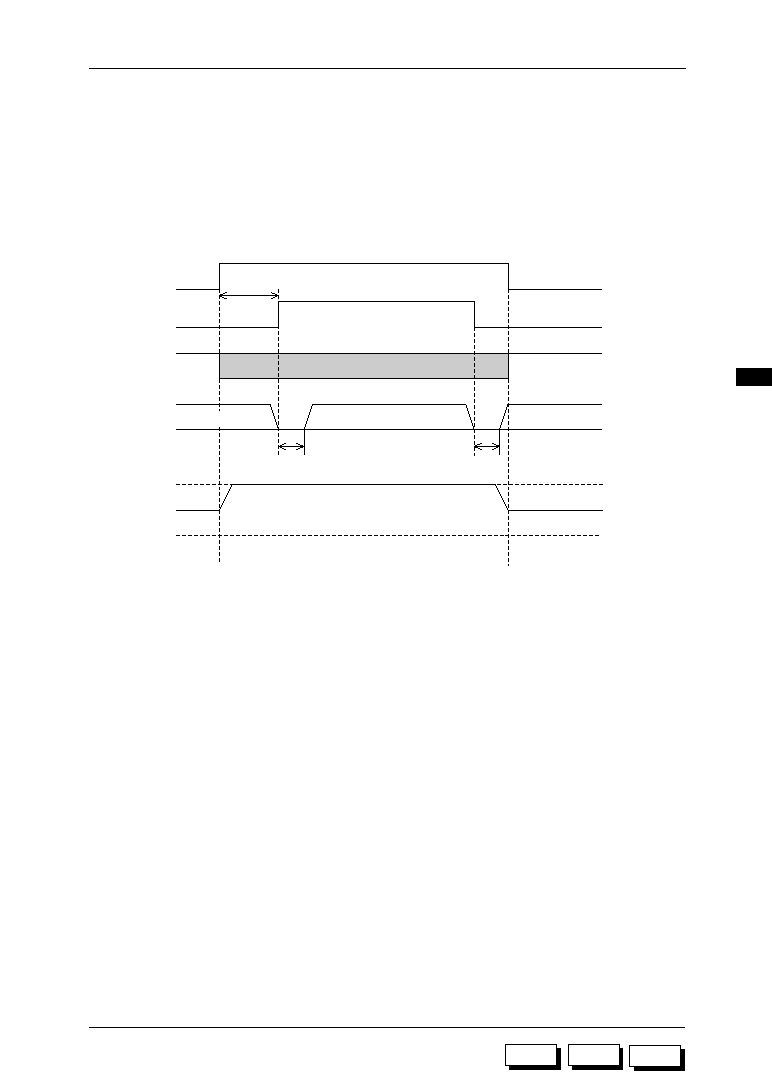

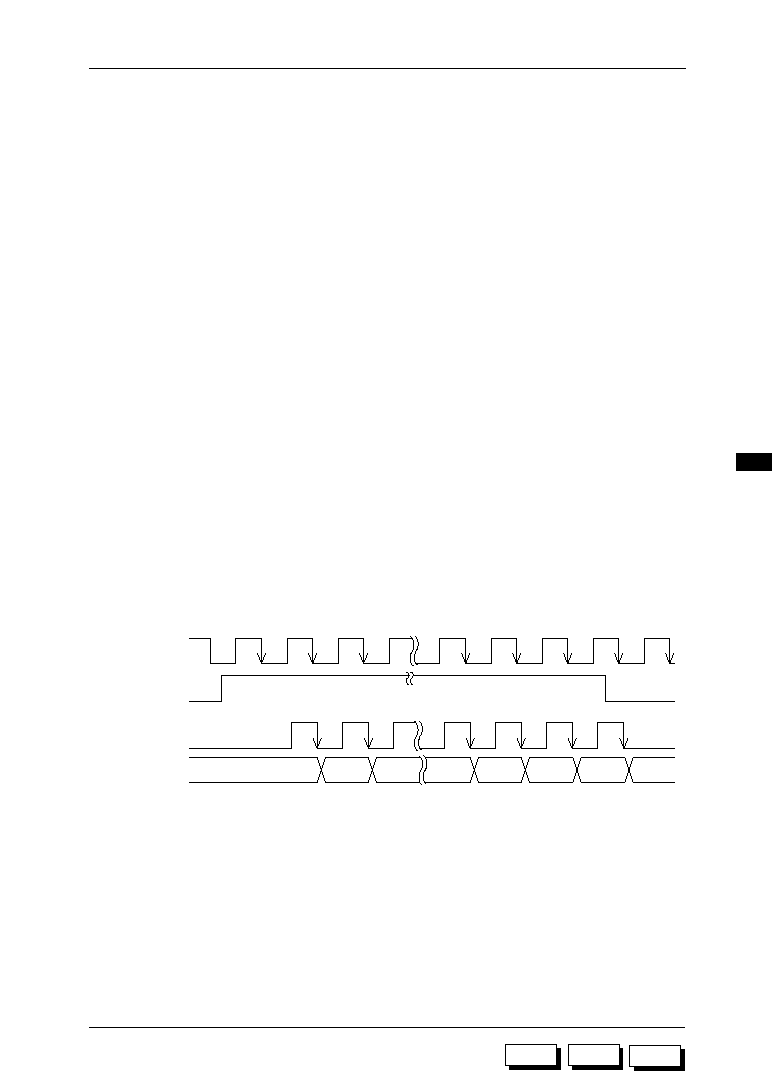

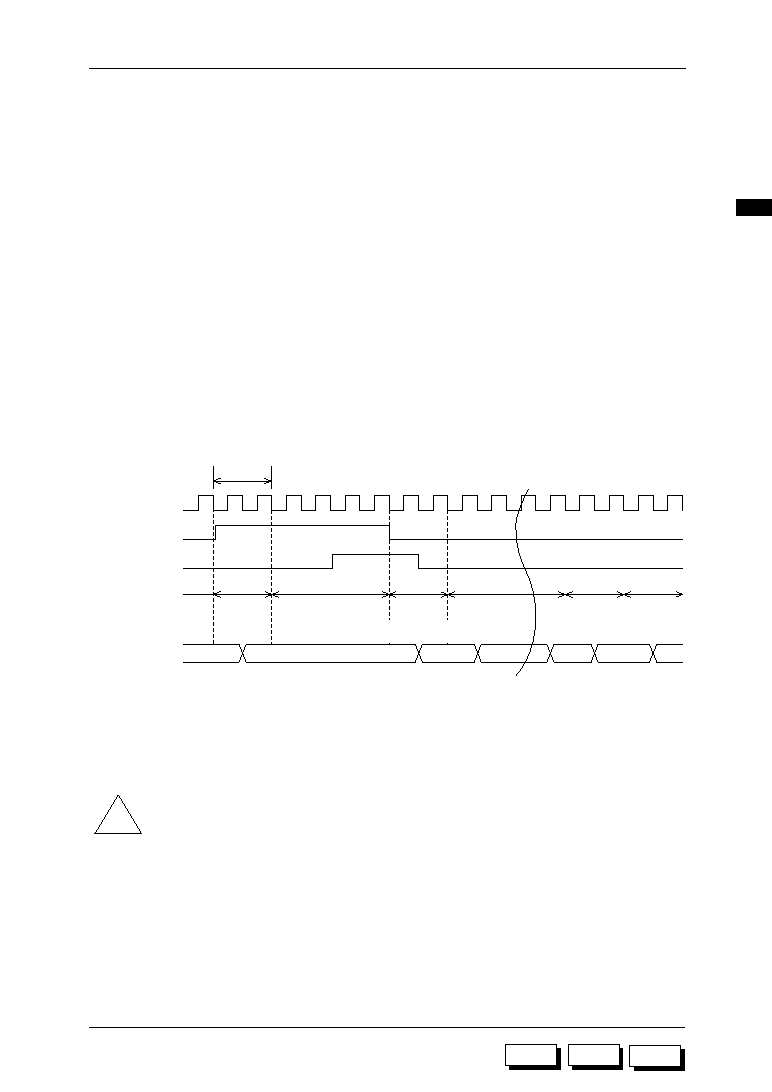

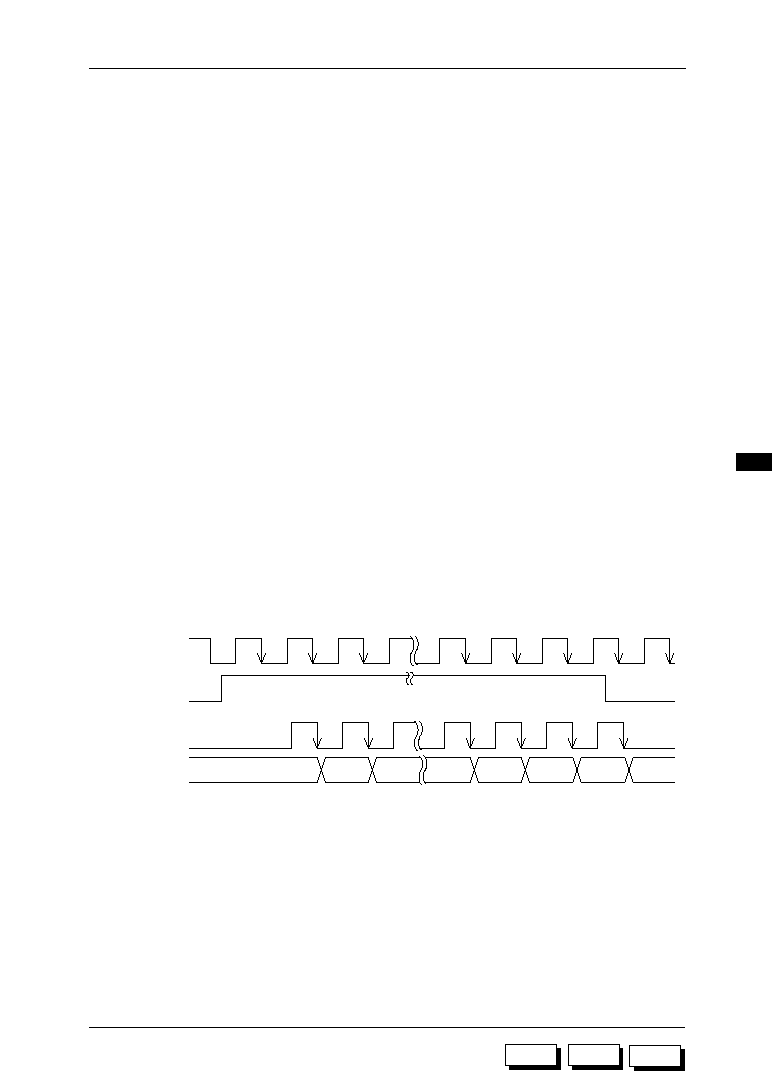

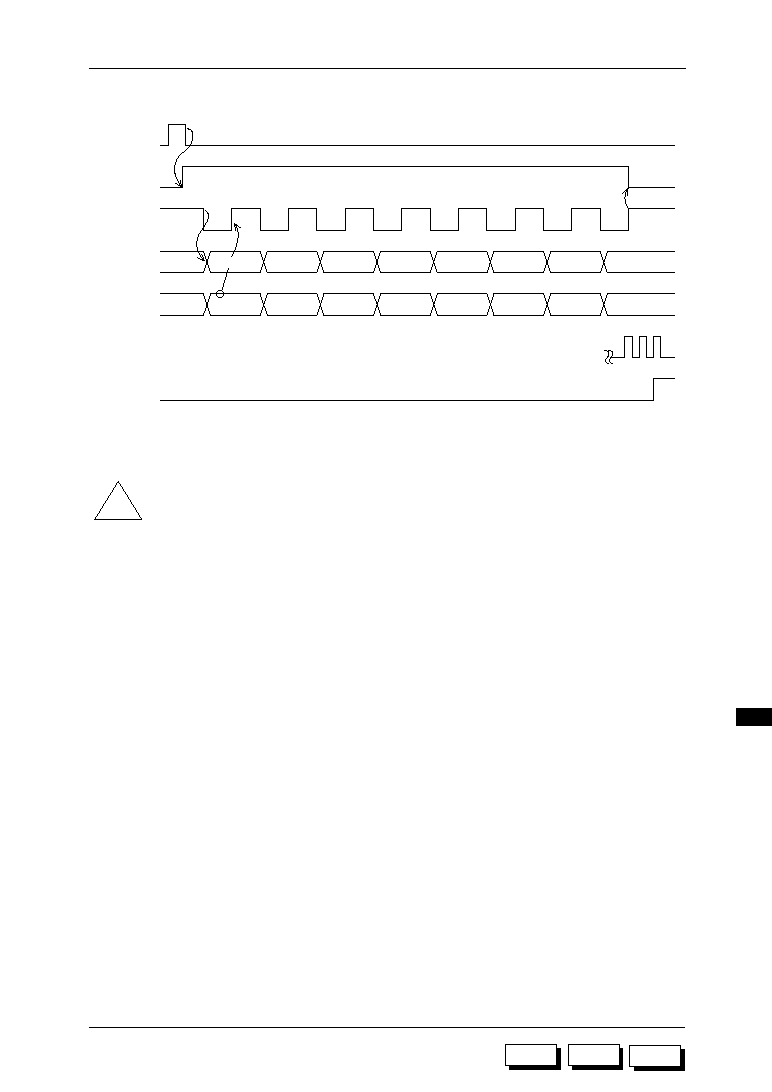

1.7 Basic Timing .................................................................................................. 1-29

1.7.1 Basic Timing of CPU Operation .......................................................... 1-29

1.7.2 Port I/O Basic Timing .......................................................................... 1-29

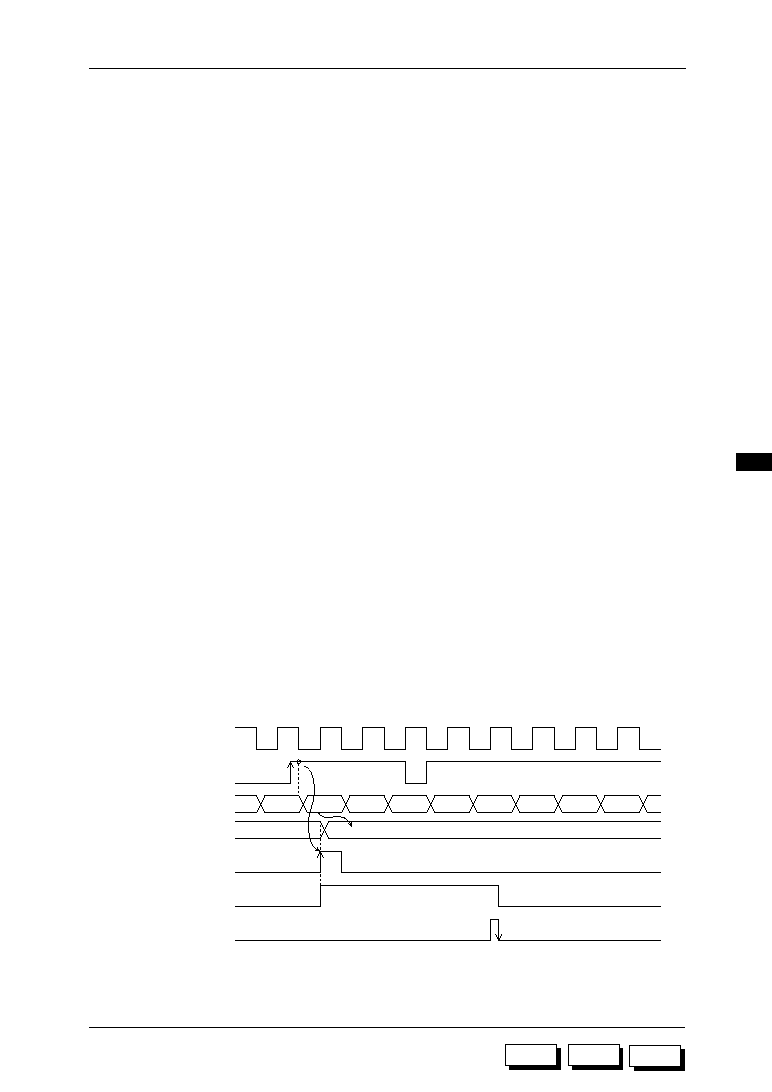

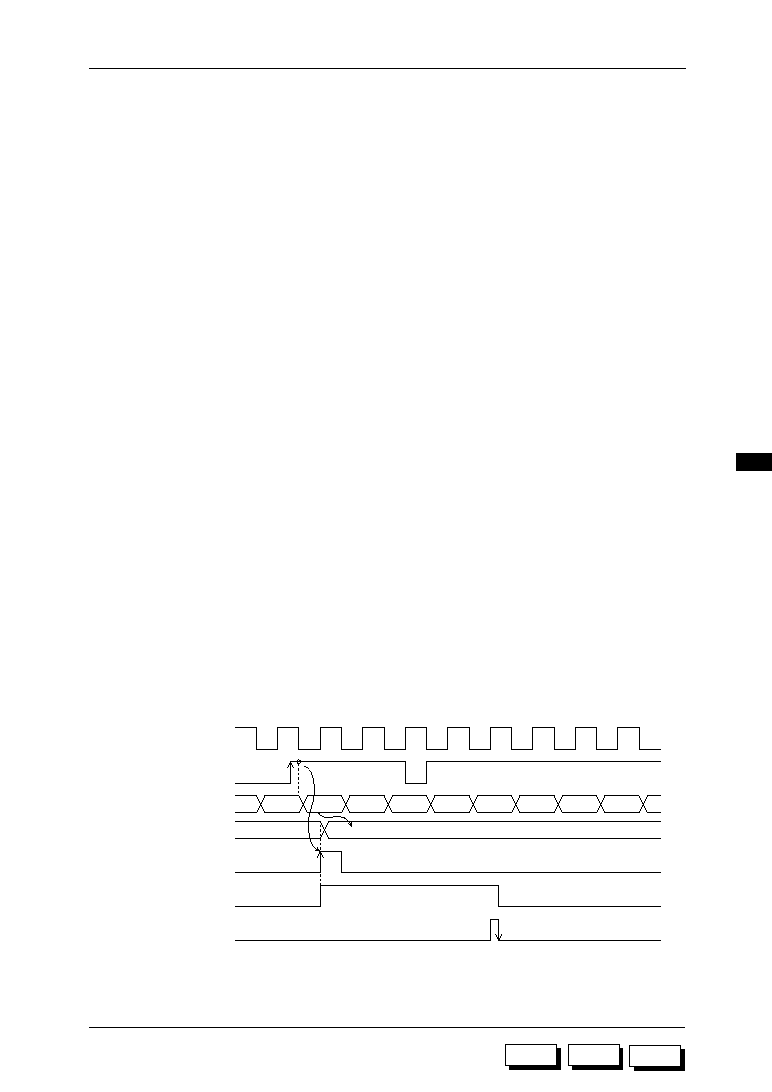

1.7.3 Interrupt Basic Timing ......................................................................... 1-31

Chapter 2 CPU and Memory Spaces

2.1 Overview ........................................................................................................ 2-1

2.2 Registers ........................................................................................................ 2-1

2.2.1 Accumulator (A) .................................................................................. 2-1

2.2.2 Flag Register ...................................................................................... 2-1

2.2.2.1 Carry Flag (C) ....................................................................... 2-1

2.2.2.2 Zero Flag (Z) ......................................................................... 2-2

2.2.2.3 G Flag (G) ............................................................................. 2-2

2.2.3 Master Interrupt Enable Flag (MIE) .................................................... 2-2

2.2.4 Current Bank Register (CBR), Extra Bank Register (EBR),

HL Register (HL), XY Register (XY) ................................................... 2-3

2.2.5 Program Counter (PC) ........................................................................ 2-4

2.2.6 RA Registers (RA3, RA2, RA1, RA0) ................................................. 2-4

2.2.7 Stack Pointer (SP) and Call Stack ...................................................... 2-5

2.2.8 Register Stack Pointer (RSP) and Register Stack .............................. 2-6

2.3 Memory Spaces ............................................................................................. 2-7

2.3.1 Program Memory Space ..................................................................... 2-7

2.3.2 Data Memory Space ........................................................................... 2-8

- ii -

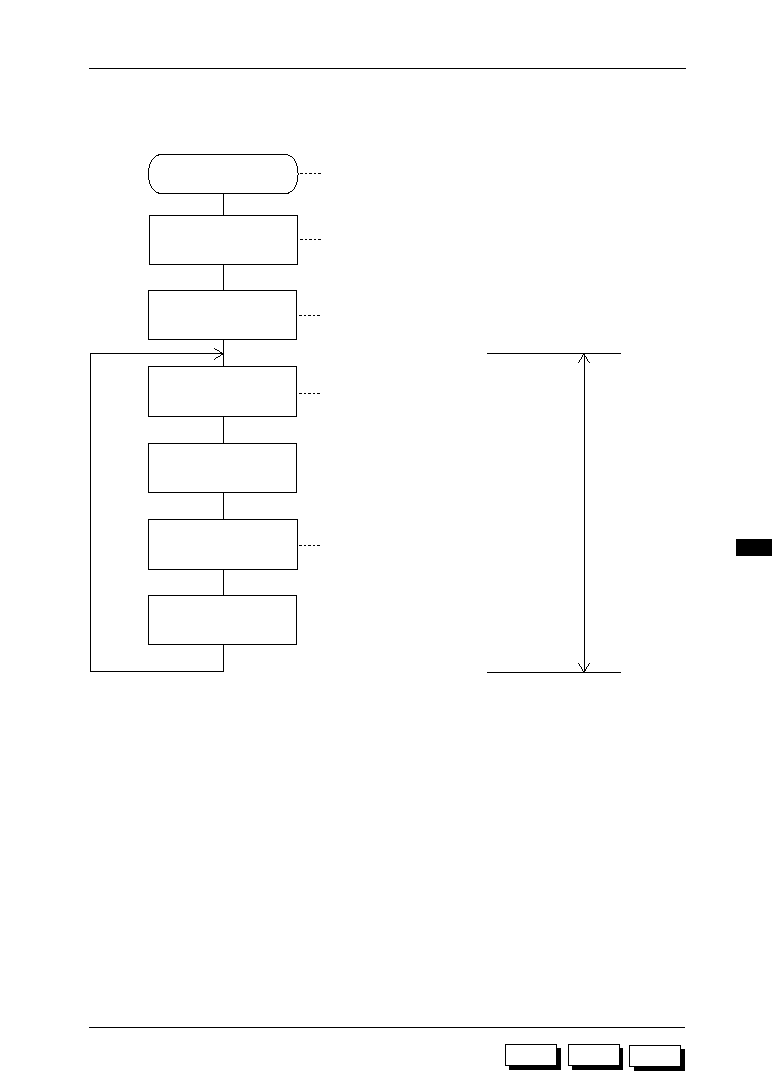

Chapter 3 CPU Control Functions

3.1 Overview ........................................................................................................ 3-1

3.2 System Reset Mode (RST) ............................................................................ 3-2

3.2.1 Transfer to and State of System Reset Mode .................................... 3-2

3.3 Halt Mode ....................................................................................................... 3-4

3.3.1 Transfer to and State of Halt Mode .................................................... 3-4

3.3.2 Halt Mode Release ............................................................................. 3-5

3.3.2.1 Release of Halt Mode by Interrupt ........................................ 3-5

3.3.2.2 Release of Halt Mode by RESET Pin ................................... 3-5

3.3.3 Melody Data Interrupt and Halt Mode Release .................................. 3-6

3.3.4 Note Concerning HALT Instruction ..................................................... 3-6

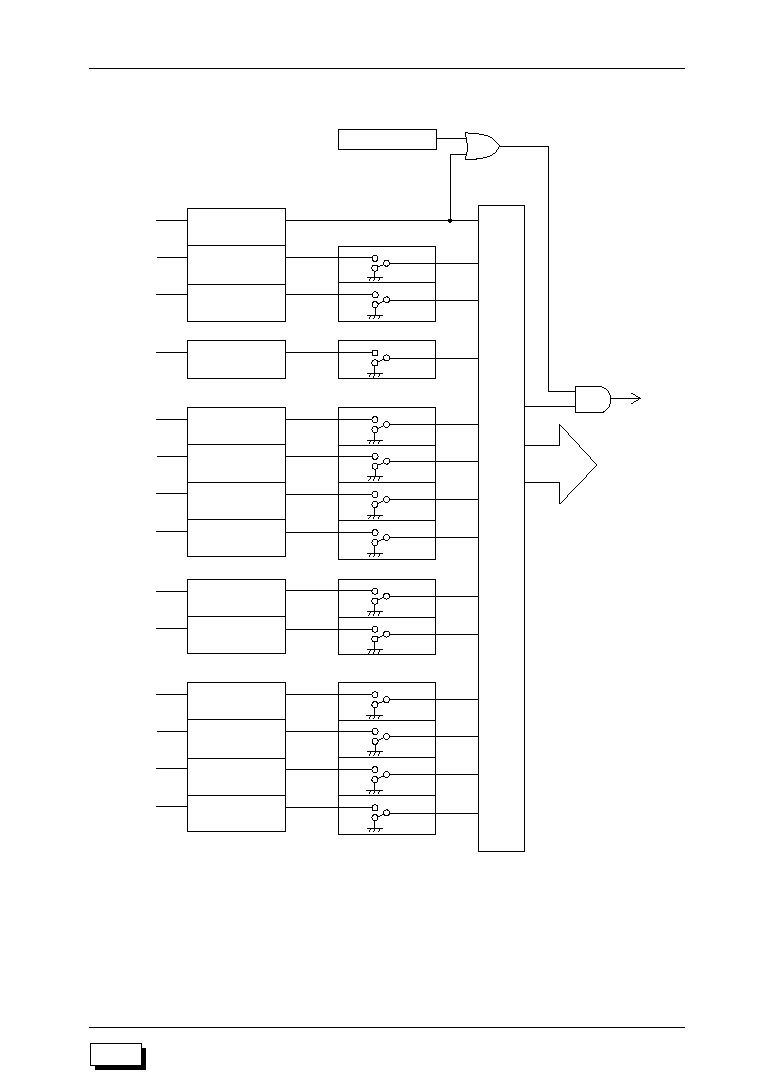

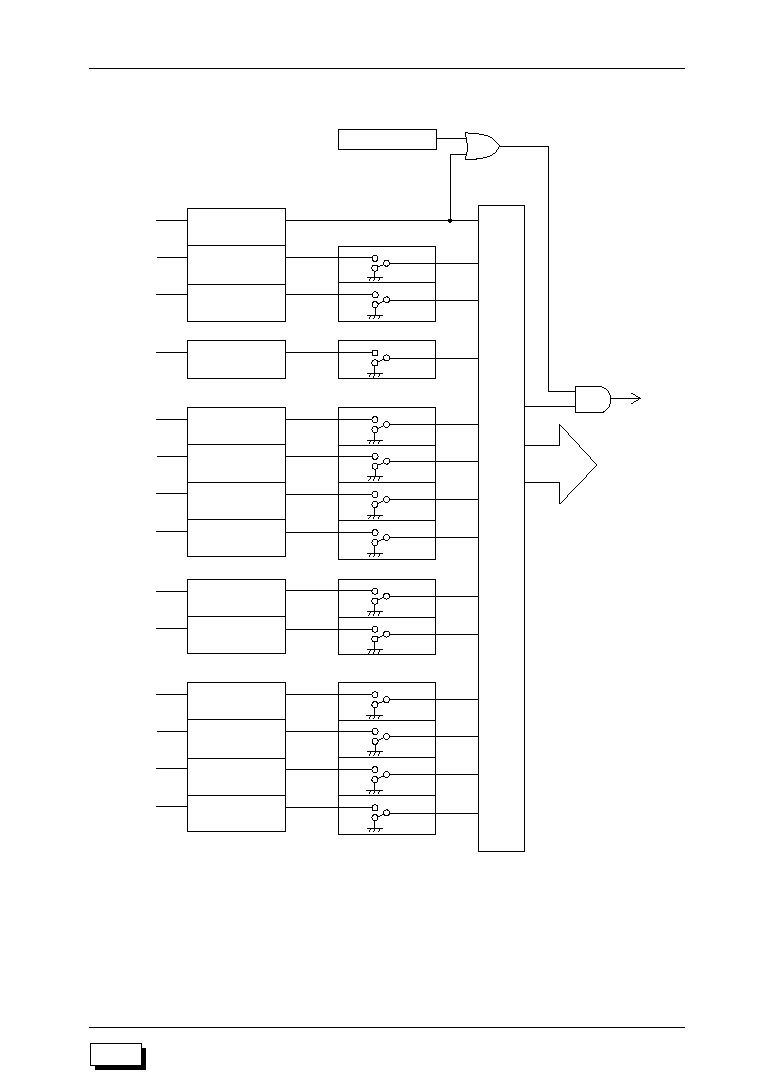

Chapter 4 ML63187 Interrupt (INT187)

4.1 Overview ........................................................................................................ 4-1

4.2 Interrupt Registers ......................................................................................... 4-3

4.3 Interrupt Sequence ........................................................................................ 4-9

4.3.1 Interrupt Processing ........................................................................... 4-9

4.3.2 Return from an Interrupt Routine ........................................................ 4-10

4.3.3 Interrupt Hold Instructions .................................................................. 4-10

Chapter 5 ML63189B Interrupt (INT189)

5.1 Overview ........................................................................................................ 5-1

5.2 Interrupt Registers ......................................................................................... 5-3

5.3 Interrupt Sequence ........................................................................................ 5-9

5.3.1 Interrupt Processing ........................................................................... 5-9

5.3.2 Return from an Interrupt Routine ........................................................ 5-10

5.3.3 Interrupt Hold Instructions .................................................................. 5-10

Chapter 6 ML63193 Interrupt (INT193)

6.1 Overview ........................................................................................................ 6-1

6.2 Interrupt Registers ......................................................................................... 6-3

6.3 Interrupt Sequence ........................................................................................ 6-11

6.3.1 Interrupt Processing ........................................................................... 6-11

6.3.2 Return from an Interrupt Routine ........................................................ 6-12

6.3.3 Interrupt Hold Instructions .................................................................. 6-12

Chapter 7 Clock Generator Circuit (OSC)

7.1 Overview ........................................................................................................ 7-1

7.2 Clock Generator Circuit Configuration ........................................................... 7-1

7.3 Low-Speed Clock Generator Circuit .............................................................. 7-2

7.4 High-Speed Clock Generator Circuit .............................................................. 7-4

7.5 System Clock Control .................................................................................... 7-6

7.6 Frequency Control Register (FCON) ............................................................. 7-7

7.7 System Clock Select Timing .......................................................................... 7-8

- iii -

Chapter 8 Time Base Counter (TBC)

8.1 Overview ........................................................................................................ 8-1

8.2 Time Base Counter Configuration.................................................................. 8-1

8.3 Time Base Counter Registers ........................................................................ 8-2

8.4 Time Base Counter Operation ....................................................................... 8-2

Chapter 9 Timers (TIMER)

9.1 Overview ........................................................................................................ 9-1

9.2 Timer Configuration ....................................................................................... 9-1

9.3 Timer Registers .............................................................................................. 9-3

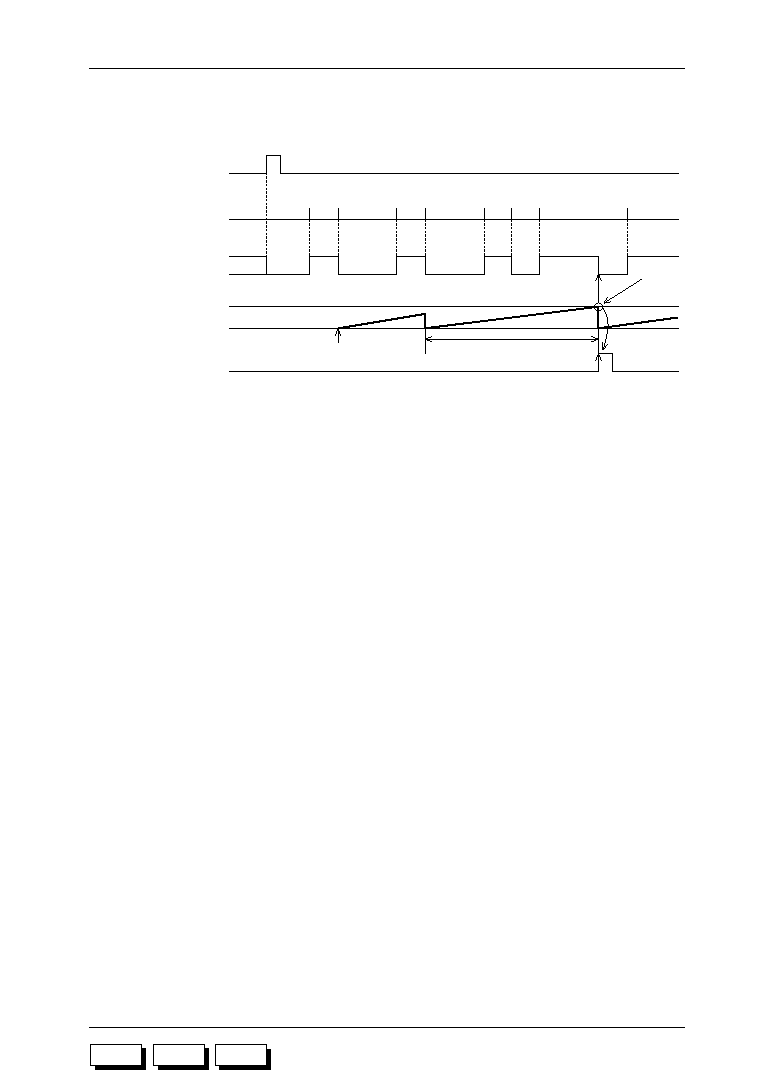

9.4 Timer Operation ............................................................................................. 9-14

9.4.1 Timer Clock ........................................................................................ 9-14

9.4.2 Timer Data Registers .......................................................................... 9-14

9.4.3 Timer Counter Registers .................................................................... 9-14

9.4.4 Timer Interrupt Requests and Overflow Flags .................................... 9-15

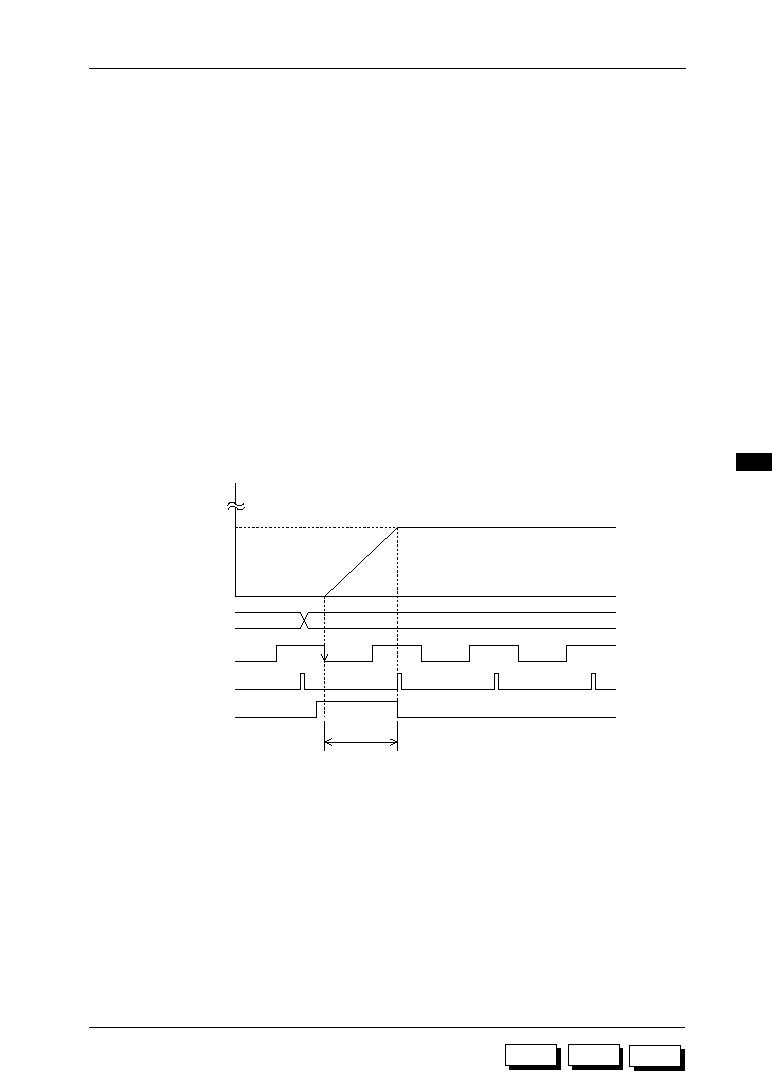

9.4.5 Auto-Reload Mode Operation ............................................................. 9-16

9.4.6 Capture Mode Operation .................................................................... 9-18

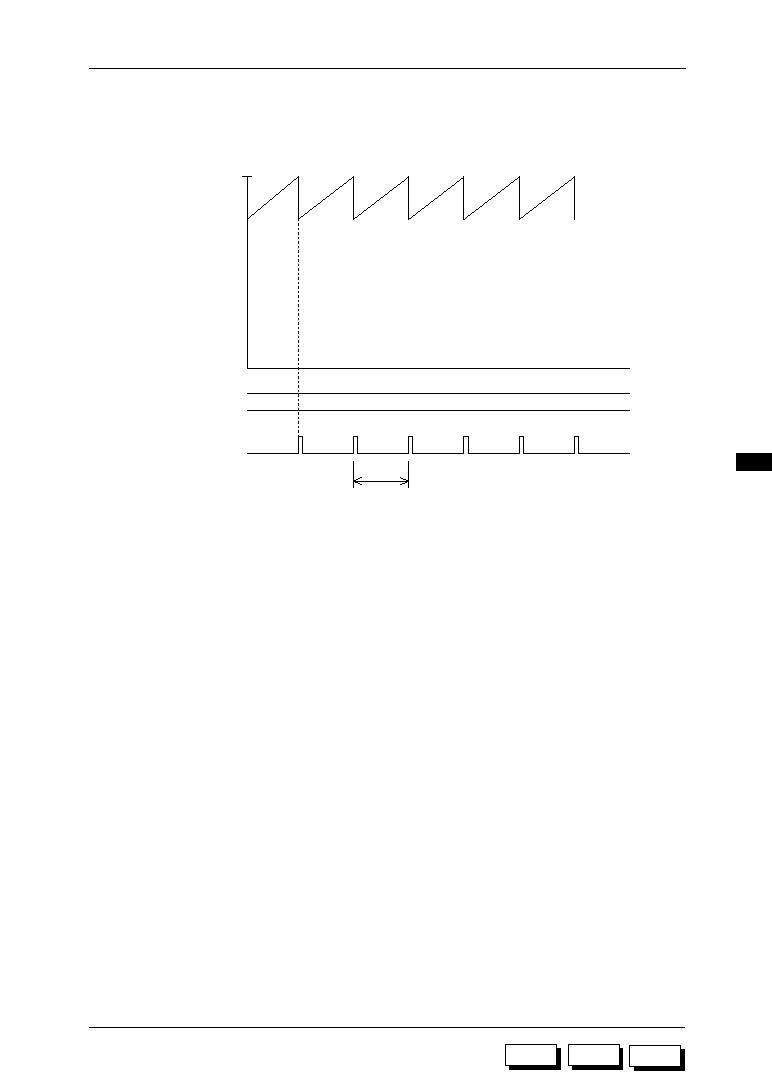

9.4.7 Frequency Measurement Mode Operation ......................................... 9-21

Chapter 10 100 Hz Timer Counter (100HzTC)

10.1 Overview ........................................................................................................ 10-1

10.2 100 Hz Timer Counter Configuration ............................................................. 10-1

10.3 100 Hz Timer Counter Registers ................................................................... 10-2

10.4 100 Hz Timer Counter Operation ................................................................... 10-3

Chapter 11 Watchdog Timer (WDT)

11.1 Overview ........................................................................................................ 11-1

11.2 Watchdog Timer Configuration ...................................................................... 11-1

11.3 Watchdog Timer Control Register (WDTCON) .............................................. 11-2

11.4 Watchdog Timer Operation ............................................................................ 11-2

- iv -

Chapter 12 Ports (INPUT, I/O PORT)

12.1 Overview ........................................................................................................ 12-1

12.2 Ports List ........................................................................................................ 12-1

12.3 Port 0 (P0.0≠P0.3) ......................................................................................... 12-2

12.3.1 Port 0 Configuration .......................................................................... 12-2

12.3.2 Port 0 Registers ................................................................................ 12-2

12.3.3 Port 0 External Interrupt Function (External Interrupt 5) ................... 12-5

12.4 Port 9, Port A (P9.0≠P9.3, PA.0≠PA.3) ......................................................... 12-7

12.4.1 Port 9, Port A Configuration .............................................................. 12-7

12.4.2 Port 9, Port A Registers .................................................................... 12-8

12.5 Port B (PB.0≠PB.3) ........................................................................................ 12-12

12.5.1 Port B Configuration ......................................................................... 12-12

12.5.2 Port B Registers ............................................................................... 12-13

12.5.3 Port B External Interrupt Function (External Interrupt 0) .................. 12-17

12.6 Port C (PC.0≠PC.3) ....................................................................................... 12-18

12.6.1 Port C Configuration ......................................................................... 12-18

12.6.2 Port C Registers ............................................................................... 12-19

12.6.3 Port C External Interrupt Function (External Interrupt 1) .................. 12-24

12.7 Port E (PE.0≠PE.3) ........................................................................................ 12-25

12.7.1 Port E Configuration ......................................................................... 12-25

12.7.2 Port E Registers ............................................................................... 12-26

12.7.3 Port E.3 External Interrupt Function (External Interrupt 2) ............... 12-29

Chapter 13 Melody Driver (MELODY)

13.1 Overview ........................................................................................................ 13-1

13.2 Melody Driver Configuration .......................................................................... 13-1

13.3 Melody Driver Registers ................................................................................. 13-2

13.4 Melody Circuit Operation ............................................................................... 13-4

13.4.1 Tempo Data ...................................................................................... 13-5

13.4.2 Melody Data ..................................................................................... 13-6

13.4.3 Melody Circuit Application Example ................................................. 13-9

13.5 Buzzer Circuit Operation ................................................................................ 13-10

Chapter 14 Serial Port (SIO)

14.1 Overview ........................................................................................................ 14-1

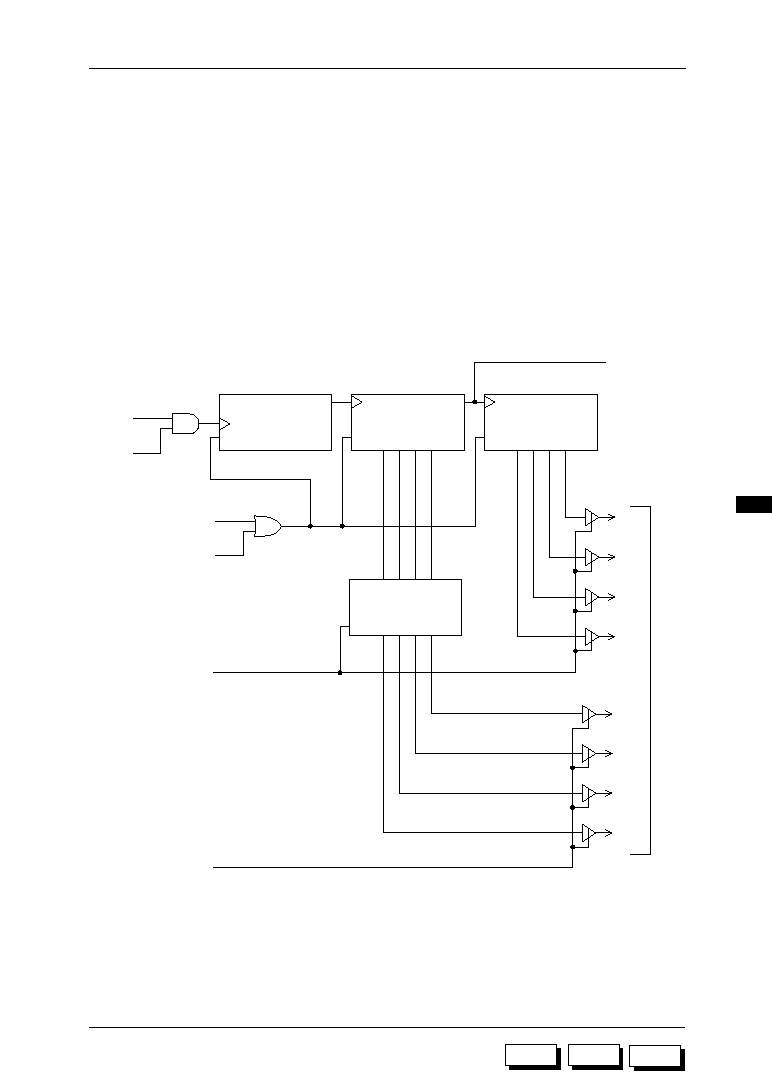

14.2 Serial Port Configuration ................................................................................ 14-1

14.3 Serial Port Registers ...................................................................................... 14-3

14.4 Serial Port Operation Description .................................................................. 14-12

14.4.1 Data Format ...................................................................................... 14-12

14.4.2 Send Operation Description ............................................................. 14-13

14.4.3 Receive Operation Description ......................................................... 14-19

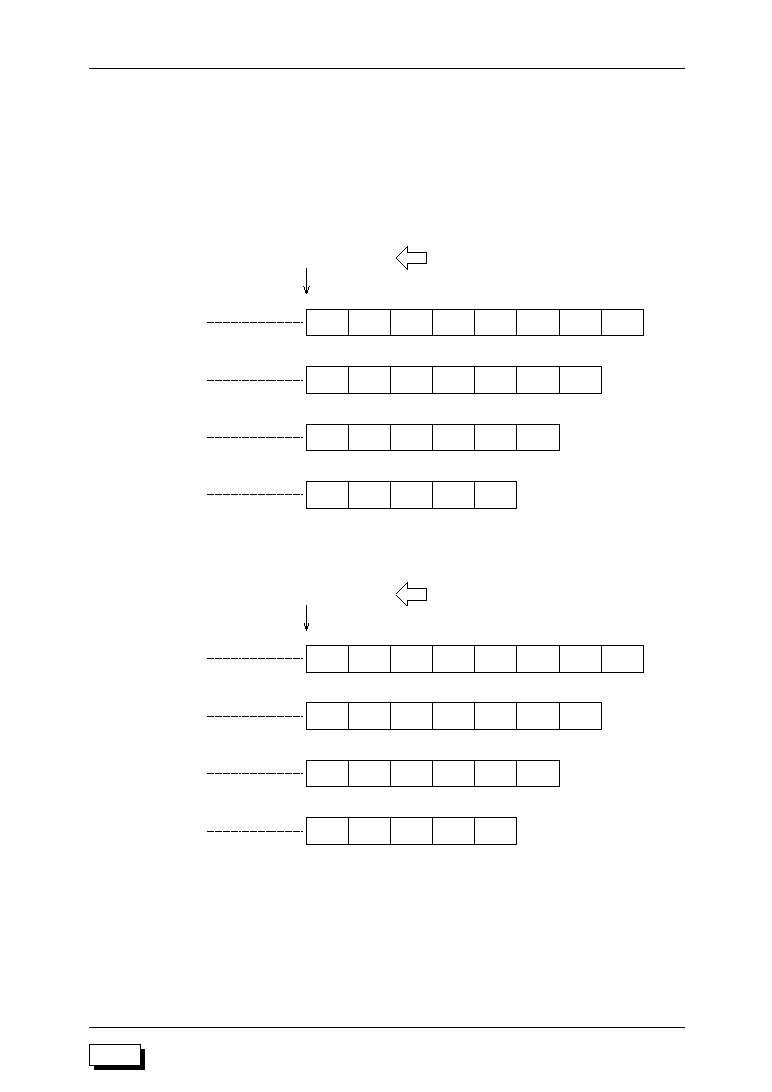

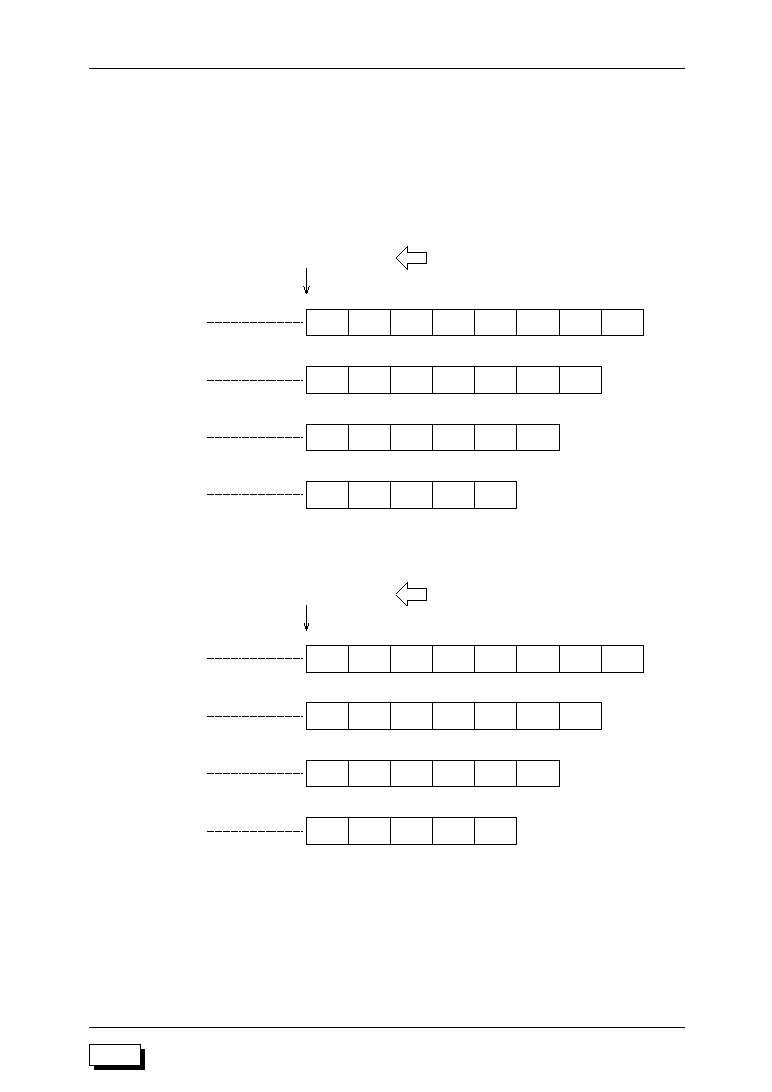

14.5 Send/Receive Data LSB/MSB First Select .................................................... 14-25

14.5.1 Selecting Send Data LSB/MSB First ................................................ 14-25

14.5.2 Selecting Receive Data LSB/MSB First ............................................ 14-26

- v -

Chapter 15 Shift Register (SFT)

15.1 Overview ........................................................................................................ 15-1

15.2 Shift Register Configuration ........................................................................... 15-1

15.3 Shift Registers ................................................................................................ 15-2

15.4 Shift Register Operation ................................................................................ 15-4

15.5 Shift Register Application Example ................................................................ 15-6

Chapter 16 LCD Driver (LCD)

16.1 Overview ........................................................................................................ 16-1

16.2 LCD Driver Configuration ............................................................................... 16-1

16.3 LCD Driver Registers ..................................................................................... 16-2

16.4 LCD Driver Operation .................................................................................... 16-5

16.5 Bias Generator (BIAS) ................................................................................... 16-6

16.6 LCD Driver Output Waveform ........................................................................ 16-9

Chapter 17 Multiplication/Division Circuit (MULDIV)

17.1 Overview ........................................................................................................ 17-1

17.2 Multiplication and Division Registers ............................................................. 17-2

17.2.1 Calculation Registers ......................................................................... 17-2

17.2.2 Multiplication/Division Condition Register ................................................ 17-4

17.3 Multiplication/Division Execution .................................................................... 17-5

Chapter 18 Battery Low Detect Circuit (BLD)

18.1 Overview ........................................................................................................ 18-1

18.2 Battery Low Detect Circuit Configuration ....................................................... 18-1

18.3 Judgment Voltage .......................................................................................... 18-2

18.4 Battery Low Detect Circuit Register ............................................................... 18-2

18.5 Battery Low Detect Circuit Operation............................................................. 18-3

Chapter 19 Backup Circuit (BACKUP)

19.1 Overview ........................................................................................................ 19-1

19.2 Power Supply Circuit Configuration ............................................................... 19-2

19.2.1 Power Supply Circuit Configuration When Backup Circuit is Used ....... 19-2

19.2.2 Power Supply Circuit Configuration When Backup Circuit is Not Used ... 19-3

19.3 Backup Circuit Register ................................................................................. 19-4

19.4 Power Supply Circuit Operation ..................................................................... 19-5

Appendixes

Appendix A

List of Special Function Registers ............................................ Appendix-1

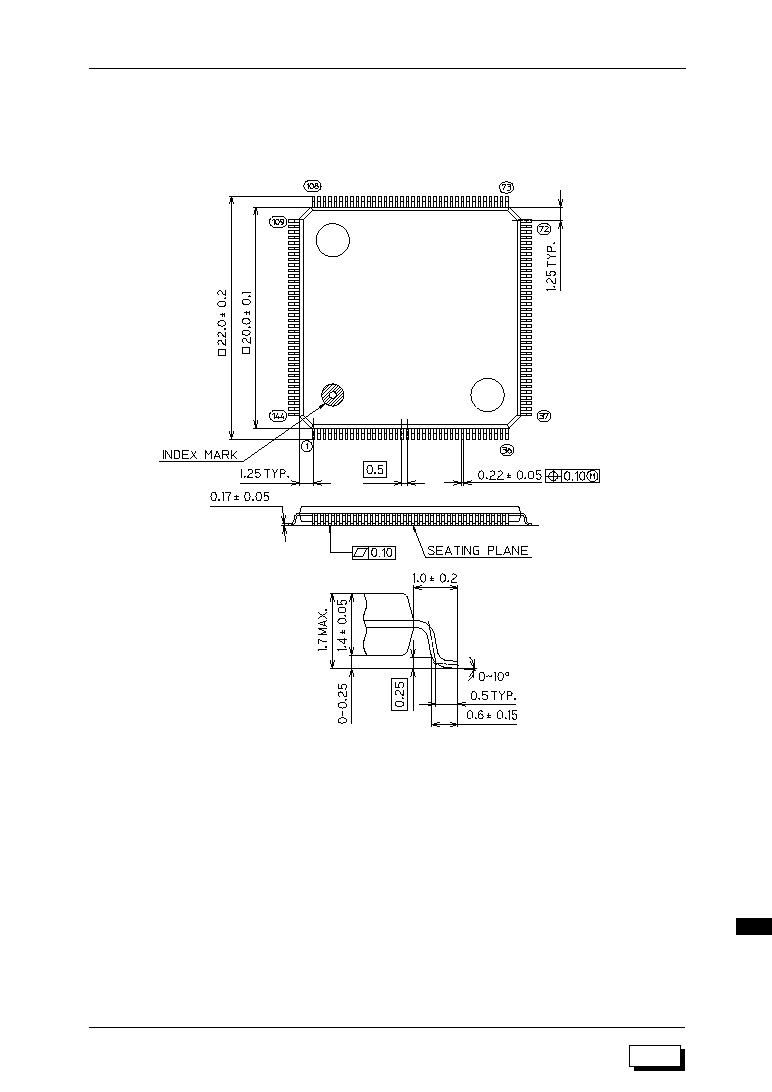

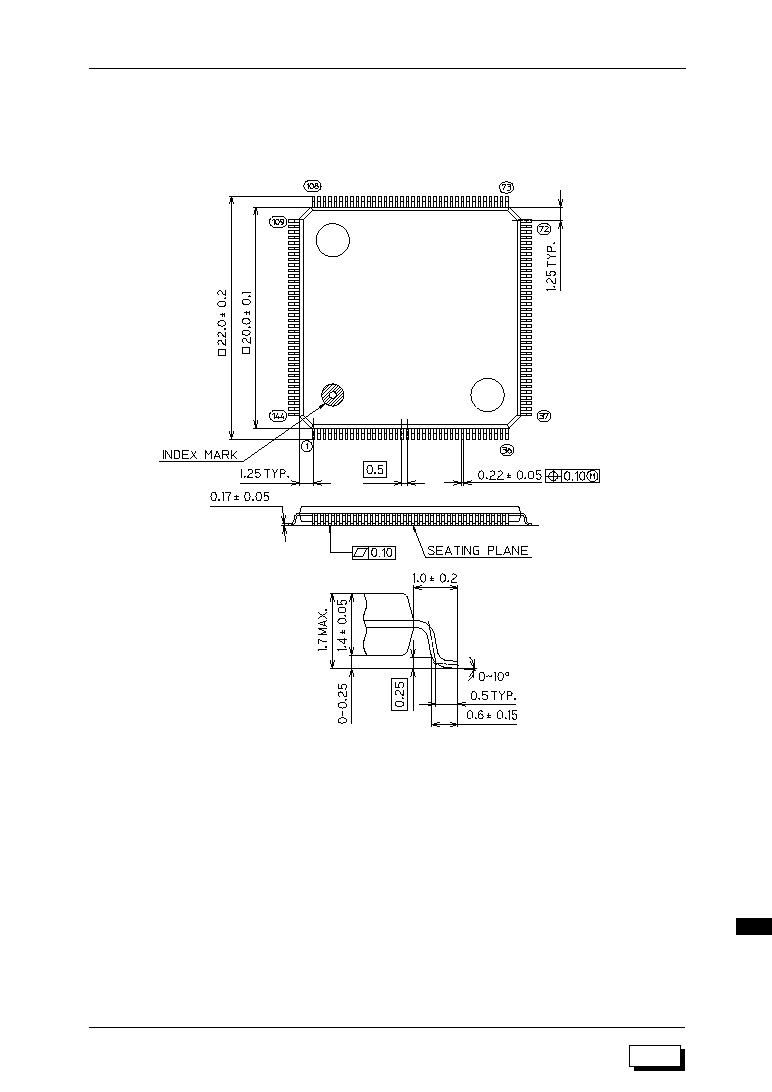

Appendix B

Package Dimensions ................................................................ Appendix-12

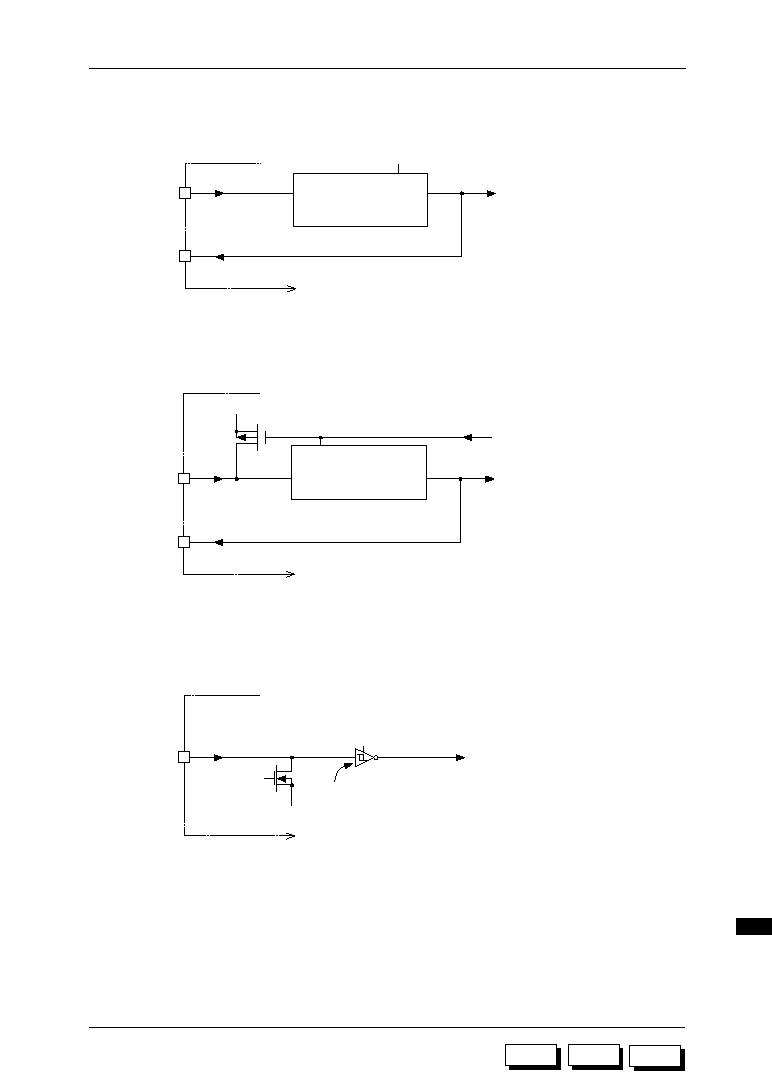

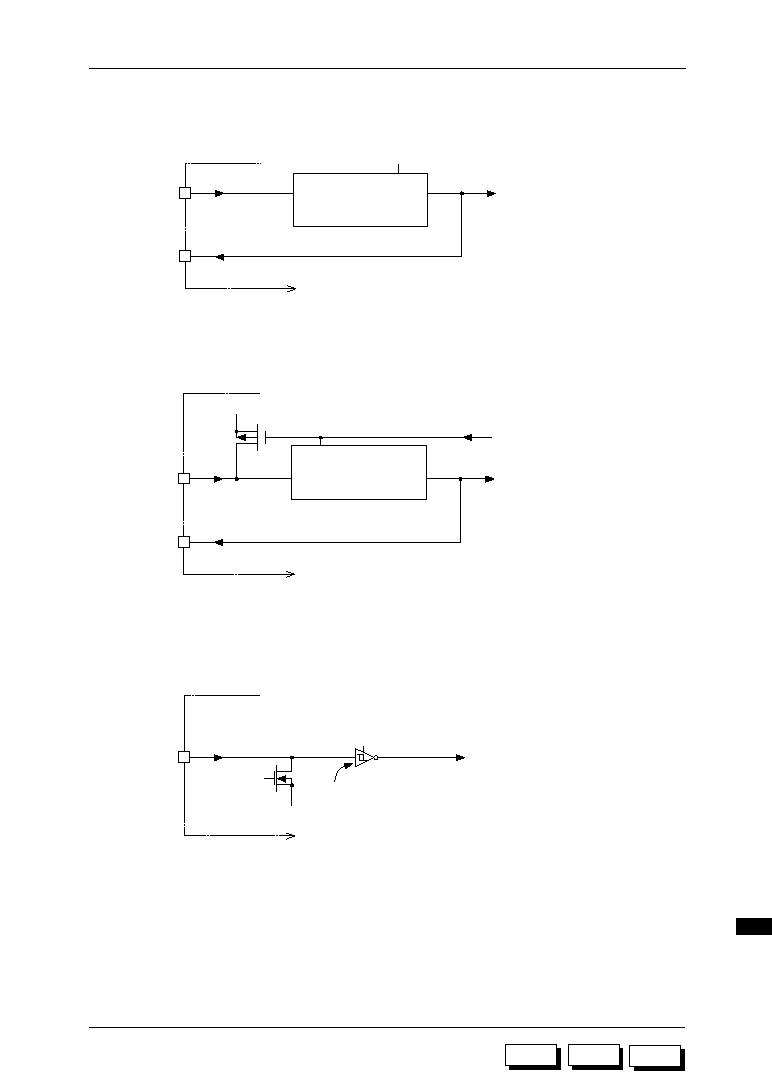

Appendix C

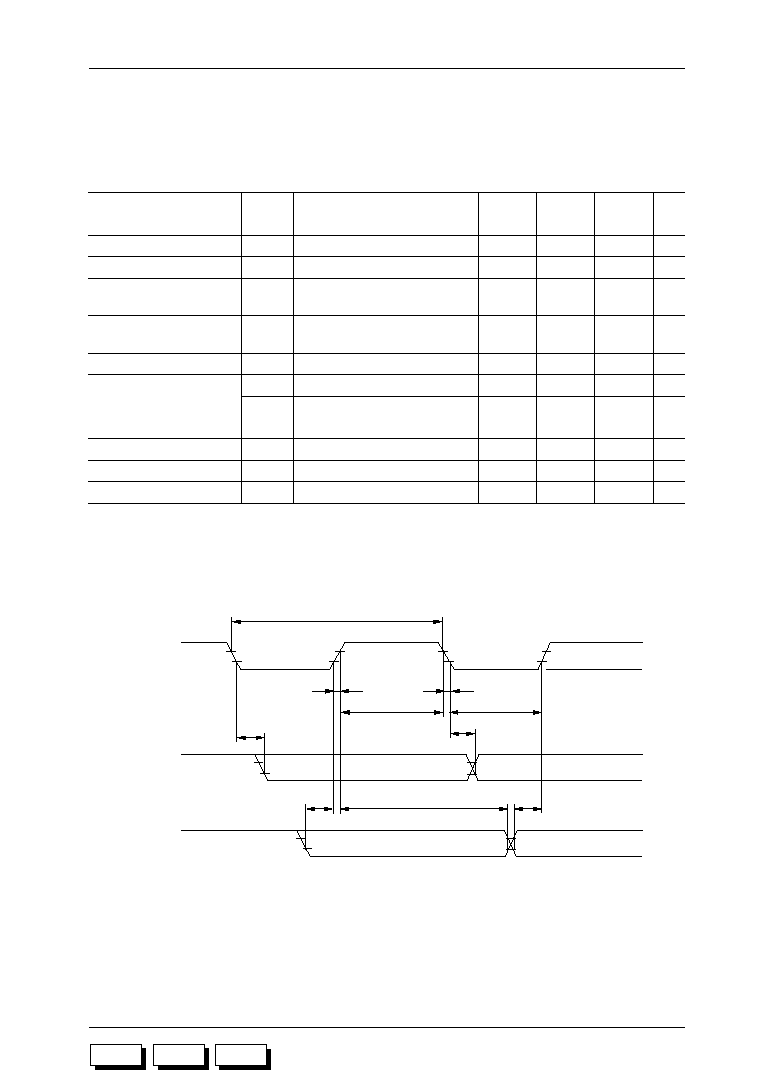

Input/Output Circuit Configuration ............................................ Appendix-14

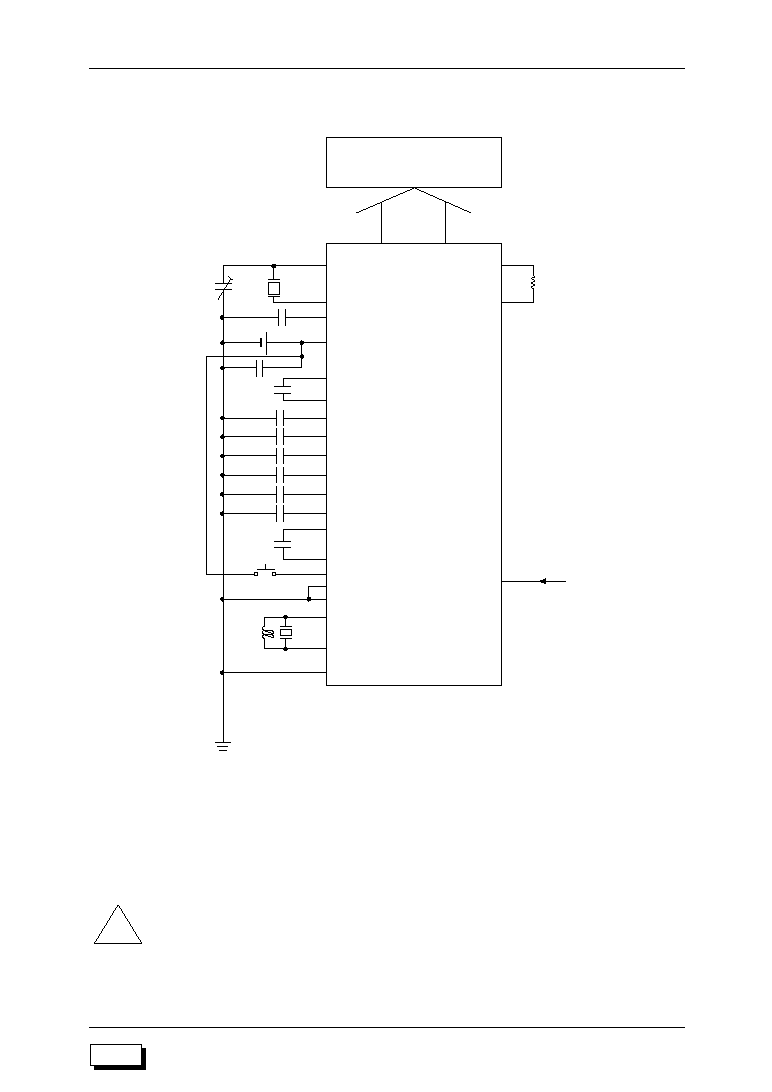

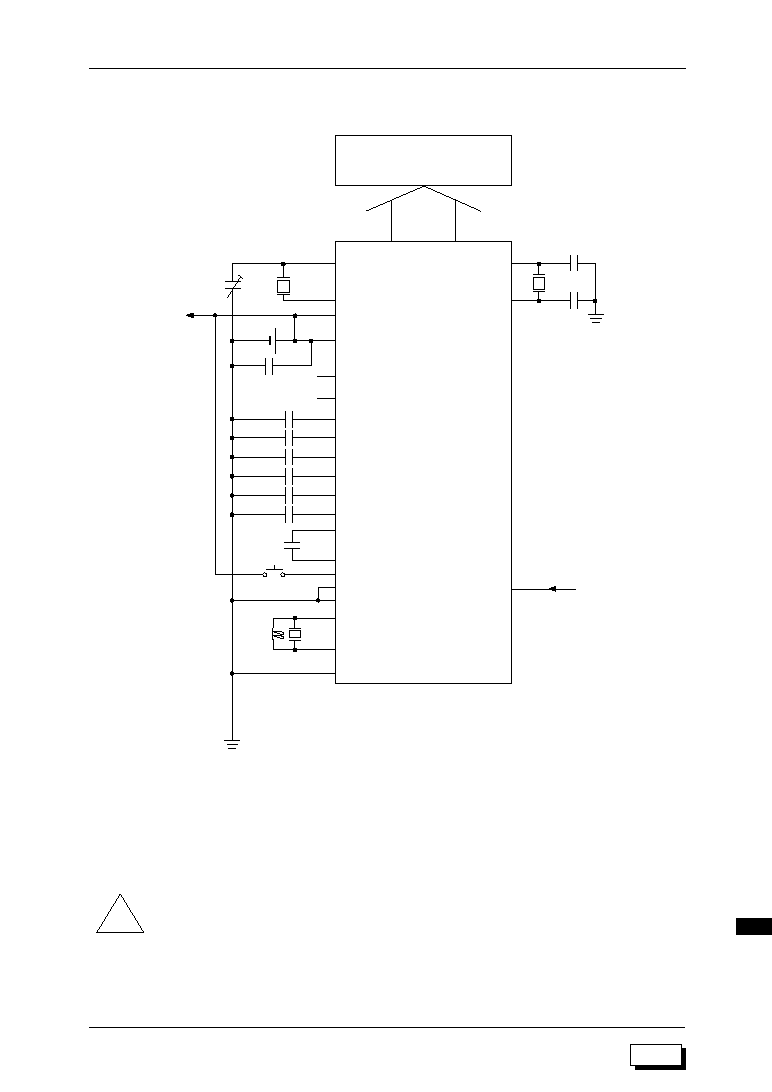

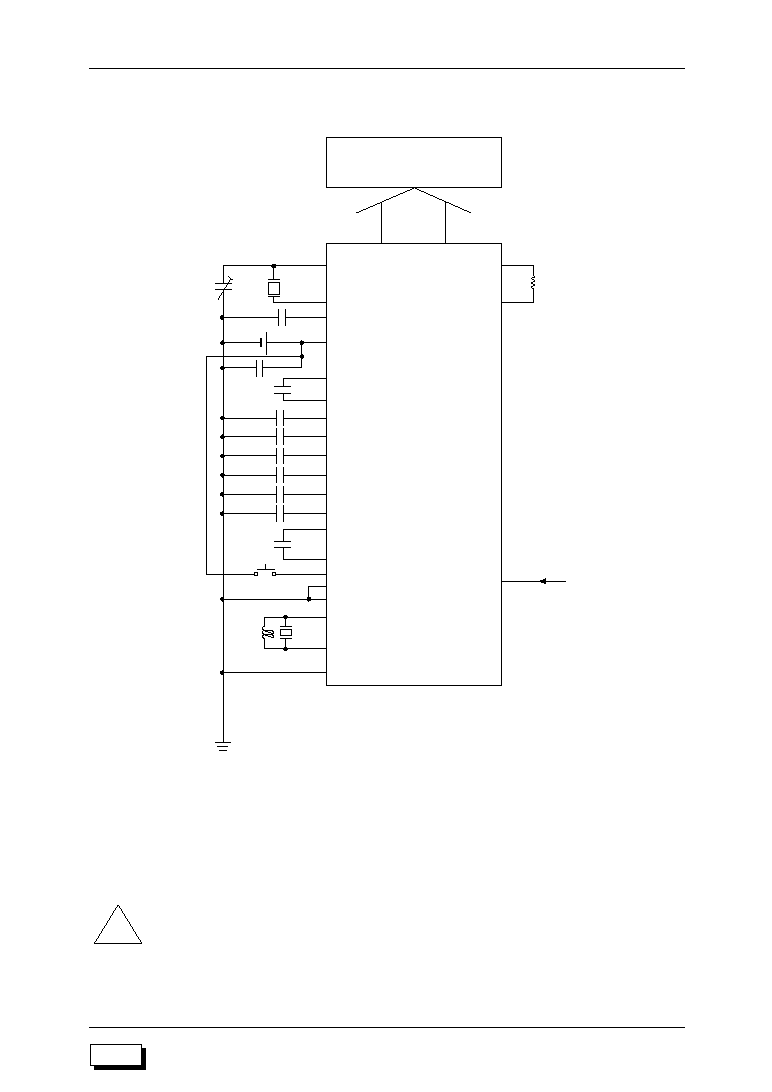

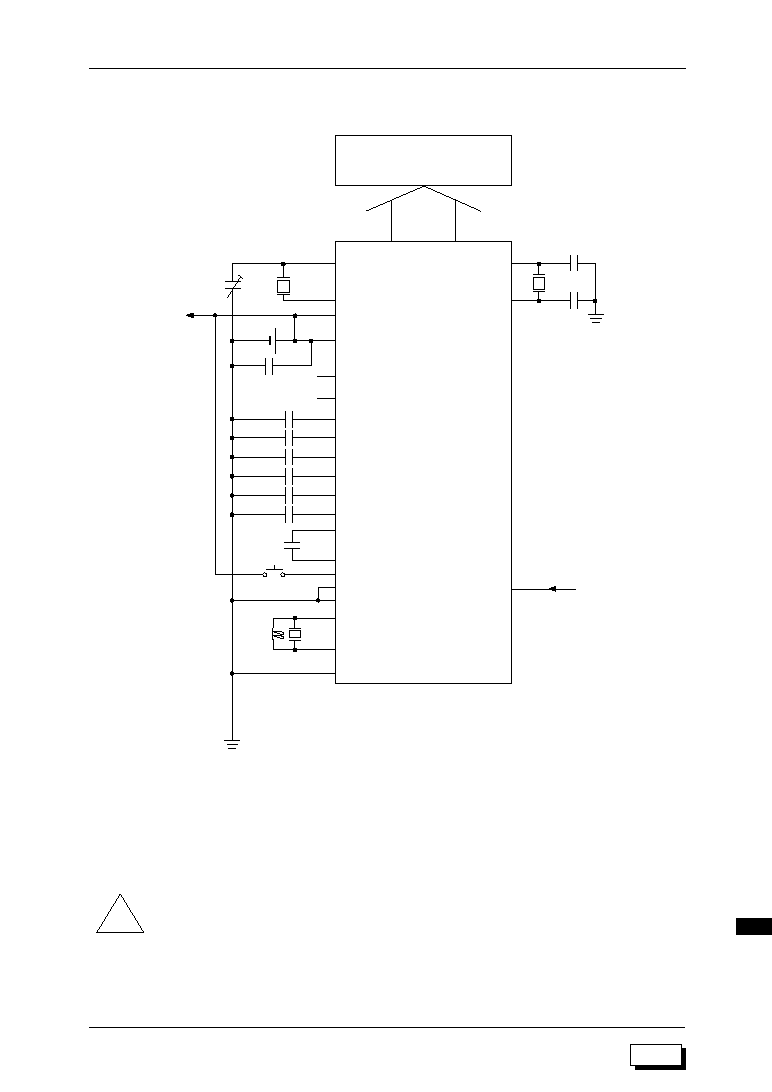

Appendix D

Peripheral Circuit Examples ..................................................... Appendix-16

Appendix E

Electrical Characteristics ......................................................... Appendix-19

Appendix F

Instruction List .......................................................................... Appendix-35

Appendix G

Mask Option ............................................................................. Appendix-57

- vi -

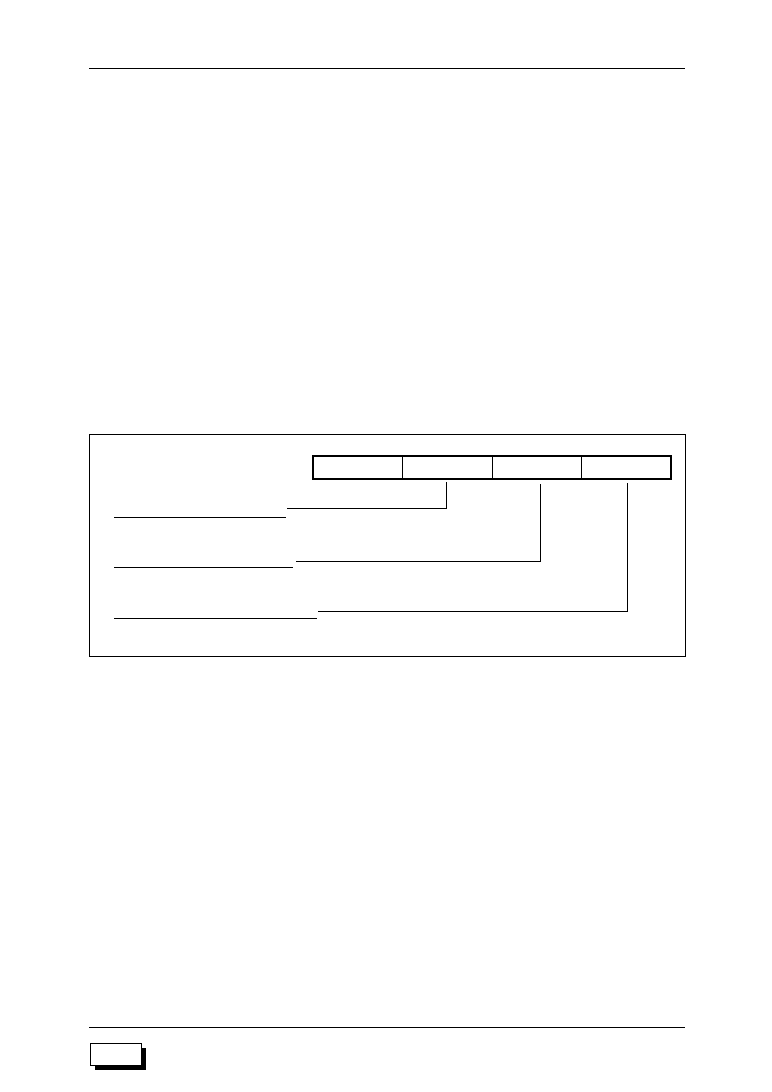

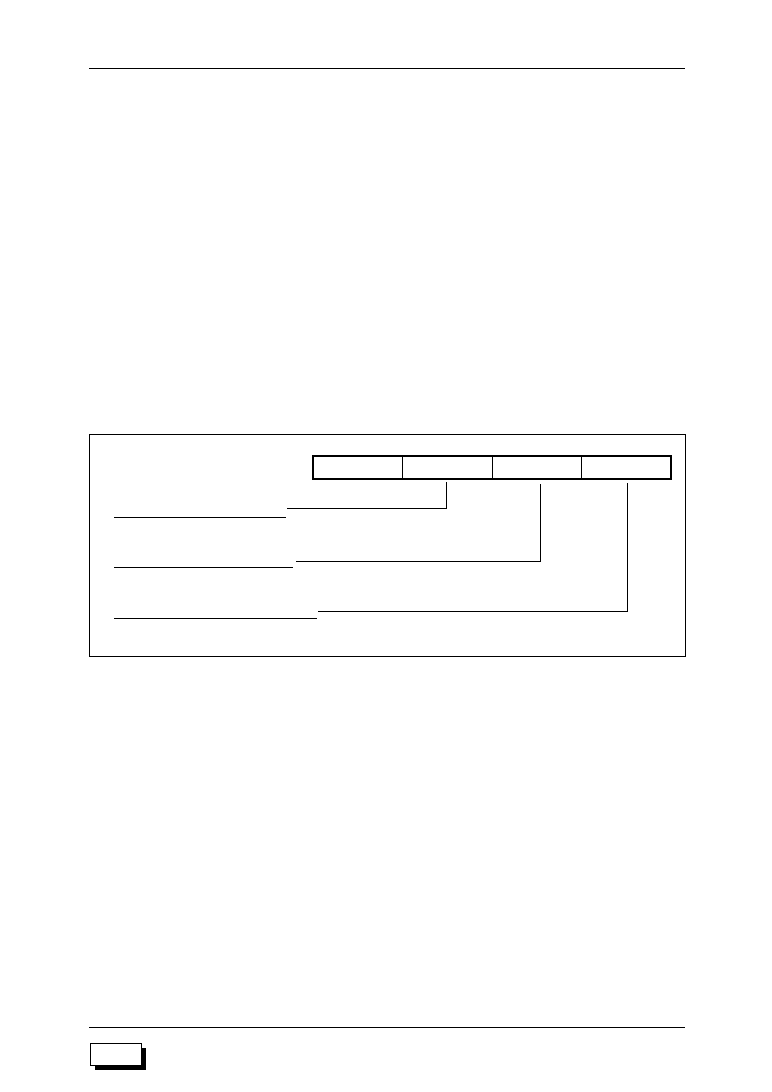

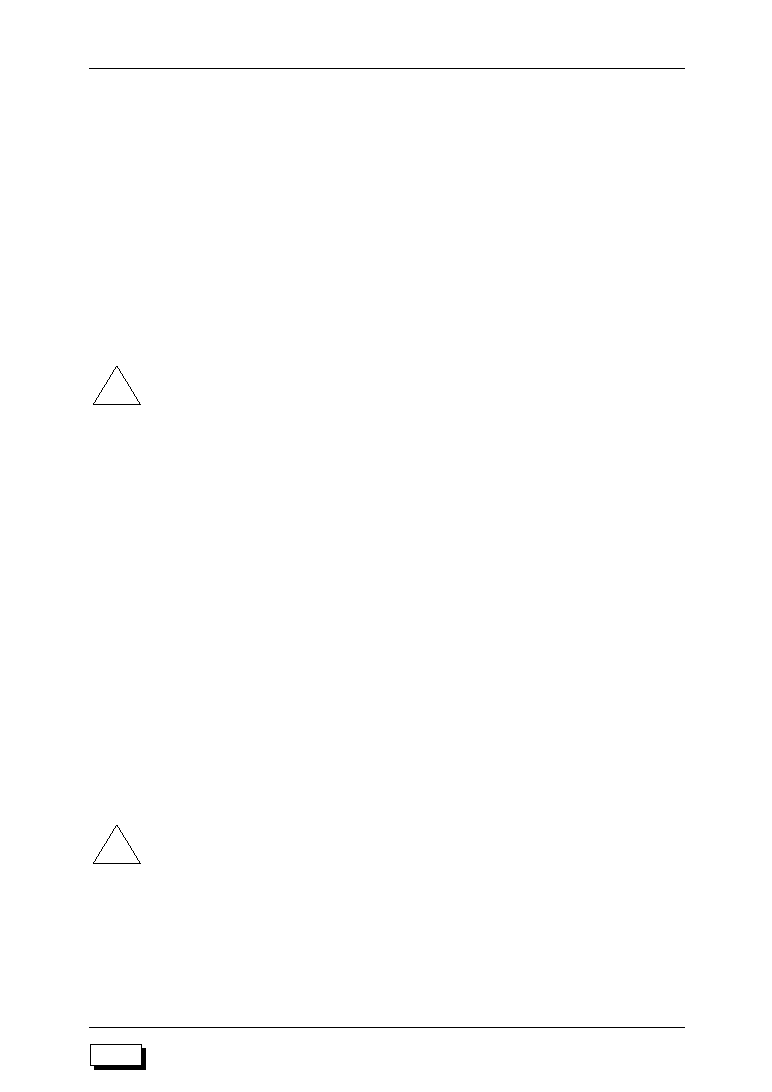

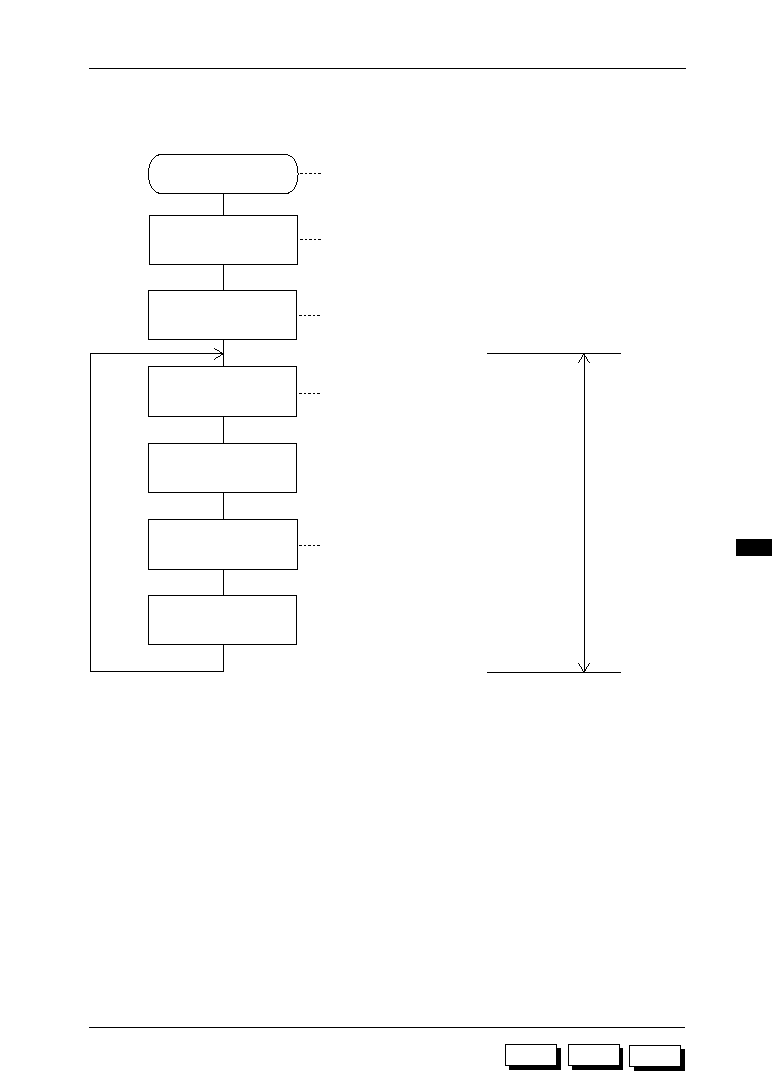

1

Chapter 1

Overview

2

Chapter 2

CPU and Memory Spaces

3

Chapter 3

CPU Control Functions

4

Chapter 4

ML63187 Interrupt (INT187)

5

Chapter 5

ML63189B Interrupt (INT189)

7

Chapter 7

Clock Generator Circuit (OSC)

8

Chapter 8

Time Base Counter (TBC)

9

Chapter 9

Timers (TIMER)

10

Chapter 10

100 Hz Timer Counter (100HzTC)

11

Chapter 11

Watchdog Timer (WDT)

16

Chapter 16

LCD Driver (LCD)

18

Chapter 18

Battery Low Detect Circuit (BLD)

19

Chapter 19

Backup Circuit (BACKUP)

Appendixes

12

Chapter 12

Ports (INPUT, I/O PORT)

13

Chapter 13

Melody Driver (MELODY)

15

Chapter 15

Shift Register (SFT)

6

Chapter 6

ML63193 Interrupt (INT193)

14

Chapter 14

Serial Port (SIO)

17

Chapter 17

Multiplication/Division Circuit (MULDIV)

M189B

M187

M193

Chapter 1

Overview

1

1-1

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

Chapter 1 Overview

1.1 Overview

The ML63187, ML63189B, and ML63193 are CMOS 4-bit microcontrollers that guarantee

operation at 0.9 V.

With an internal dot matrix LCD driver, these devices are well suited for applications having

liquid-crystal display (LCD) such as games, toys, watches, etc.

The ML63187, ML63189B, and ML63193 are masked-ROM devices belonging to the

M6318x series of the OLMS-63K family with an internal Oki's original CPU core nX-4/250.

Compared to other products of the M6318x series (MSM63184A), the ML63187 and

ML63189B have slimmer functions, more memory capacity and a greater number of LCD

drivers. Also, the reference voltage value of the battery low detect circuit has been optimized,

and to accommodate requirements for low power consumption, supply current has decreased

compared to other devices in the same series.

The ML63193 is a higher-end model over the ML63187 and ML63189B, featuring enlarged

memory capacity and additional I/O ports. It also has the multiplication/division circuit and

a serial port.

1.2 Features

The ML63187, ML63189B, and ML63193 have the following features.

a. Extensive instruction set

∑

408 instructions

Transfer, rotate, increment/decrement, arithmetic operations, compare, logic

operations, mask operations, bit operations, ROM table reference, stack

operations, flag operations, jump, conditional branch, call/return, control

b. Wide variety of addressing modes

∑

Indirect addressing mode for 4 types of data memory with current bank register,

extra bank register, HL register and XY register

∑

Data memory bank internal direct addressing mode

c. Processing speed

∑

2 clocks per machine cycle, with most instructions executed in 1 machine cycle

∑

Minimum instruction execution time:

61

m

s (@ 32.768 kHz system clock)

1

m

s (@ 2 MHz system clock)

d. Clock generation circuit

∑

Low-speed clock:

Crystal oscillation or RC oscillation selected with mask option (30 kHz to 80 kHz)

∑

High-speed clock:

Ceramic oscillation or RC oscillation selected with software (2 MHz max.)

e. Program memory space

∑

ML63187:

16K words

∑

ML63189B:

32K words

∑

ML63193:

64K words

∑

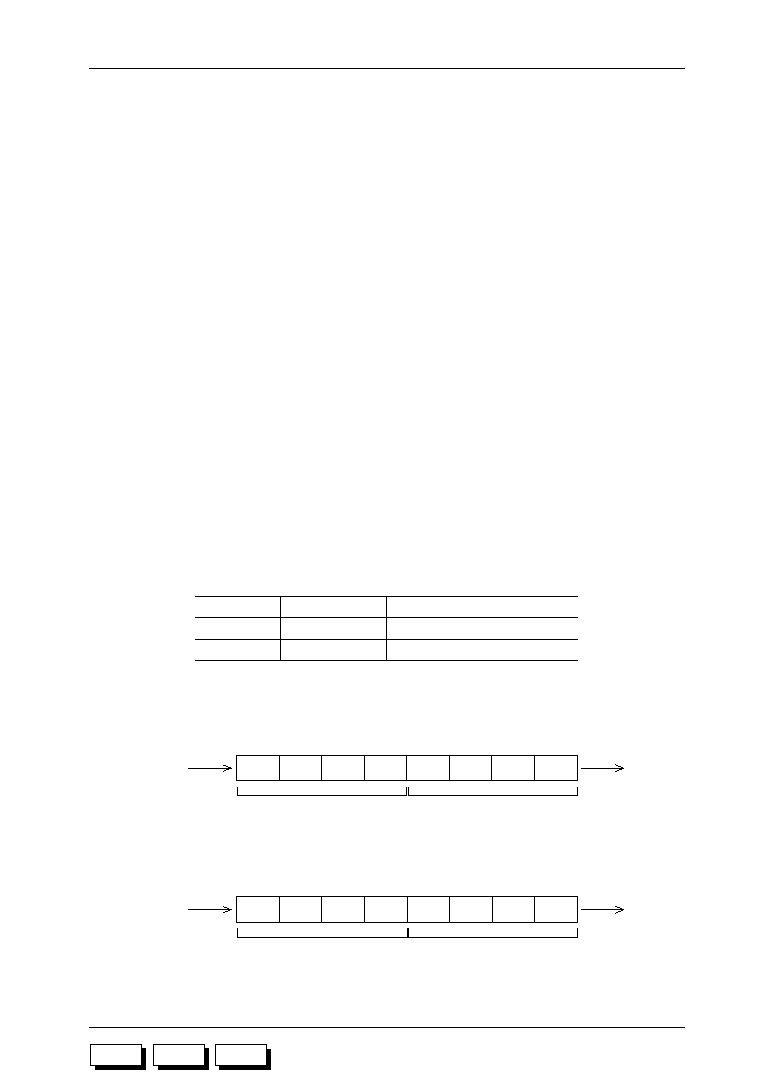

The basic instruction length is 16 bits per word.

1-2

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

f. Data memory space

∑

ML63187:

1024 nibbles

∑

ML63189B: 1536 nibbles

∑

ML63193:

2048 nibbles

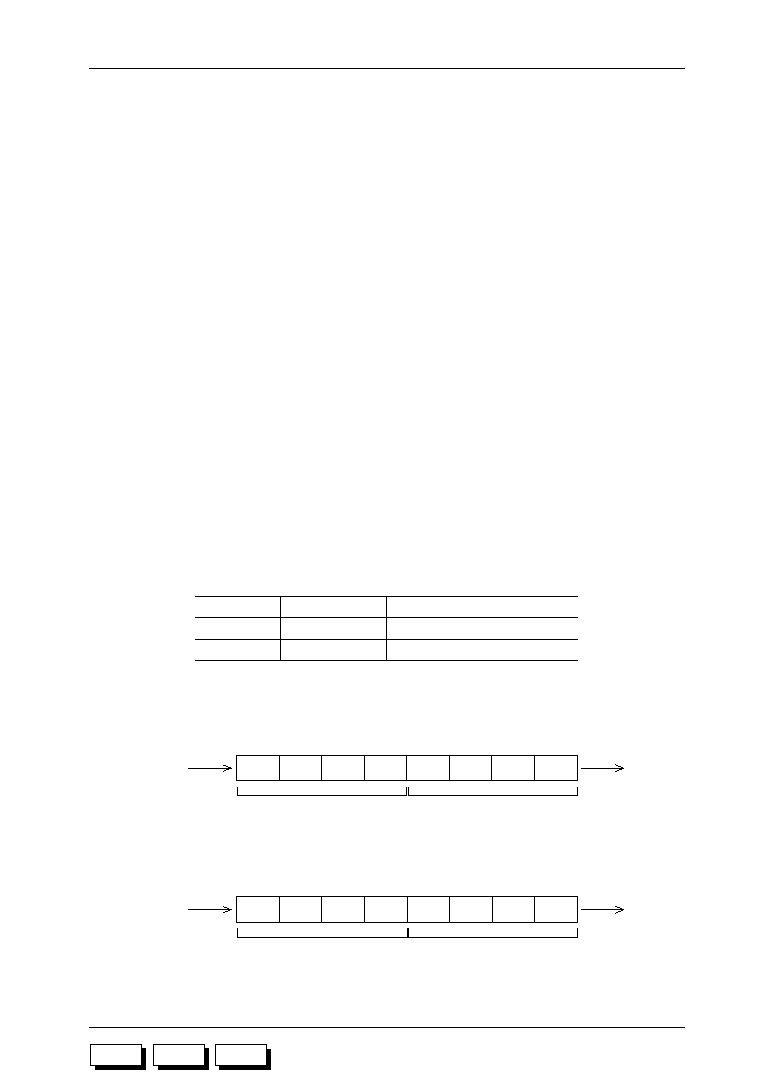

g. Stack level

Call stack level

Register stack level

ML63187

16

16

ML63189B

16

16

ML63193

16

16

h. Ports

∑

Input ports:

Selectable as input with pull-up resistor, input with pull-down resistor or high

impedance input.

∑

I/O ports:

Selectable as input with pull-up resistor, input with pull-down resistor or high

impedance input.

Selectable as p-channel open drain output, n-channel open drain output, high

impedance output or CMOS output.

∑

Can be interfaced to external devices having different power supplies.

V

DDI

is the power supply pin for ports.

∑

Number of ports:

Input ports

I/O ports

ML63187

--

2 ports

•

4 bits

ML63189B

1 port

•

4 bits

4 ports

•

4 bits

ML63193

1 port

•

4 bits

5 ports

•

4 bits

i. Melody output

∑

Melody frequency:

529 Hz to 2979 Hz

∑

Tone length:

63 varieties

∑

Tempo:

15 varieties

∑

Melody data:

Stored in program memory

∑

Buzzer driver signal output: 4 kHz

j. LCD driver

∑

Number of segments:

1024 segments max. (64 seg.

•

16 com.)

∑

1/1 to 1/16 duty

∑

1/4 or 1/5 bias (internal regulator)

∑

Selectable as all-ON mode, all-OFF mode, power down mode, and normal

display mode

∑

Adjustable contrast

k. Multiplication/division circuit

∑

Multiplication: (8-bit)

◊

(8-bit) = product (16-bit)

∑

Division: (16-bit)

˜

(8-bit) = quotient (16-bit), remainder (8-bit)

l. System reset function

∑

System reset by RESET pin (Built-in 2 kHz RESET sampling circuit can be

selected by mask option)

∑

System reset by power-on detection (When not using 2 kHz RESET sampling

circuit)

∑

System reset by detection that low-speed clock has stopped oscillation

1-3

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

n. Power supply backup

∑

Turning on the backup circuit (multiplied voltage circuit) enables operation at the

low voltage of 0.9 V.

o. Timers, counters

∑

8-bit timer:

4 channels

Selectable as auto-reload mode, capture mode,

clock frequency measurement mode

∑

Watchdog timer:

1 channel

∑

100 Hz timer:

1 channel

1/100 sec. measurement possible

∑

15-bit TBC:

1 channel

1 Hz, 2 Hz, 4 Hz, 8 Hz, 16 Hz, 32 Hz, 64 Hz,128 Hz signals

can be read

p. Serial port (ML63193 only)

∑

Mode: UART mode, synchronous mode

∑

Communication speed in UART mode: 1200 bps, 2400 bps, 4800 bps, 9600 bps

∑

Clock frequency in synchronous mode: 32.768 kHz (internal clock mode);

external clock frequency

∑

Data length: 5 to 8 bits

q. Shift register

∑

Shift clock:

System clock

•

1 or

•

1/2, external clock

∑

Data length:

8 bits

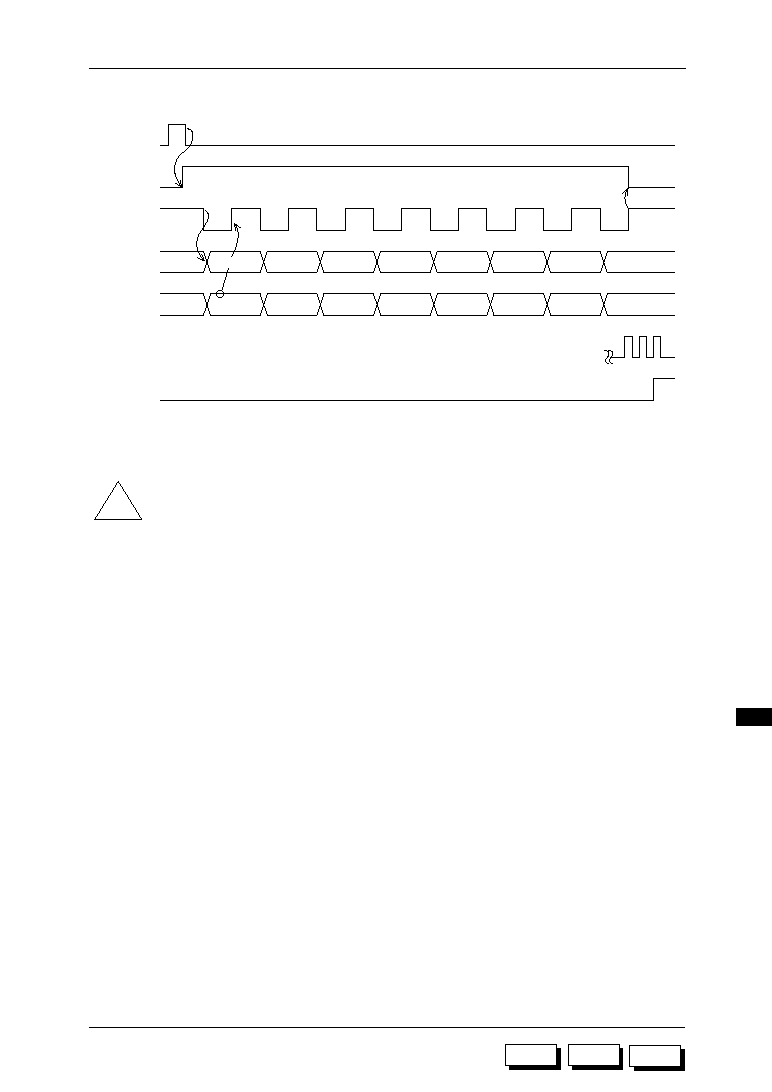

r. Interrupt factors

External factors

Internal factors

ML63187

2

12

ML63189B

3

12

ML63193

4

14

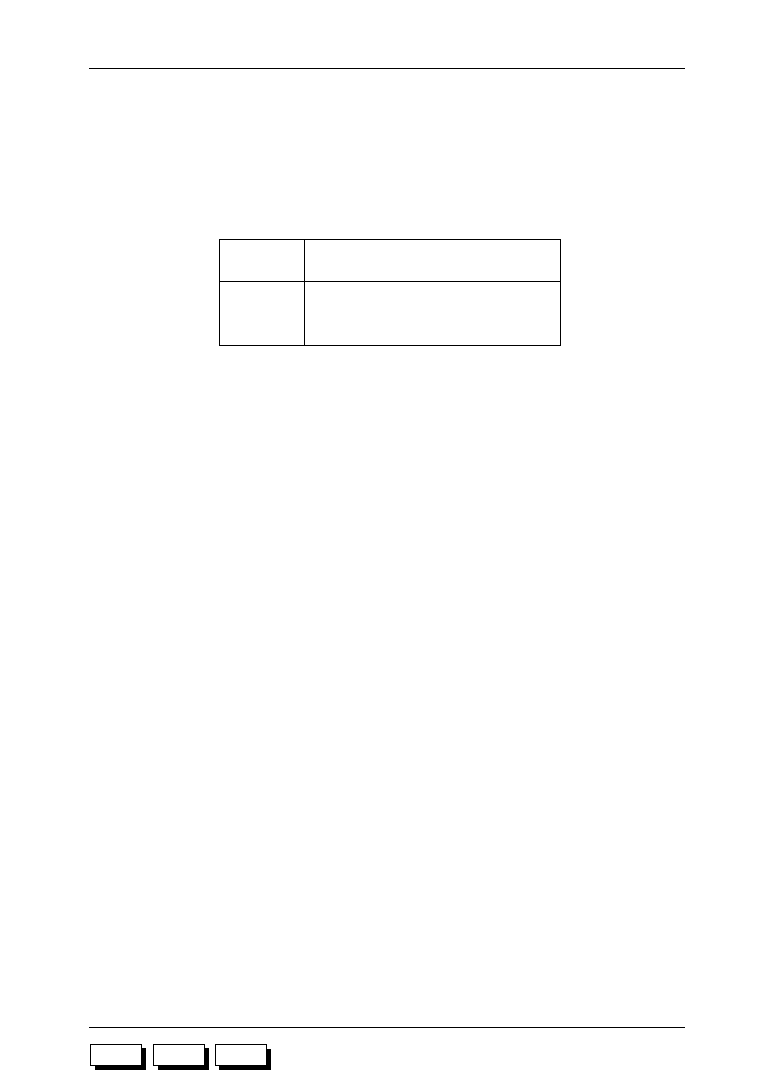

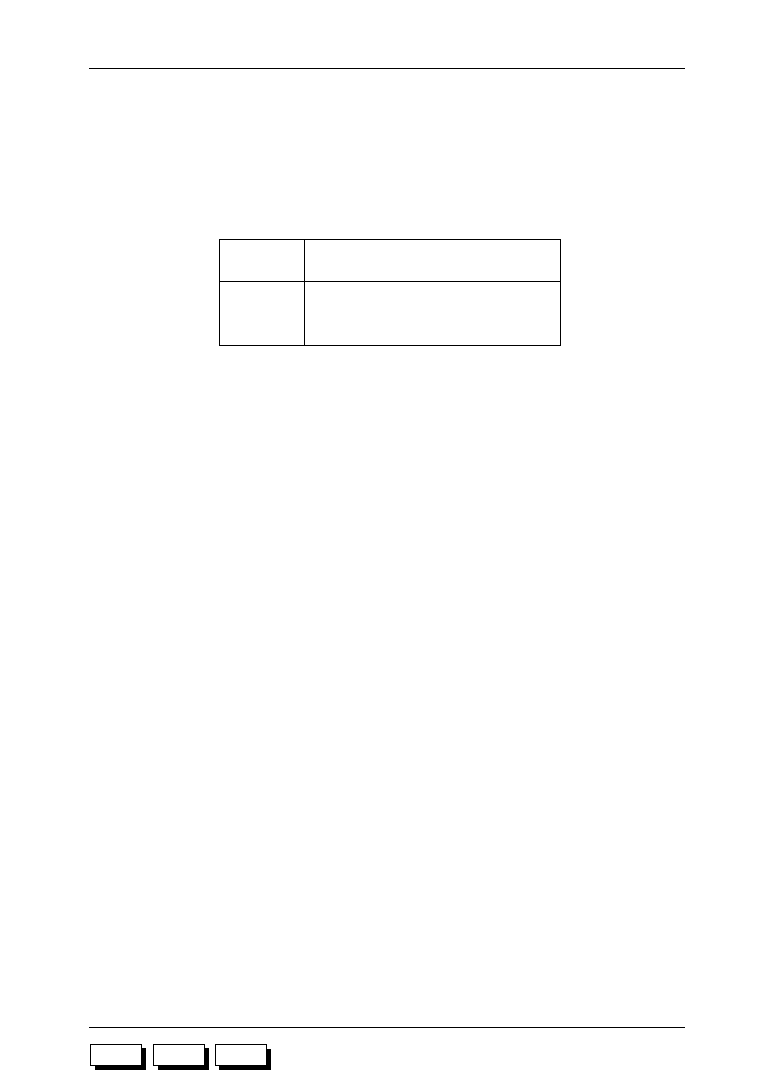

Judgment voltage (V)

Comments

LD0

LD1

1.05 ±0.10

Ta = 25∞C

0

0

1.20 ±0.10

Ta = 25∞C

1

0

1.80 ±0.10

Ta = 25∞C

0

1

2.40 ±0.10

Ta = 25∞C

1

1

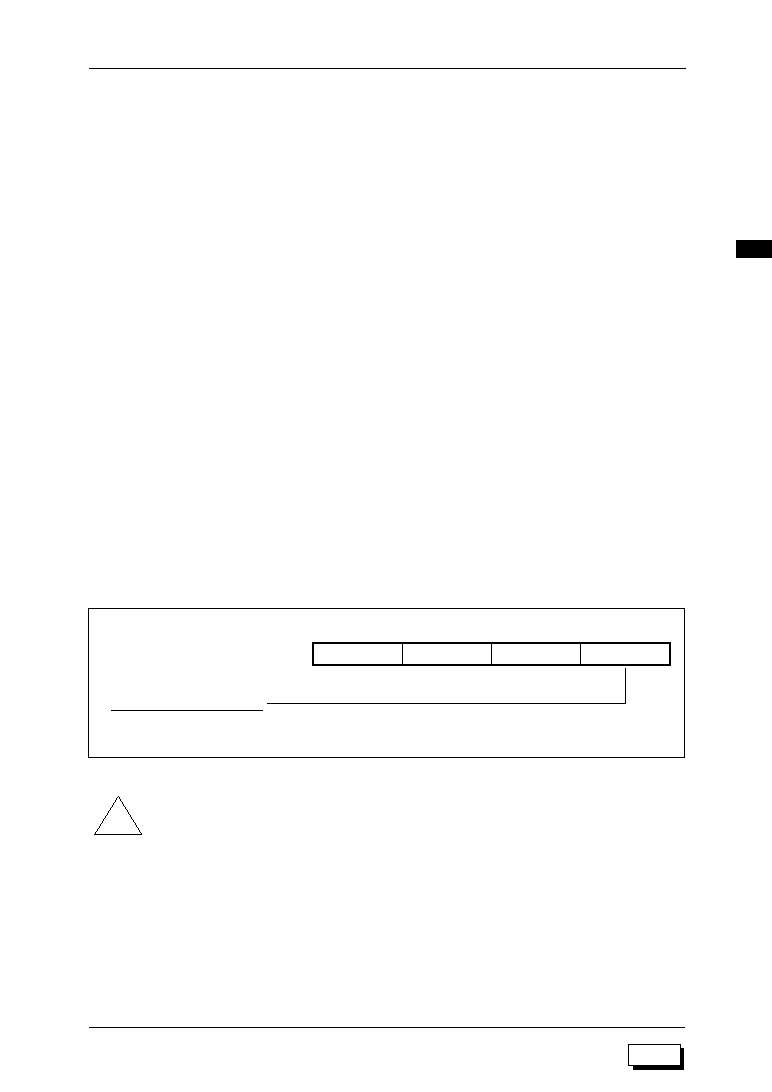

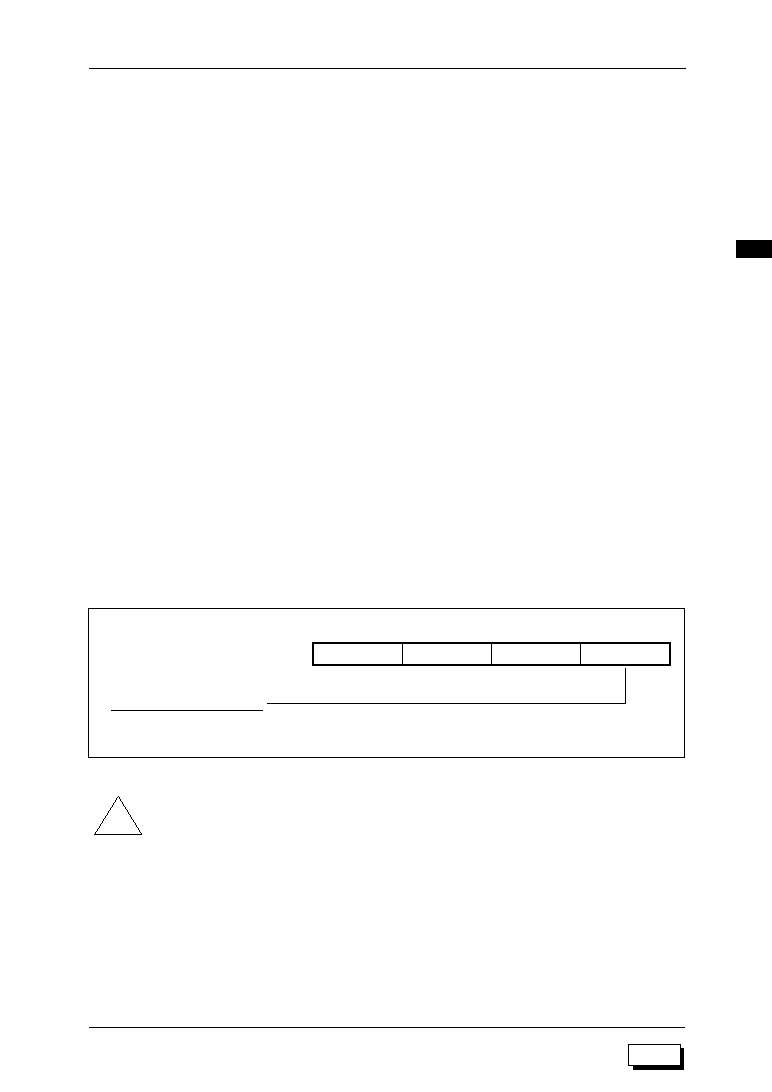

m. Battery check

∑

Function that detects battery low voltage

∑

Selection of judgment voltage by software (LD1 and LD0 bit settings of

BLDCON)

1-4

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

s. Shipping products

Package

Product

ML63187

∑ Chip (111 pads)

ML63187-xxxWA

∑ 128-pin flat package (128QFP)

ML63187-xxxGA

QFP128-P-1420-0.50-K

ML63189B

∑ Chip (123 pads)

ML63189B-xxxWA

∑ 128-pin flat package (128QFP)

ML63189B-xxxGA

QFP128-P-1420-0.50-K

ML63193

∑ Chip (128 pads)

ML63193-xxxWA

∑ 144-pin flat package (144LQFP)

ML63193-xxxTC

LQFP144-P-2020-0.50-K

xxx indicates the ROM code number.

t. Operating temperature

∑

≠20 to +70

∞

C

u. Power supply voltage

∑

When using backup:

0.9 V to 2.7 V (30 to 80 kHz operating frequency)

1.2 V to 2.7 V (500 kHz max. operating frequency)

1.5 V to 2.7 V (1 MHz max. operating frequency)

∑

When not using backup: 1.8 V to 5.5 V (2 MHz max. operating frequency)

1-5

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

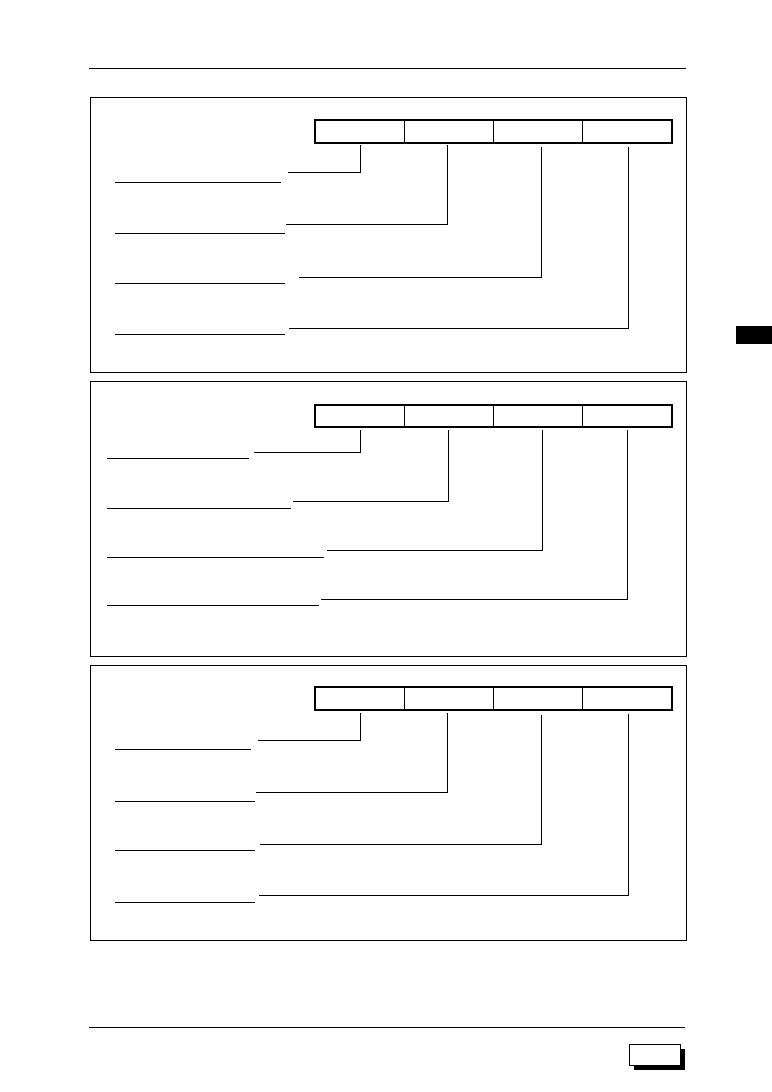

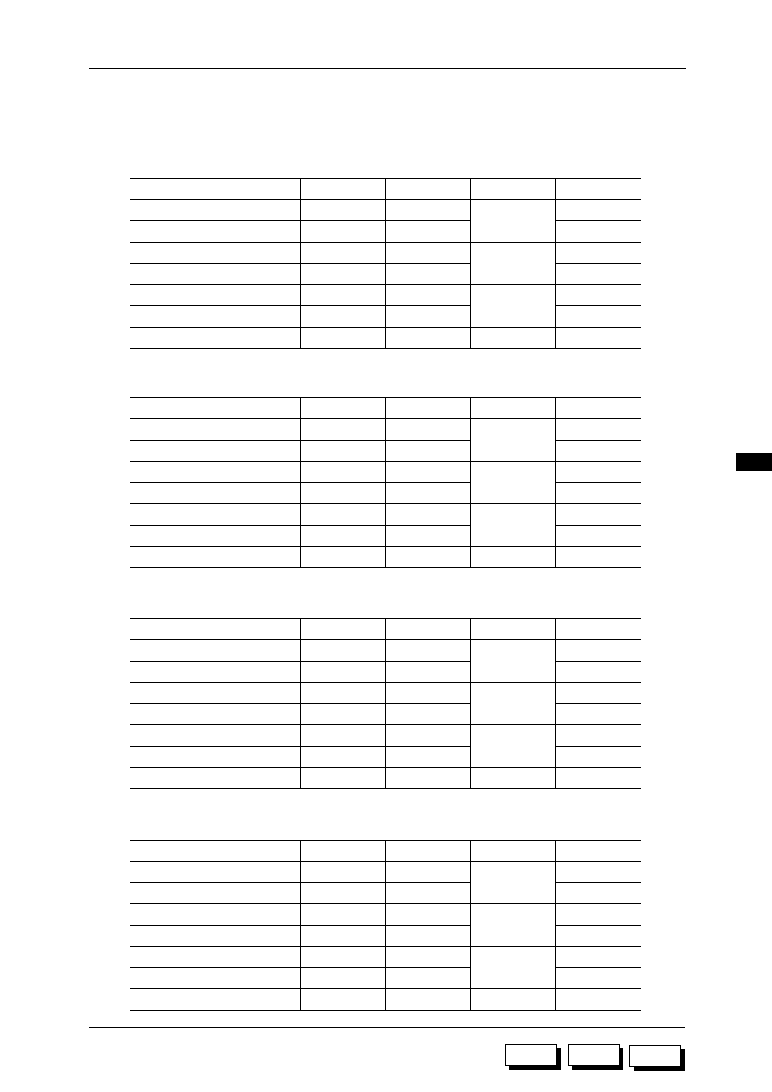

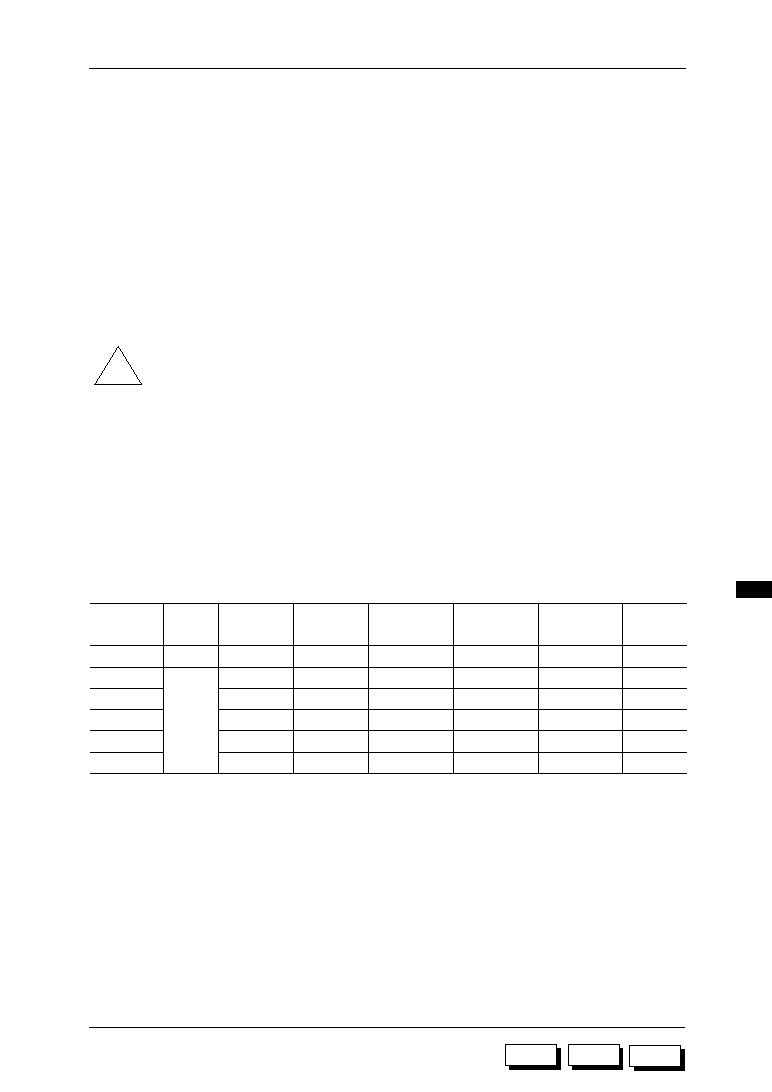

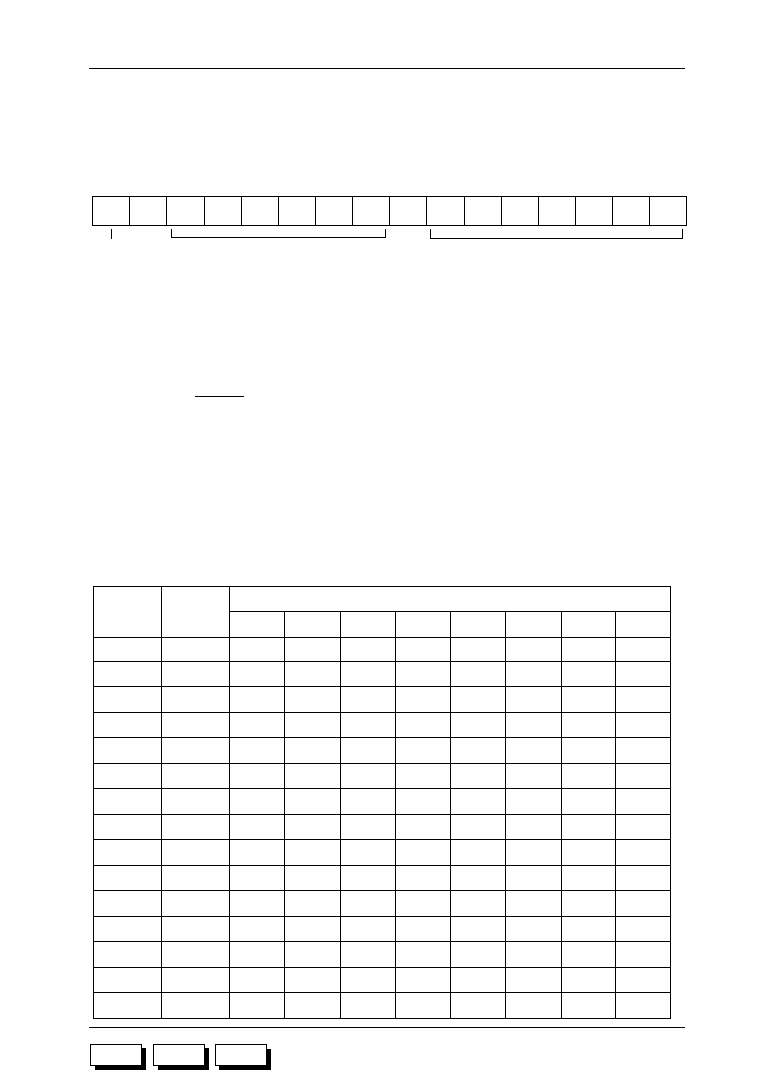

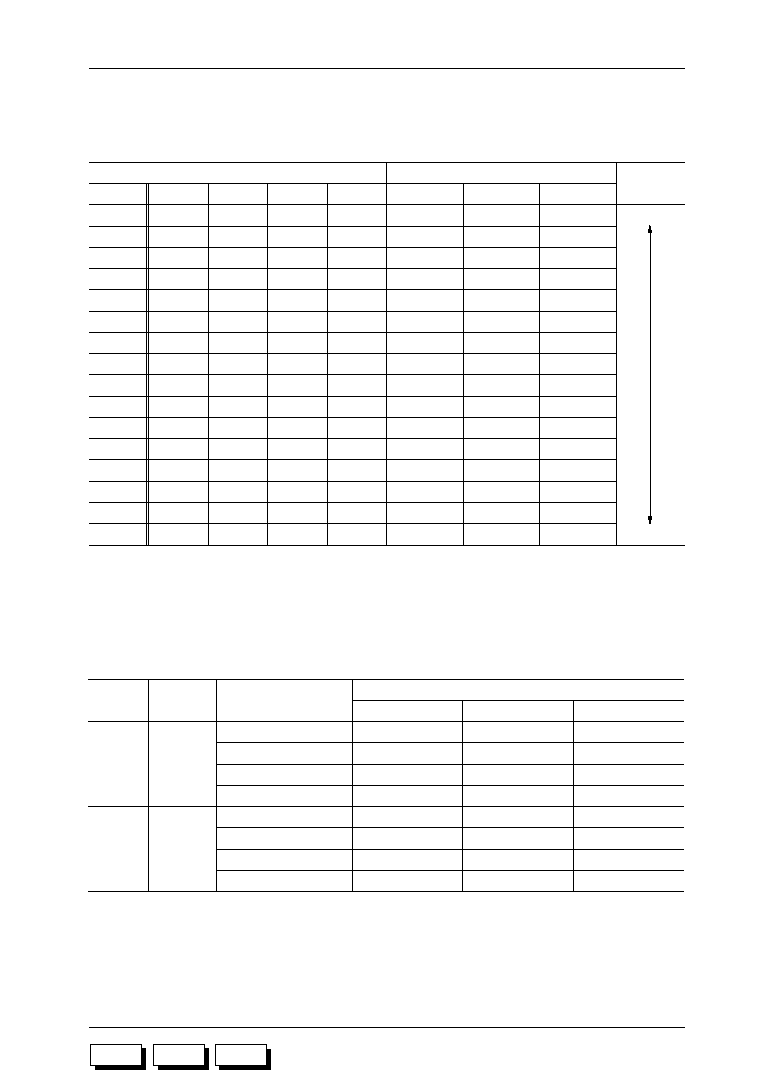

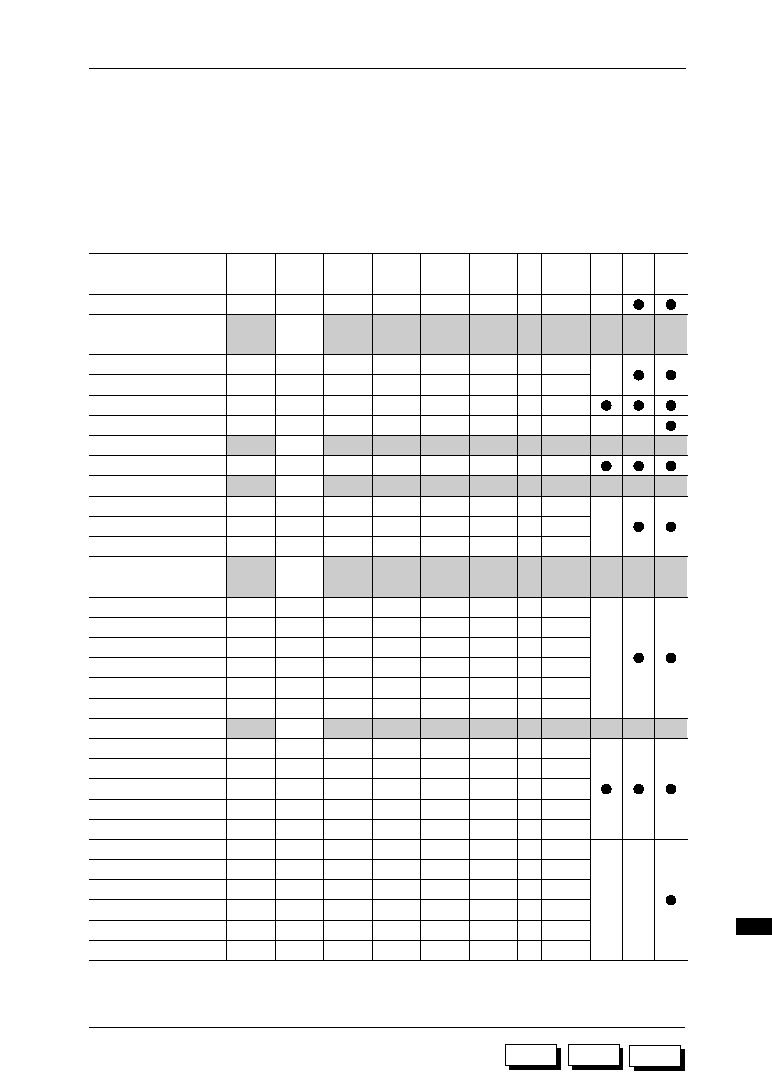

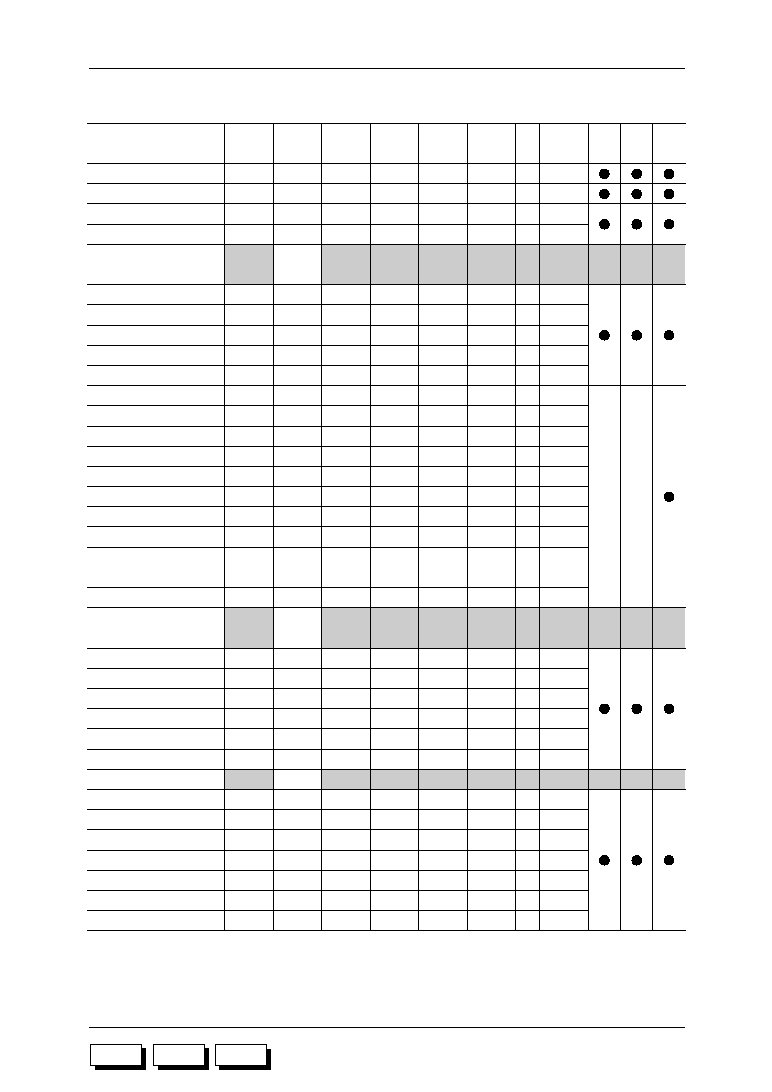

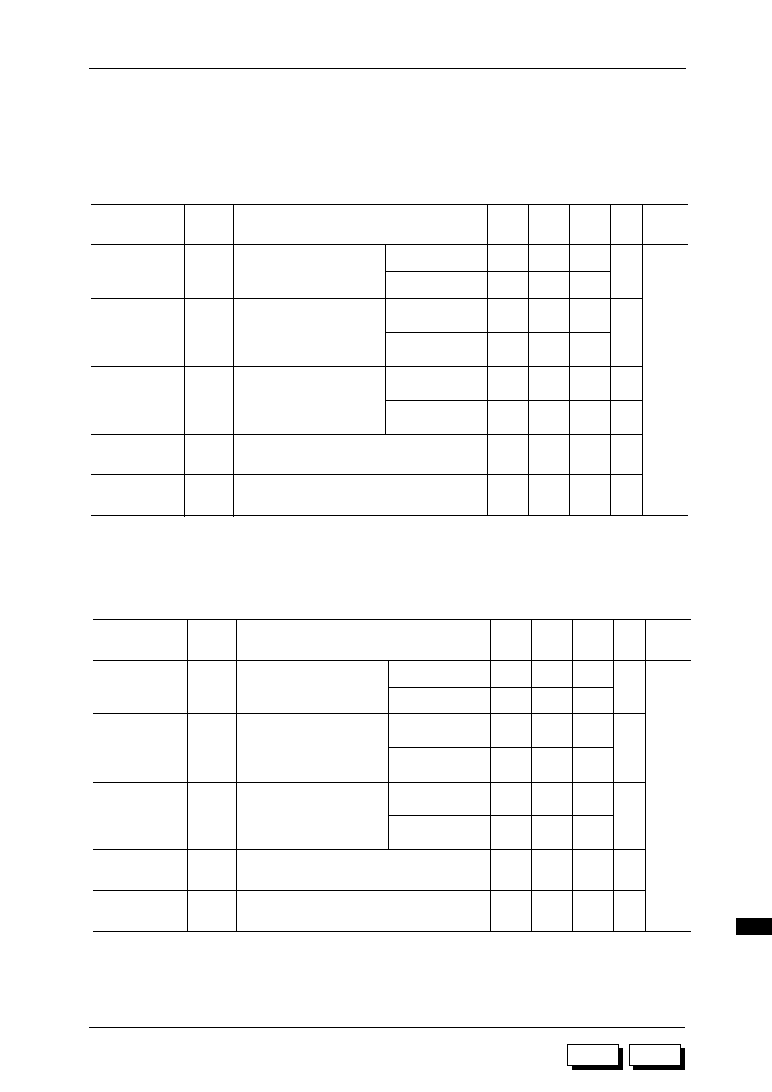

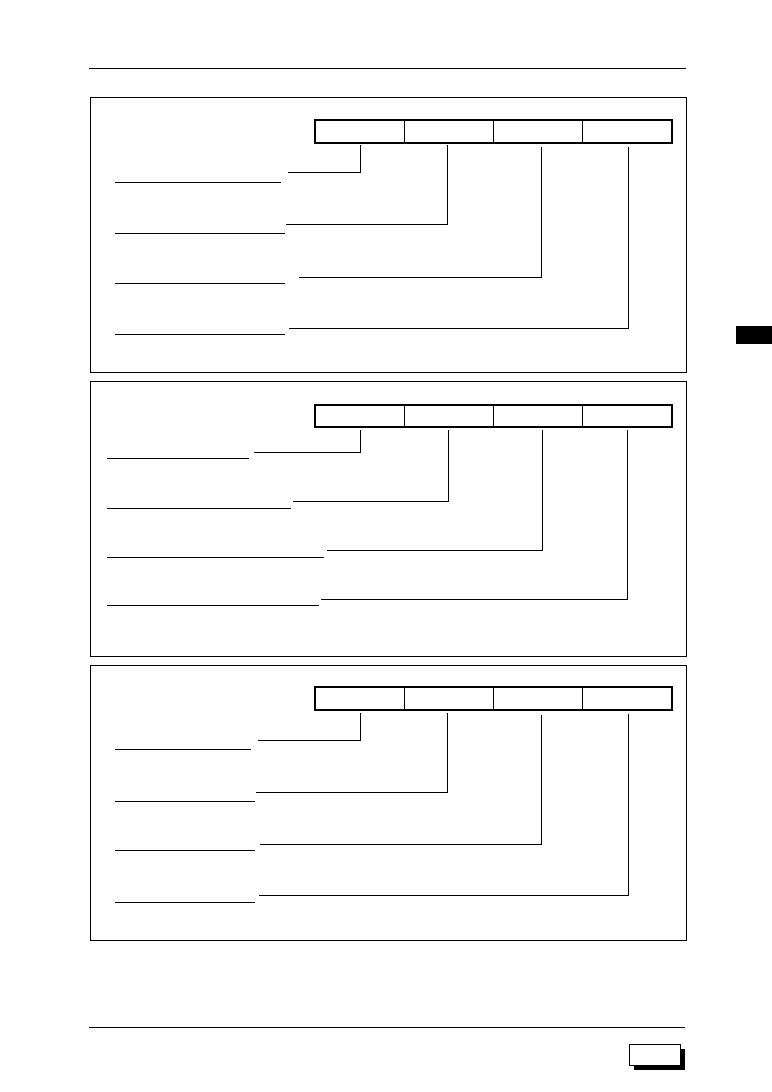

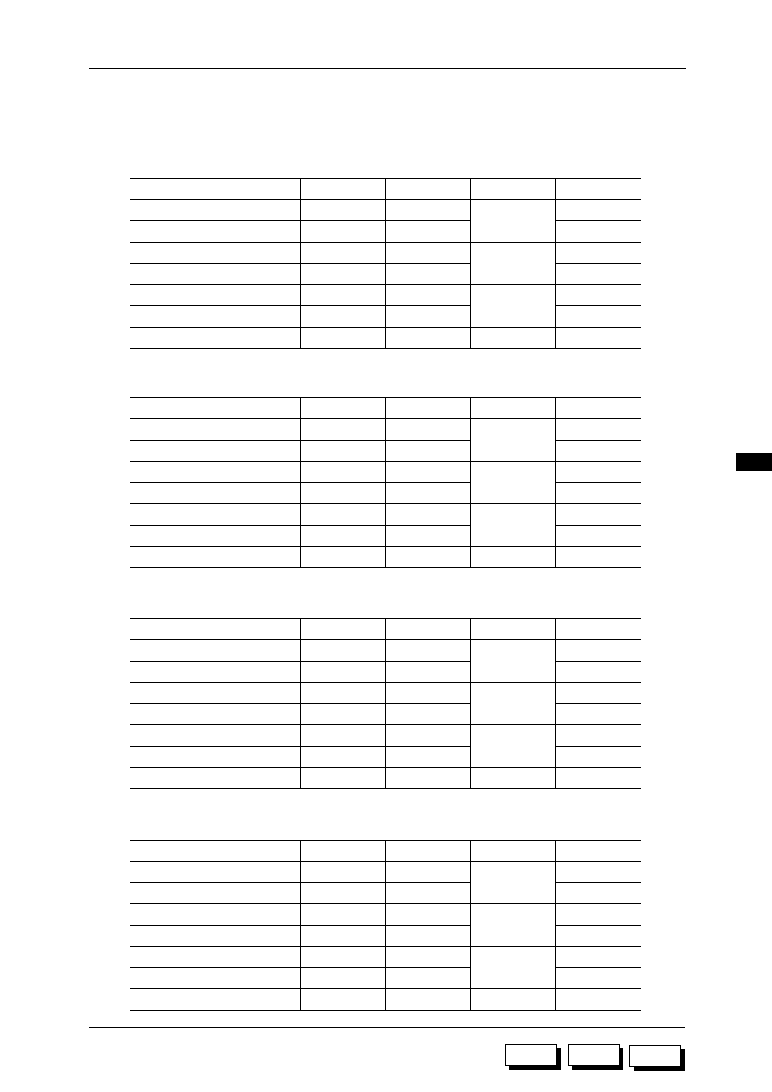

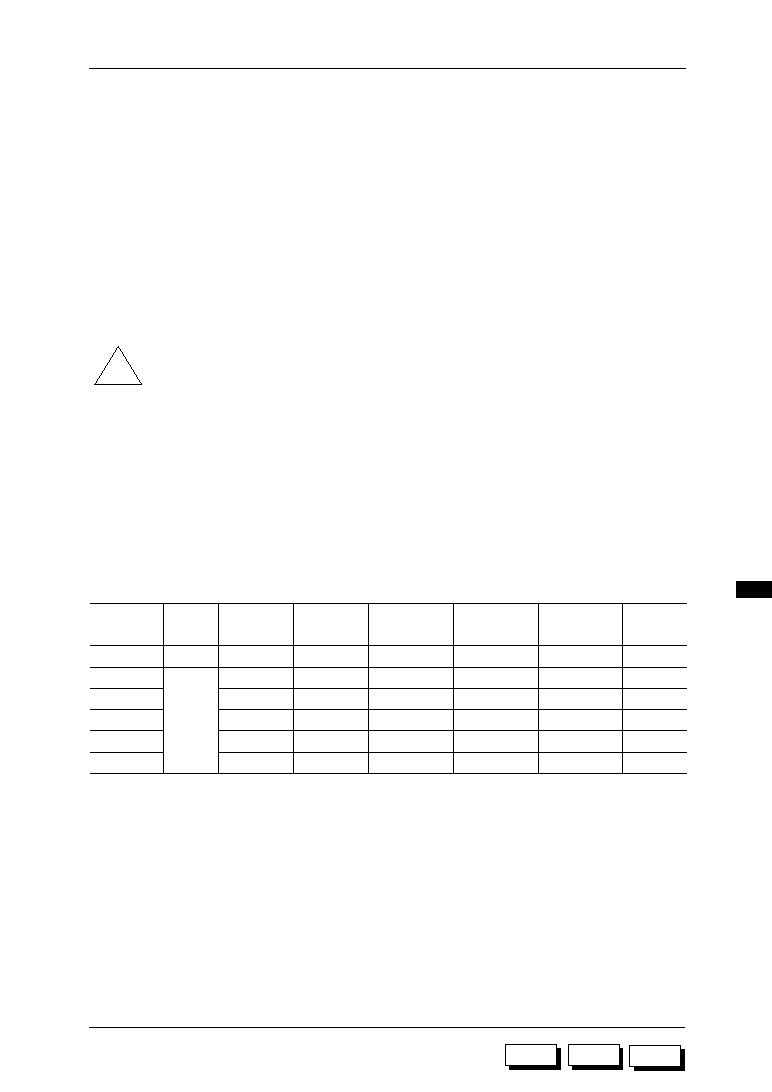

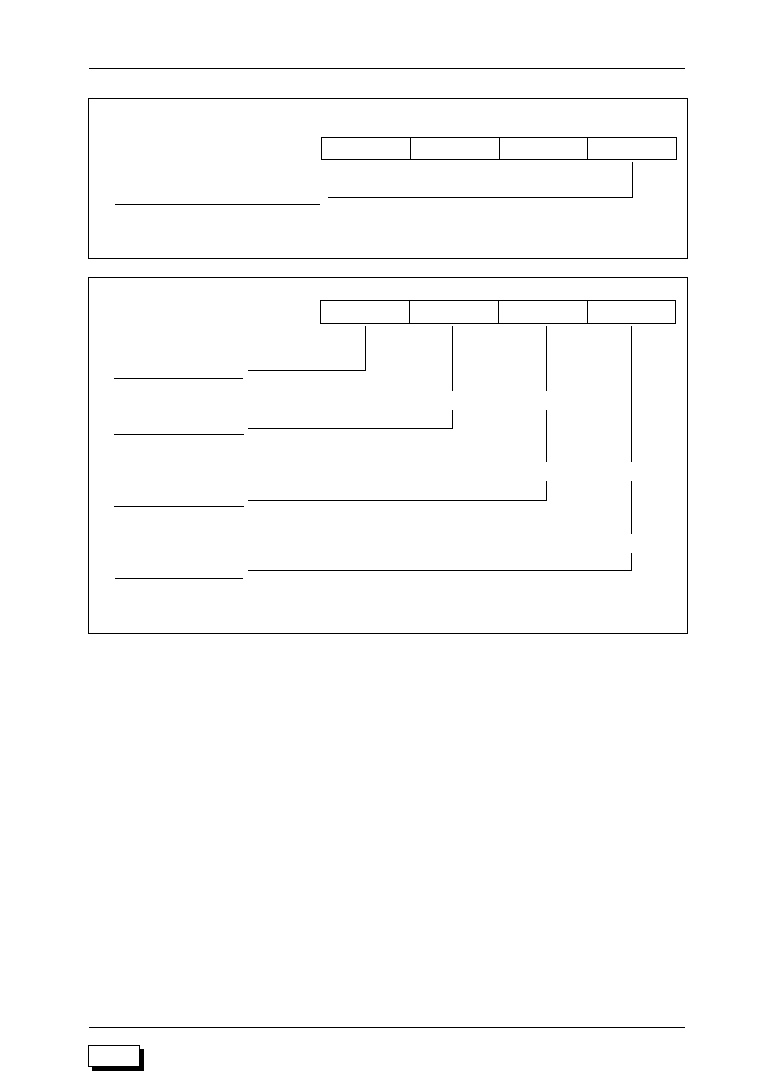

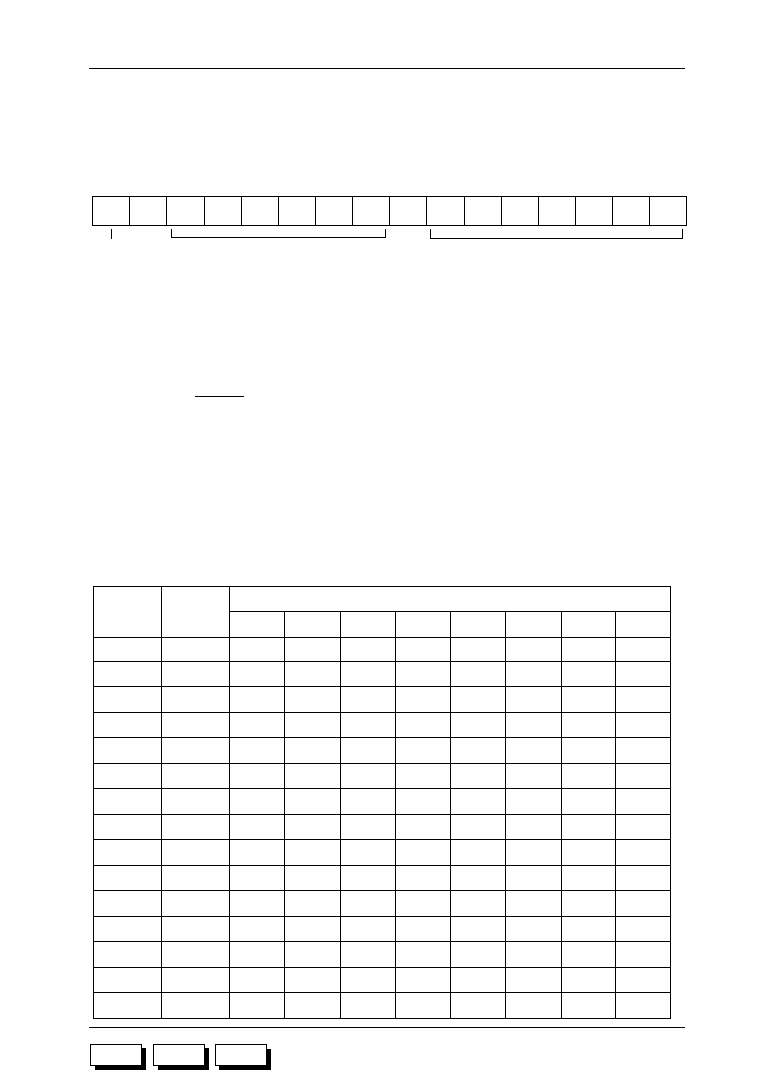

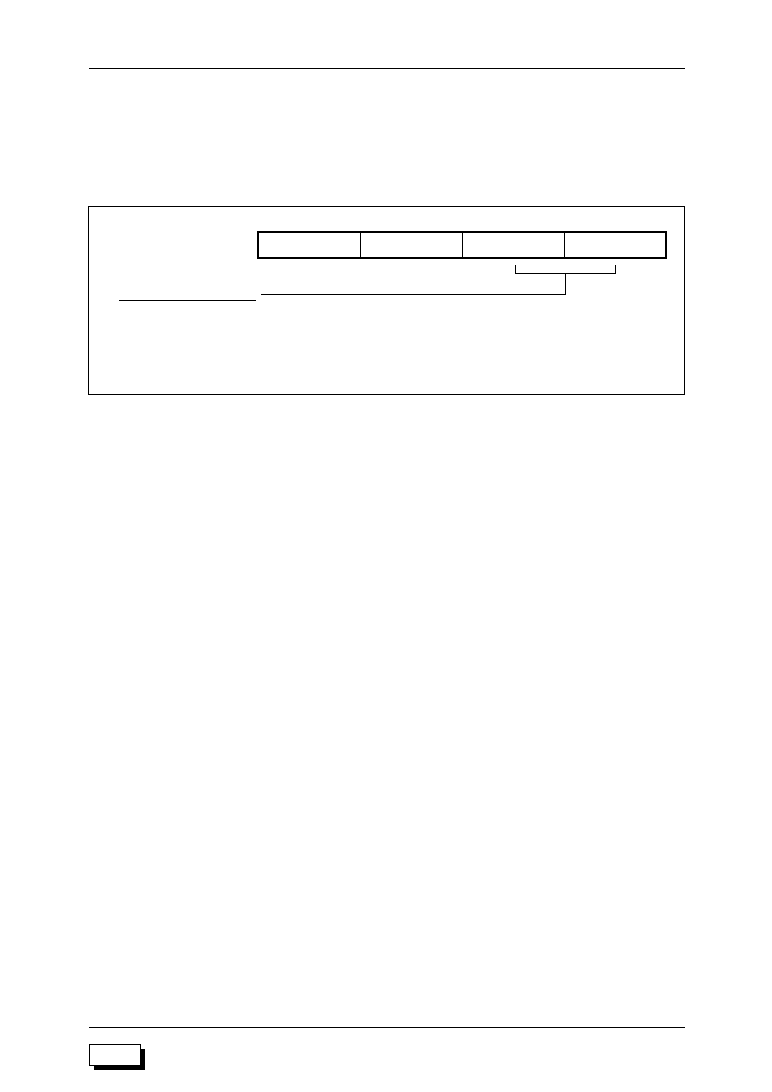

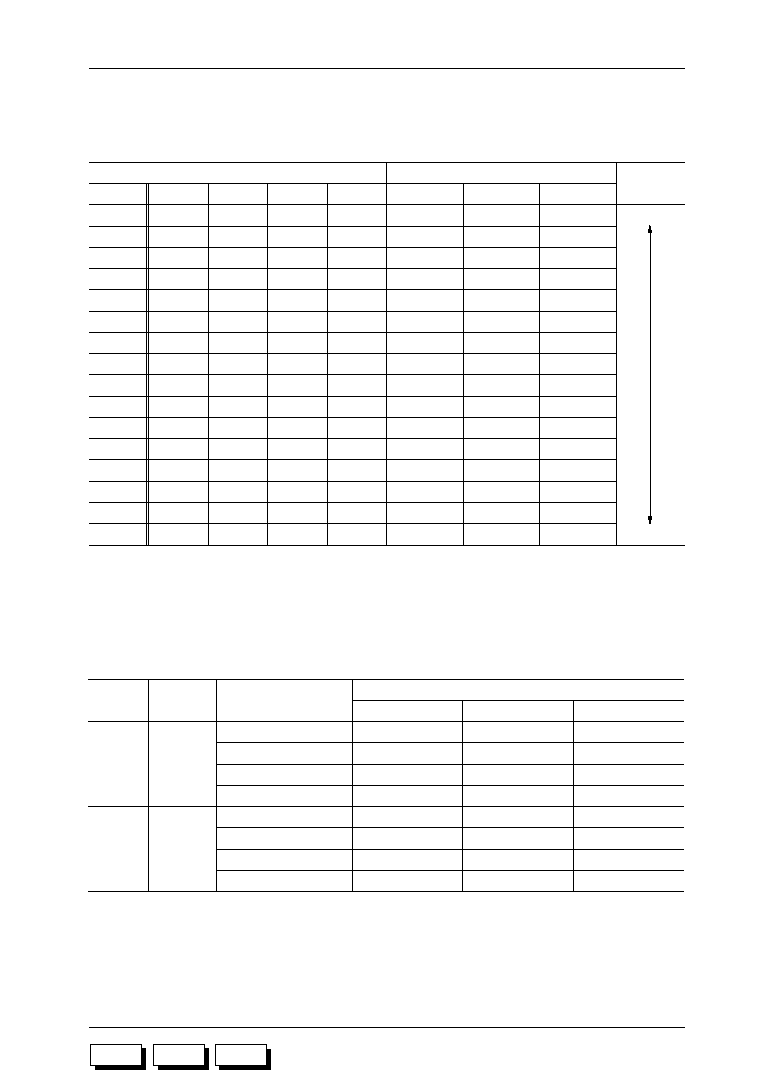

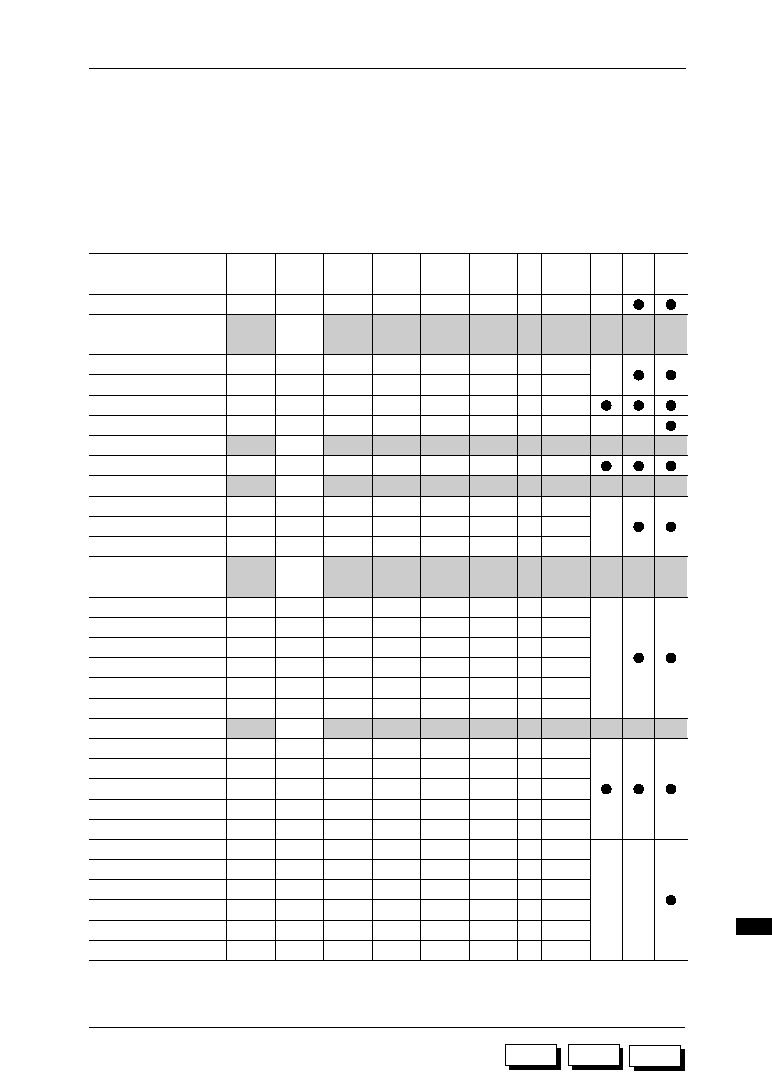

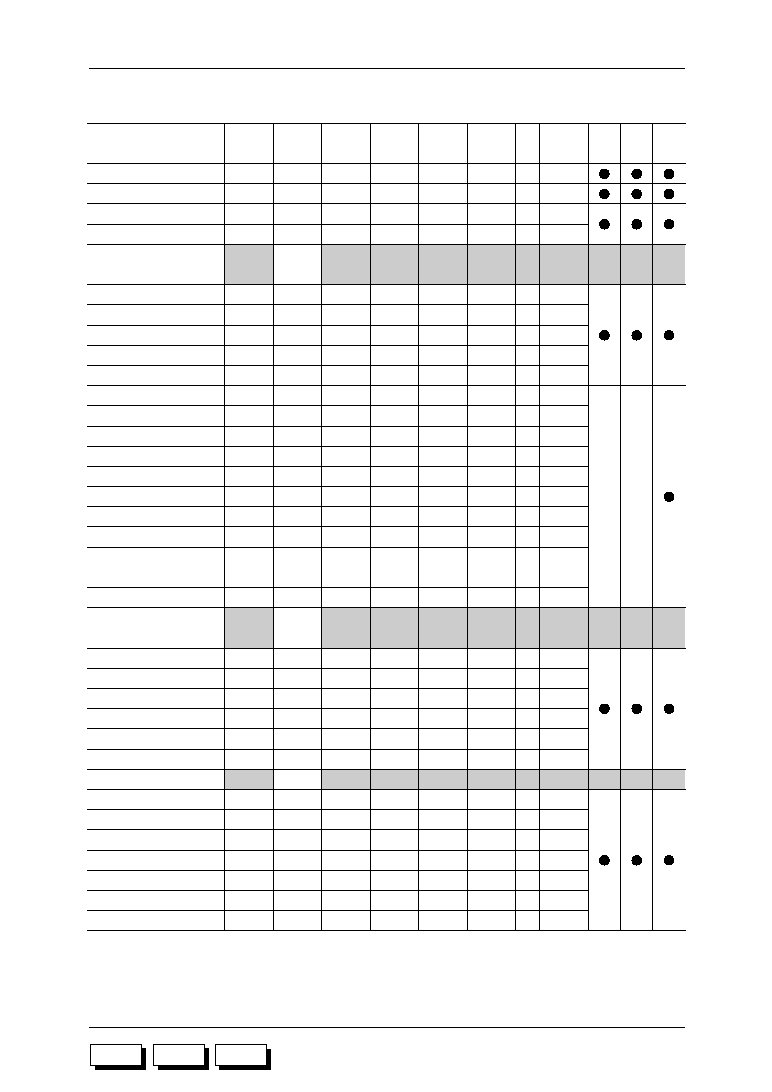

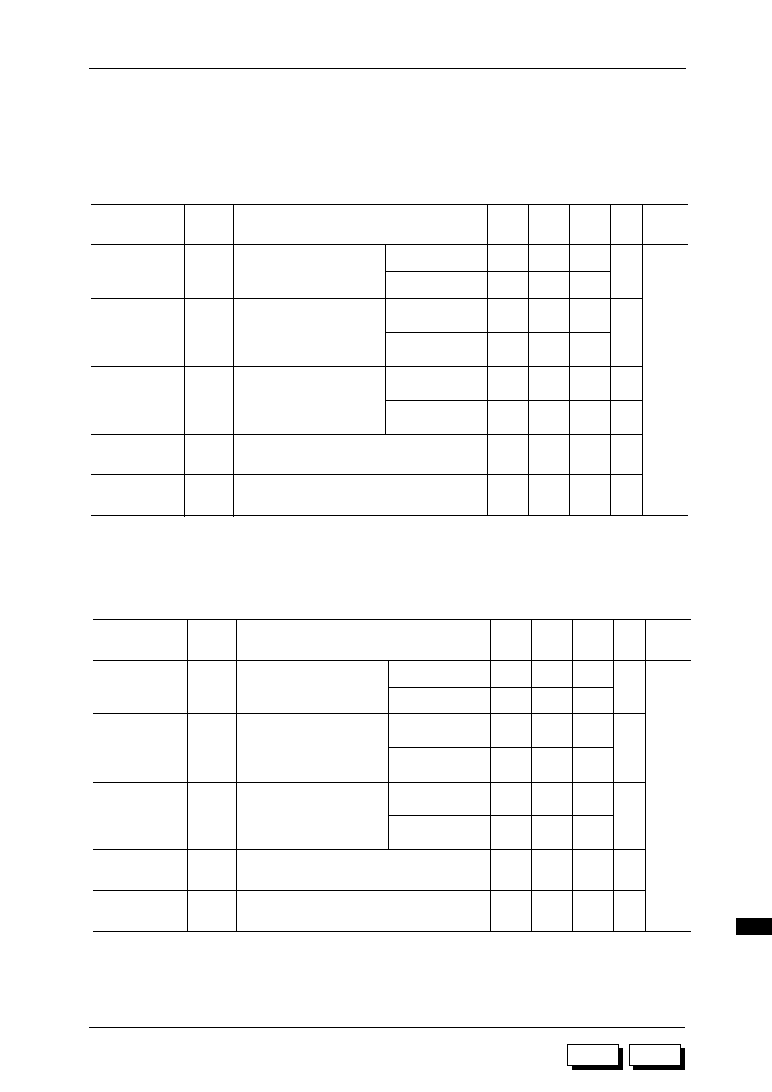

1.3 Function List

Table 1-1 lists the ML63187, ML63189B, and ML63193 functions. The solid black circles

within the chart indicate that the product has the particular function.

Table 1-1 Function List

ML63193 interrupt

Function

Symbol

ML63187

ML63189B

Reference page

ROM (

• 16 bits)

ROM

16352

32736

∆2-7

RAM (

• 4 bits)

RAM

1024

1536

∆2-8

STACK RAM

STACK

16 levels

16 levels

∆2-5

16 levels

16 levels

∆2-6

System reset generation circuit

RST

l

l

∆3-2

Interrupt

INT187

l

--

∆4-1

INT189

--

l

∆5-1

Clock generator circuit

OSC

l

l

∆7-1

Time base counter

TBC

l

l

∆8-1

Timers

TIMER

l

l

∆9-1

100 Hz timer counter

100HzTC

l

l

∆10-1

Watchdog timer

WDT

l

l

∆11-1

Input port

INPUT PORT

--

1 port

• 4 bits

--

P0

--

l

∆12-2

I/O port

I/O PORT 2 ports

• 4 bits 4 ports • 4 bits

--

P9

--

l

∆12-7

PA

--

l

PB

l

l

∆12-12

PE

l

l

∆12-25

Melody driver

MELODY

l

l

∆13-1

Shift register

SFT

l

l

∆15-1

LCD driver

LCD

16 lines

16 lines

∆16-1

64 lines

64 lines

Display register (

• 4 bits)

DSPR

256

256

∆16-4

Bias generator

BIAS

l

l

∆16-6

Battery low detect circuit

BLD

l

l

∆18-1

Backup circuit

BACKUP

l

l

∆19-1

Call

Register

ML63187 interrupt

ML63189B interrupt

Port 0

Port 9

Port A

Port B

Port E

COM

SEG

INT193

--

--

∆6-1

PC

--

--

∆12-18

Port C

Serial port

SIO

--

--

∆14-1

Multiplication/division circuit

MULDIV

--

--

∆17-1

ML63193

65504

2048

16 levels

16 levels

l

--

--

l

l

l

l

l

1 port

• 4 bits

l

5 ports

• 4 bits

l

l

l

l

l

l

16 lines

64 lines

256

l

l

l

l

l

l

l

1-6

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

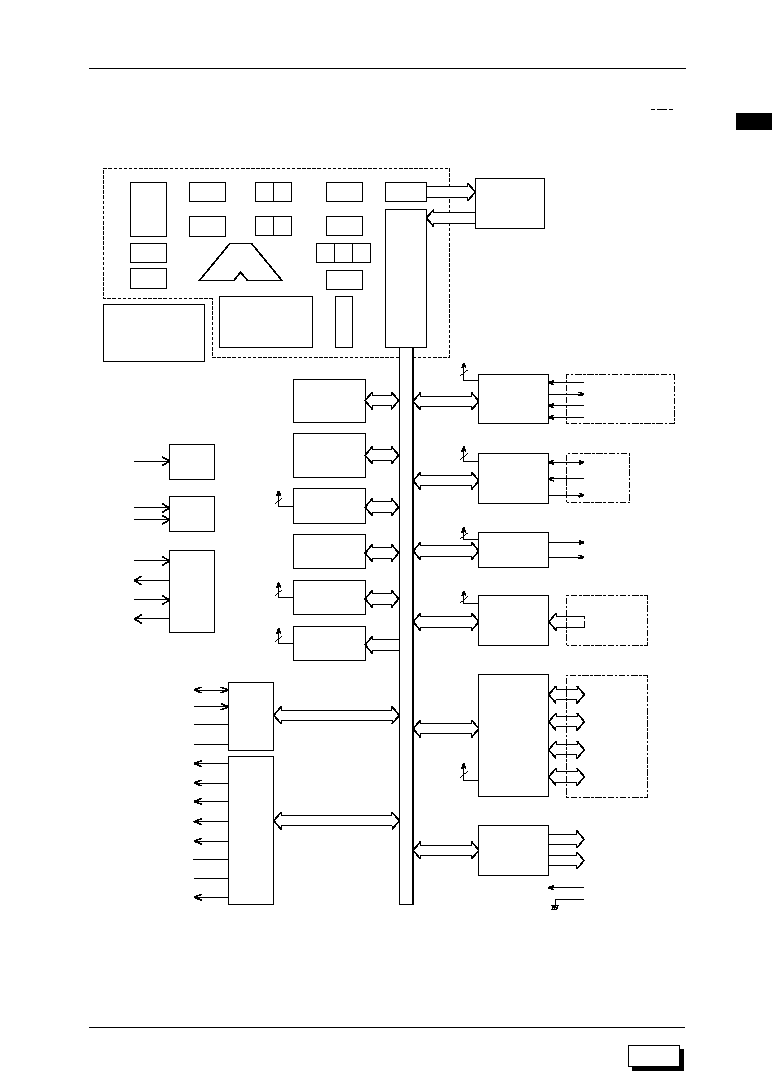

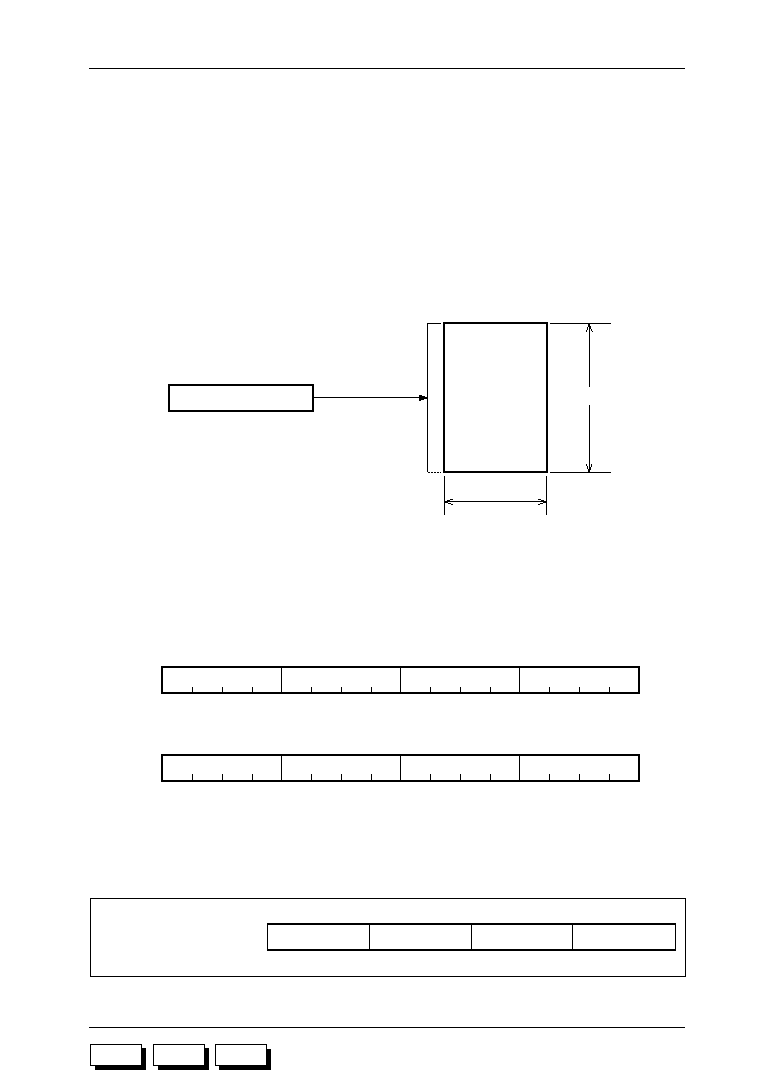

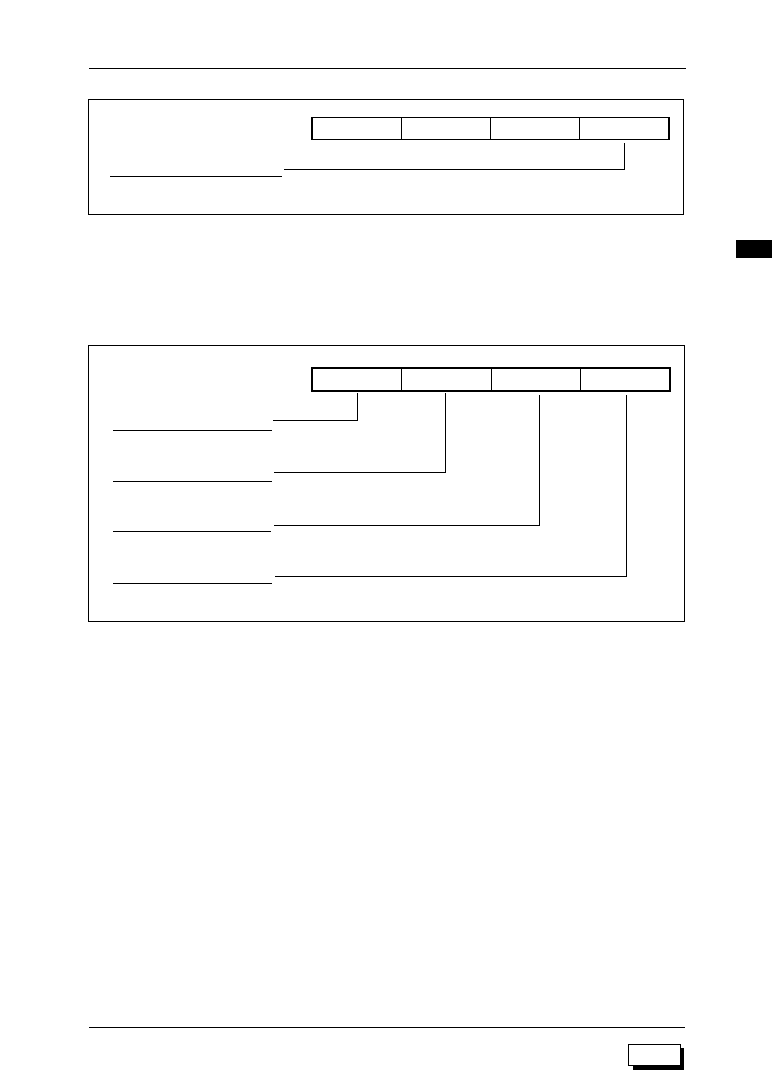

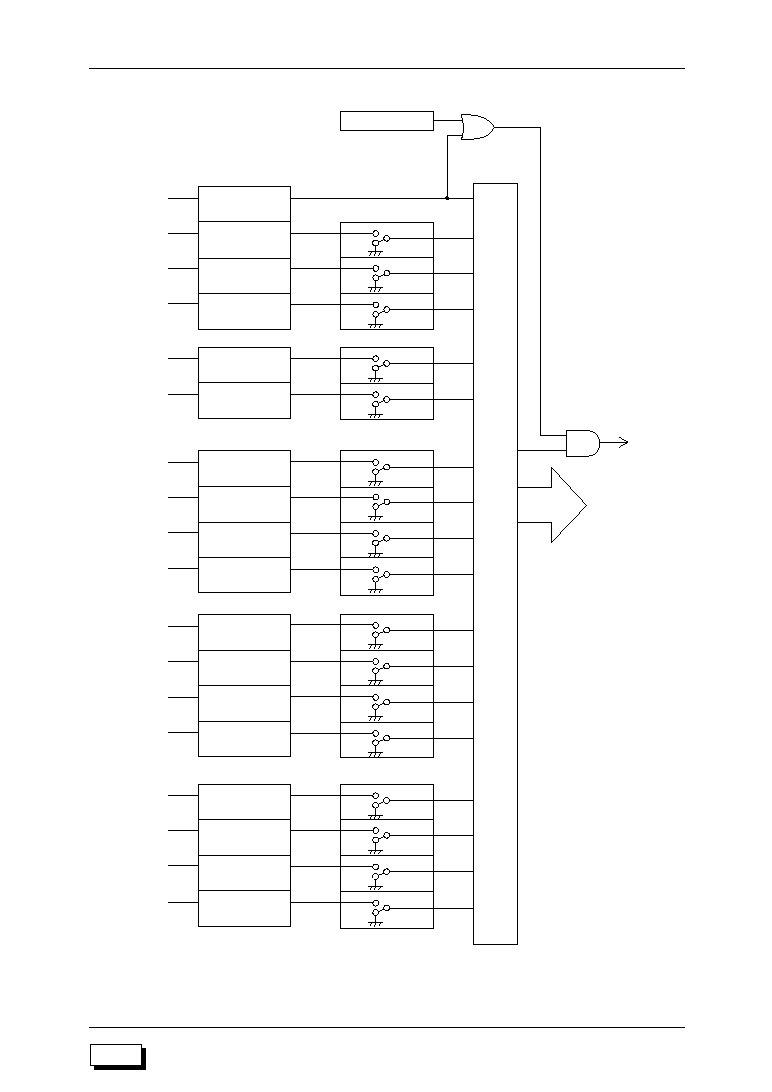

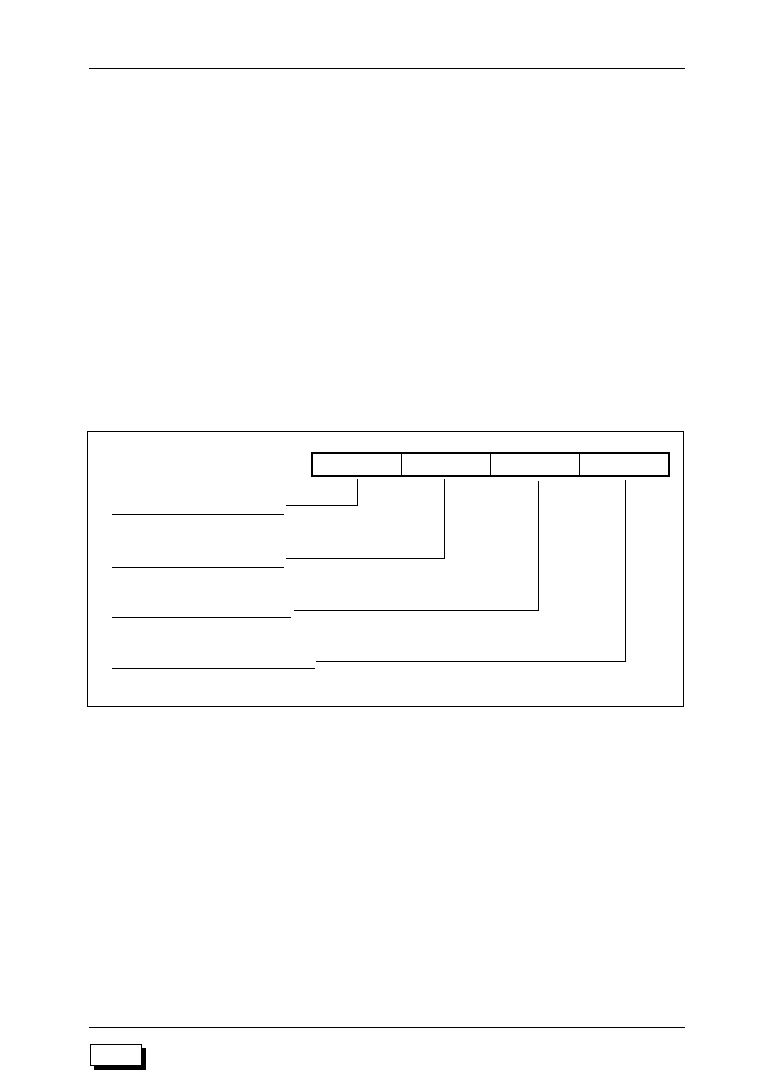

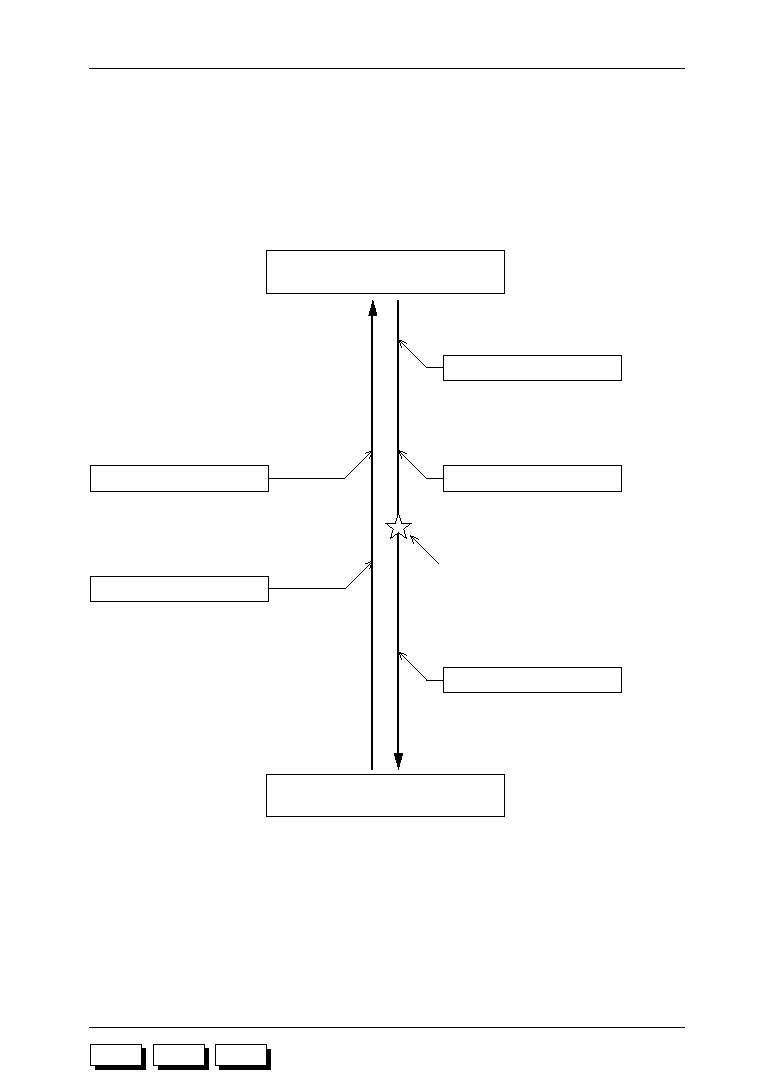

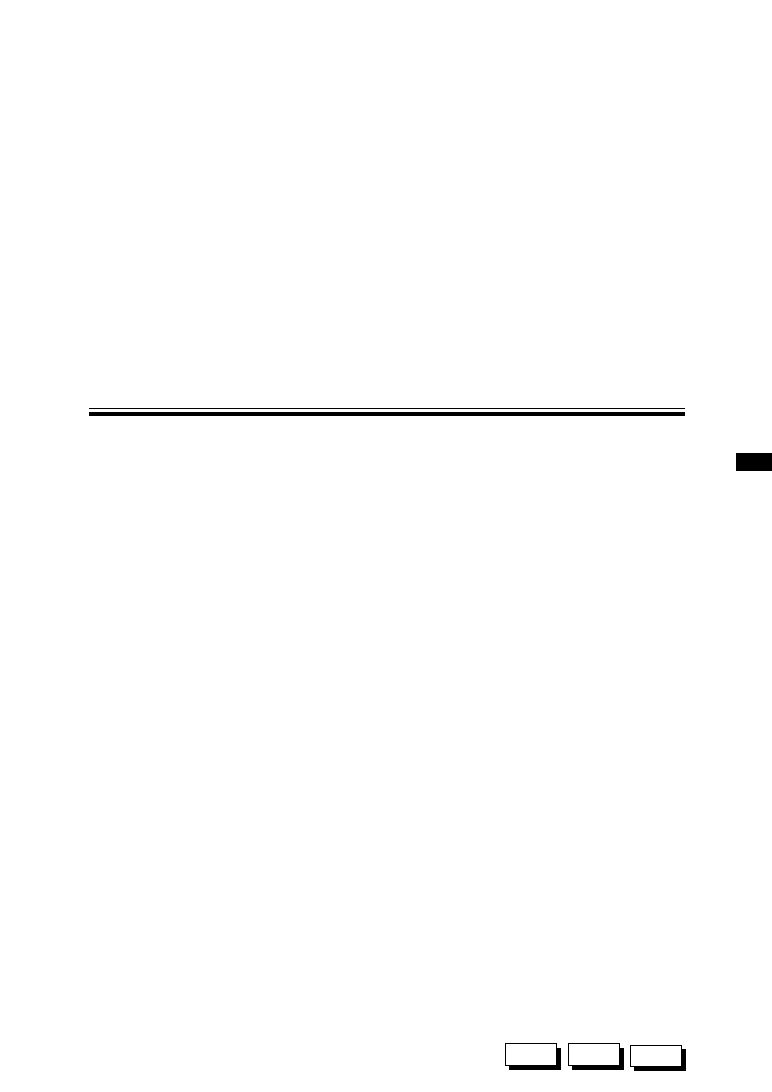

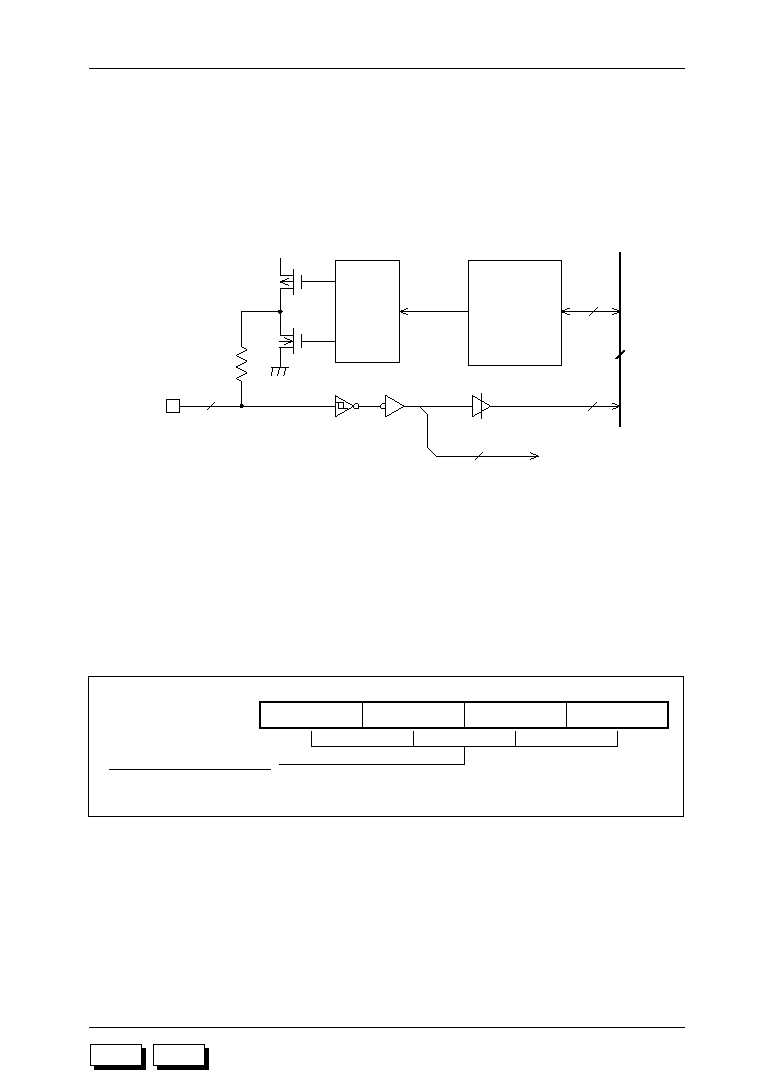

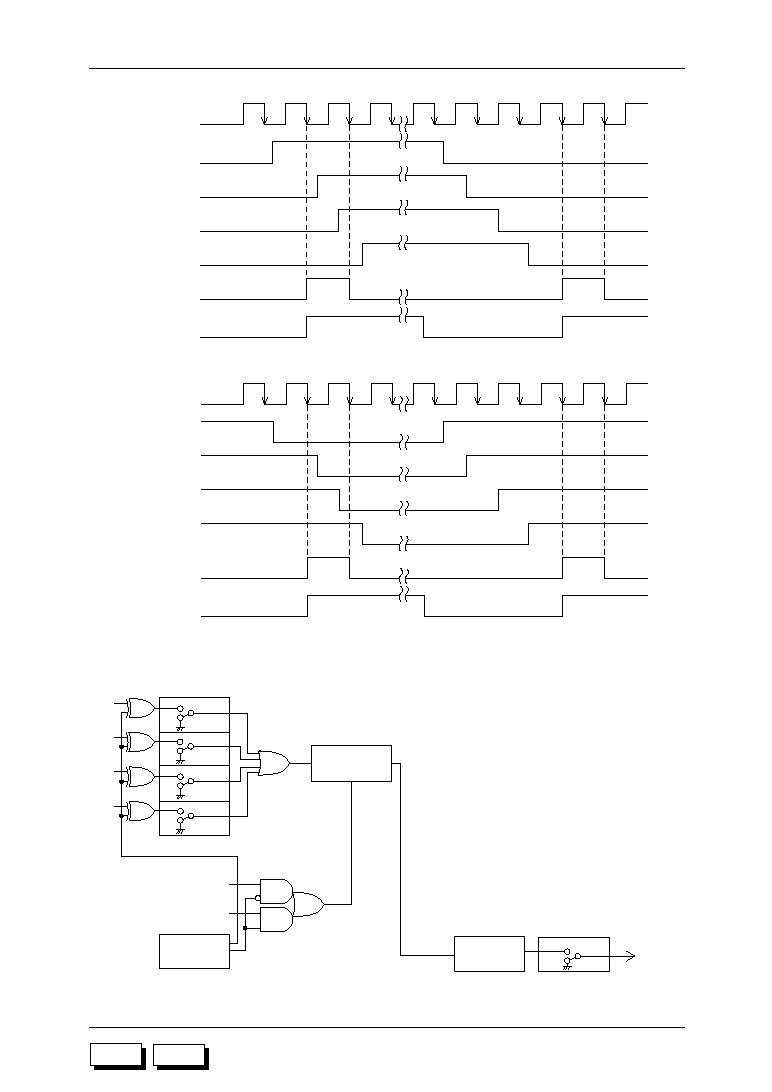

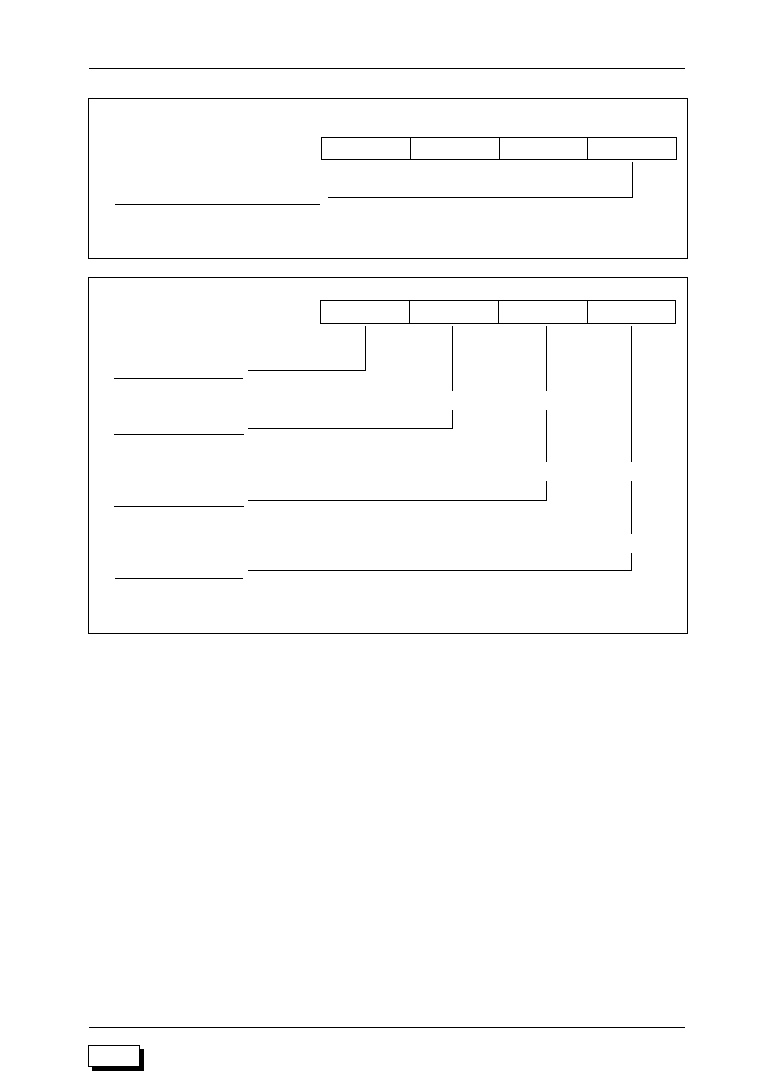

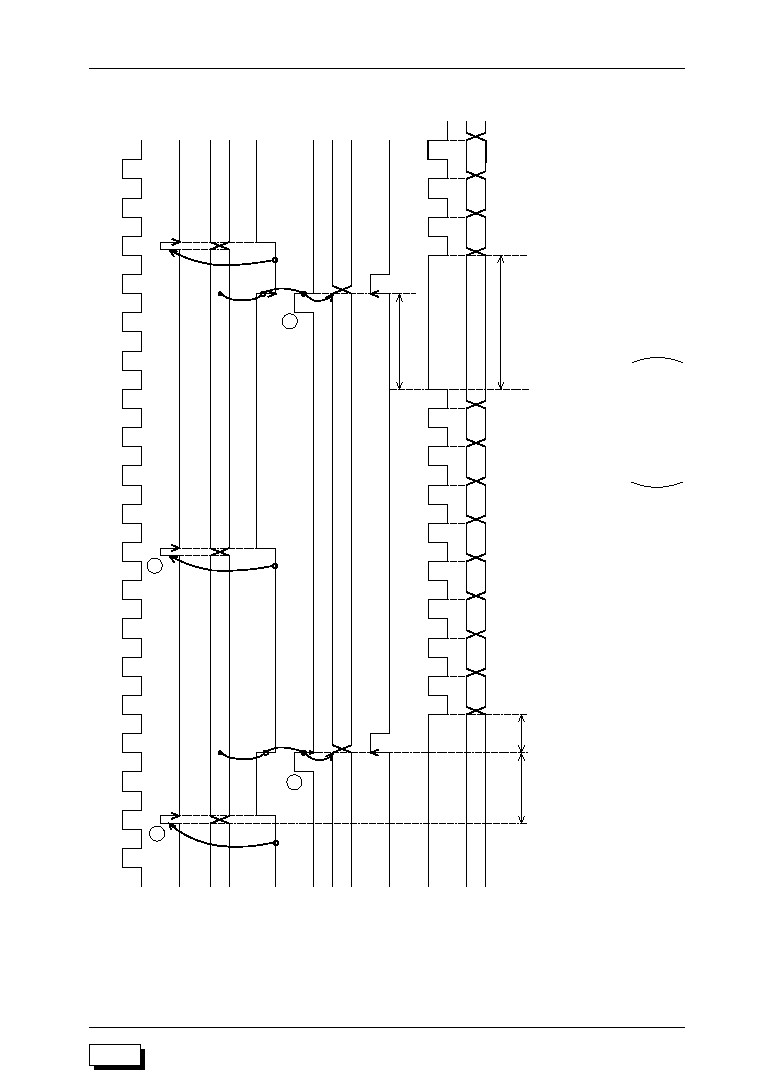

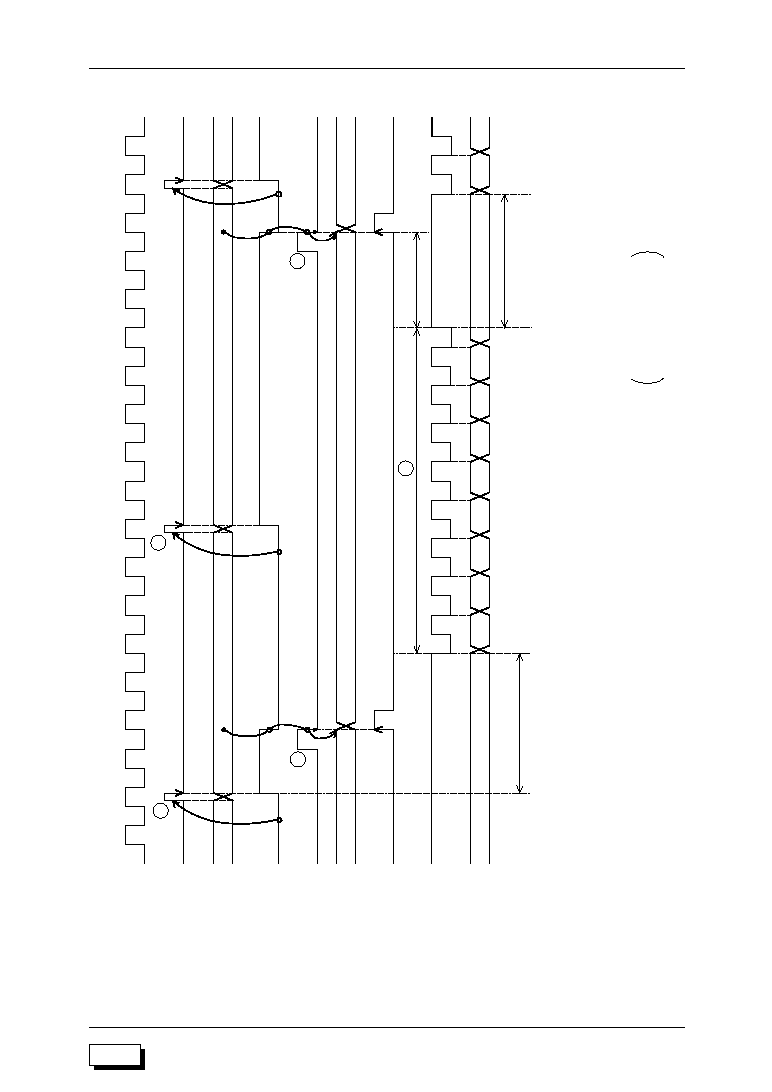

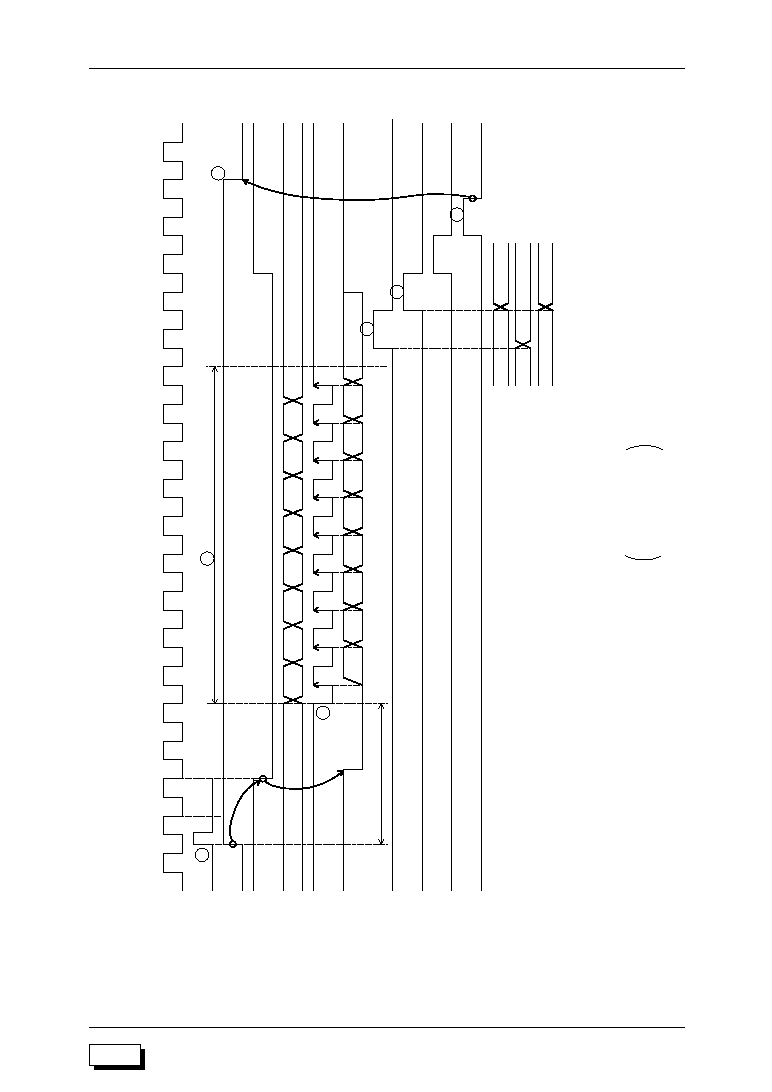

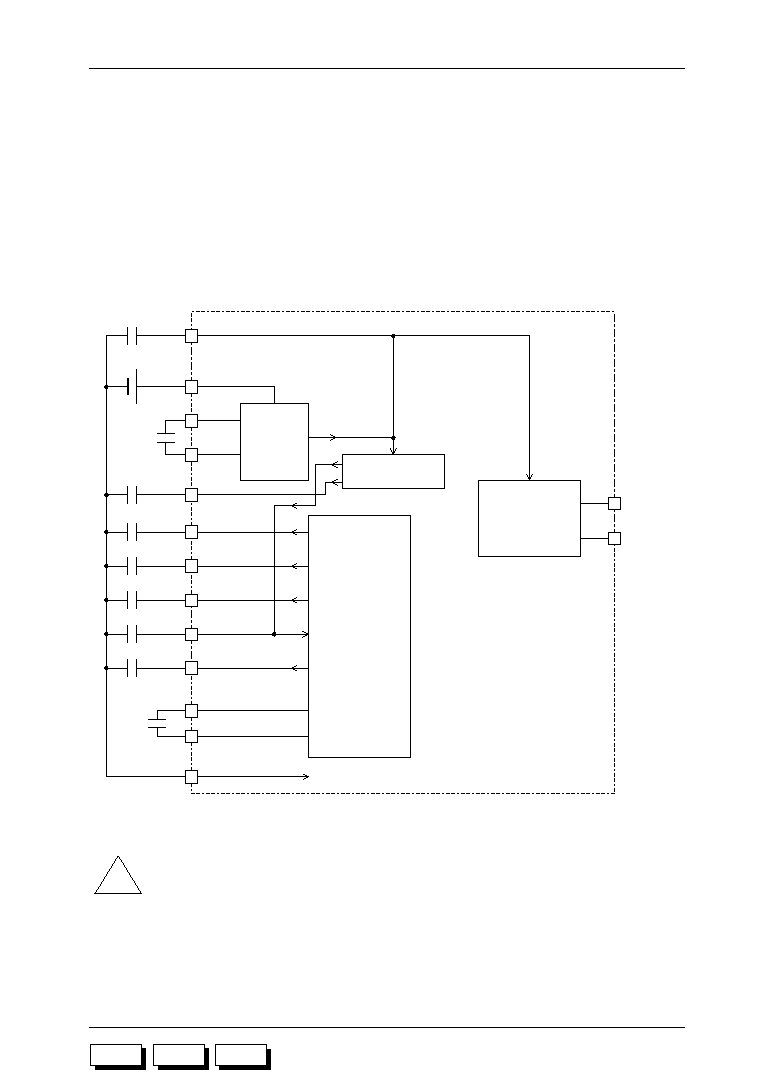

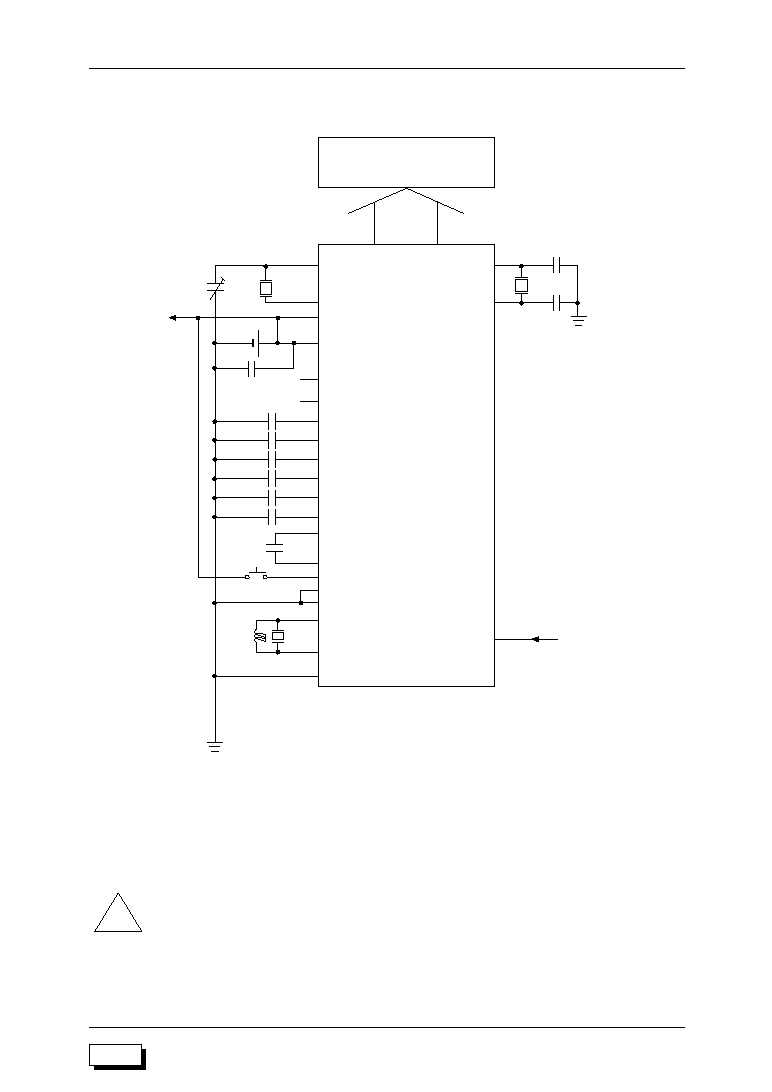

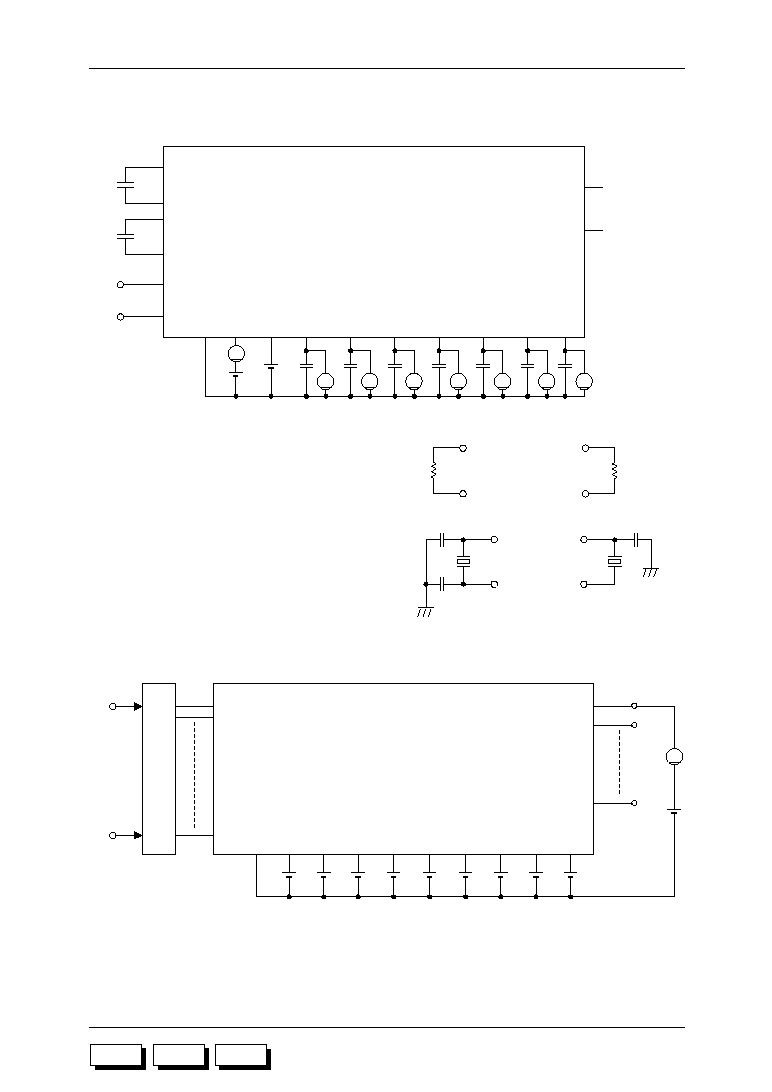

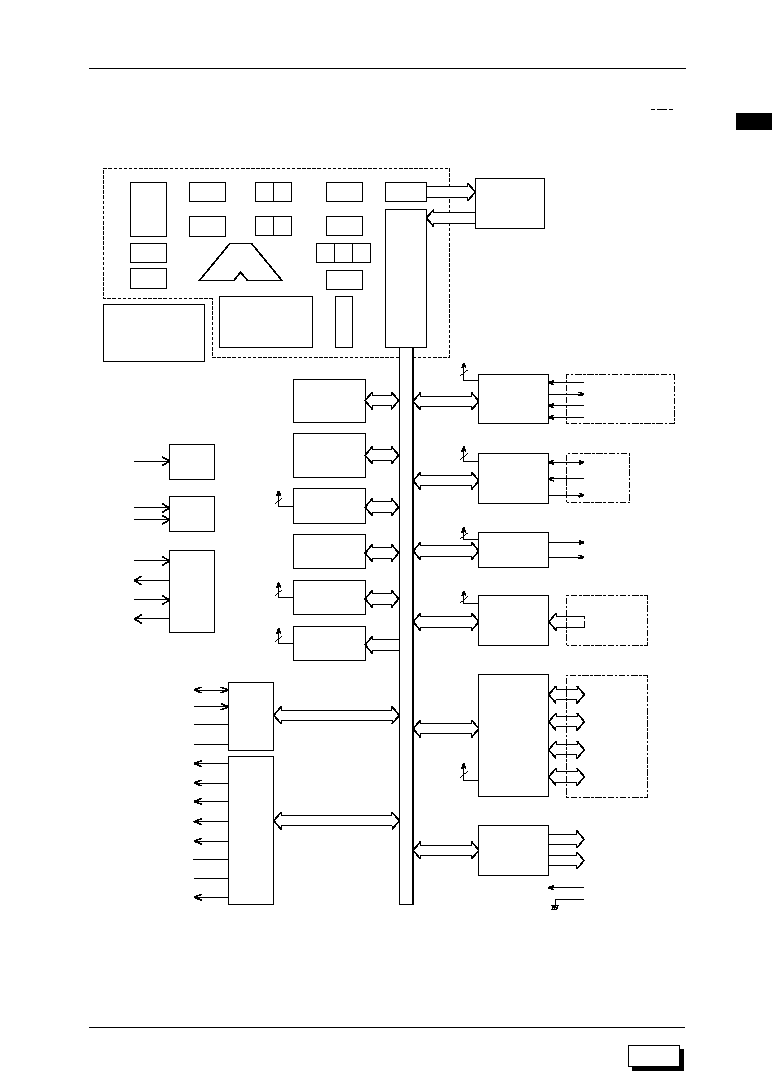

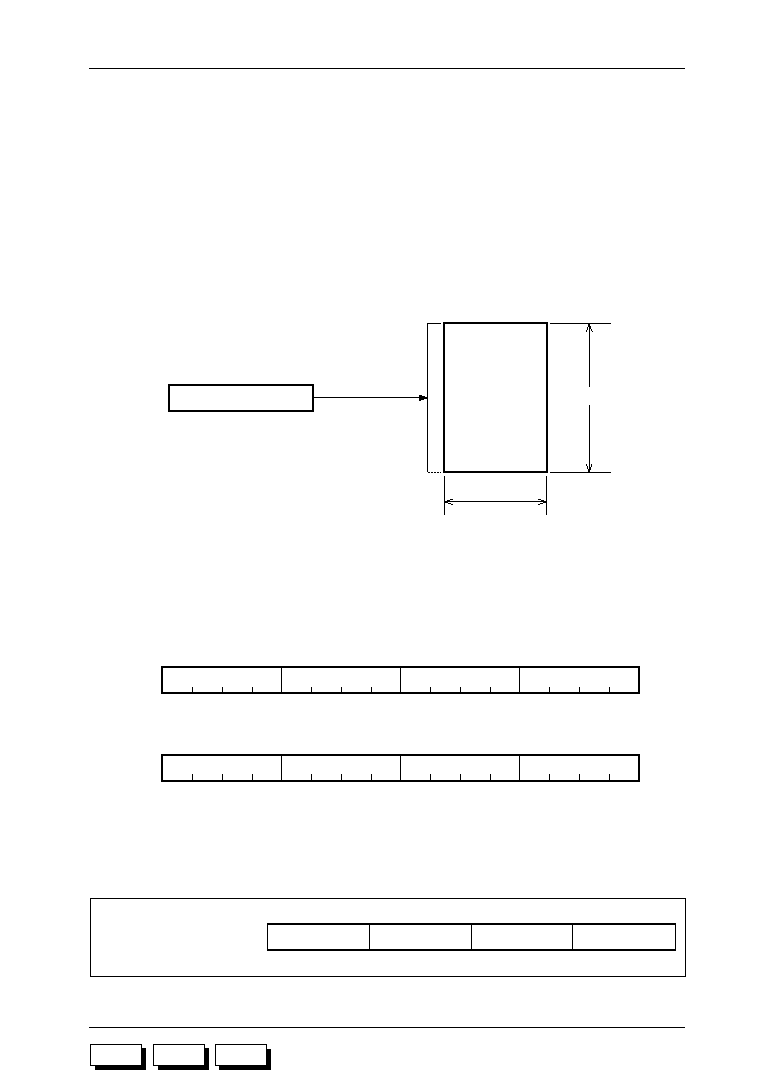

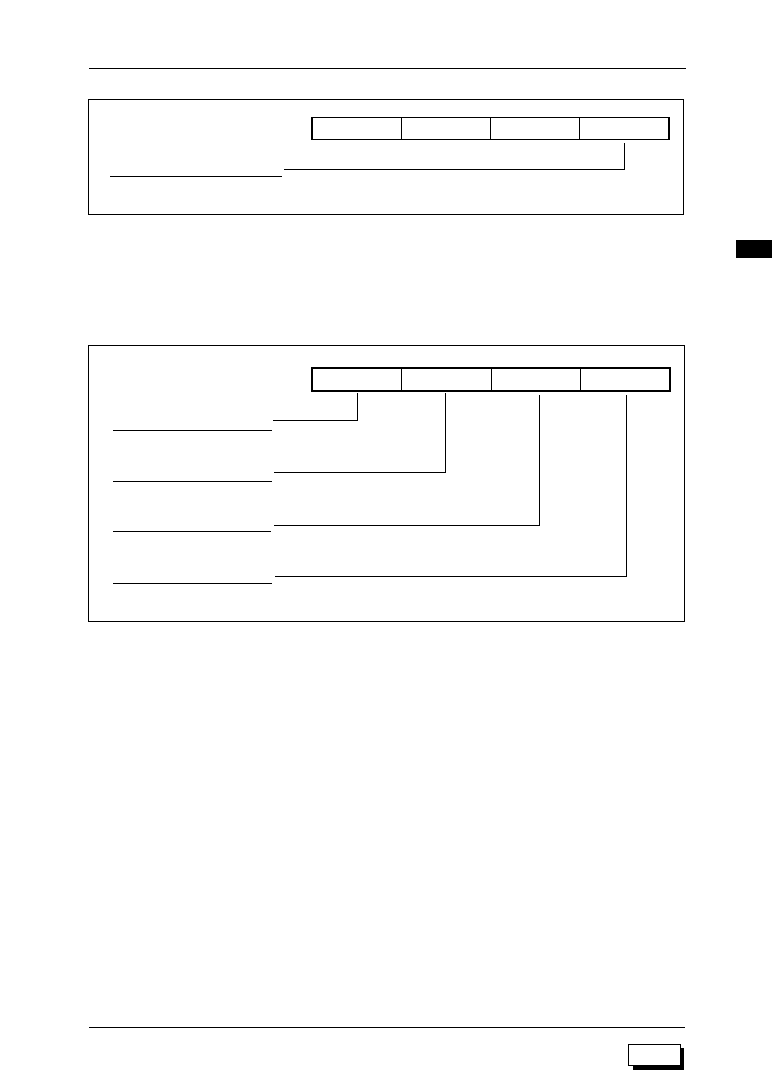

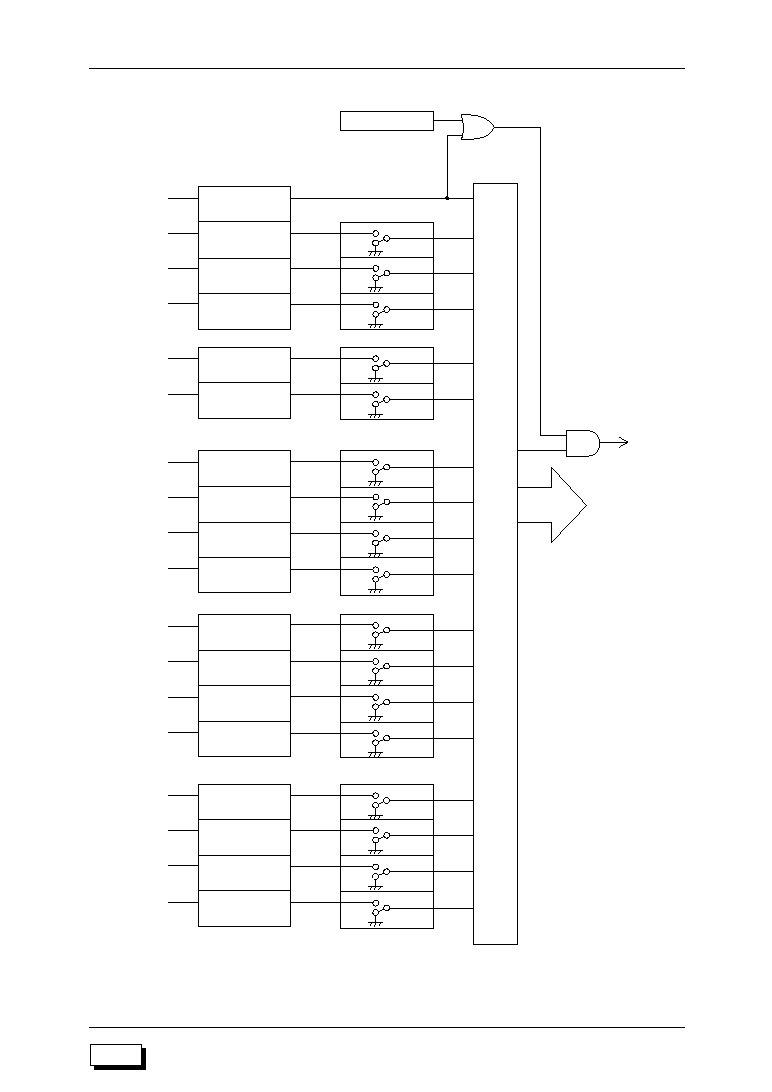

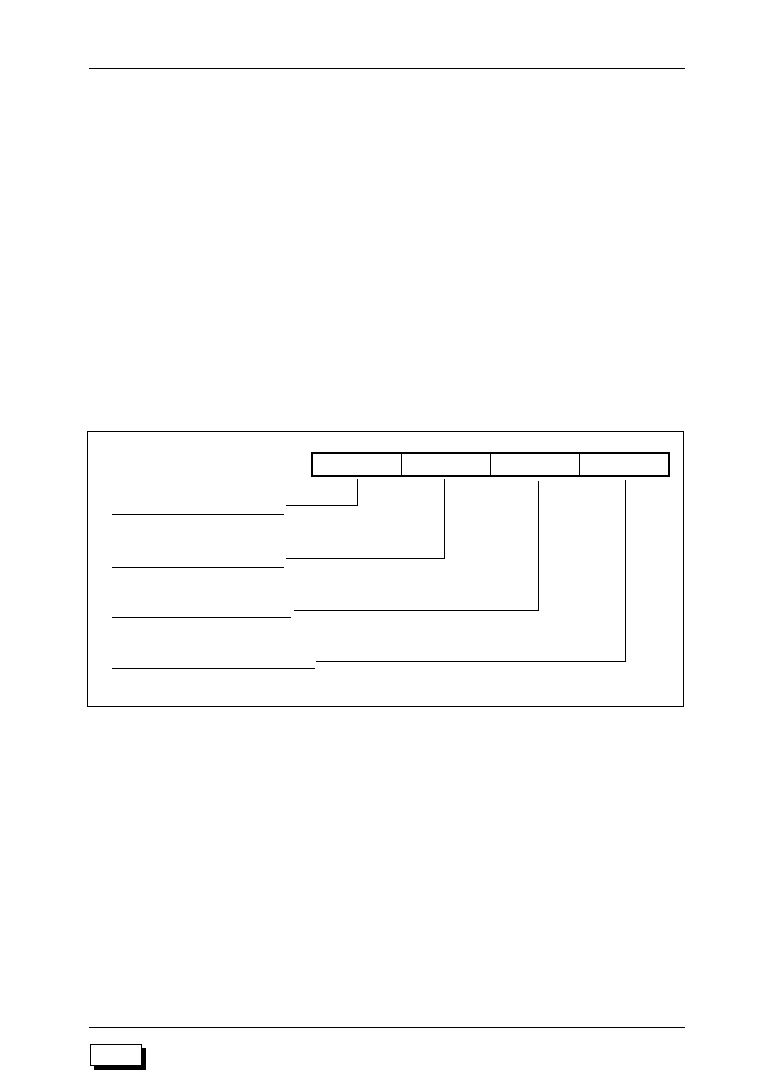

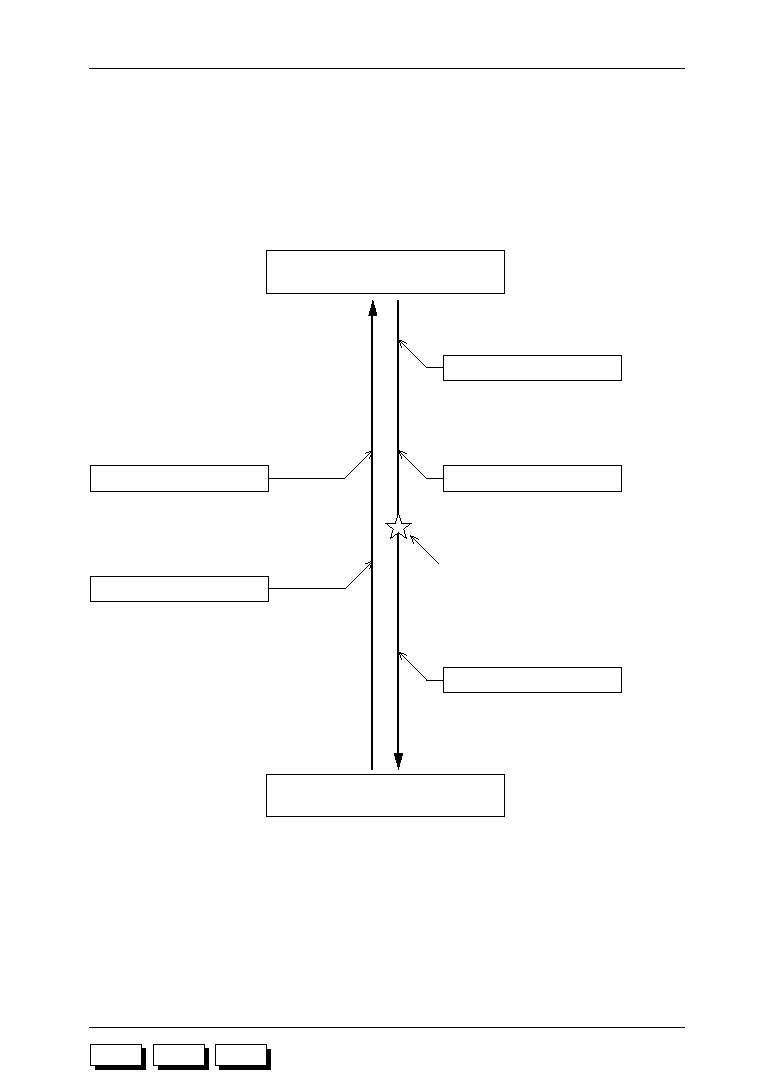

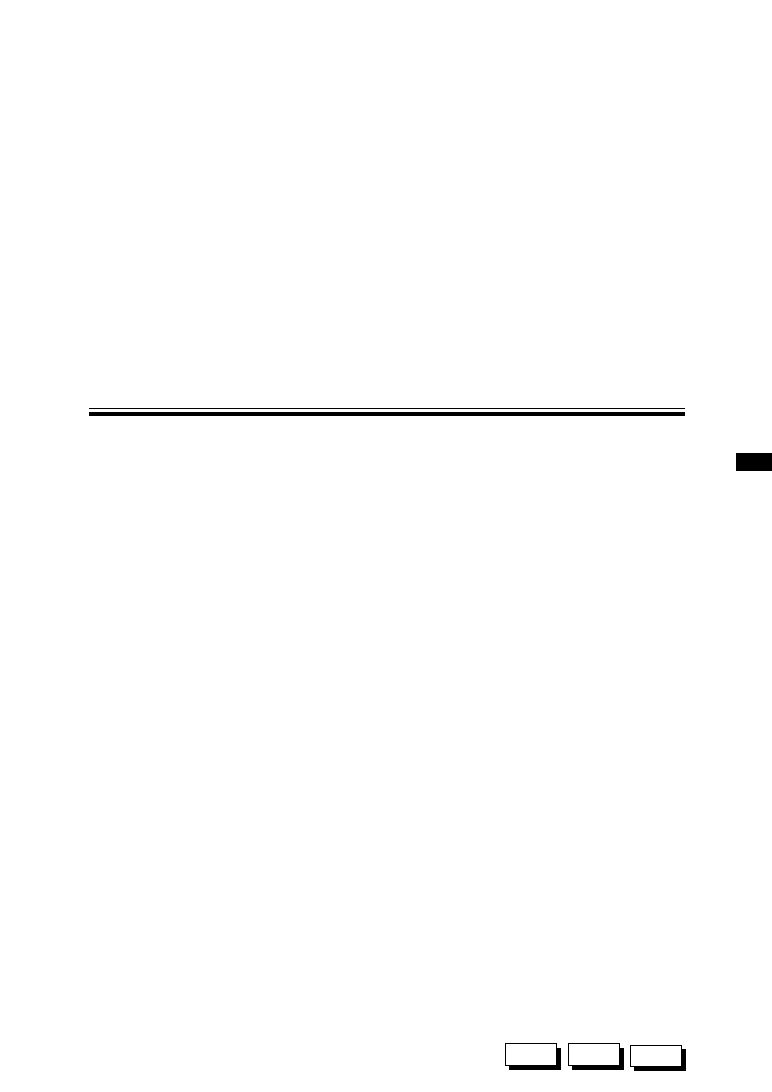

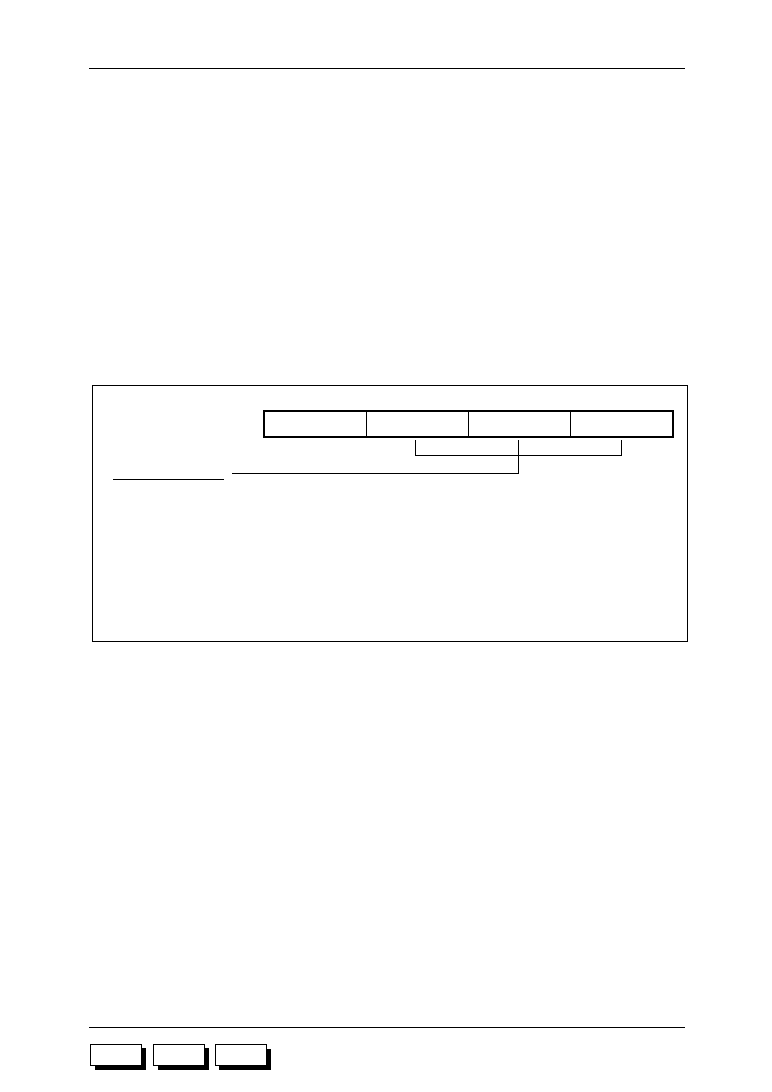

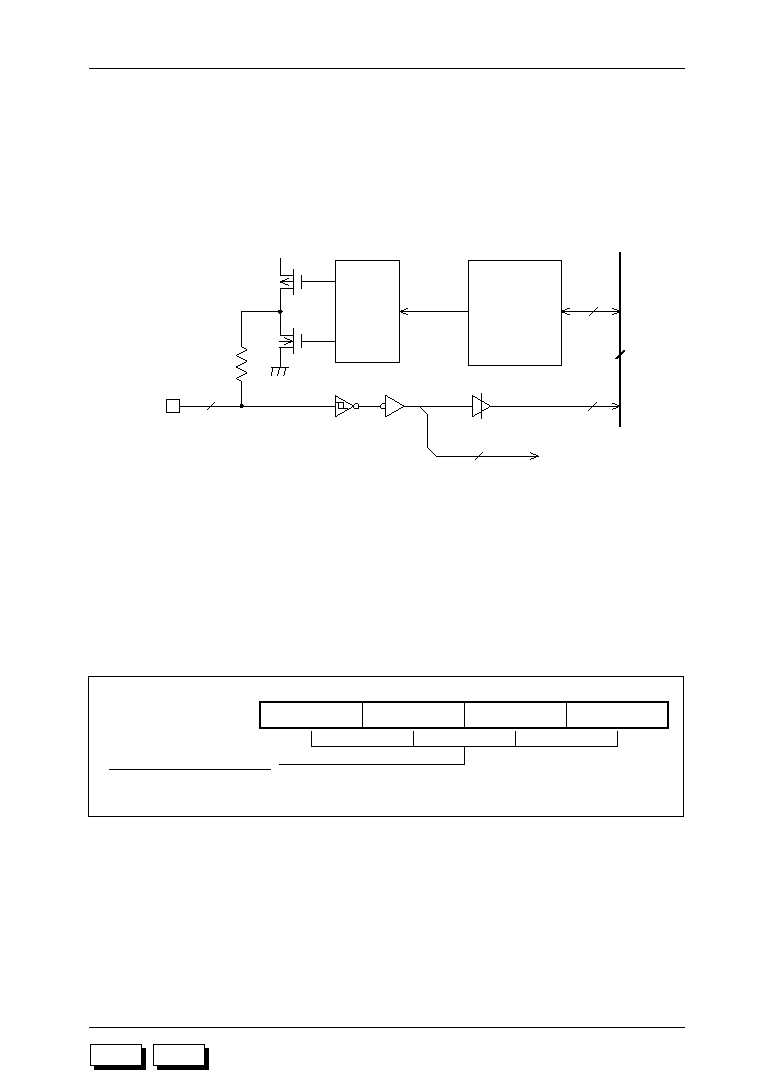

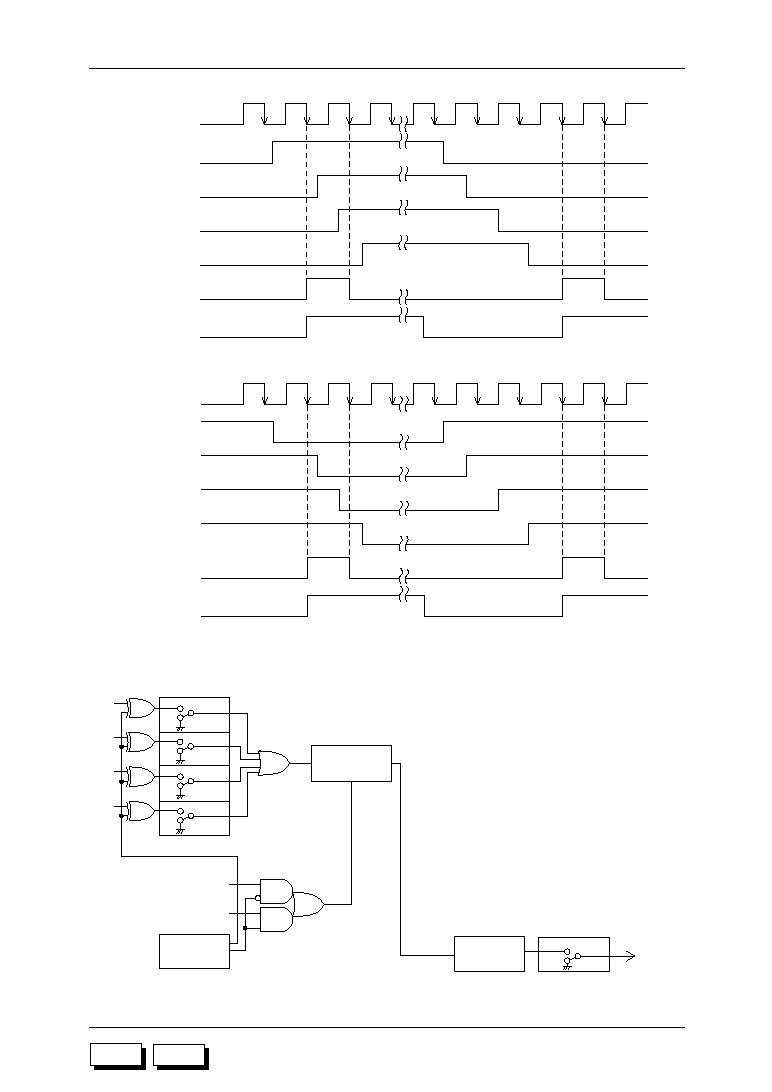

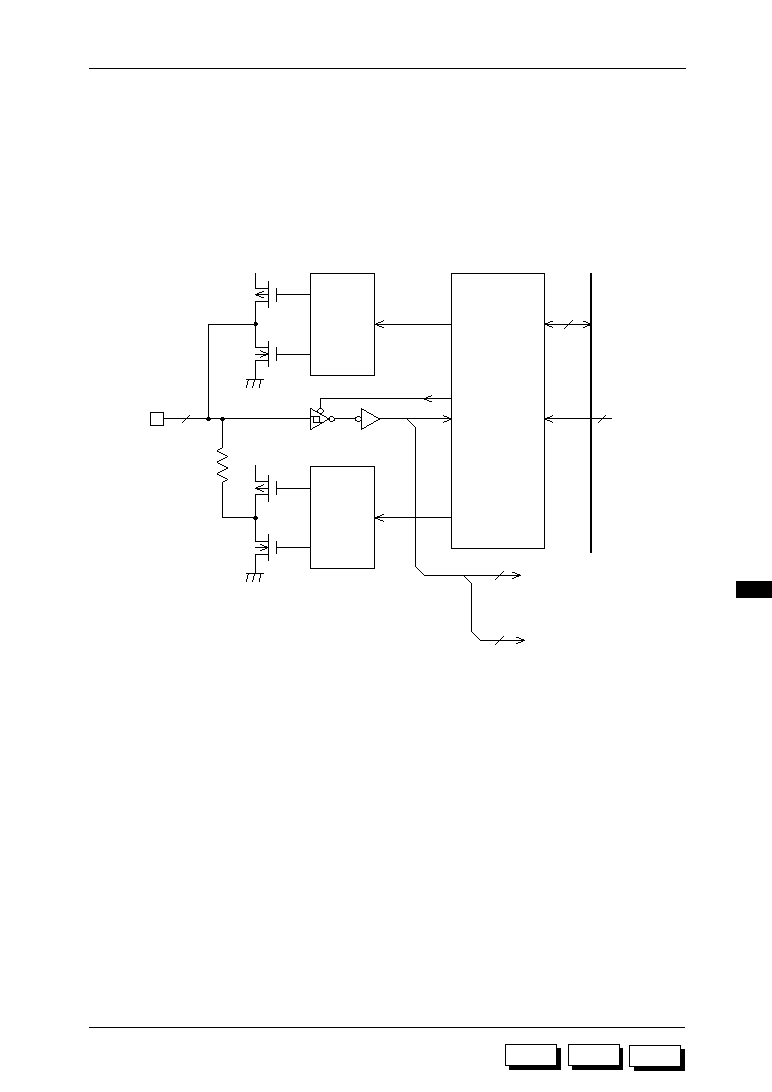

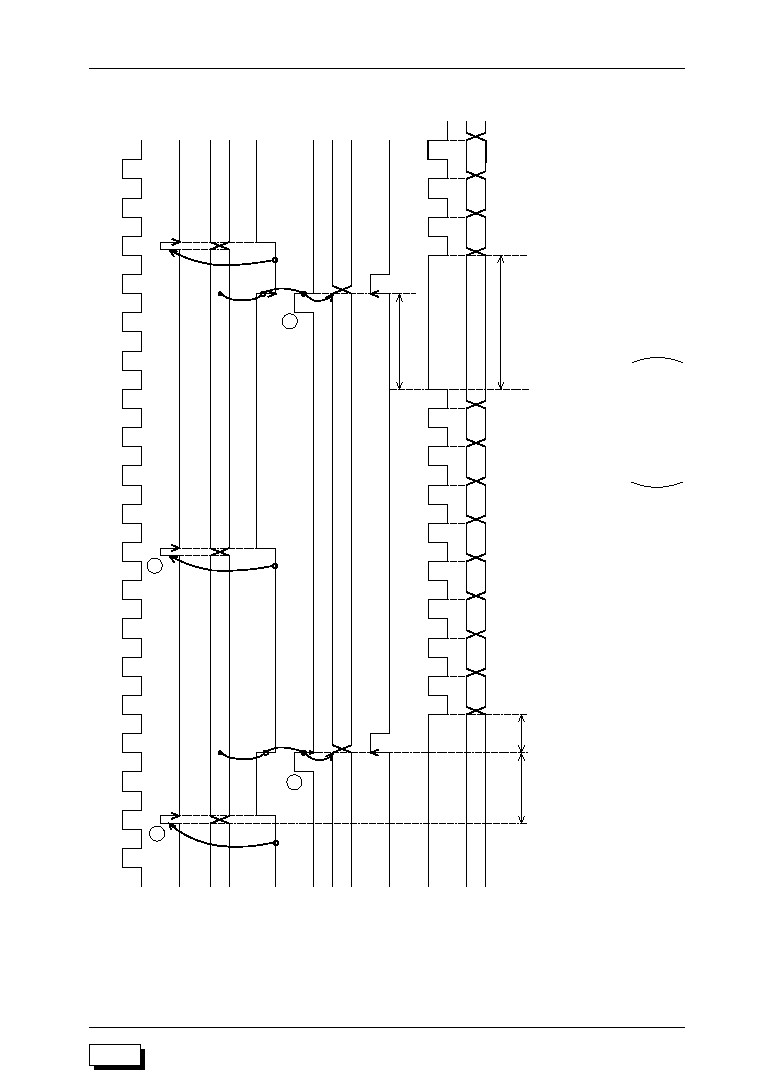

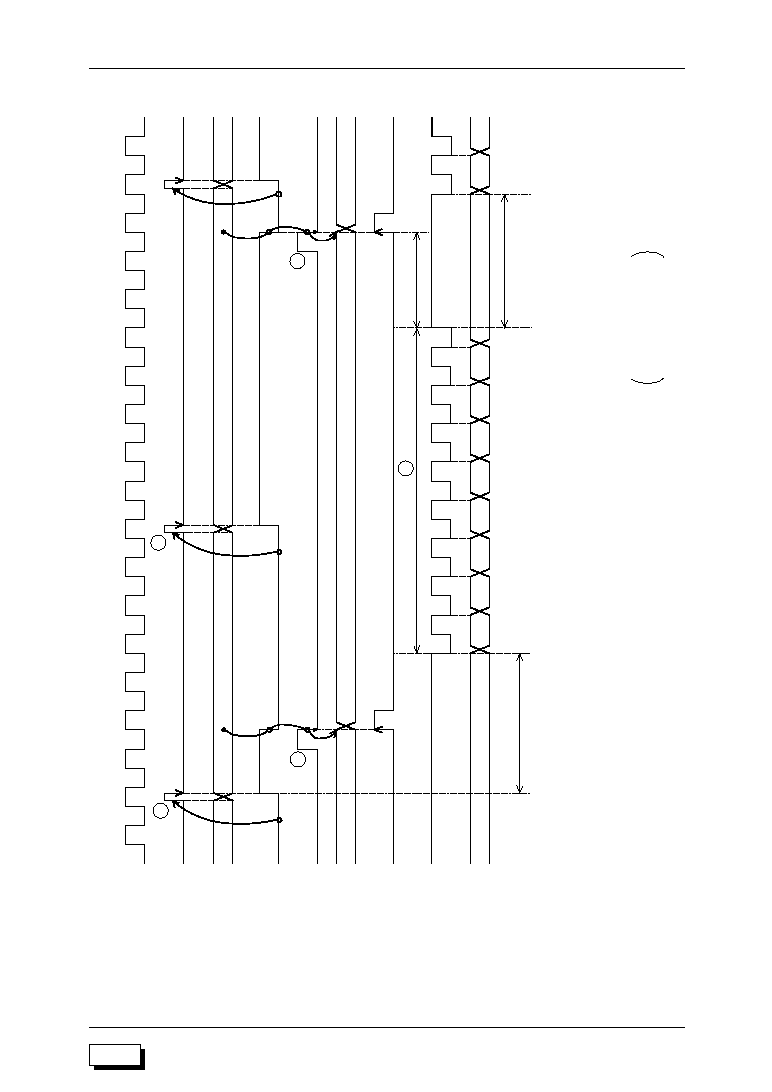

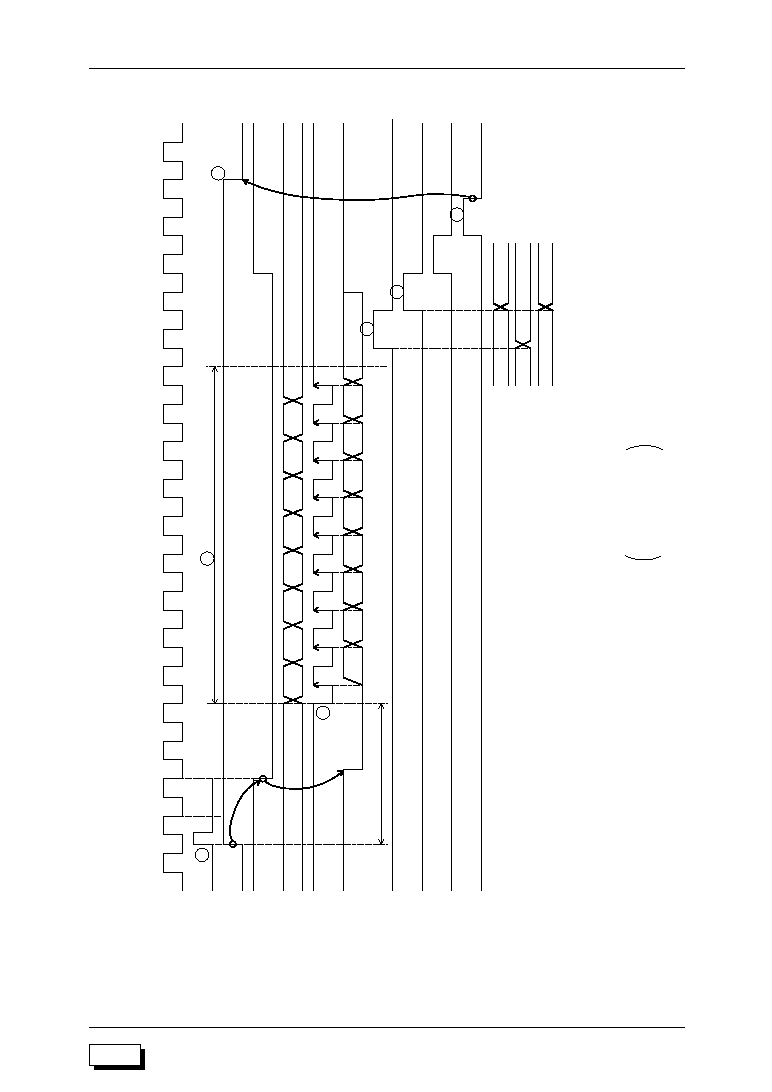

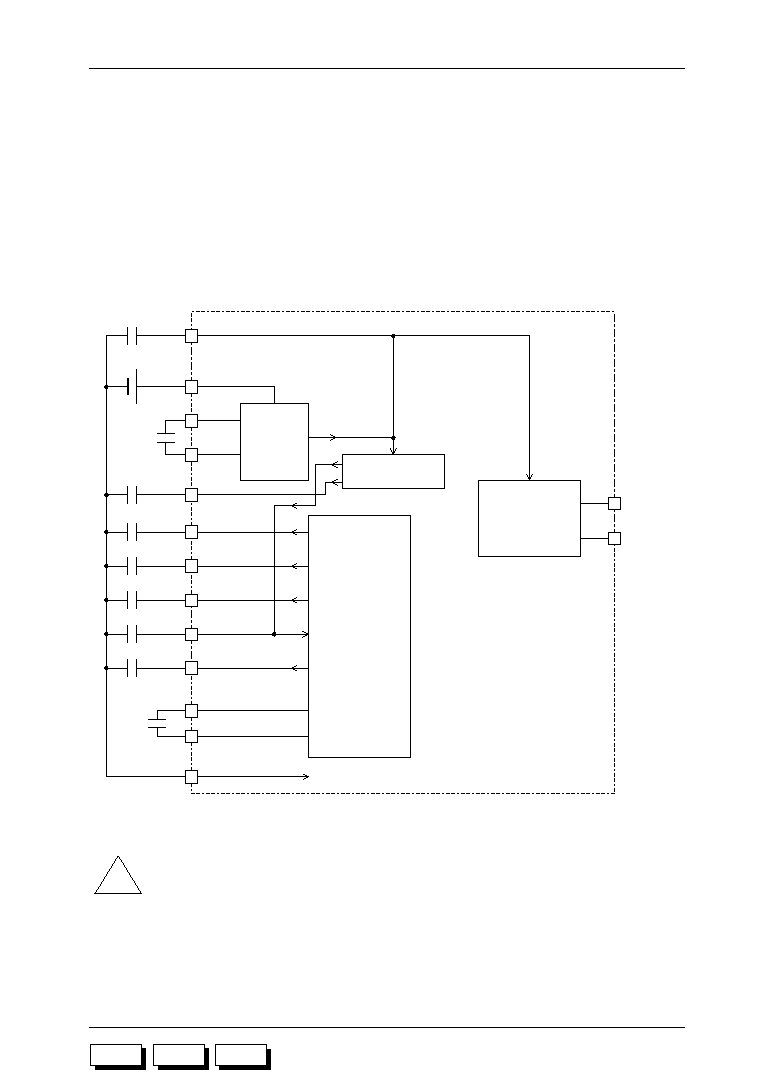

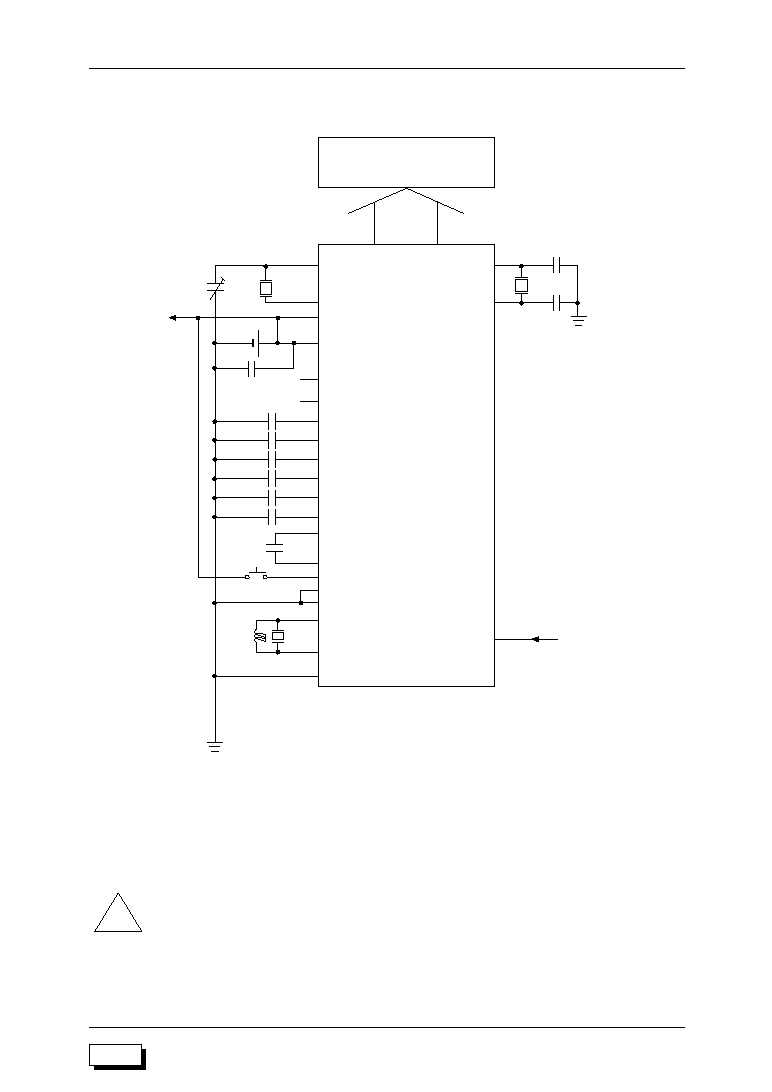

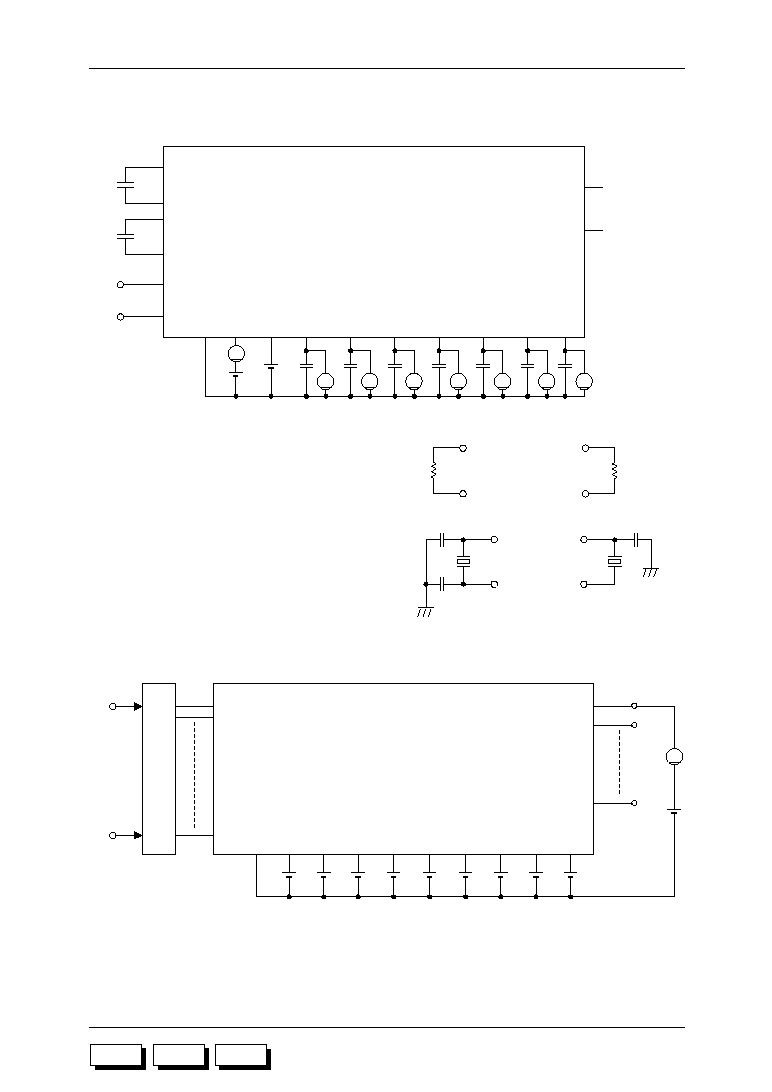

1.4 Block Diagram

Block diagrams of the ML63187, ML63189B, and ML63193 are shown in Figures 1-1, 1-2, and

1-3 respectively.

Asterisks (*) indicate port secondary functions. Signal names enclosed by chain lines (

)

indicate interface signals of the V

DDI

power supply system.

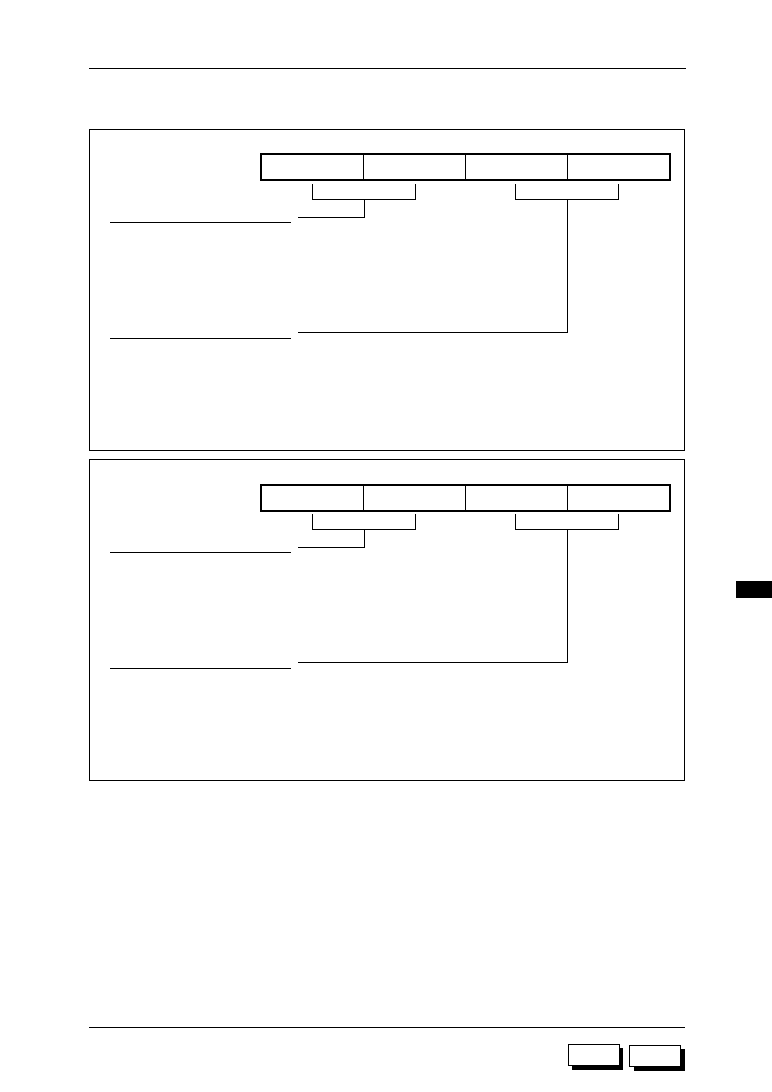

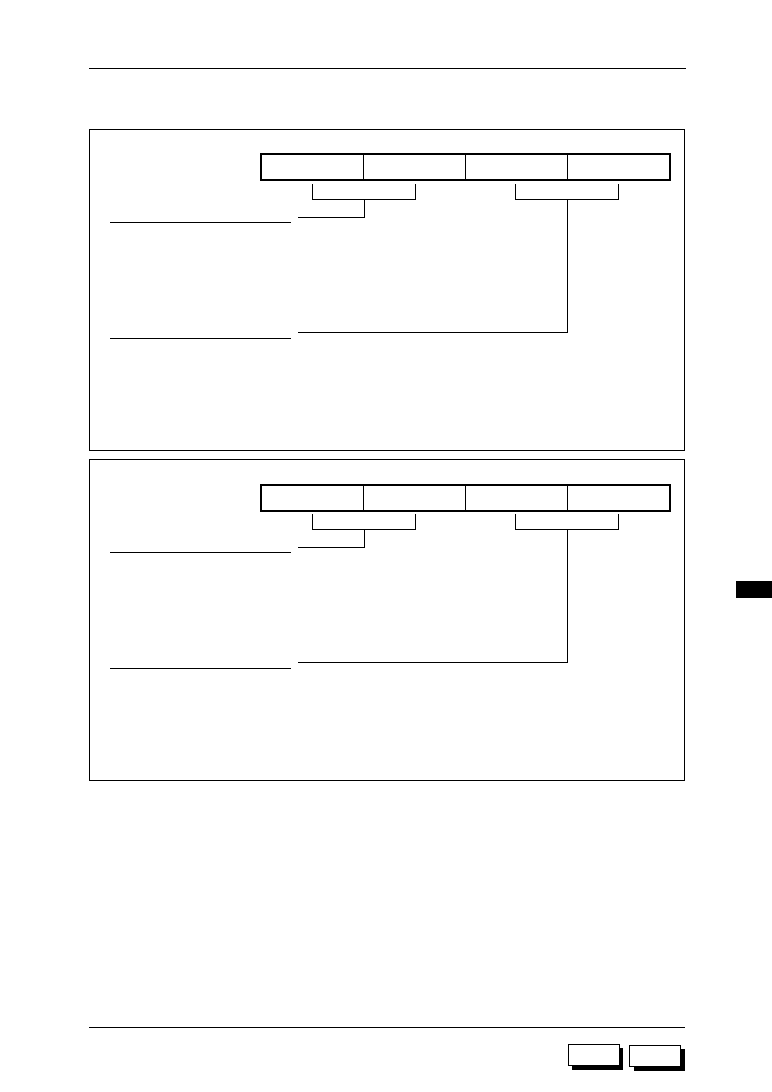

Figure 1-1 ML63187 Block Diagram

ROM

16KW

BUS

CON-

TROL

MIE

XT0

XT1

OSC0

OSC1

OSC

CBR

EBR

L

C

G

Z

ALU

RA

A

IR

INSTRUCTION

DECODER

RAM

1024N

nX-4/250

RESET

RST

V

DDI

PC

H

Y

X

TIMING

CON-

TROL

SP

RSP

STACK

CAL.S : 16 levels

REG.S : 16 levels

TIMER

8 bits

• 4

SCLK*

SIN*

SOUT*

4

INT

SFT

TM0CAP/TM1CAP*

TM0OVF/TM1OVF*

T02CK*

T13CK*

1

INT

I/O

PORT

PB.0≠PB.3

PE.0≠PE.3

2

INT

V

DDH

V

DD

CB1

CB2

DATA BUS

TBC

4

INT

BLD

INT

100HzTC

1

BACK-

UP

V

SS

MELODY

MD

1

INT

MDB

LCD

&

DSPR

COM1≠16

SEG0≠63

TST1

TST

TST2

INT

WDT

1

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDL

BIAS

INT187

CPU CORE

1-7

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

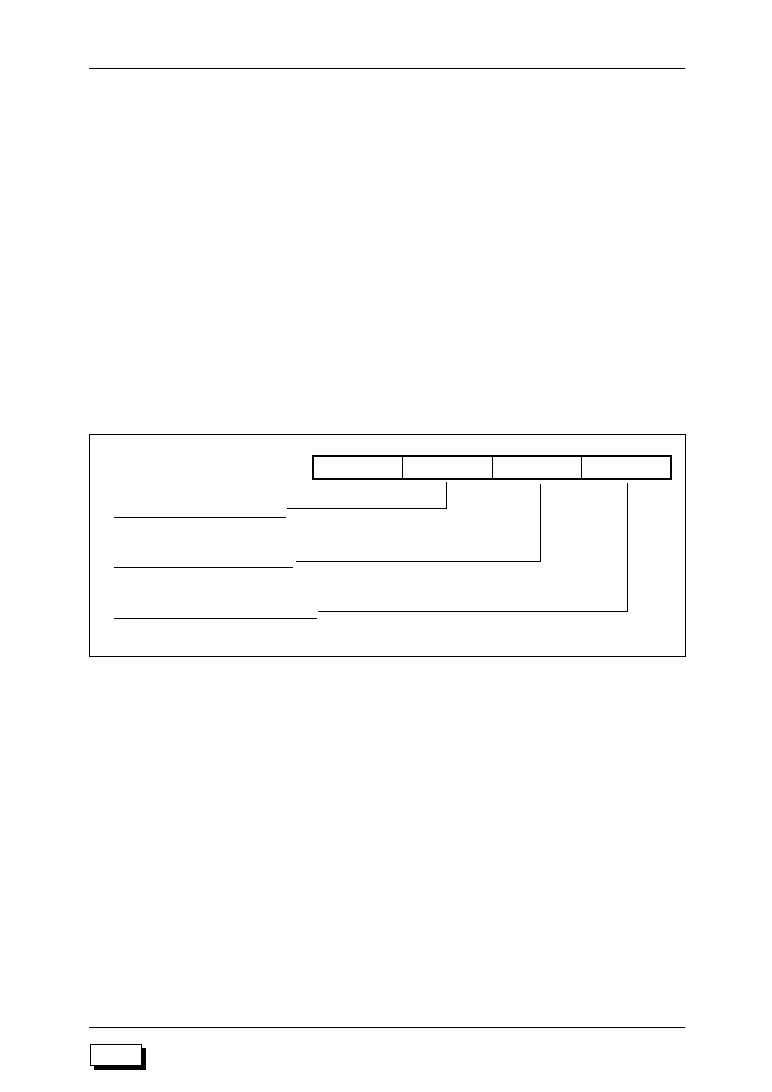

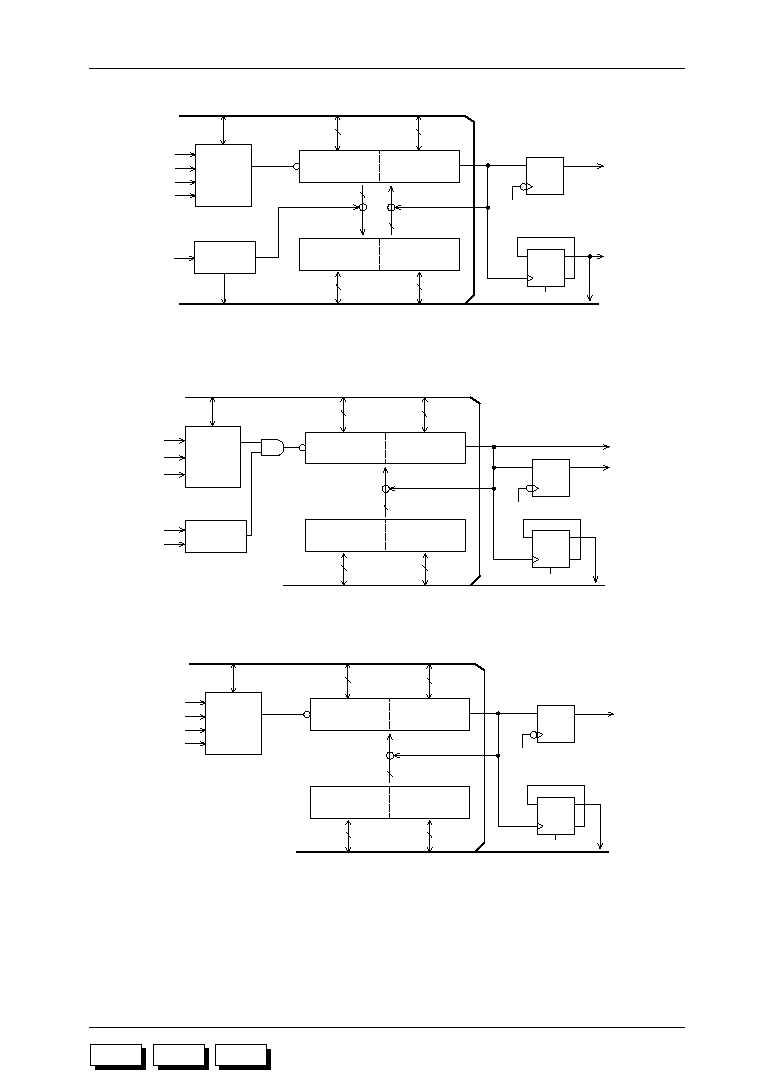

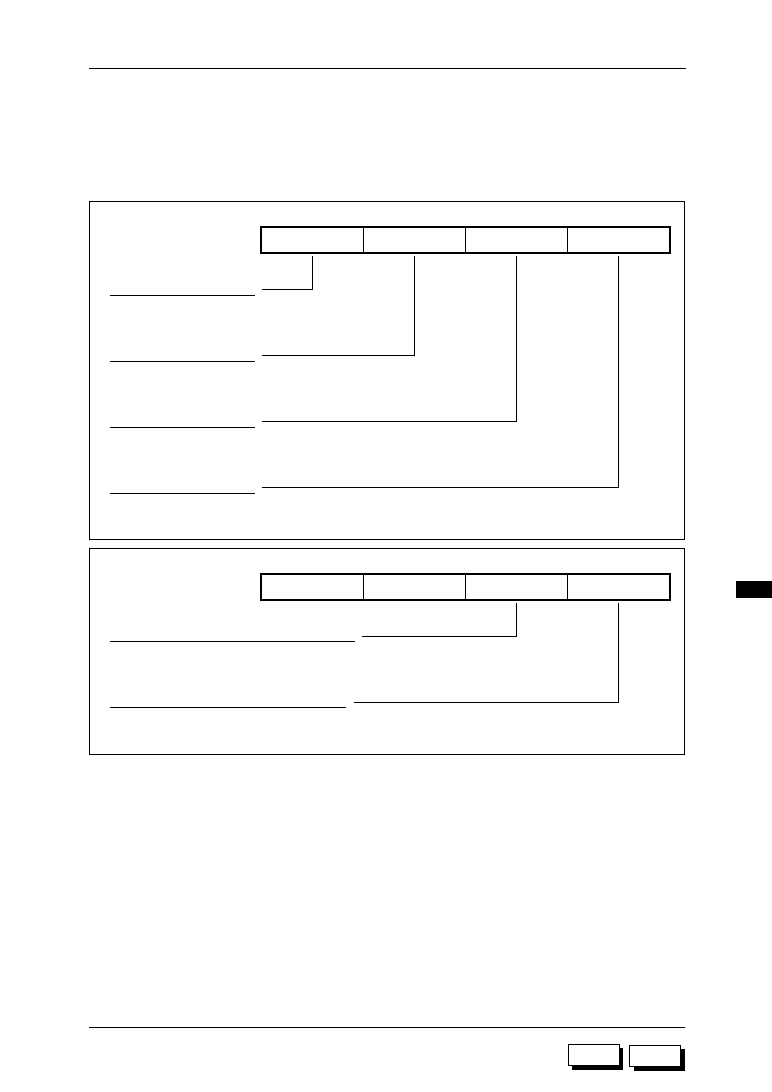

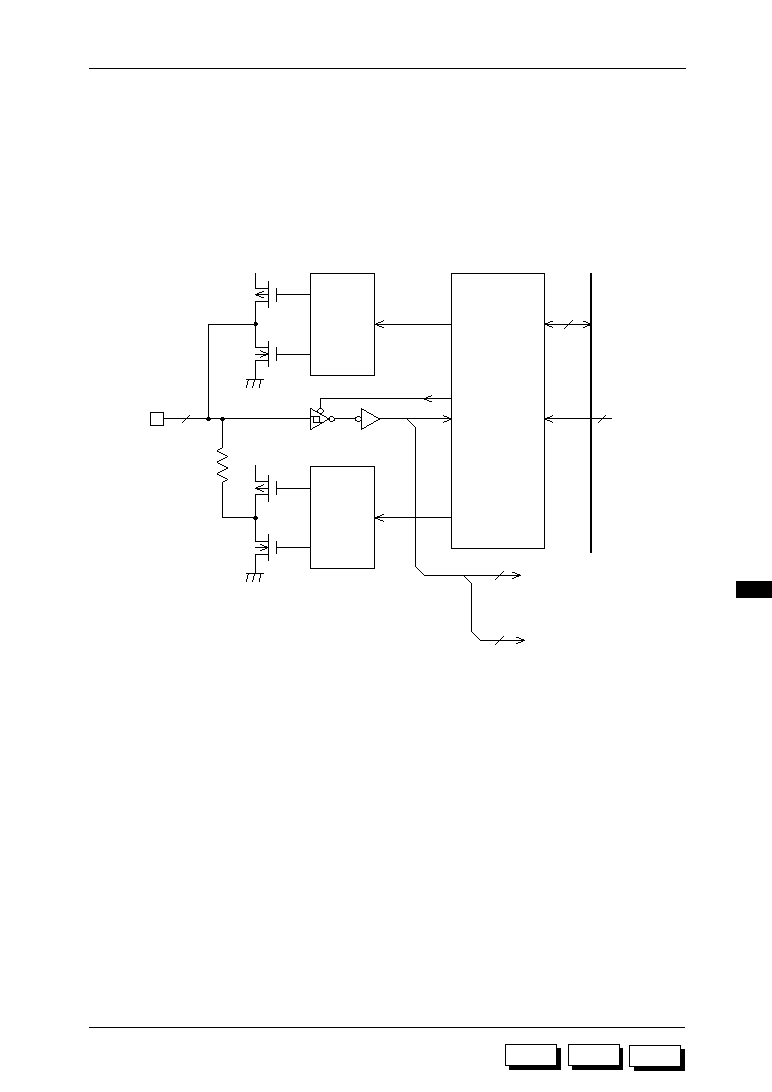

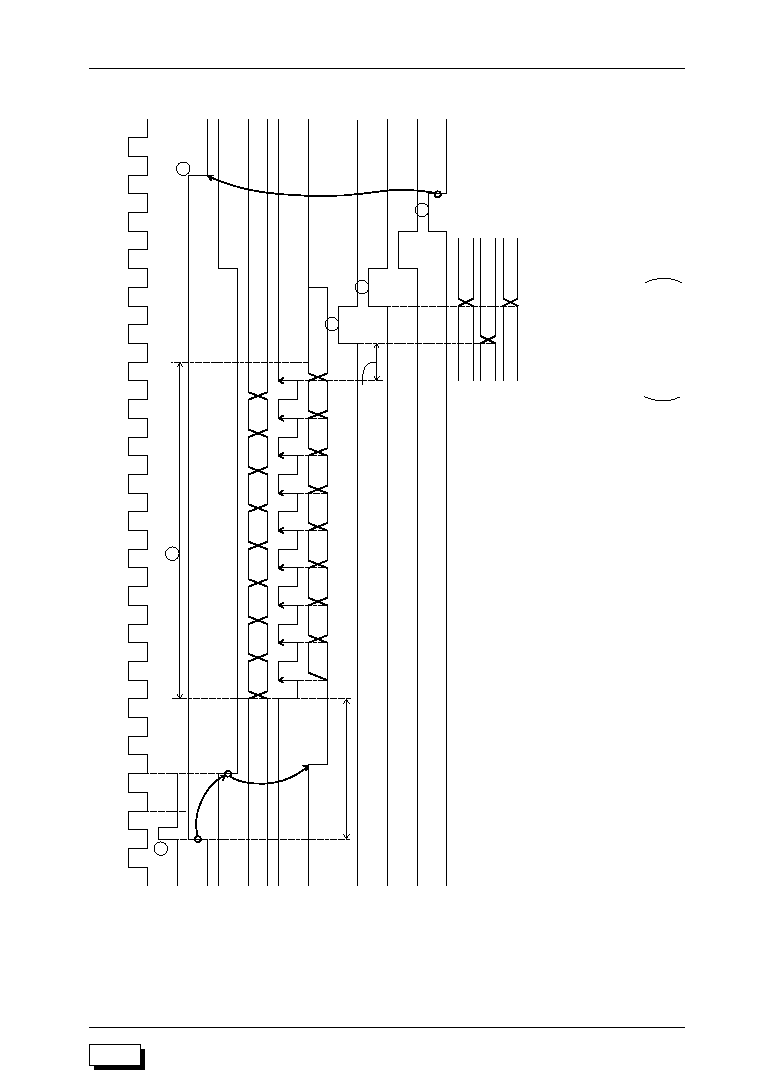

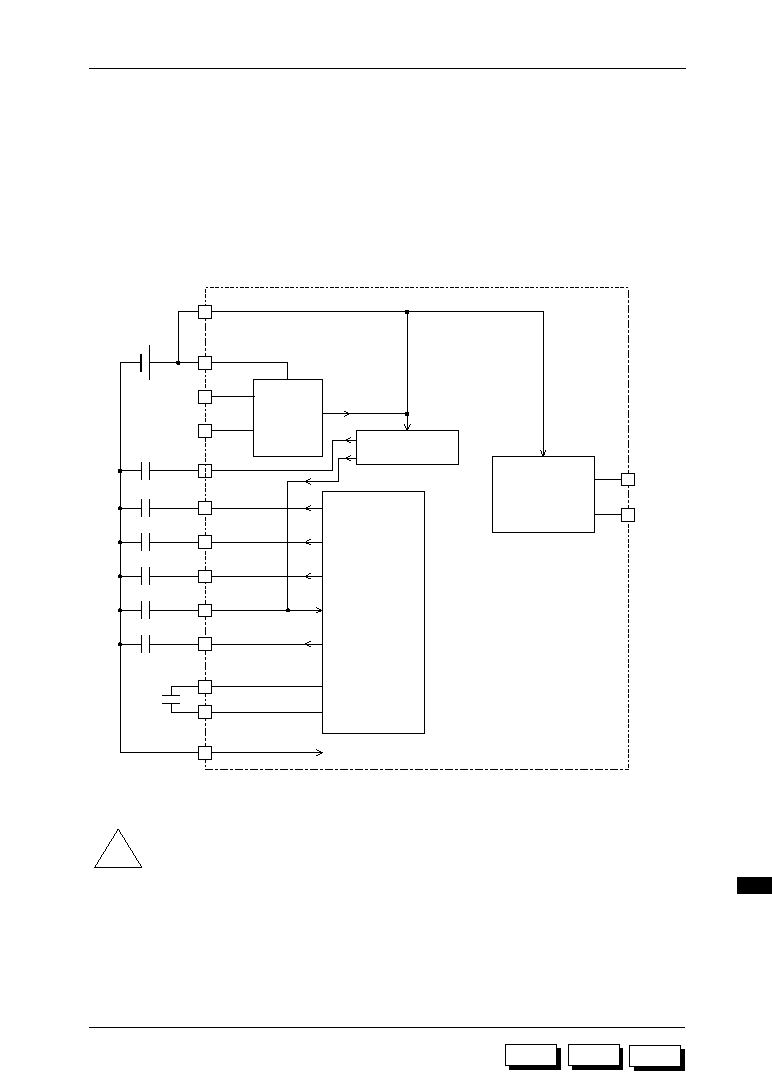

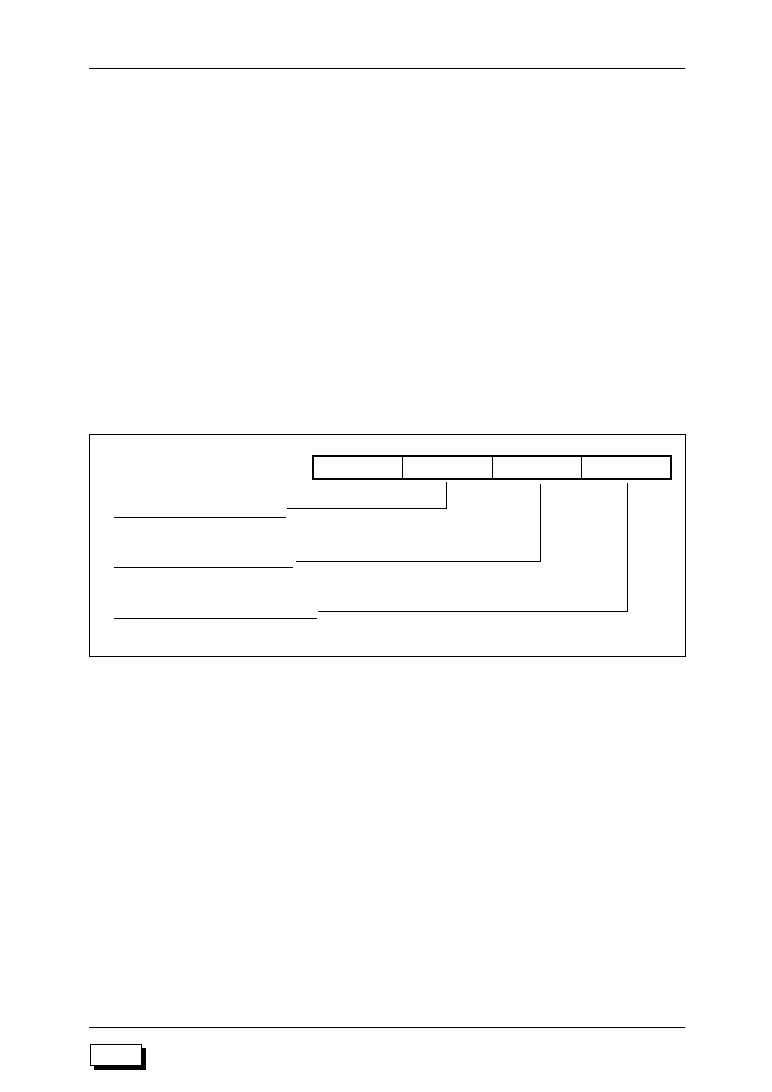

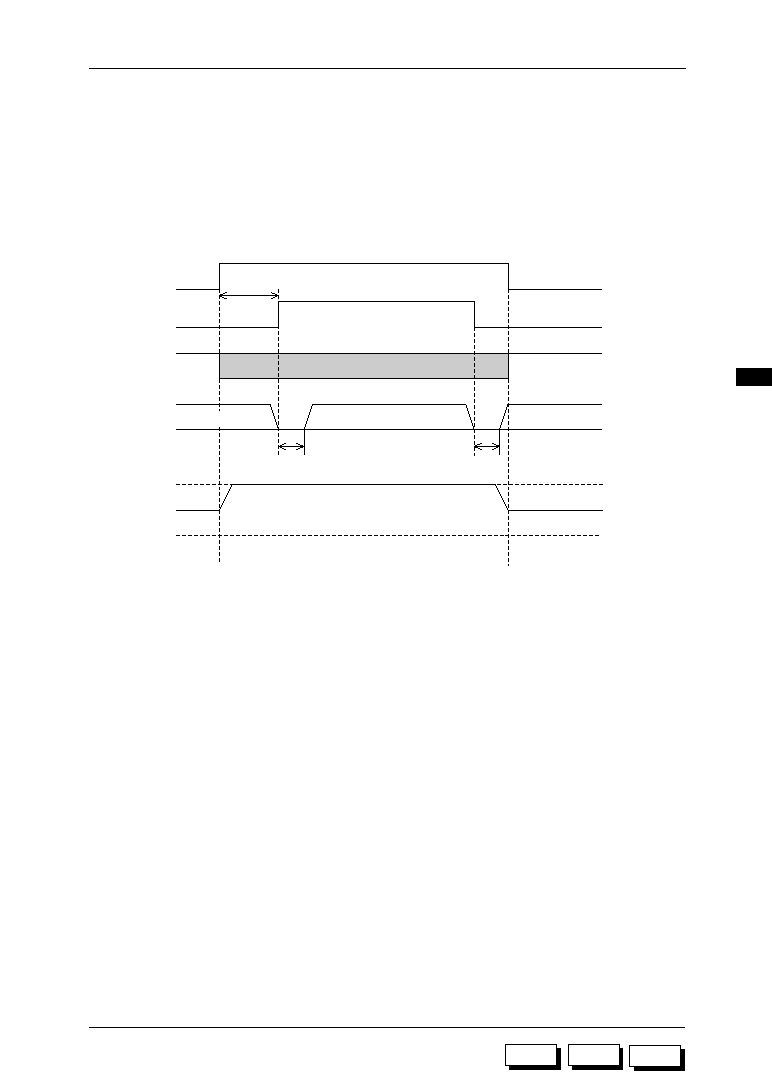

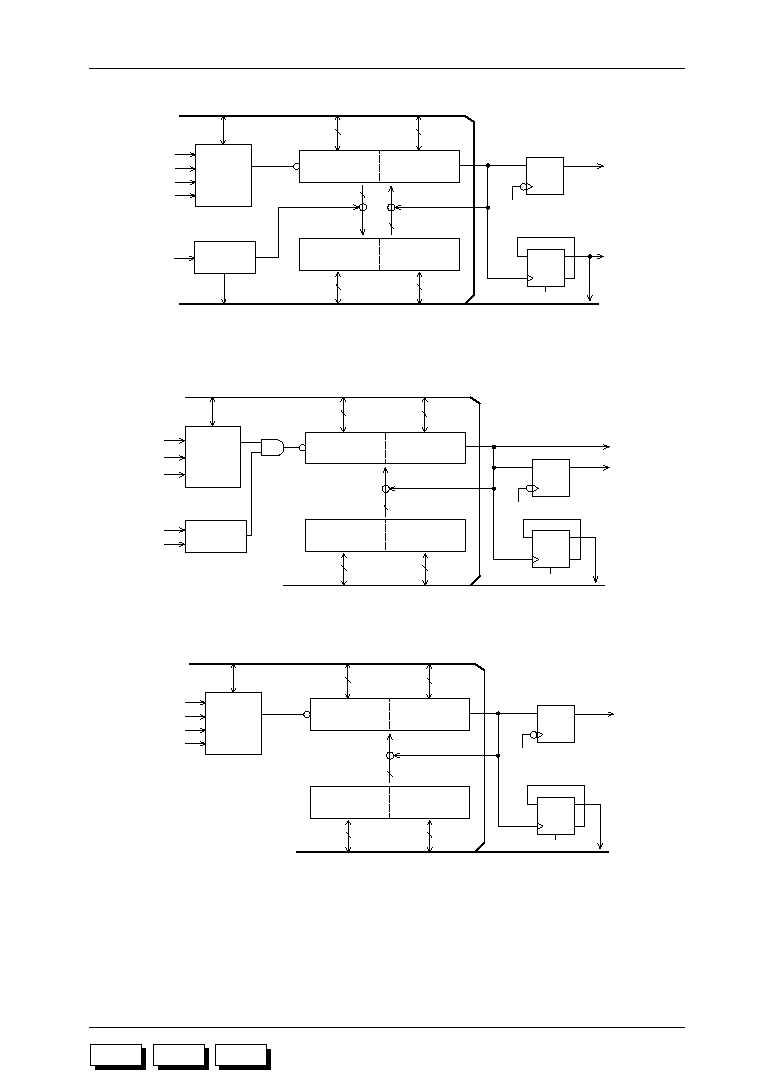

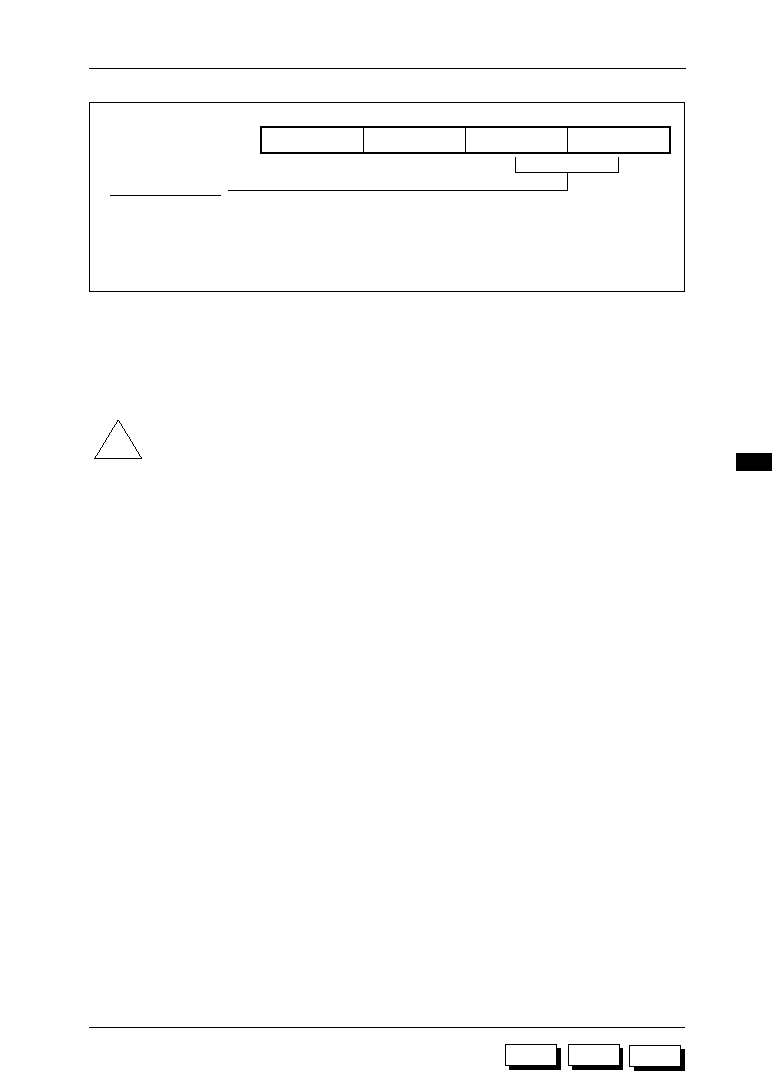

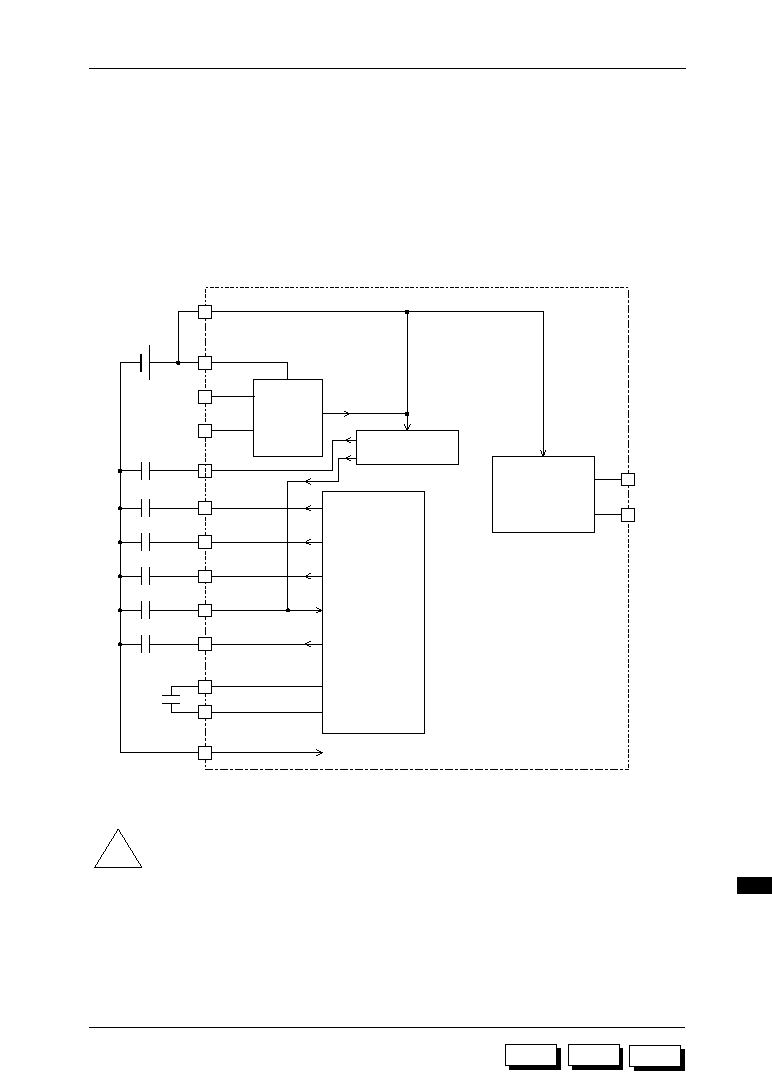

Asterisks (*) indicate port secondary functions. Signal names enclosed by chain lines (

)

indicate interface signals of the V

DDI

power supply system.

XT0

XT1

OSC0

OSC1

OSC

RAM

1536N

RESET

RST

V

DDI

TIMER

8 bits

• 4

SCLK*

SIN*

SOUT*

4

INT

SFT

TM0CAP/TM1CAP*

TM0OVF/TM1OVF*

T02CK*

T13CK*

1

INT

I/O

PORT

P9.0≠P9.3

PA.0≠PA.3

PB.0≠PB.3

PE.0≠PE.3

2

INT

V

DDH

V

DD

CB1

CB2

DATA BUS

TBC

4

INT

BLD

INT

100HzTC

1

BACK-

UP

V

SS

MELODY

MD

1

INT

MDB

1

INT

INPUT

PORT

P0.0≠P0.3

LCD

&

DSPR

COM1≠16

SEG0≠63

TST1

TST

TST2

INT

WDT

1

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDL

BIAS

INT189

ROM

32KW

BUS

CON-

TROL

MIE

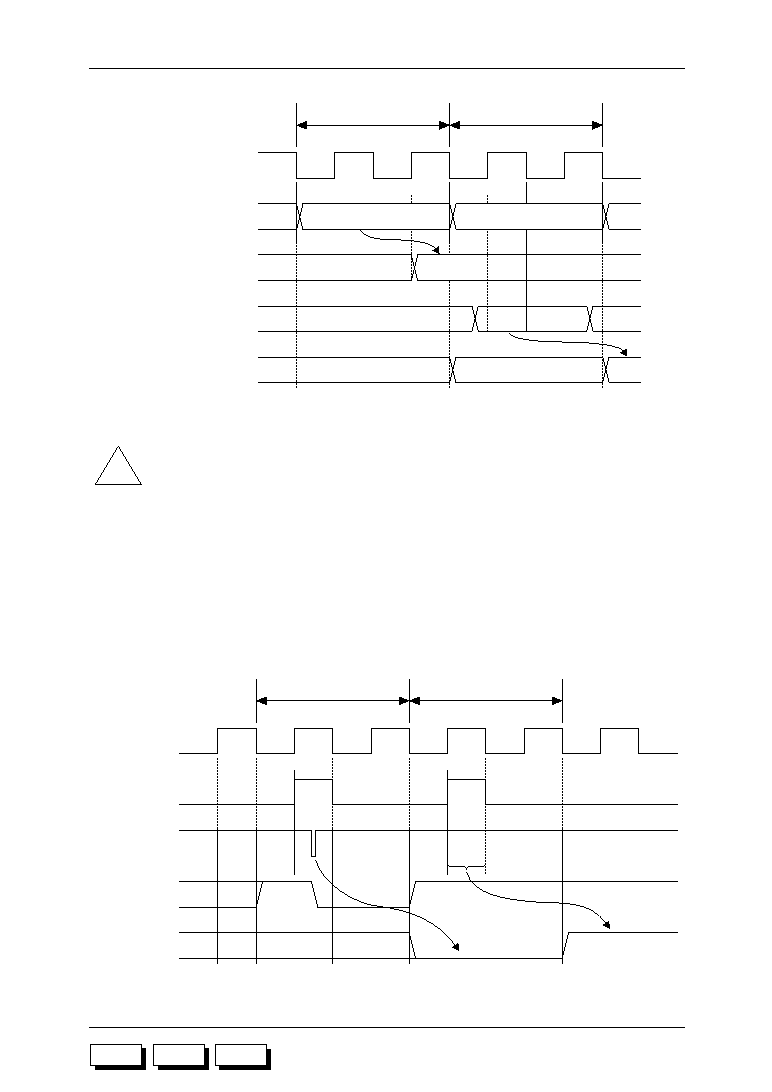

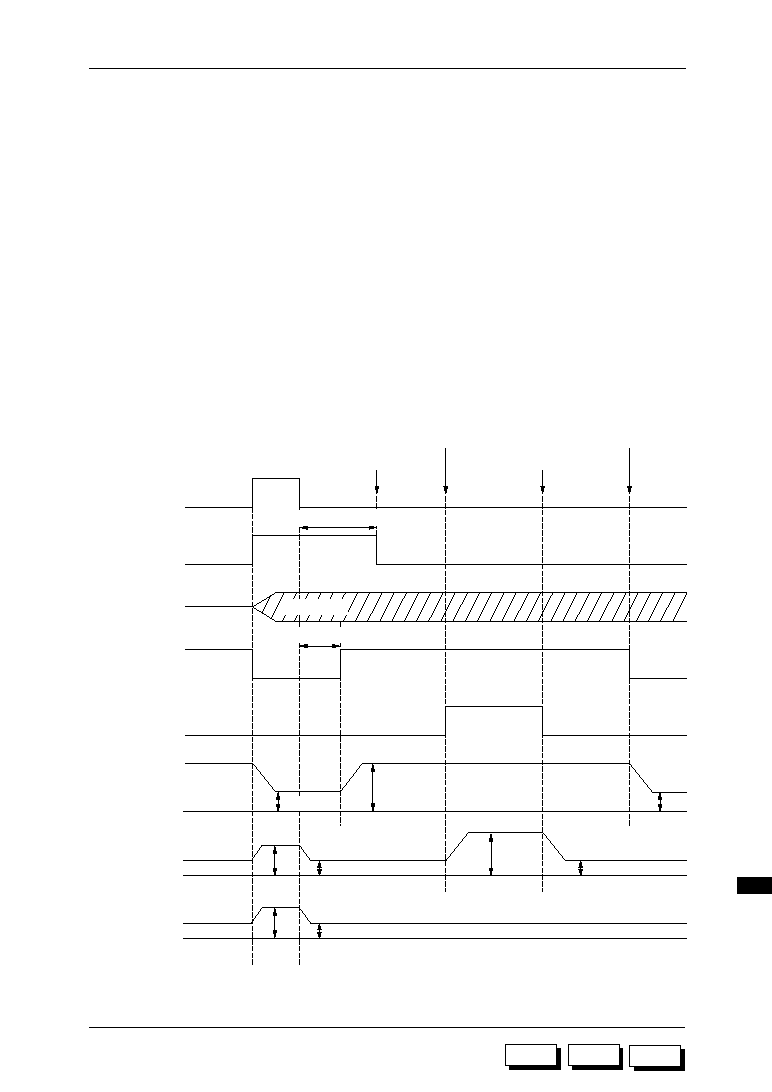

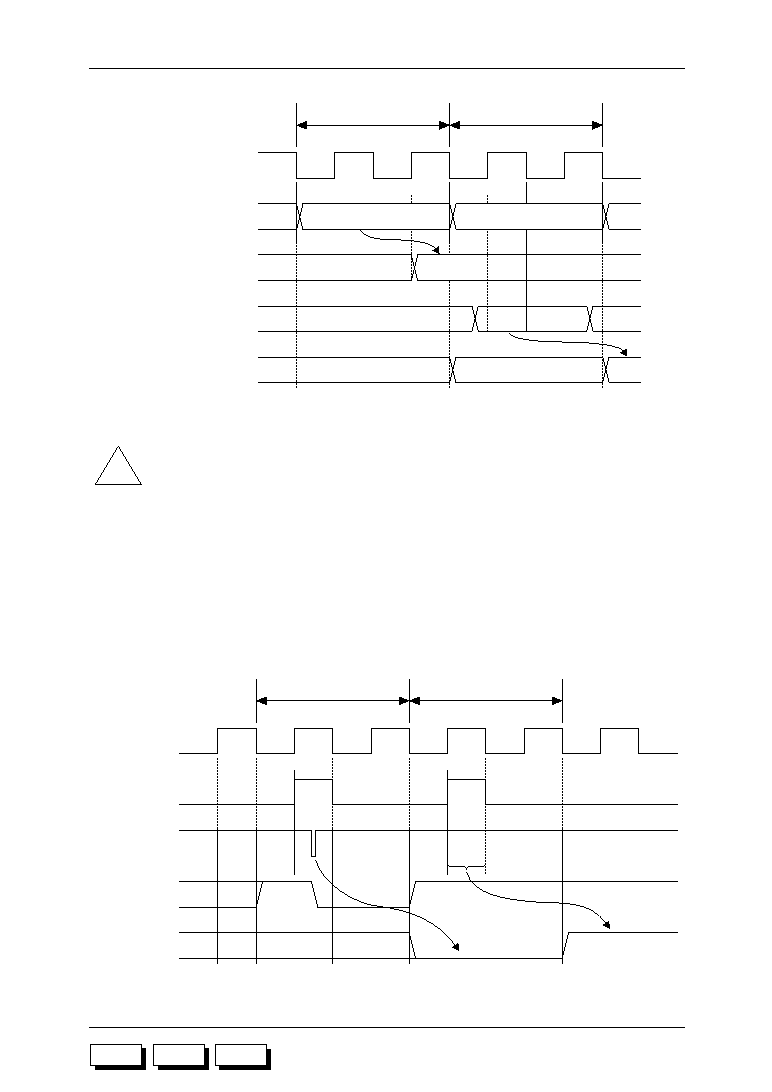

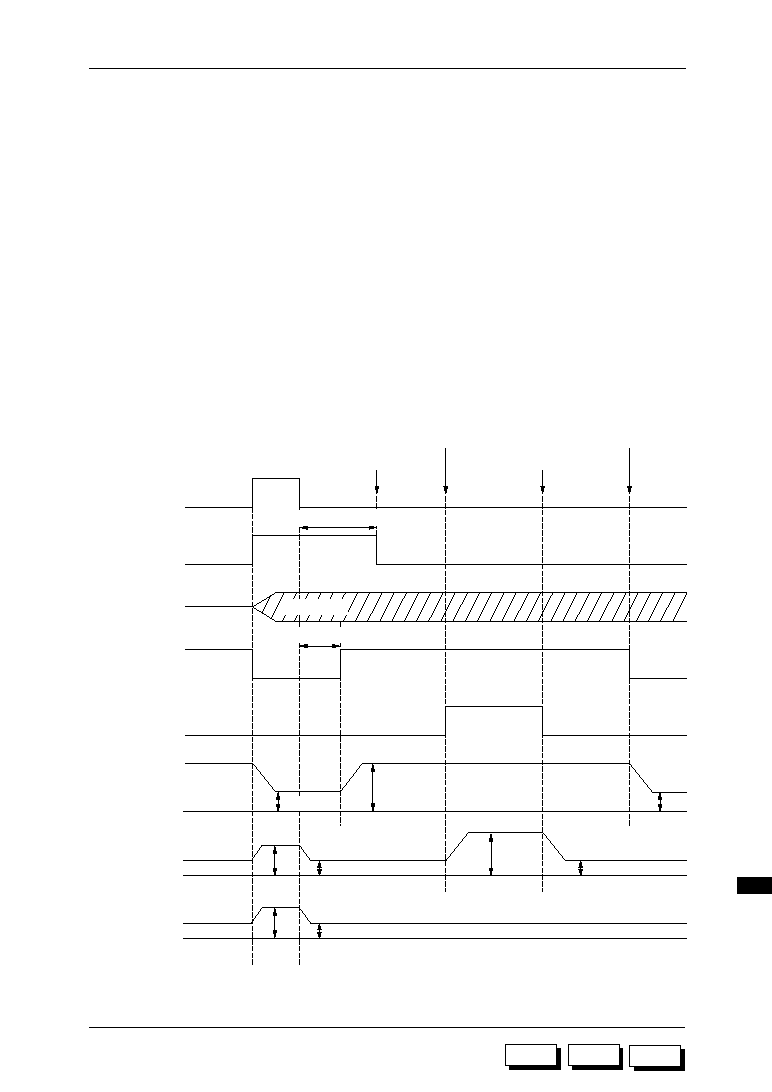

CBR

EBR

L

C

G

Z

ALU

RA

A

IR

INSTRUCTION

DECODER

nX-4/250

PC

H

Y

X

TIMING

CON-

TROL

SP

RSP

STACK

CAL.S : 16 levels

REG.S : 16 levels

CPU CORE

Figure 1-2 ML63189B Block Diagram

M189B

1-8

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

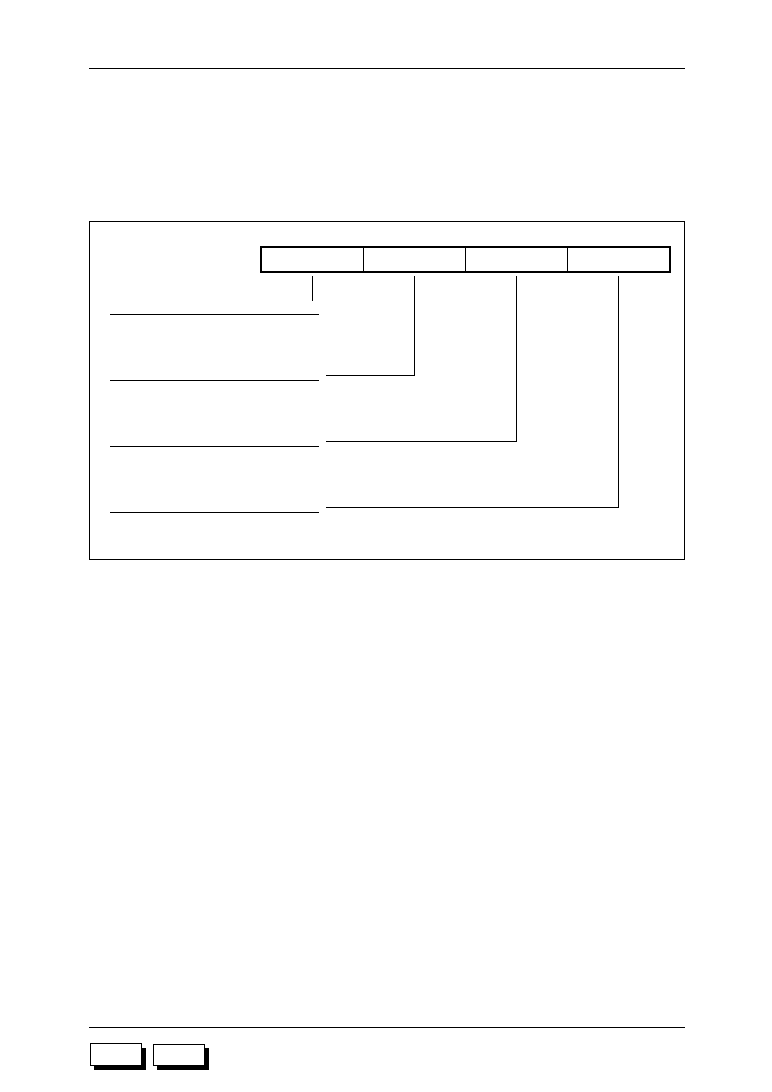

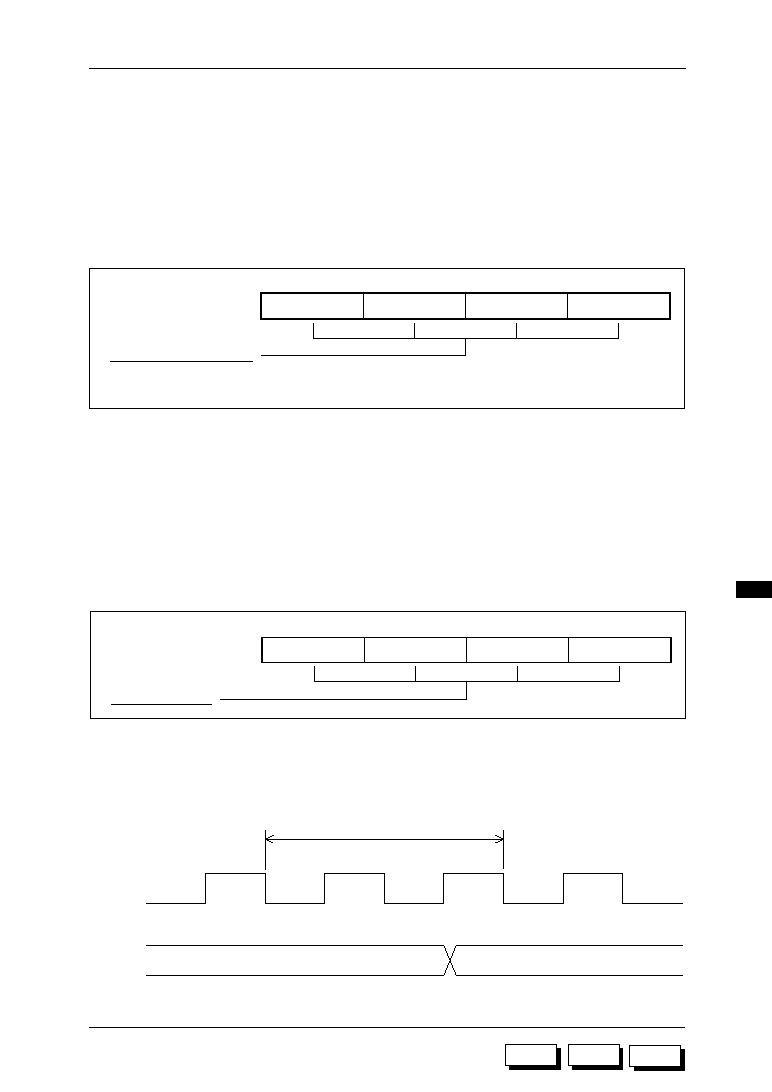

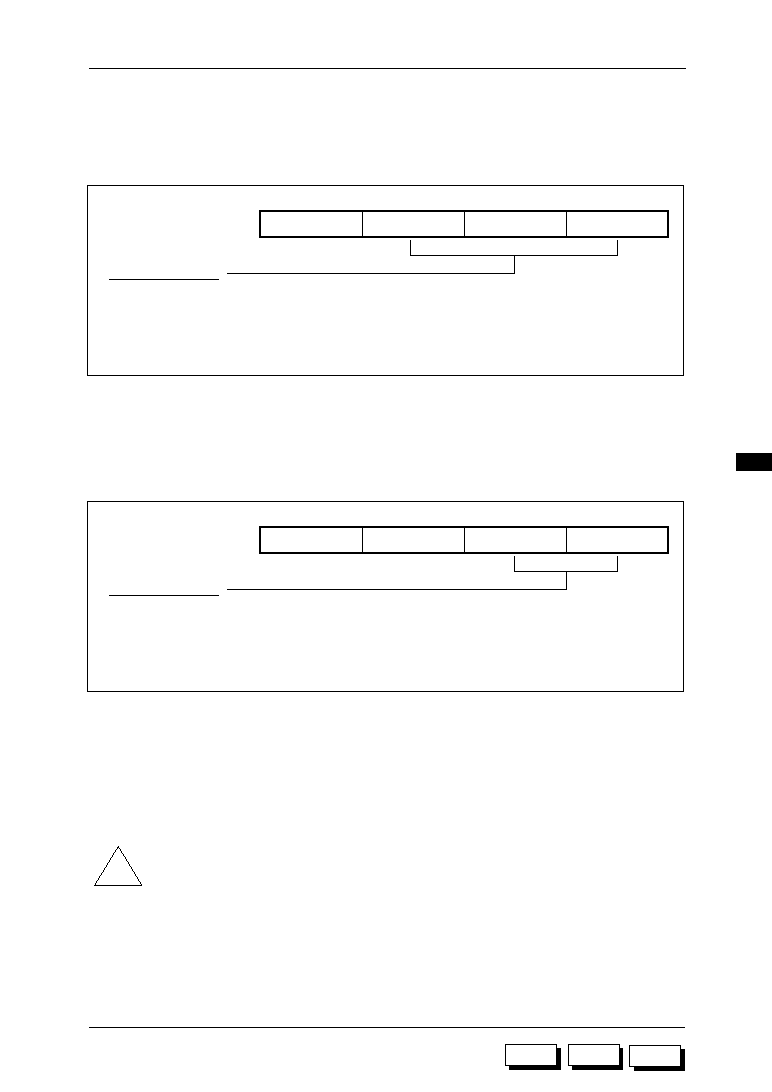

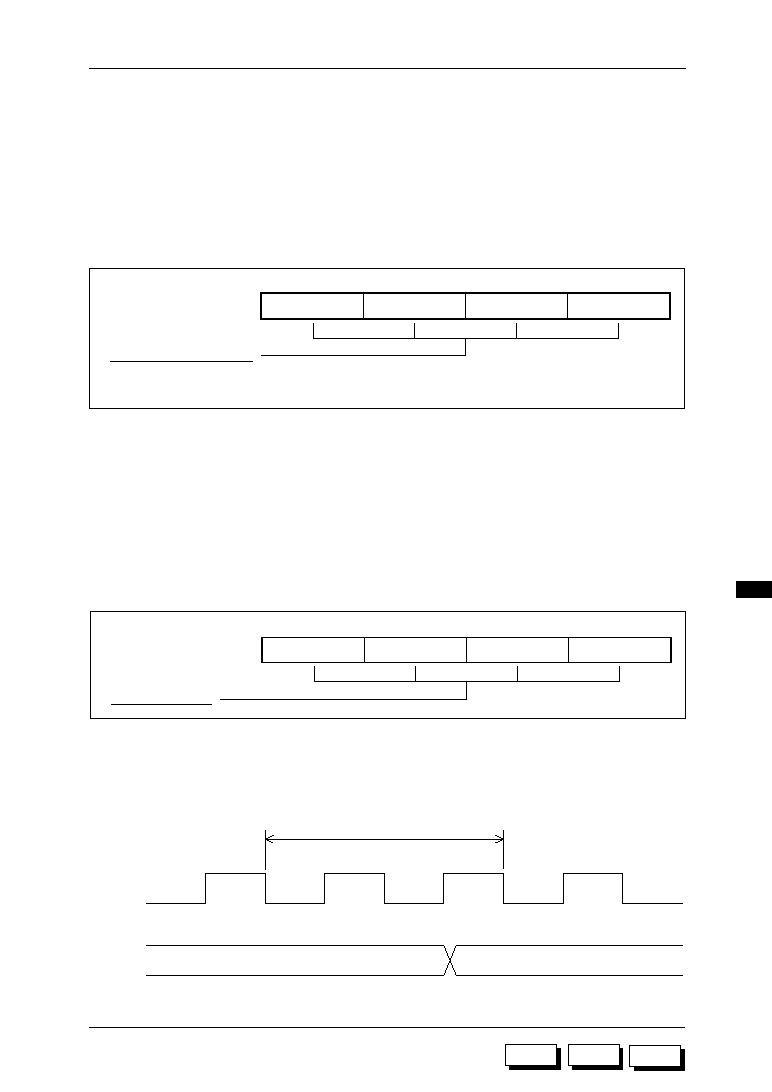

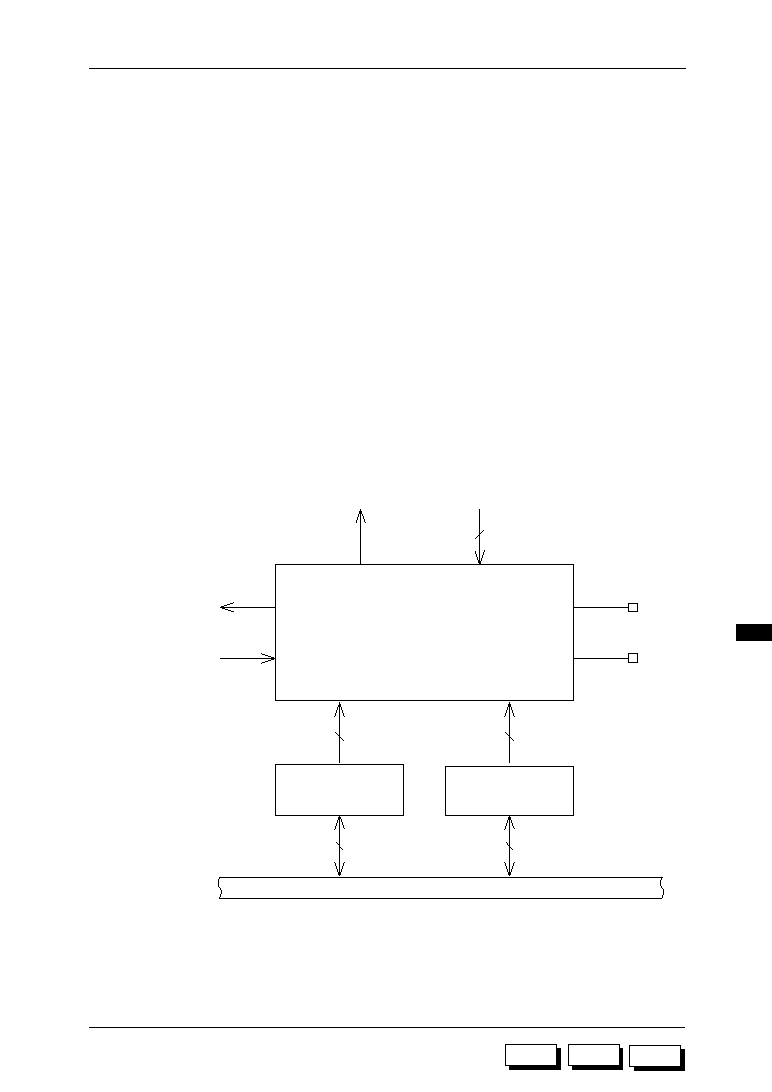

Asterisks (*) indicate port secondary functions. Signal names enclosed by chain lines (

)

indicate interface signals of the V

DDI

power supply system.

Figure 1-3 ML63193 Block Diagram

XT0

XT1

OSC0

OSC1

OSC

RAM

2048N

RESET

RST

V

DDI

TIMER

8 bits

• 4

SCLK*

SIN*

SOUT*

4

INT

SFT

TM0CAP/TM1CAP*

TM0OVF/TM1OVF*

T02CK*

T13CK*

1

INT

I/O

PORT

P9.0≠P9.3

PA.0≠PA.3

PB.0≠PB.3

PC.0≠PC.3

PE.0≠PE.3

3

INT

V

DDH

V

DD

CB1

CB2

DATA BUS

TBC

4

INT

BLD

INT

100HzTC

1

BACK-

UP

V

SS

MELODY

MD

1

INT

MDB

1

INT

INPUT

PORT

P0.0≠P0.3

LCD

&

DSPR

COM1≠16

SEG0≠63

TST1

TST

TST2

INT

WDT

1

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDL

BIAS

INT193

ROM

64KW

BUS

CON-

TROL

MIE

CBR

EBR

L

C

G

Z

ALU

RA

A

IR

INSTRUCTION

DECODER

nX-4/250

PC

H

Y

X

TIMING

CON-

TROL

SP

RSP

STACK

CAL.S : 16 levels

REG.S : 16 levels

MULDIV

SIO

2

INT

RXC*

TXC*

RXD*

TXD*

CPU CORE

M193

1-9

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

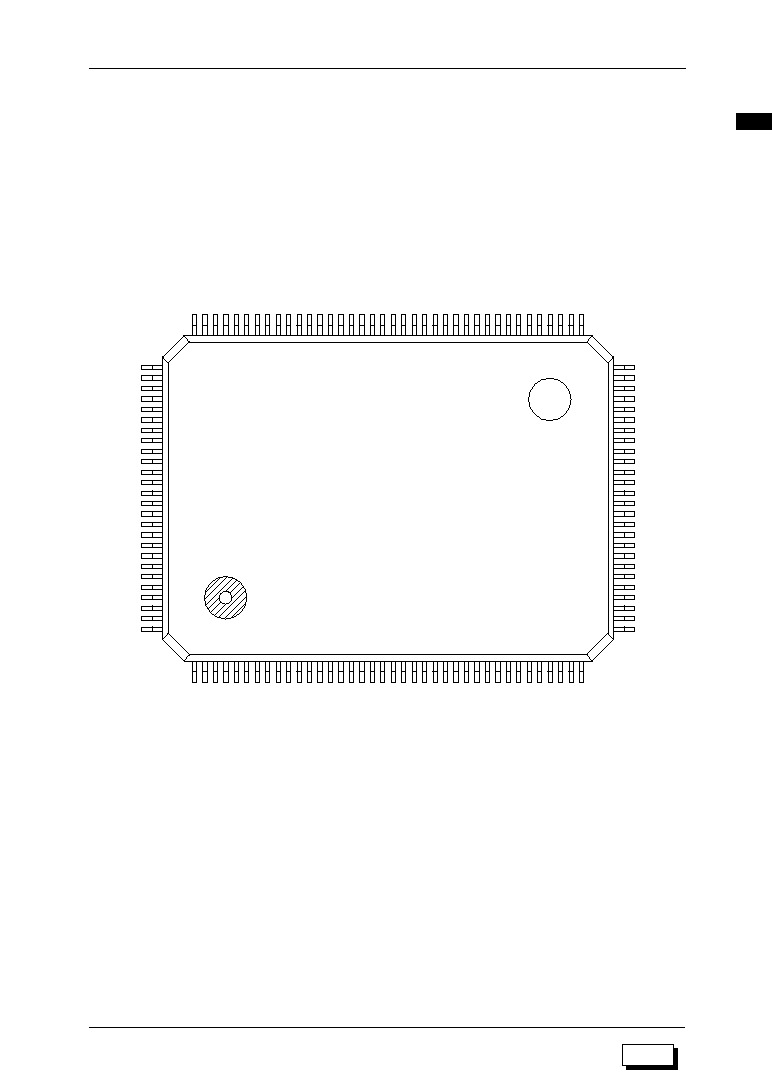

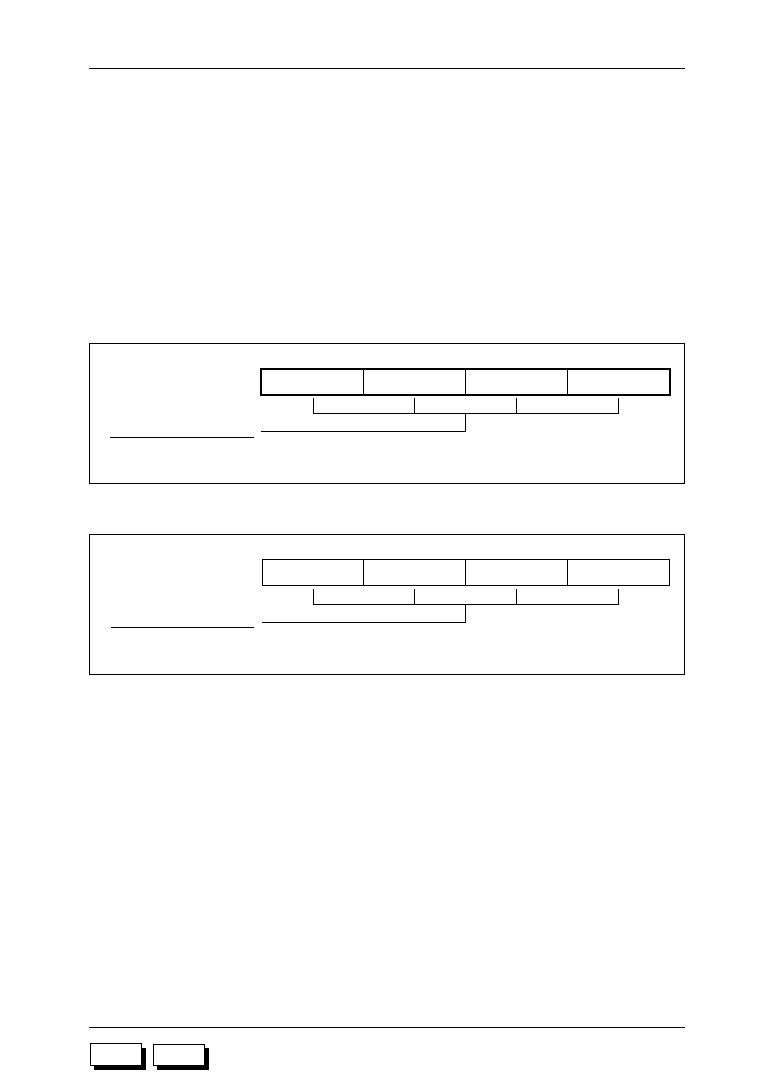

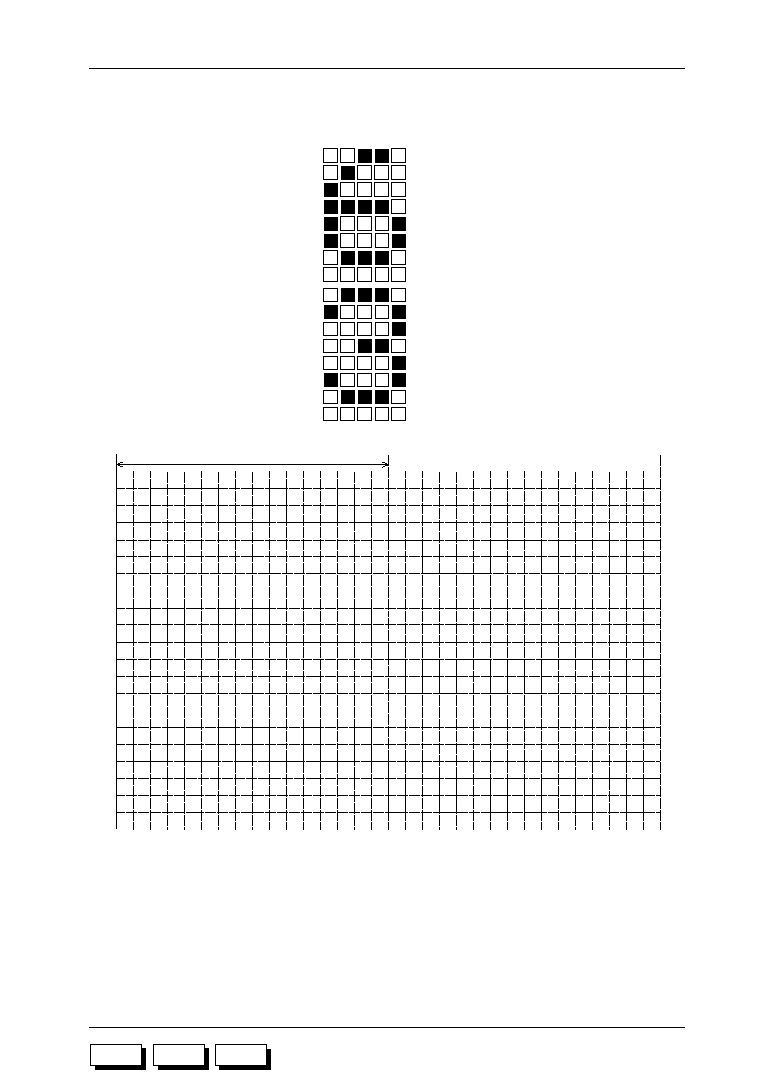

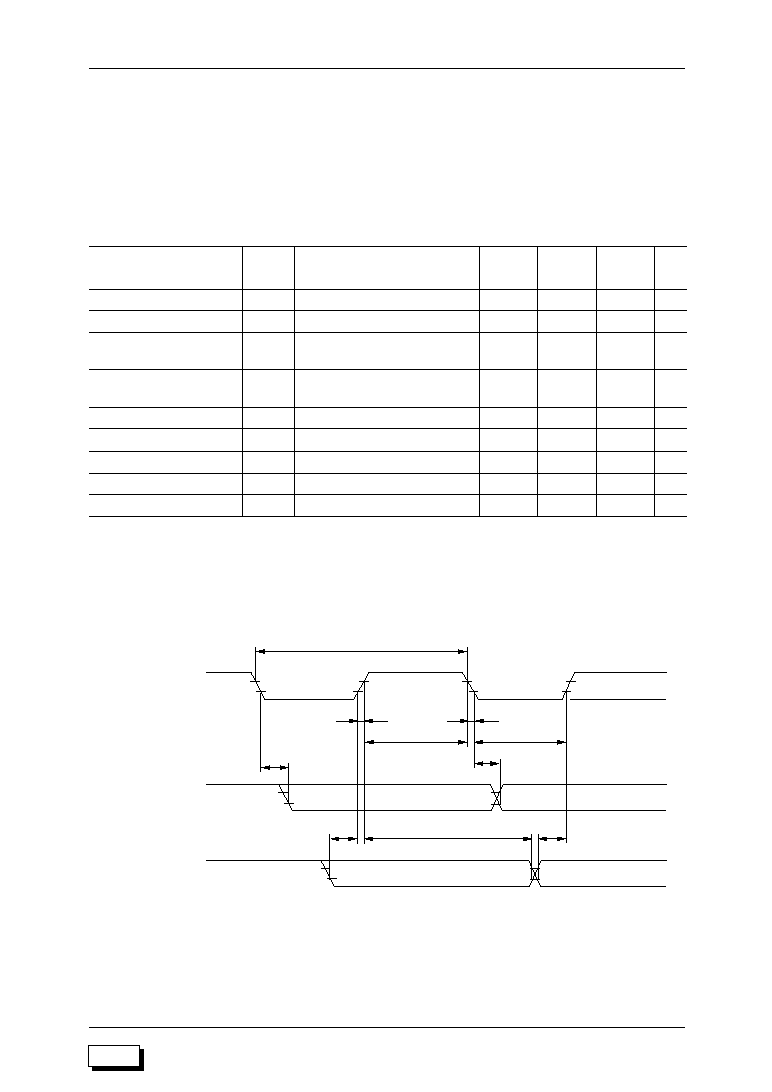

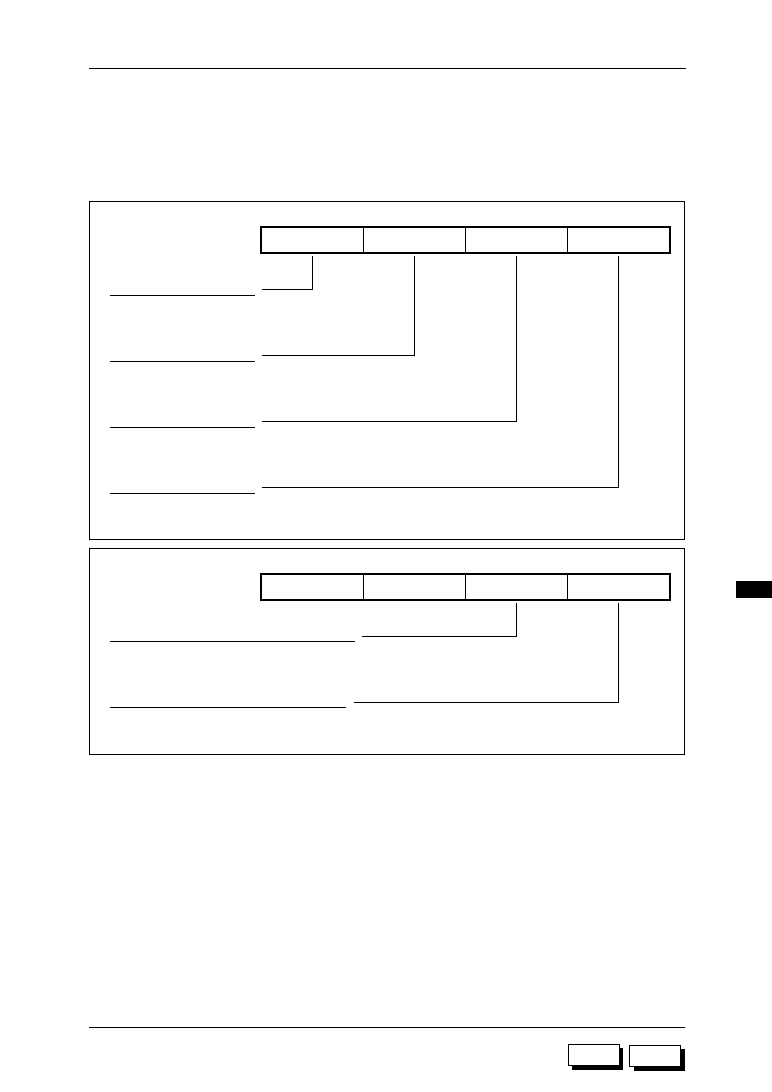

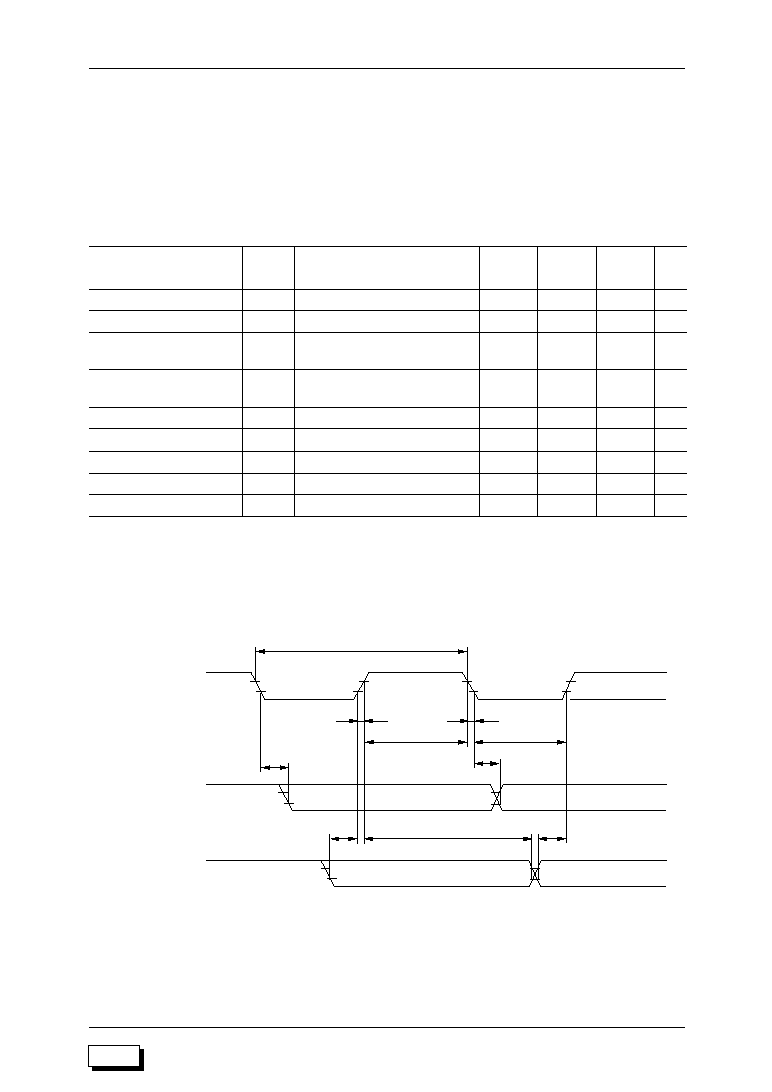

1.5 Pin Configuration

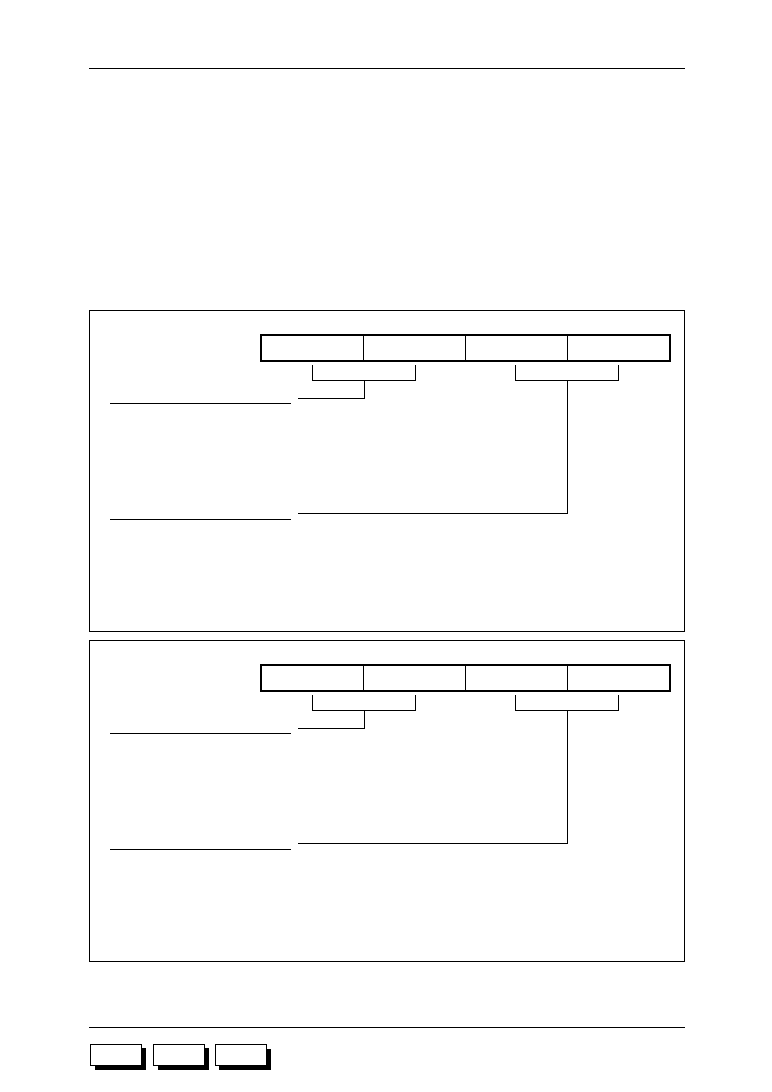

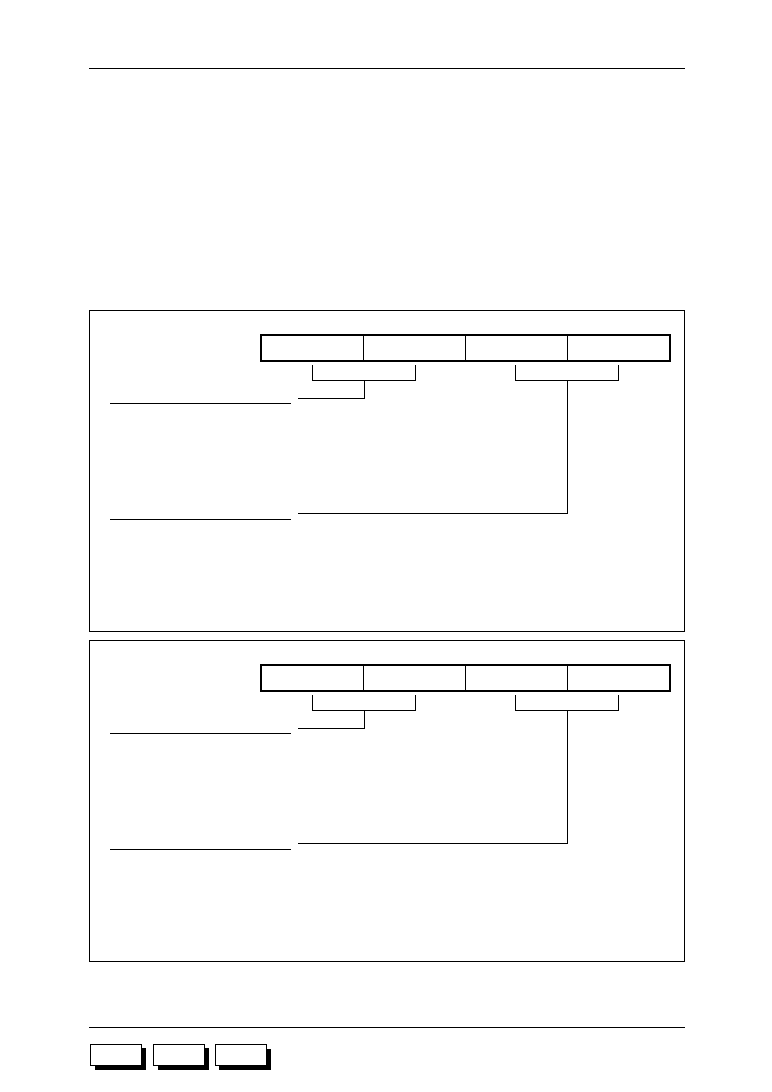

1.5.1 ML63187 Pin Configuration

The ML63187 pin configuration, chip pin configuration, and pad coordinates are shown in

Figures 1-4, 1-5, and Table 1-2, respectively.

NC (not connected) indicates an unused pin that is left unconnected (open).

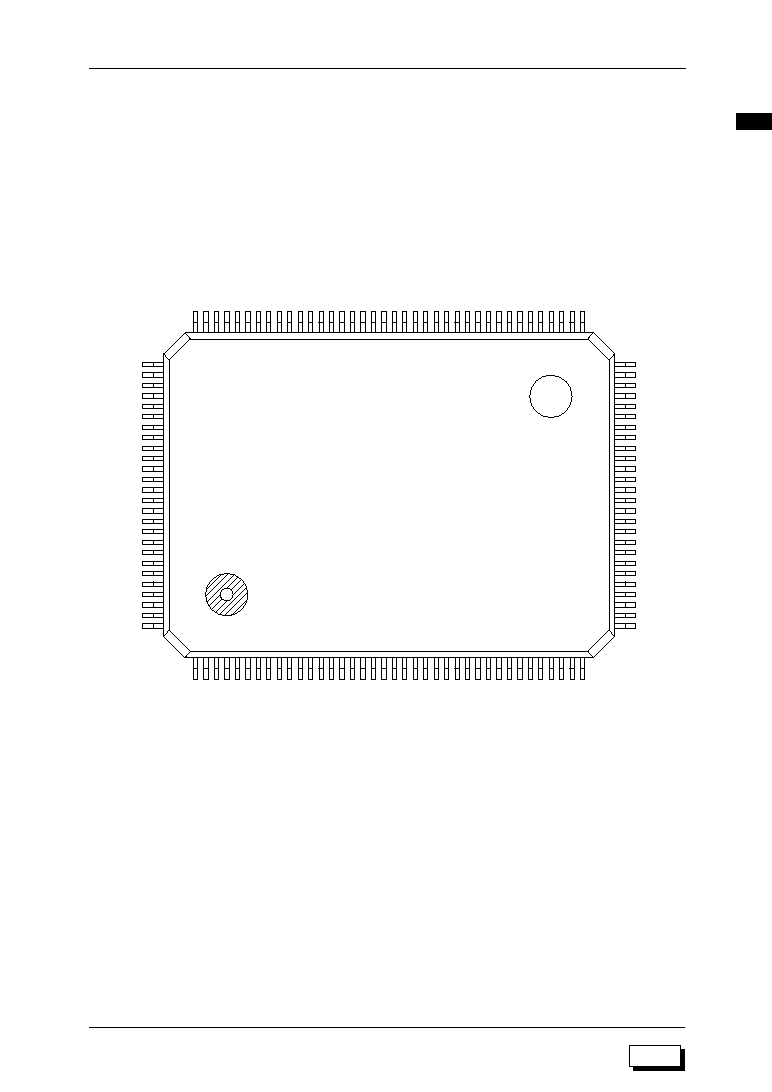

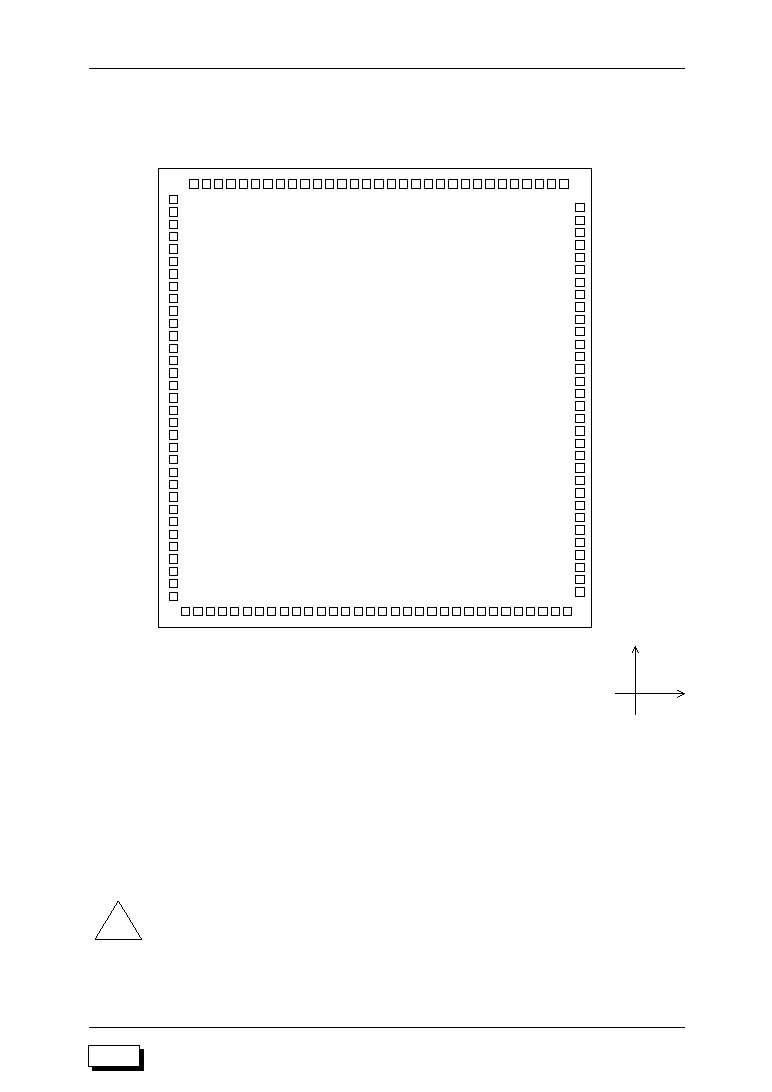

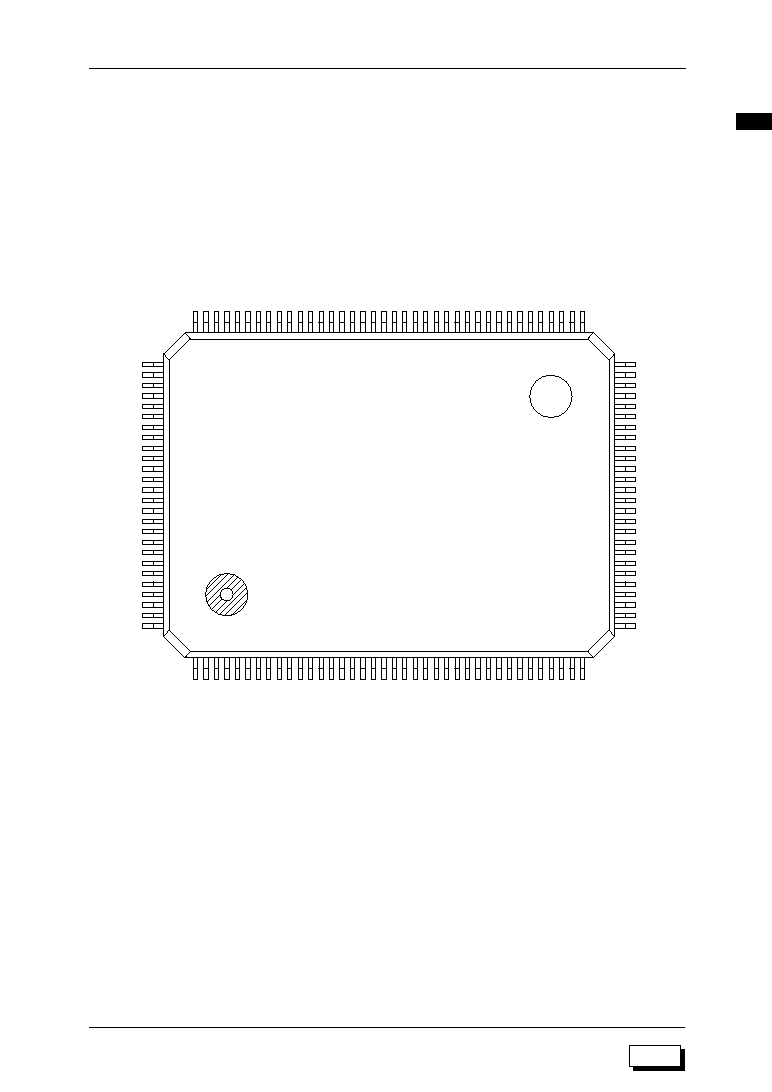

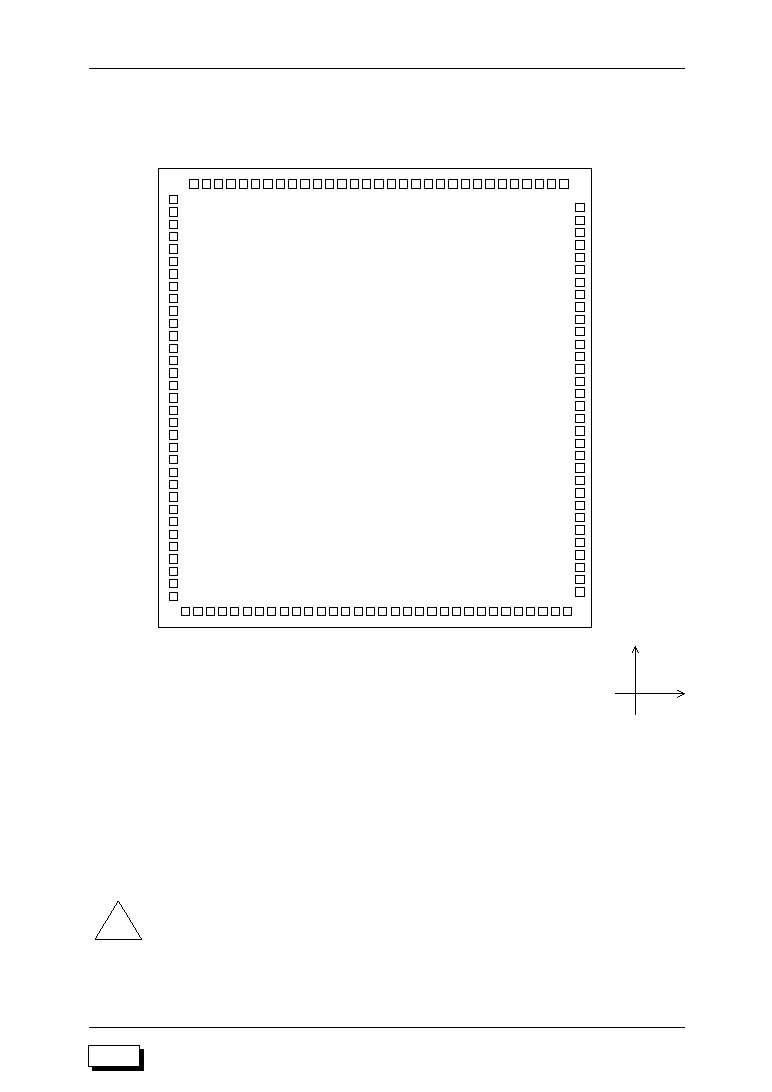

Figure 1-4 ML63187 128-Pin QFP Pin Configuration (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

(NC)

(NC)

(NC)

(NC)

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

COM11

COM12

(NC)

(NC)

(NC)

(NC)

MDB

MD

TST2

TST1

XT0

XT1

RESET

OSC0

OSC1

V

DDL

V

DD

CB2

CB1

V

DDH

C2

C1

V

DD5

V

DD4

V

DD3

V

DD2

V

DD1

V

SS

COM16

COM15

COM14

COM13

(NC)

(NC)

(NC)

(NC)

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM8

COM7

COM6

COM5

COM4

COM3

COM2

COM1

PB.3

PB.2

PB.1

PB.0

PE.3

PE.2

PE.1

PE.0

V

DDI

(NC)

(NC)

(NC)

(NC)

(NC)

M187

1-10

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

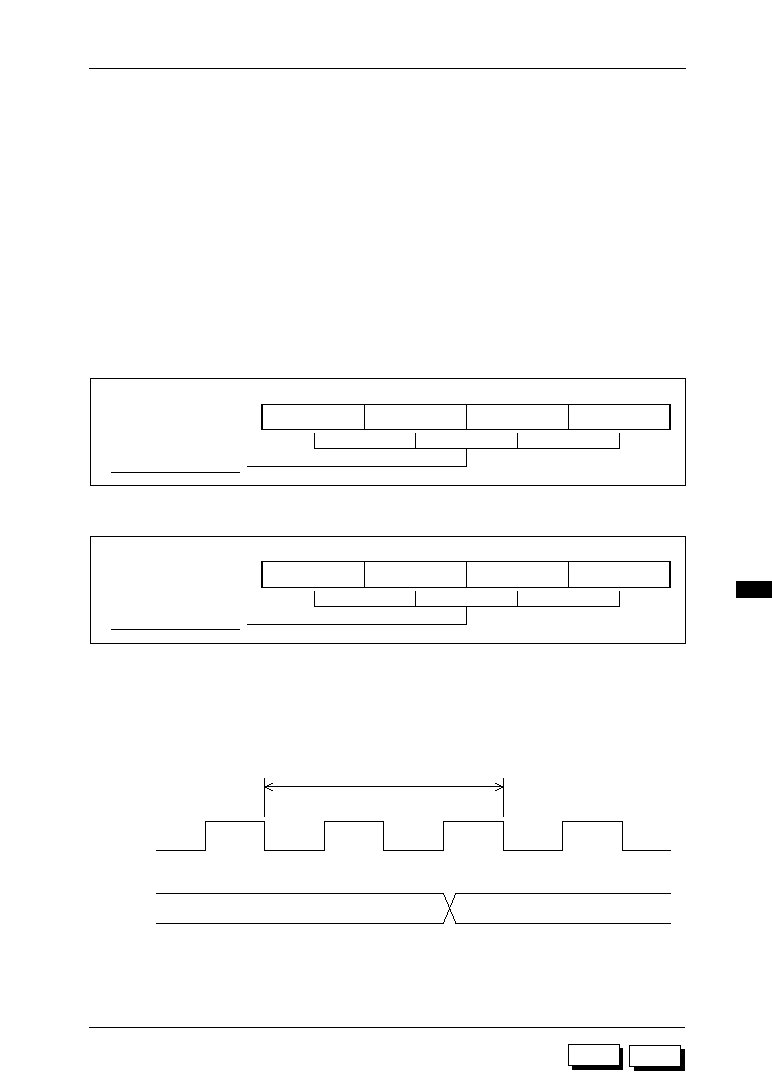

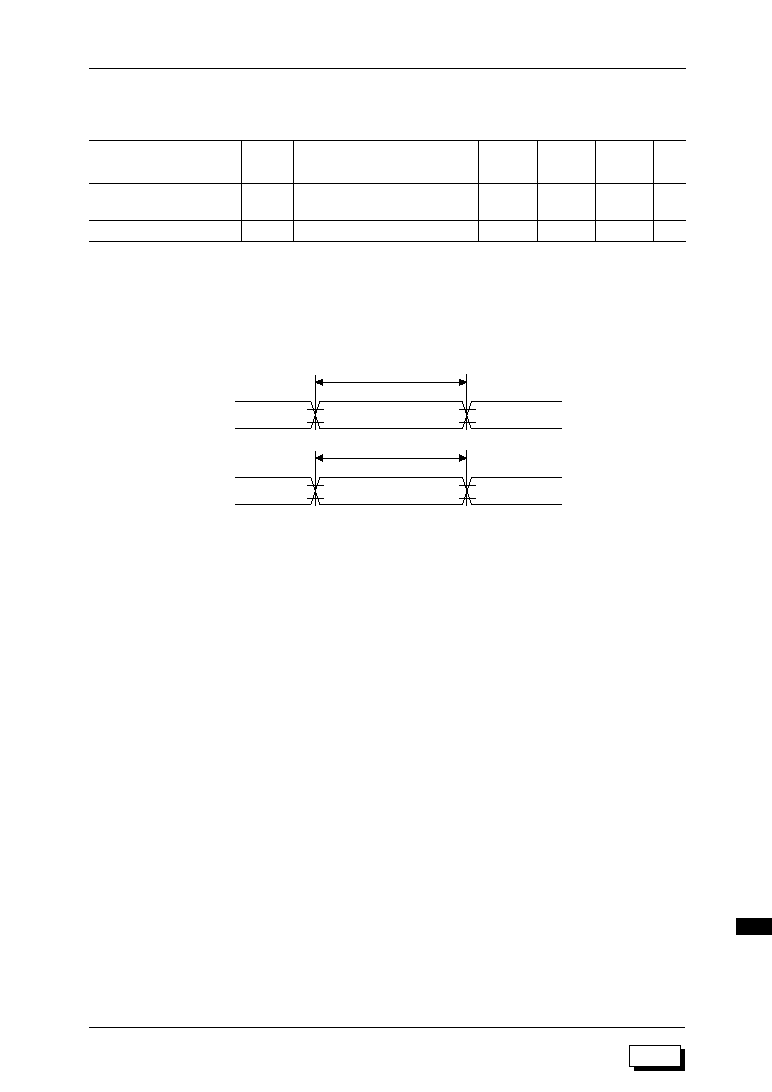

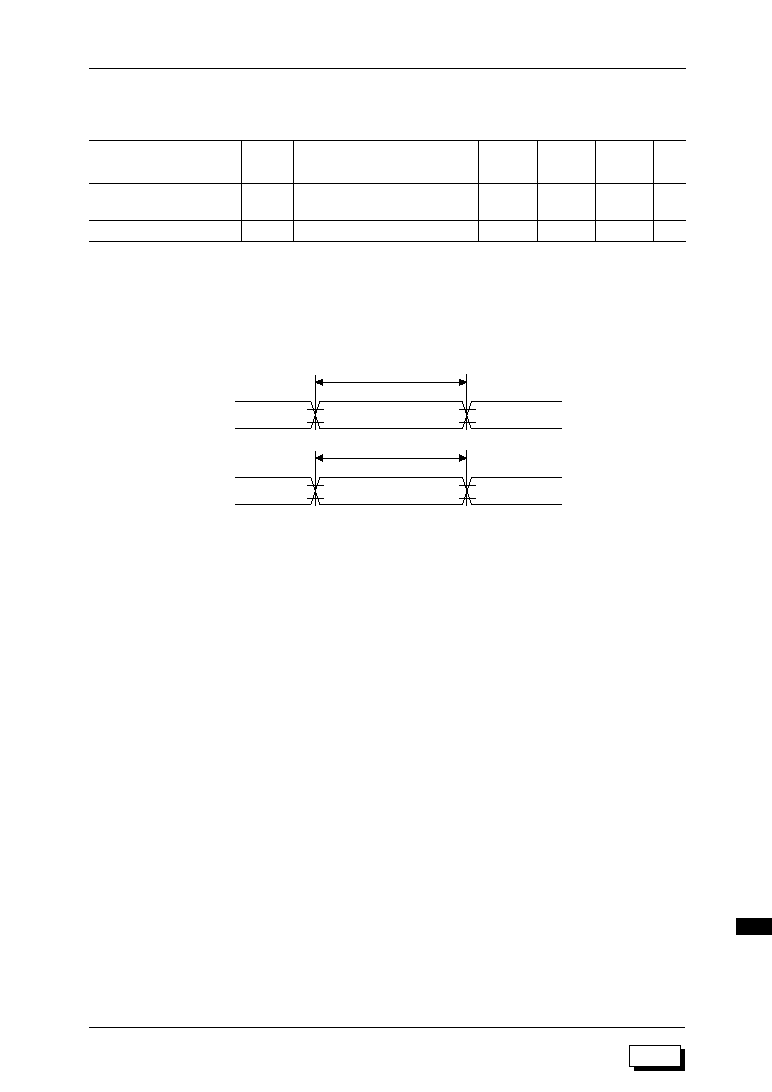

∑ Chip size

: 4.238 mm

•

4.914 mm

∑ Chip thickness

: 350

m

m (280

m

m: available as required)

∑ Coordinate origin

: center of chip

∑ Pad hole size

: 100

m

m

•

100

m

m

∑ Pad size

: 110

m

m

•

110

m

m

∑ Minimum pad pitch

: 140

m

m

!

Note: The chip substrate voltage is V

SS

.

Figure 1-5 ML63187 Chip Pin Configuration (Top View)

Y

X

27 SEG38

28 SEG39

SEG11 111

29 SEG40

SEG10 110

30 SEG41

SEG9 109

31 SEG42

SEG8 108

32 SEG43

SEG7 107

33 SEG44

SEG6 106

34 SEG45

SEG5 105

35 SEG46

SEG4 104

36 SEG47

SEG3 103

37 SEG48

SEG2 102

38 SEG49

SEG1 101

39 SEG50

SEG0 100

40 SEG51

COM8 99

41 SEG52

COM7 98

42 SEG53

COM6 97

43 SEG54

COM5 96

44 SEG55

COM4 95

45 SEG56

COM3 94

46 SEG57

COM2 93

47 SEG58

COM1 92

48 SEG59

PB.3 91

49 SEG60

PB.2 90

50 SEG61

PB.1 89

SEG30 19

SEG29 18

57 COM13

SEG28 17

58 COM14

SEG27 16

59 COM15

SEG26 15

60 COM16

SEG25 14

61 V

SS

SEG24 13

62 V

DD1

SEG23 12

63 V

DD2

SEG22 11

64 V

DD3

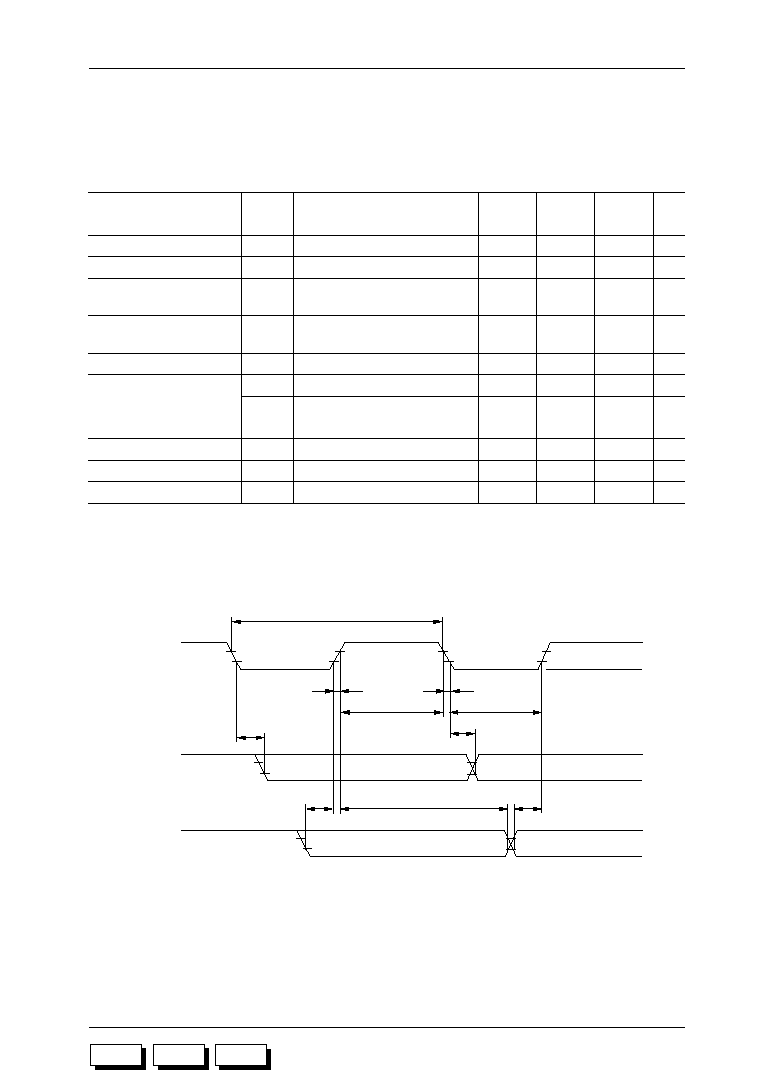

SEG21 10

65 V

DD4

SEG20 9

66 V

DD5

SEG19 8

67 C1

SEG18 7

68 C2

SEG17 6

69 V

DDH

SEG16 5

70 CB1

SEG15 4

71 CB2

SEG14 3

72 V

DD

SEG13 2

73 V

DDL

SEG12 1

74 OSC1

75 OSC0

76 RESET

77 XT1

78 XT0

79 TST1

80 TST2

81 MD

82 MDB

SEG37 26

SEG36 25

SEG35 24

SEG34 23

SEG33 22

SEG32 21

SEG31 20

51 SEG62

PB.0 88

52 SEG63

PE.3 87

53 COM9

PE.2 86

54 COM10

PE.1 85

55 COM11

PE.0 84

56 COM12

V

DDI

83

ML63187

1-11

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

M187

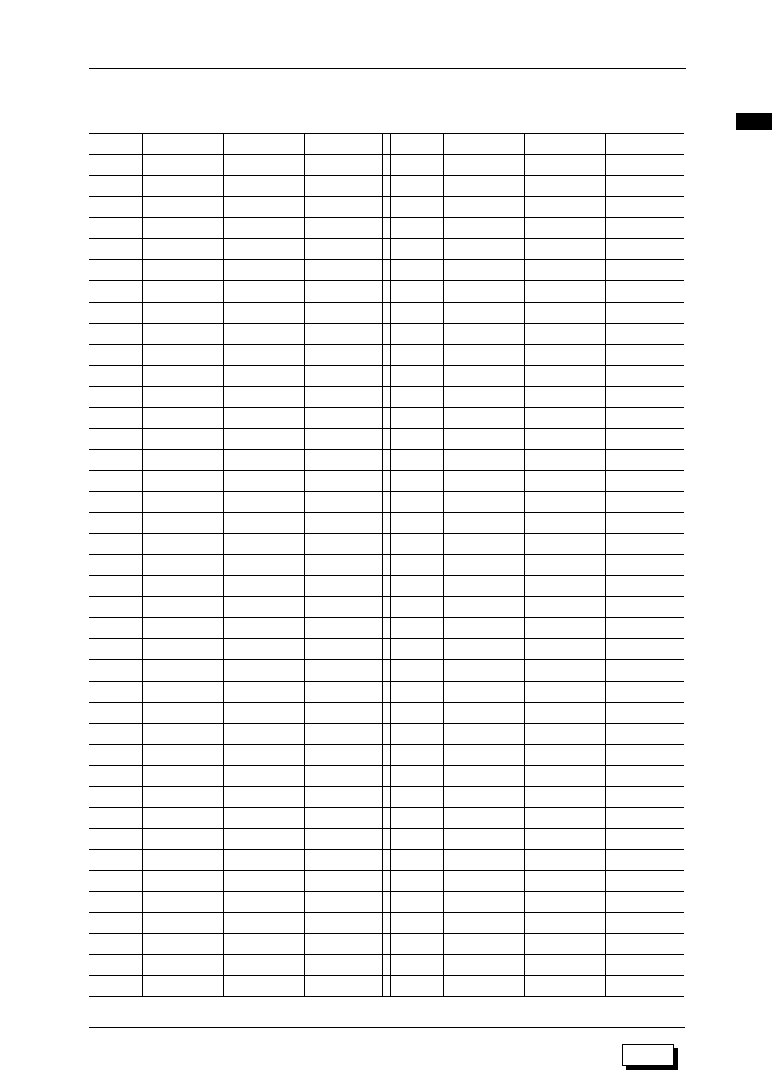

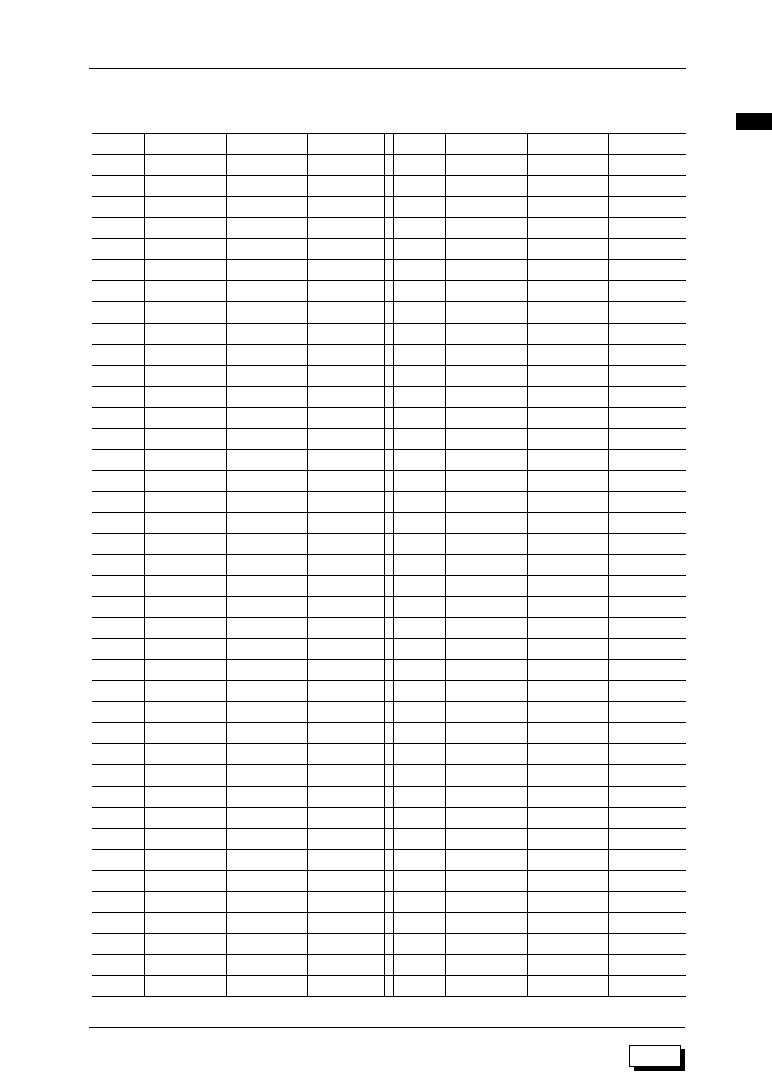

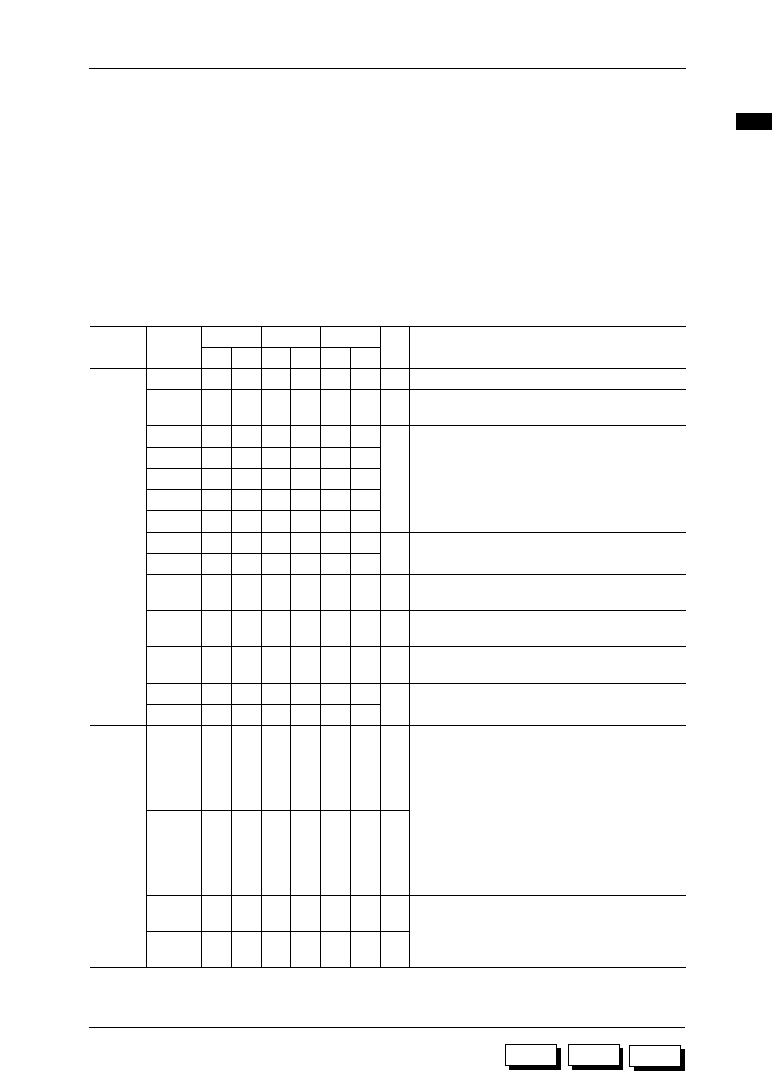

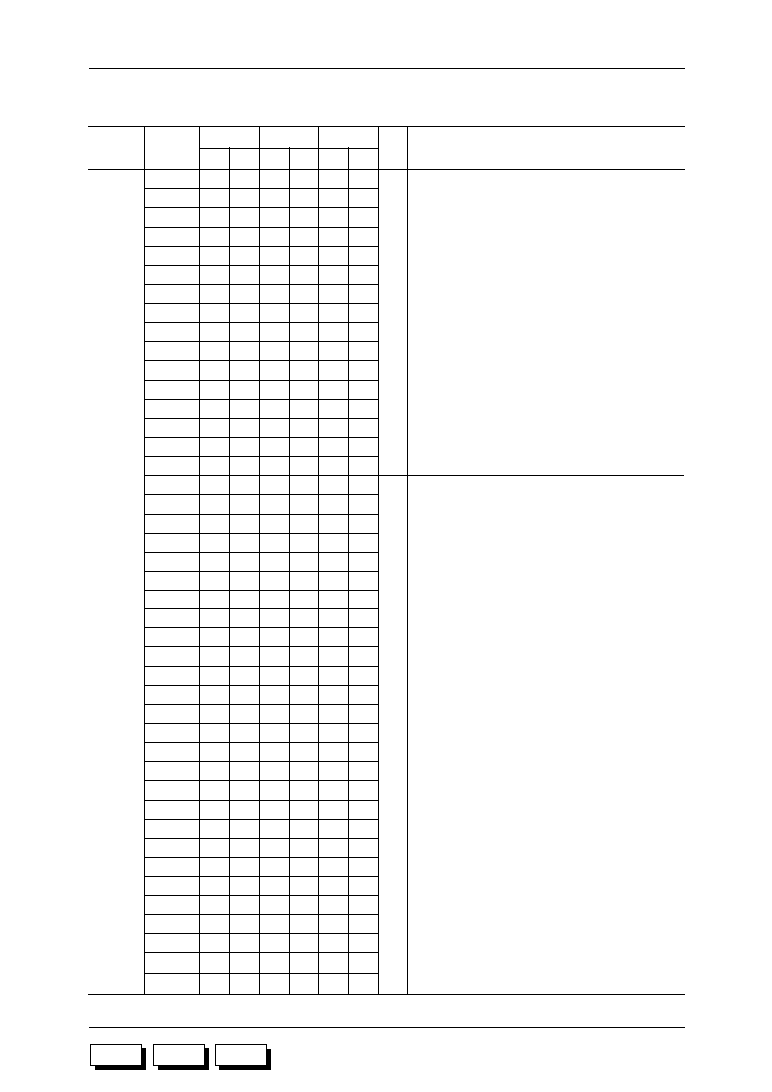

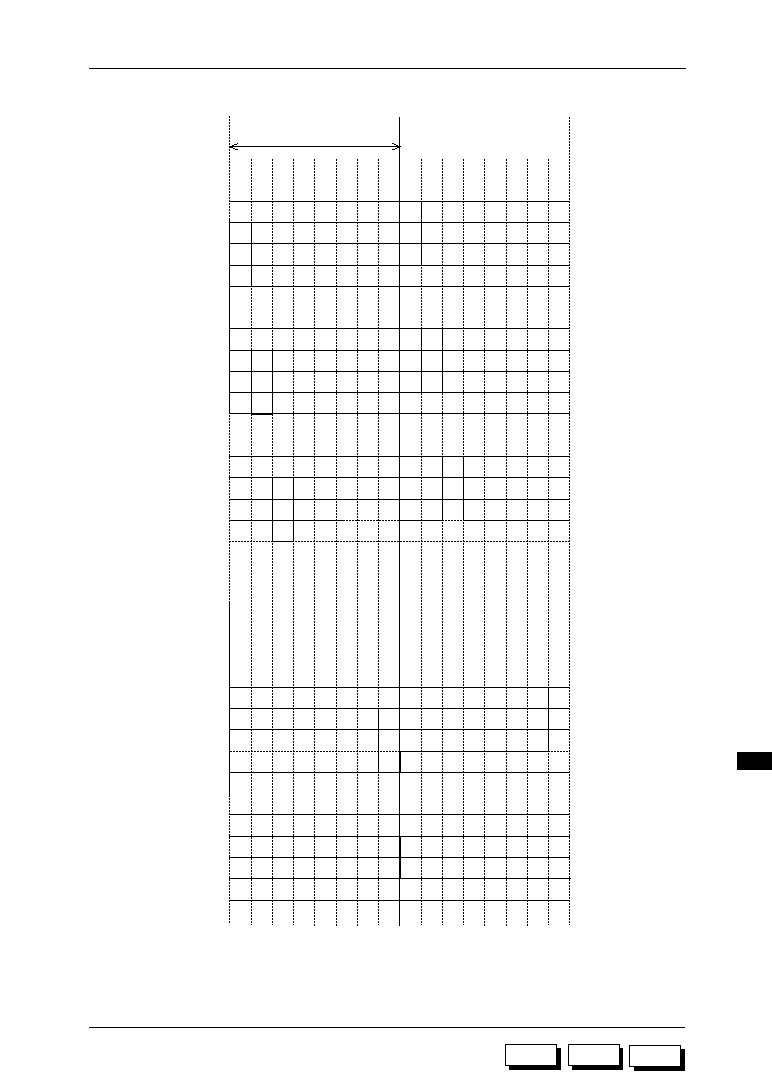

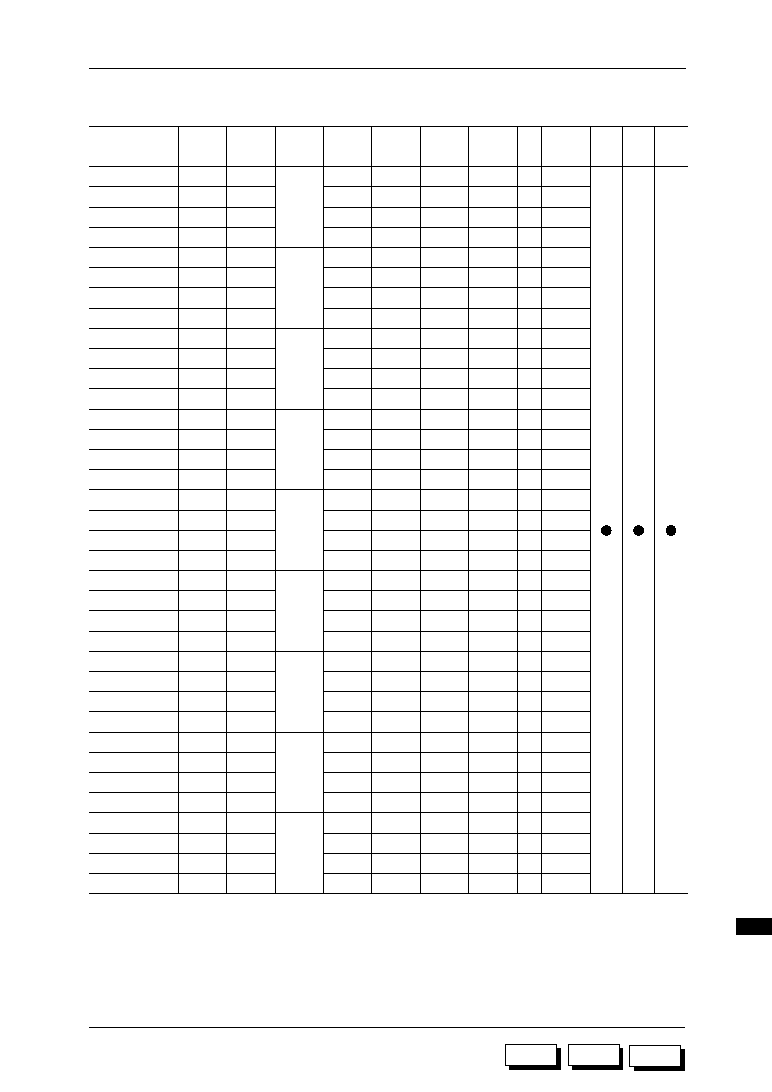

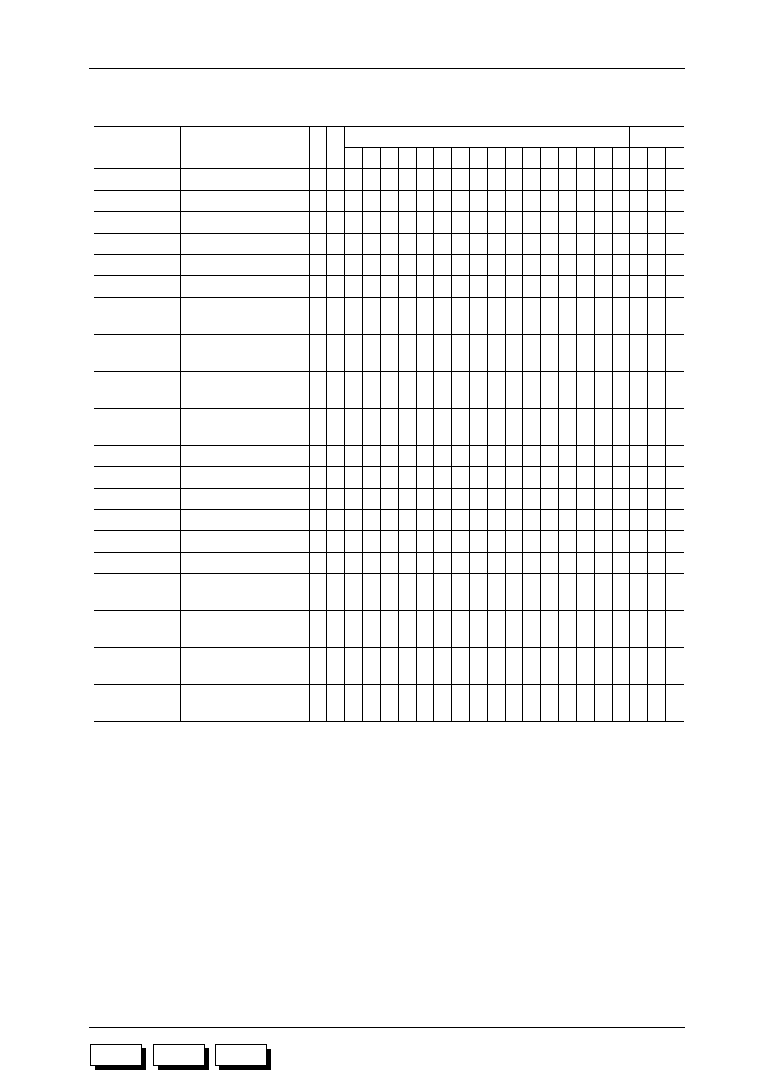

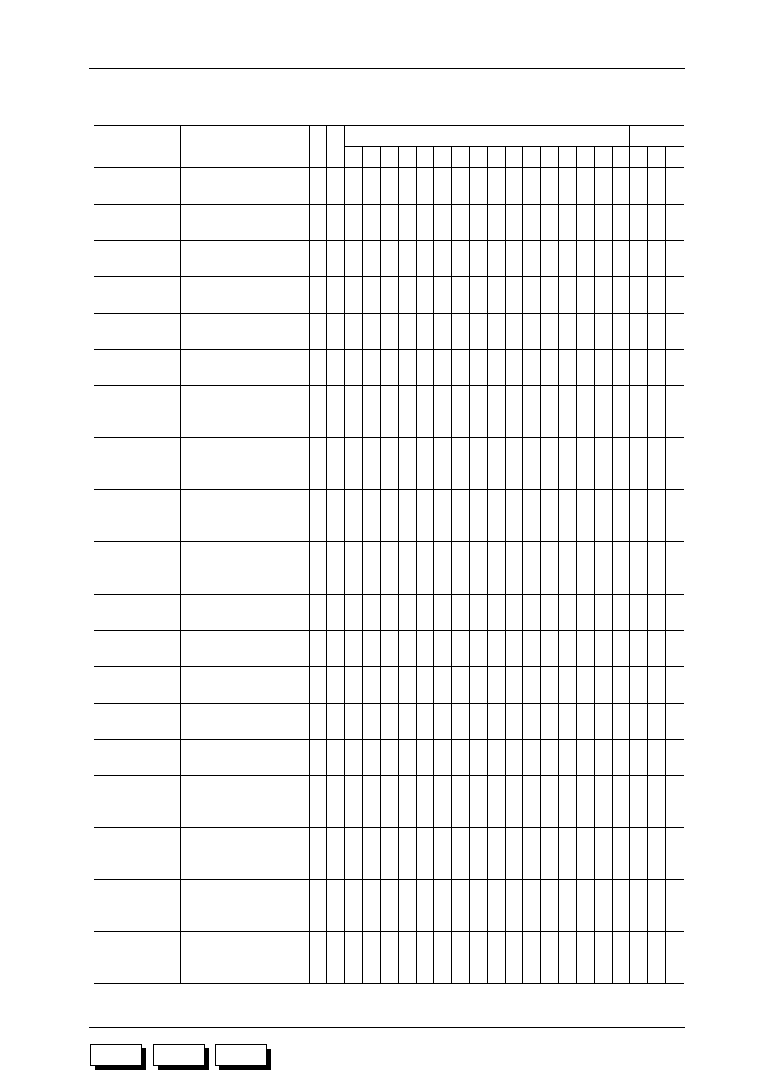

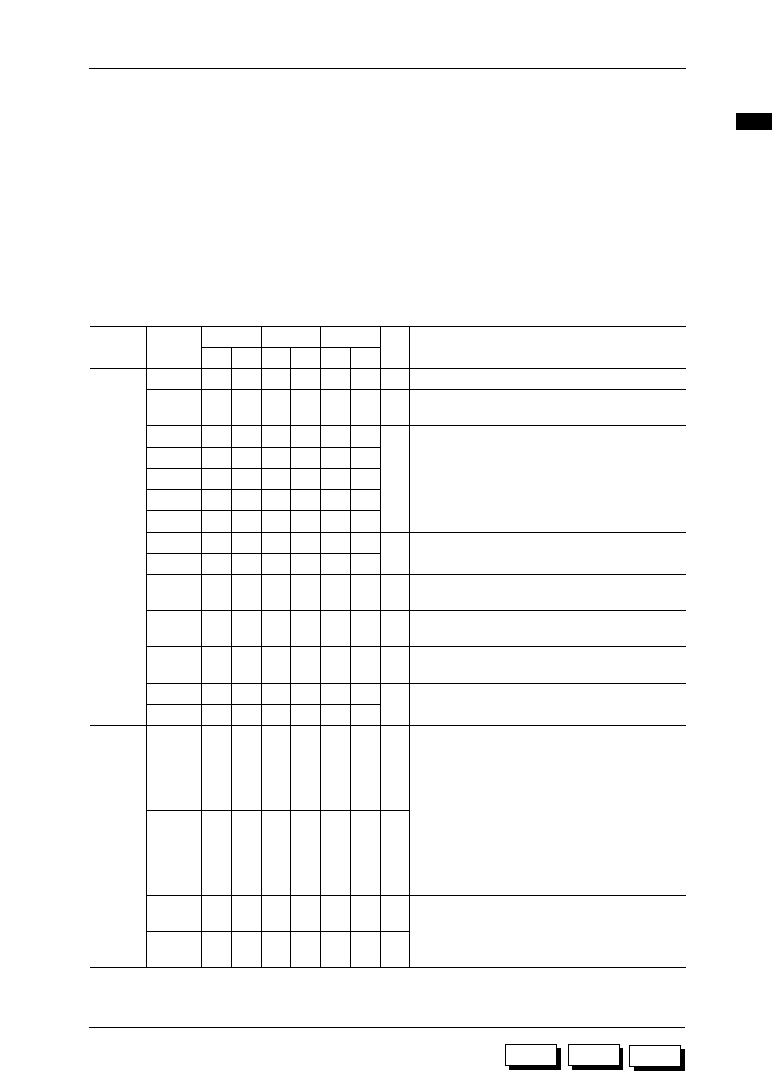

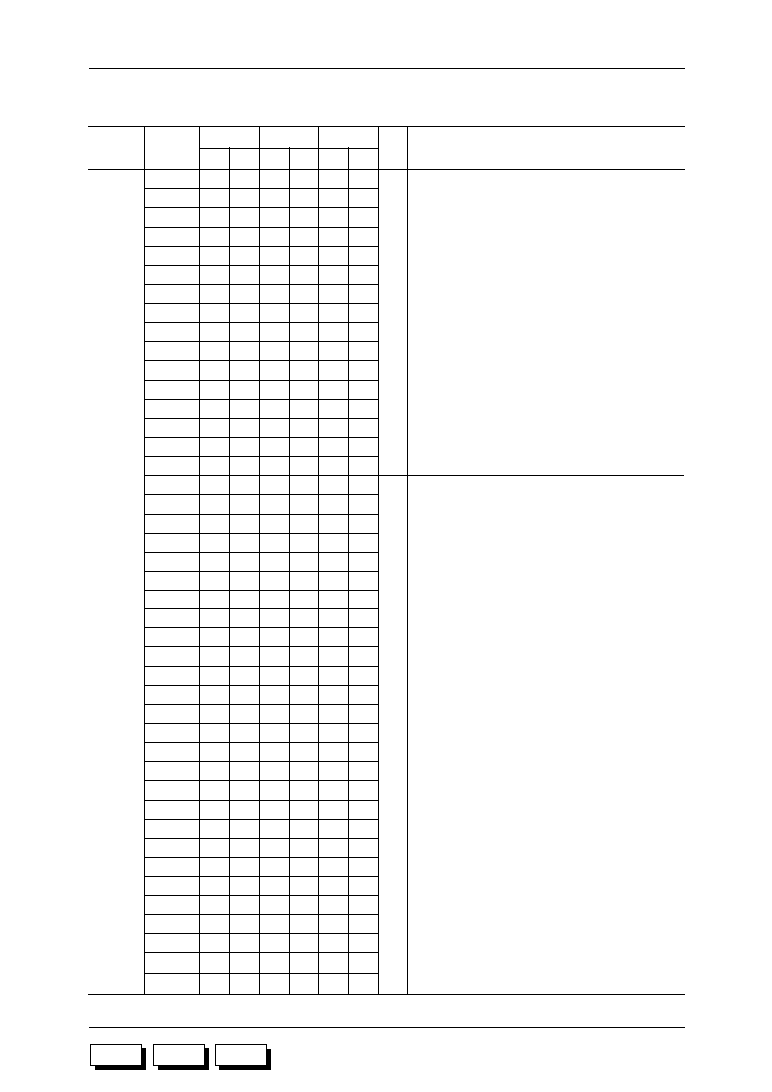

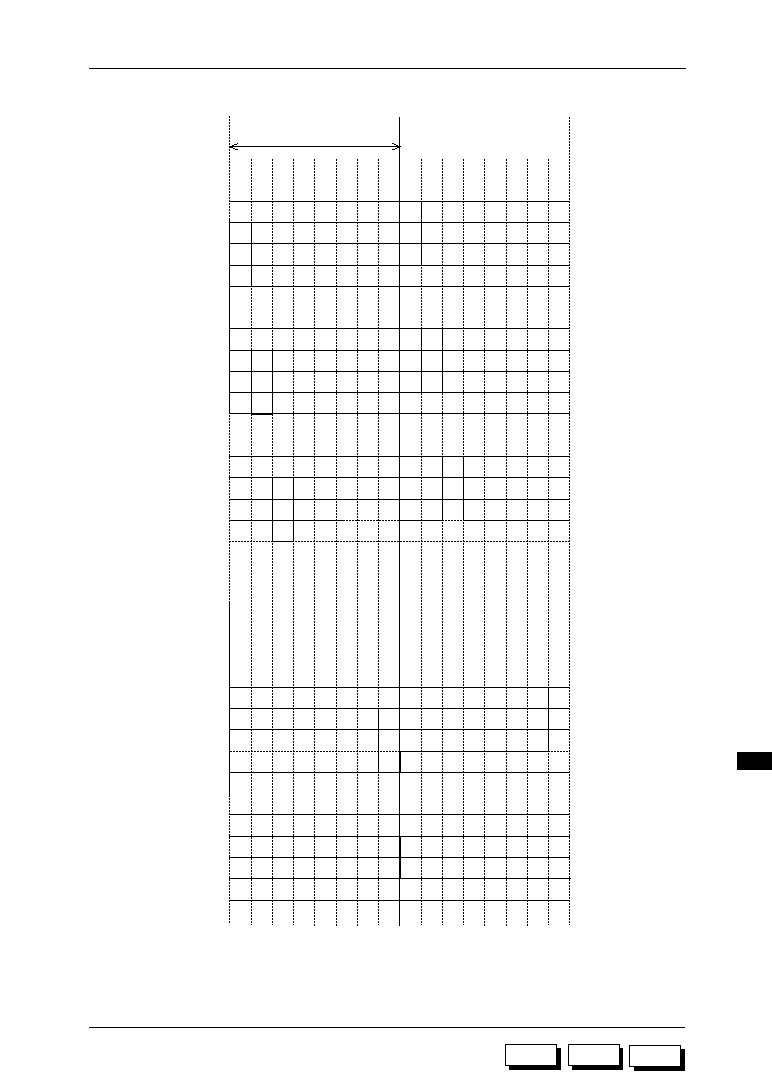

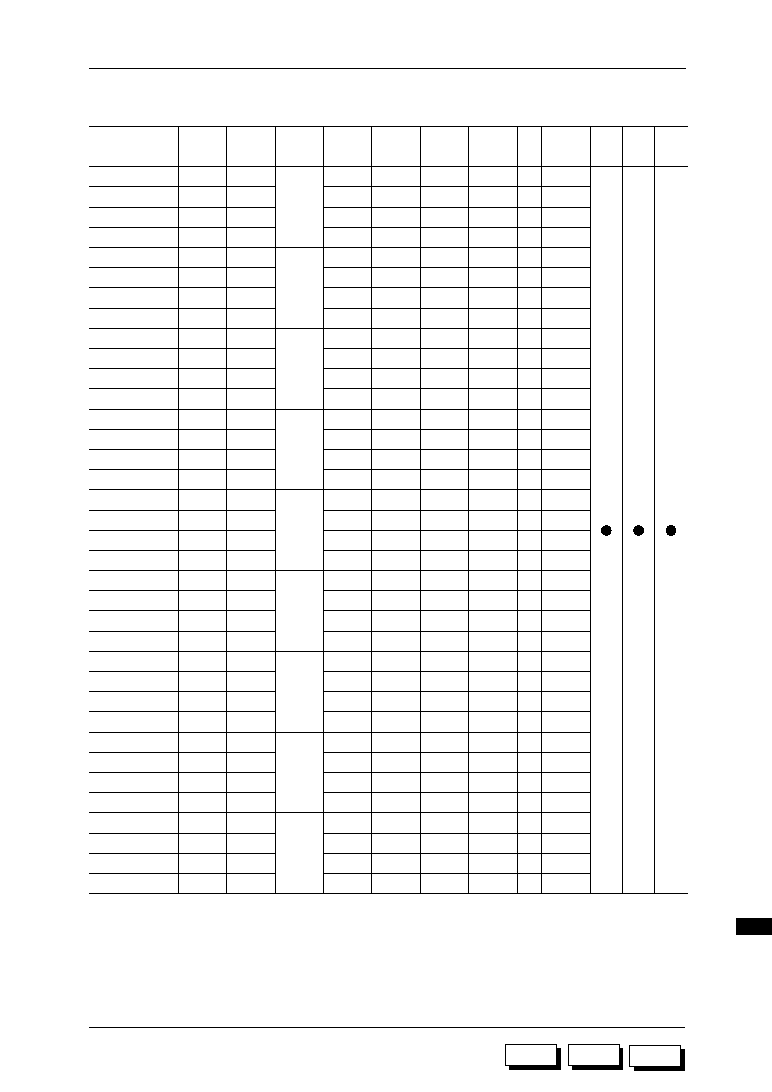

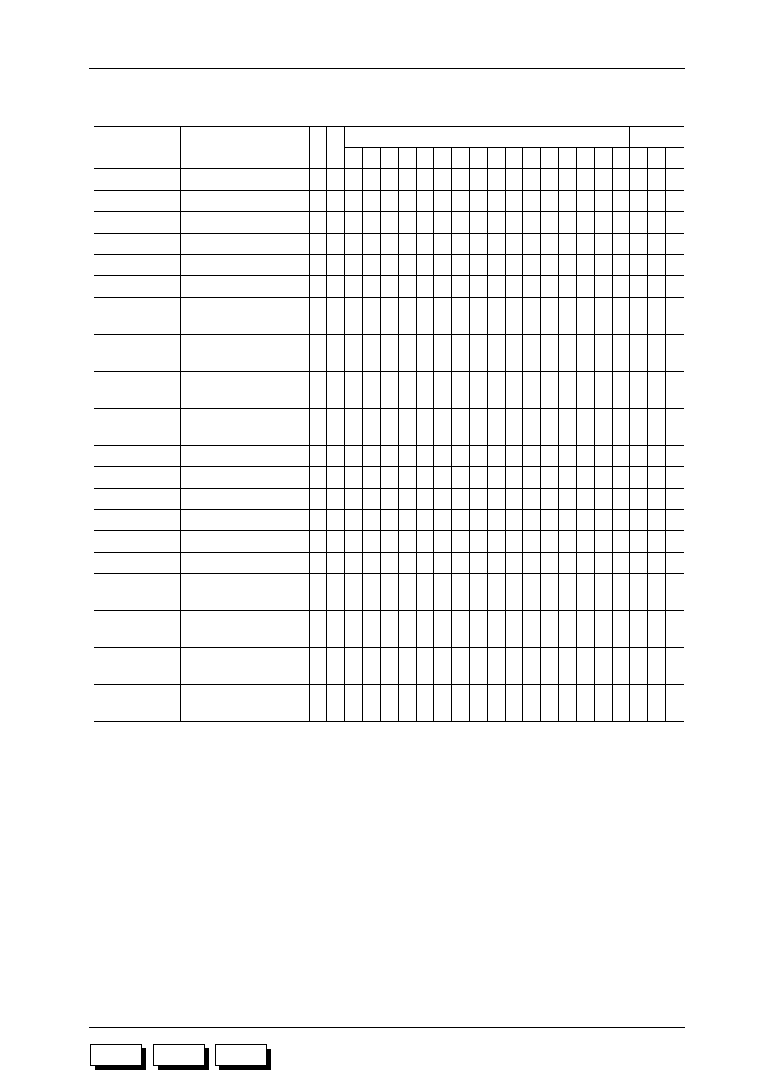

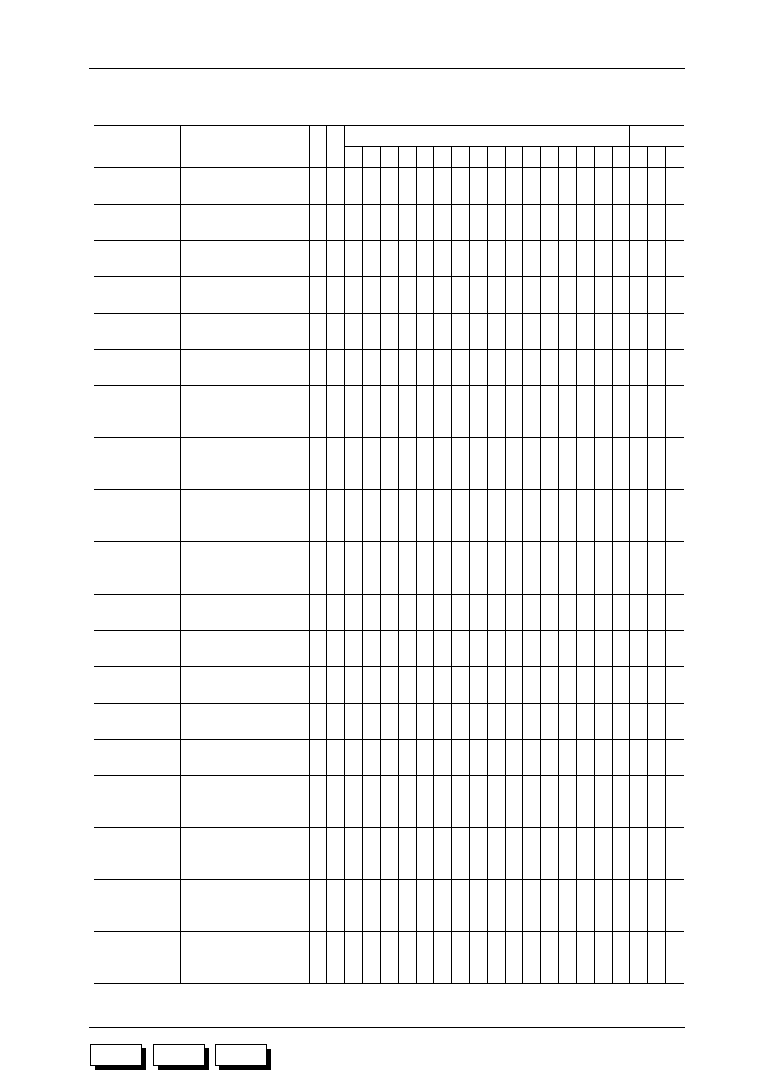

Table 1-2 ML63187 Pad Coordinates

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

V

SS

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDH

CB1

CB2

V

DD

V

DDL

OSC1

OSC0

RESET

XT1

XT0

TST1

TST2

≠1755

≠1615

≠1474

≠1334

≠1193

≠1053

≠913

≠772

≠632

≠491

≠351

≠211

≠70

70

211

351

491

632

772

913

1053

1193

1334

1474

1615

1755

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2311

≠2036

≠1895

≠1755

≠1615

≠1474

≠1334

≠1193

≠1053

≠913

≠772

≠632

≠491

≠351

≠211

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1969

1755

1615

1474

1334

1193

1053

913

772

632

491

351

211

70

≠70

≠211

≠351

≠491

≠632

≠772

≠913

≠1053

≠1193

≠1334

≠1474

≠70

70

211

351

491

632

772

913

1053

1193

1334

1474

1615

1755

1895

2036

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

2311

1-12

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

Table 1-2 ML63187 Pad Coordinates (continued)

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

MD

MDB

V

DDI

PE.0

PE.1

PE.2

PE.3

PB.0

PB.1

PB.2

PB.3

COM1

COM2

COM3

COM4

COM5

≠1615

≠1755

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

2311

2311

1895

1755

1615

1474

1334

1193

1053

913

772

632

491

351

211

70

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

COM6

COM7

COM8

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠1969

≠70

≠211

≠351

≠491

≠632

≠772

≠913

≠1053

≠1193

≠1334

≠1474

≠1615

≠1755

≠1895

≠2036

1-13

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

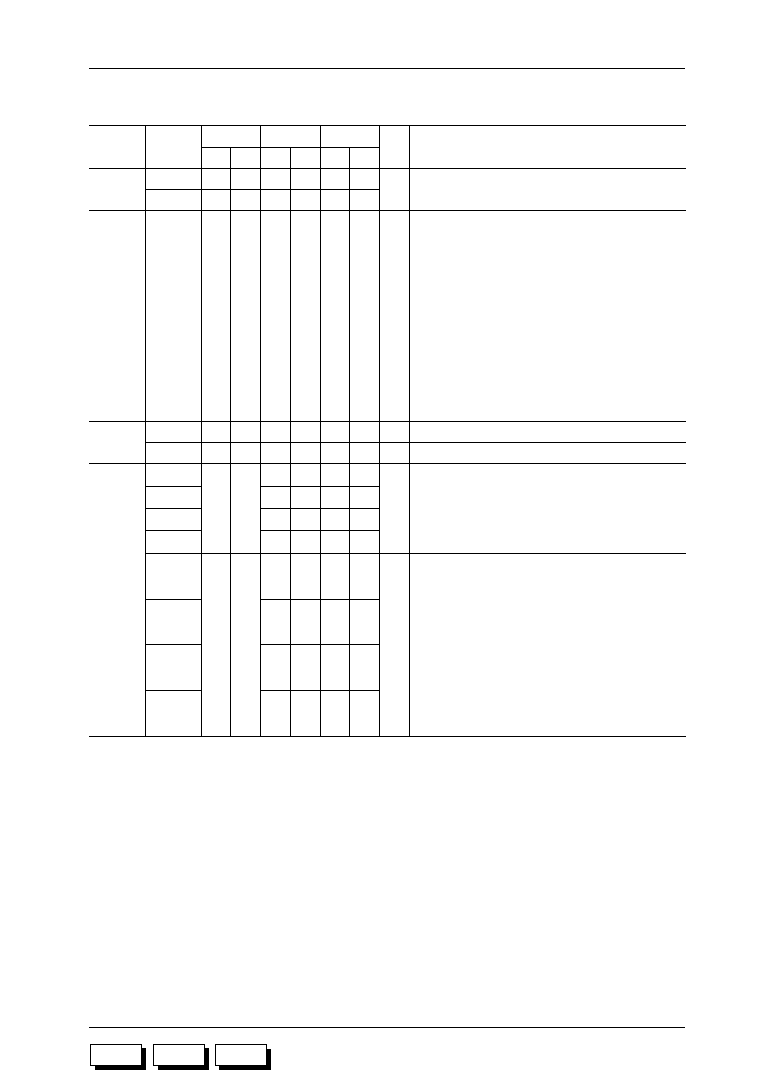

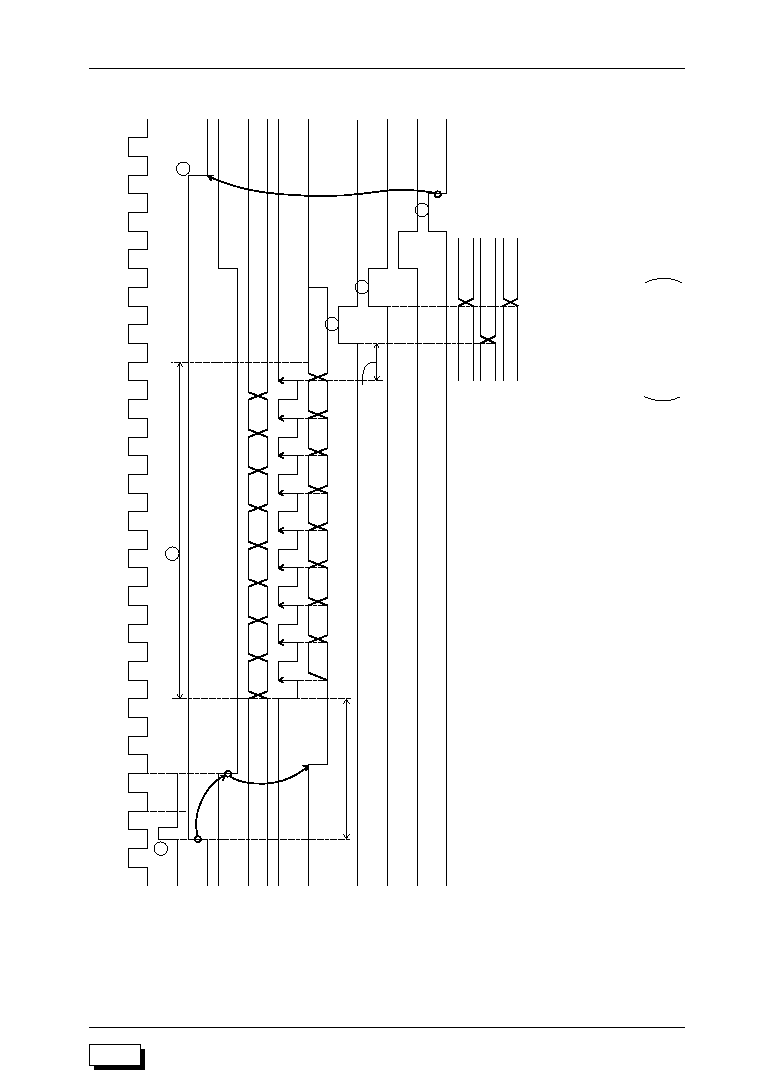

1.5.2 ML63189B Pin Configuration

The ML63189B pin configuration, chip pin configuration, and pad coordinates are shown in

Figures 1-6, 1-7, and Table 1-3, respectively.

NC (not connected) indicates an unused pin that is left unconnected (open).

Figure 1-6 ML63189B 128-Pin QFP Pin Configuration (Top View)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

(NC)

SEG30

SEG31

SEG32

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

(NC)

TST2

TST1

XT0

XT1

RESET

OSC0

OSC1

V

DDL

V

DD

CB2

CB1

V

DDH

C2

C1

V

DD5

V

DD4

V

DD3

V

DD2

V

DD1

V

SS

COM16

COM15

COM14

COM13

(NC)

SEG3

SEG2

SEG1

SEG0

COM8

COM7

COM6

COM5

COM4

COM3

COM2

COM1

P0.3

P0.2

P0.1

P0.0

P9.3

P9.2

P9.1

P9.0

PE.0

V

DDI

(NC)

MDB

MD

(NC)

SEG33

SEG34

SEG35

SEG36

SEG37

COM12

COM11

PA.3

PA.2

PA.1

PA.0

PB.3

PB.2

PB.1

PB.0

PE.3

PE.2

PE.1

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

M189B

1-14

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

∑ Chip size

: 4.81 mm

•

5.20 mm

∑ Chip thickness

: 350

m

m (280

m

m: available as required)

∑ Coordinate origin

: center of chip

∑ Pad hole size

: 100

m

m

•

100

m

m

∑ Pad size

: 110

m

m

•

110

m

m

∑ Minimum pad pitch

: 140

m

m

!

Note: The chip substrate voltage is V

SS

.

Figure 1-7 ML63189B Chip Pin Configuration (Top View)

64 COM10

31 SEG32

Y

X

SEG1 123

92 MDB

SEG2 1

63 COM9

SEG31 30

32 SEG33

SEG0 122

33 SEG34

COM8 121

34 SEG35

COM7 120

35 SEG36

COM6 119

36 SEG37

COM5 118

37 SEG38

COM4 117

38 SEG39

COM3 116

39 SEG40

COM2 115

40 SEG41

COM1 114

41 SEG42

P0.3 113

42 SEG43

P0.2 112

43 SEG44

P0.1 111

44 SEG45

P0.0 110

45 SEG46

P9.3 109

46 SEG47

P9.2 108

47 SEG48

P9.1 107

48 SEG49

P9.0 106

49 SEG50

PA.3 105

50 SEG51

PA.2 104

51 SEG52

PA.1 103

52 SEG53

PA.0 102

53 SEG54

PB.3 101

54 SEG55

PB.2 100

55 SEG56

PB.1 99

56 SEG57

PB.0 98

57 SEG58

PE.3 97

58 SEG59

PE.2 96

59 SEG60

PE.1 95

60 SEG61

PE.0 94

61 SEG62

62 SEG63

V

DDI

93

SEG30 29

65 COM11

SEG29 28

66 COM12

SEG28 27

67 COM13

SEG27 26

68 COM14

SEG26 25

69 COM15

SEG25 24

70 COM16

SEG24 23

71 V

SS

SEG23 22

72 V

DD1

SEG22 21

73 V

DD2

SEG21 20

74 V

DD3

SEG20 19

75 V

DD4

SEG19 18

76 V

DD5

SEG18 17

77 C1

SEG17 16

78 C2

SEG16 15

79 V

DDH

SEG15 14

80 CB1

SEG14 13

81 CB2

SEG13 12

82 V

DD

SEG12 11

83 V

DDL

SEG11 10

84 OSC1

SEG10 9

85 OSC0

SEG9 8

86 RESET

SEG8 7

87 XT1

SEG7 6

88 XT0

SEG6 5

89 TST1

SEG5 4

90 TST2

SEG4 3

91 MD

SEG3 2

ML63189B

M189B

1-15

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

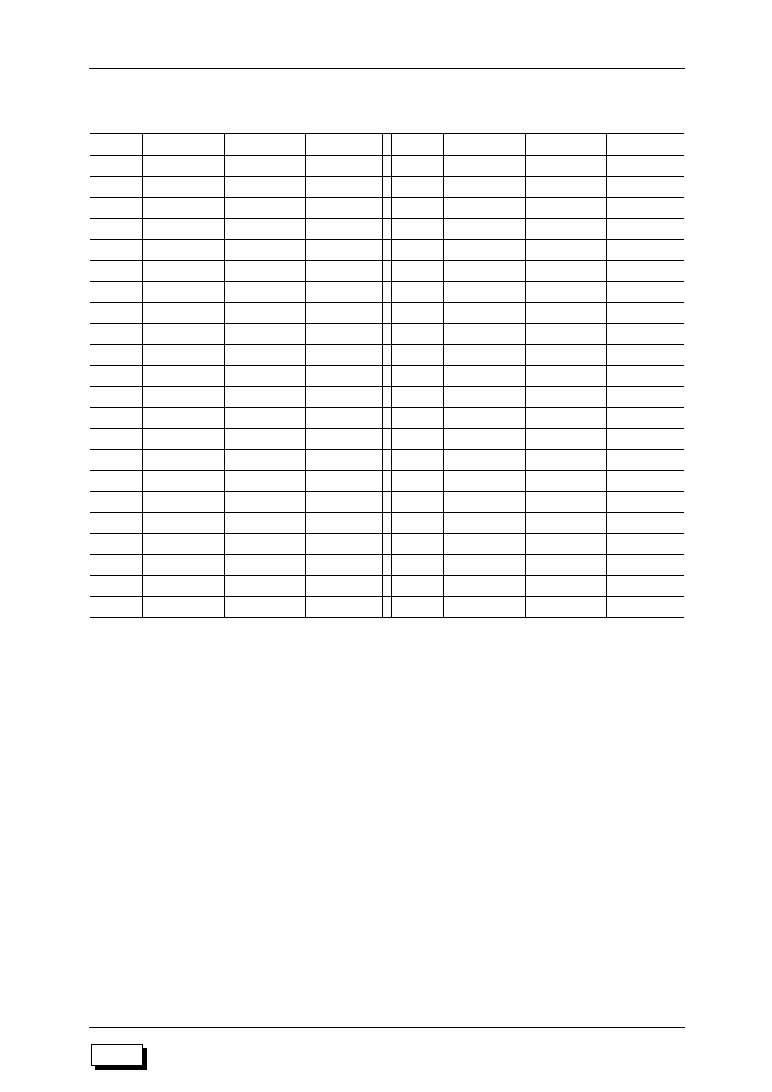

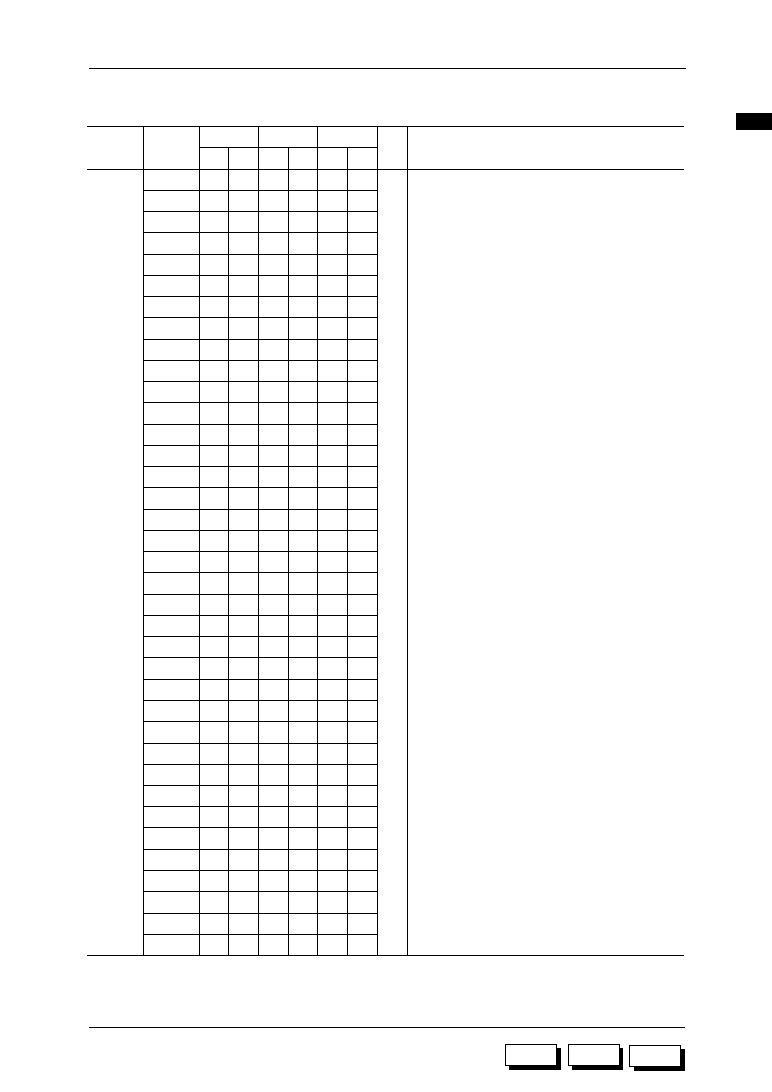

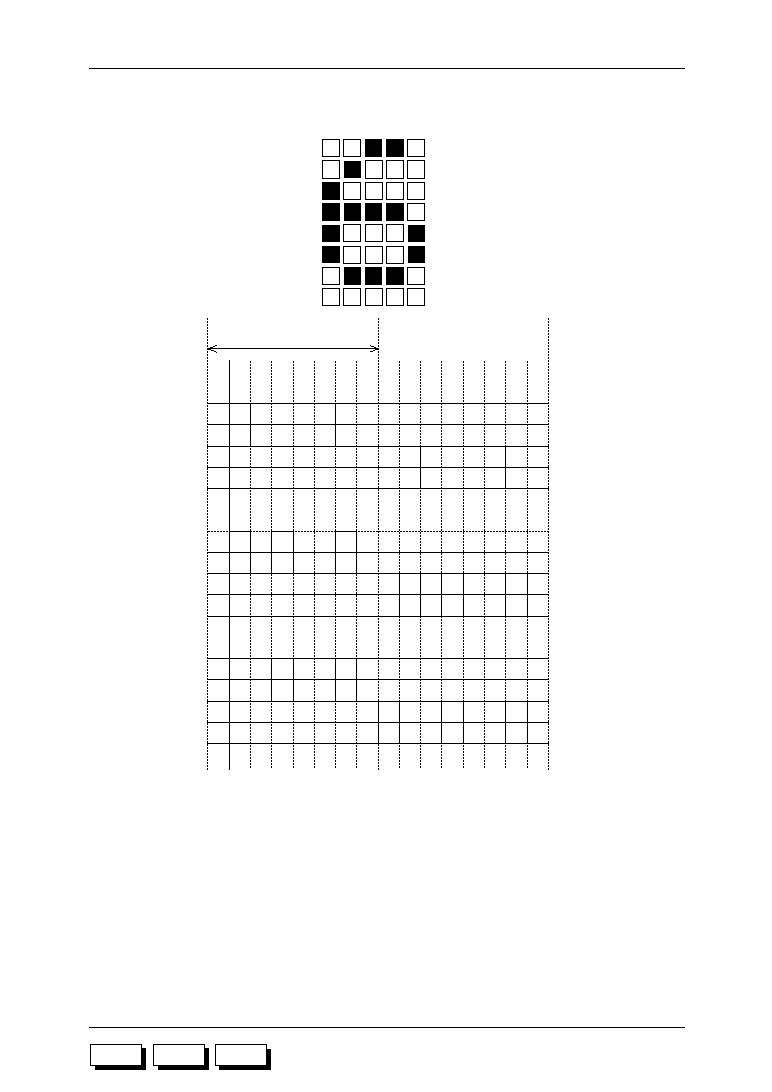

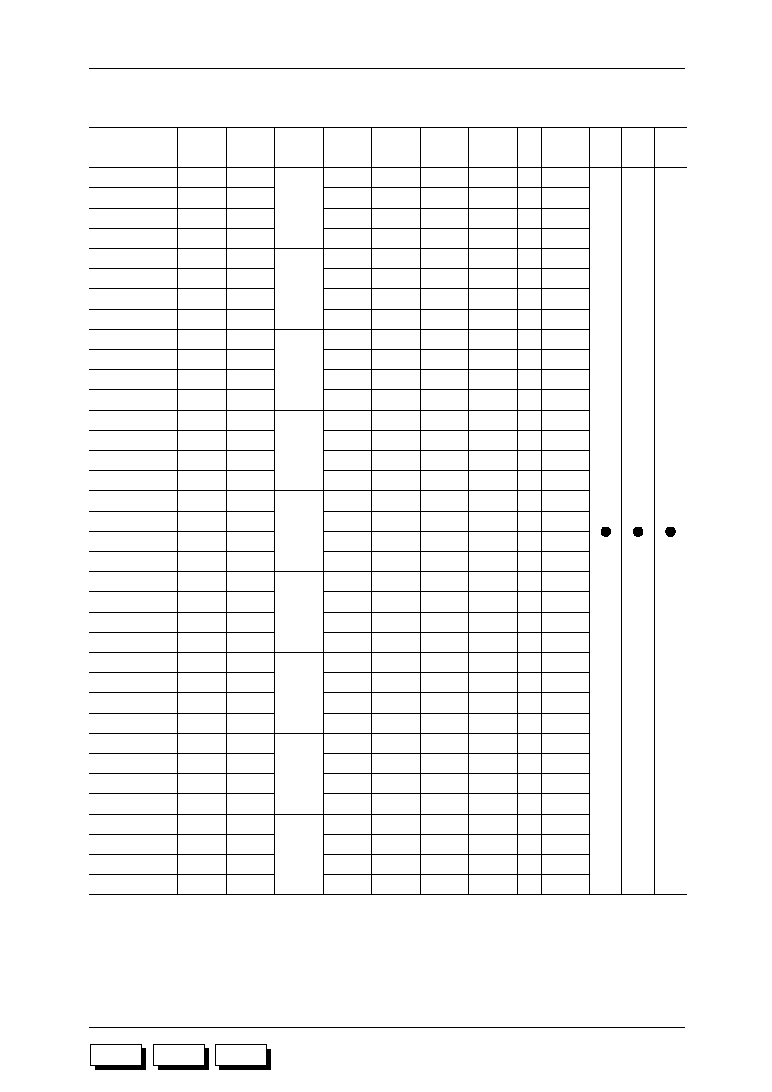

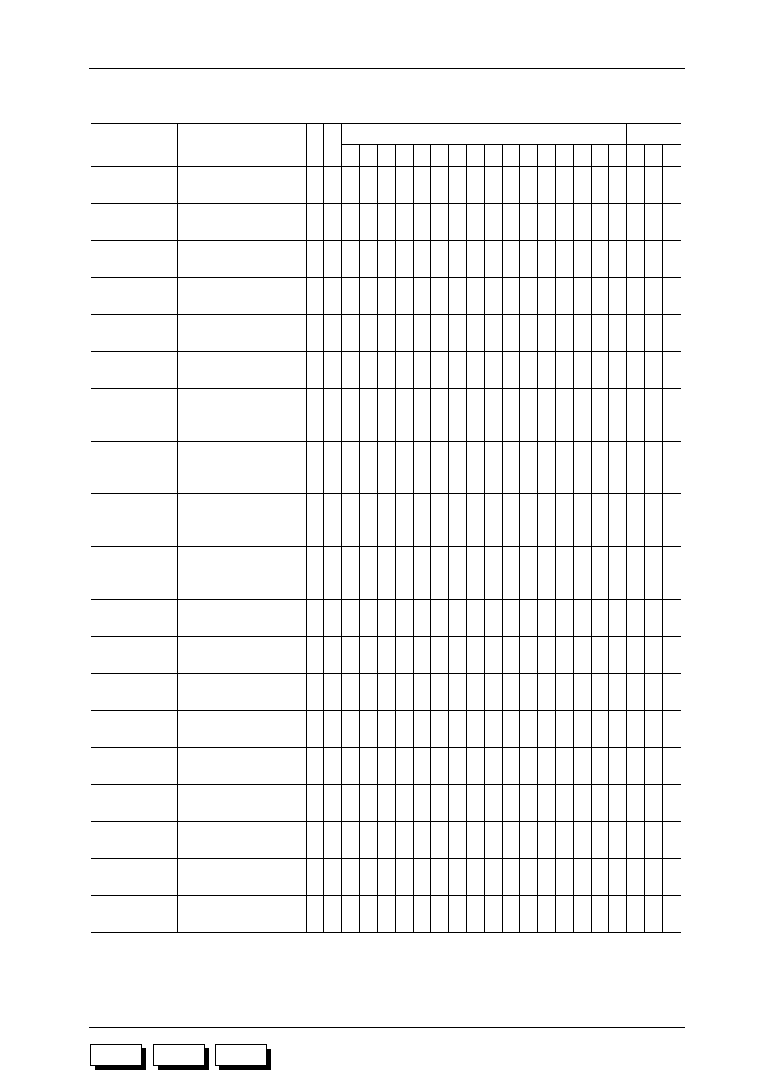

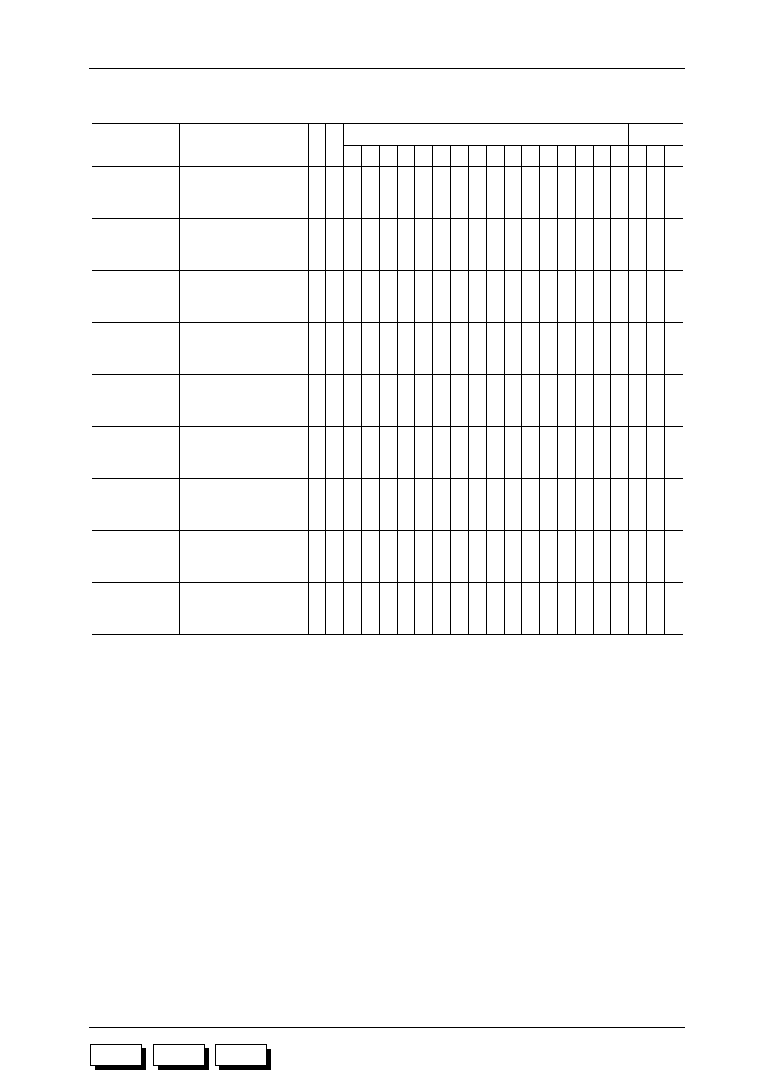

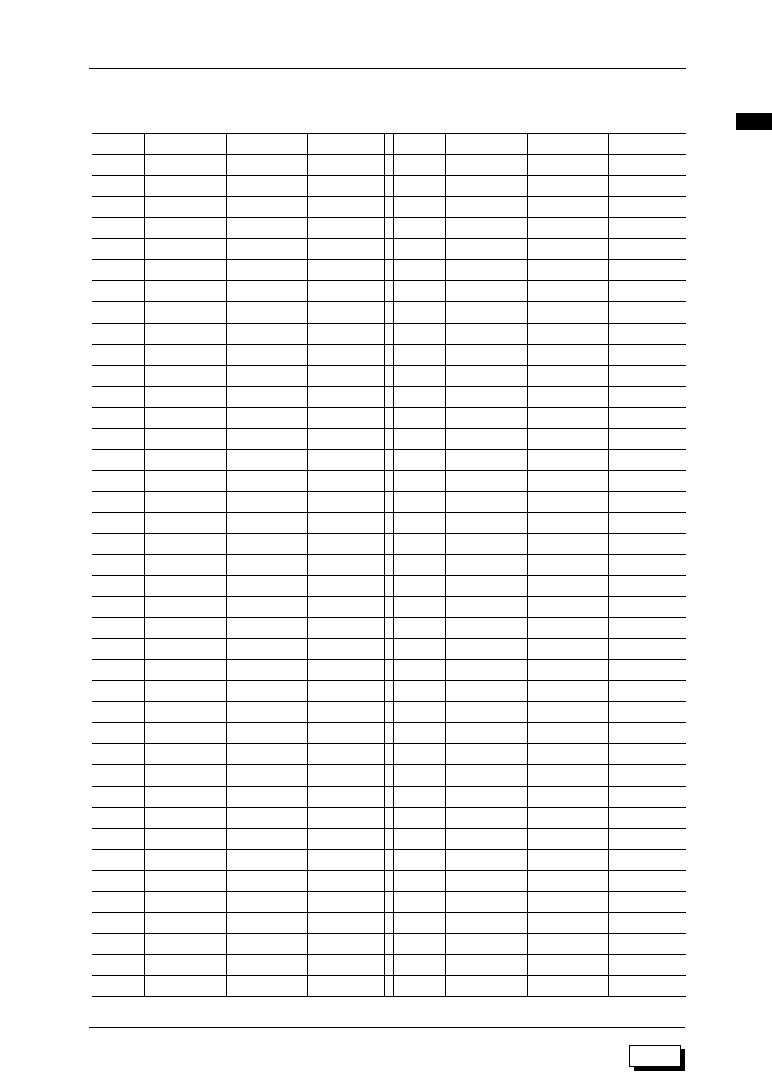

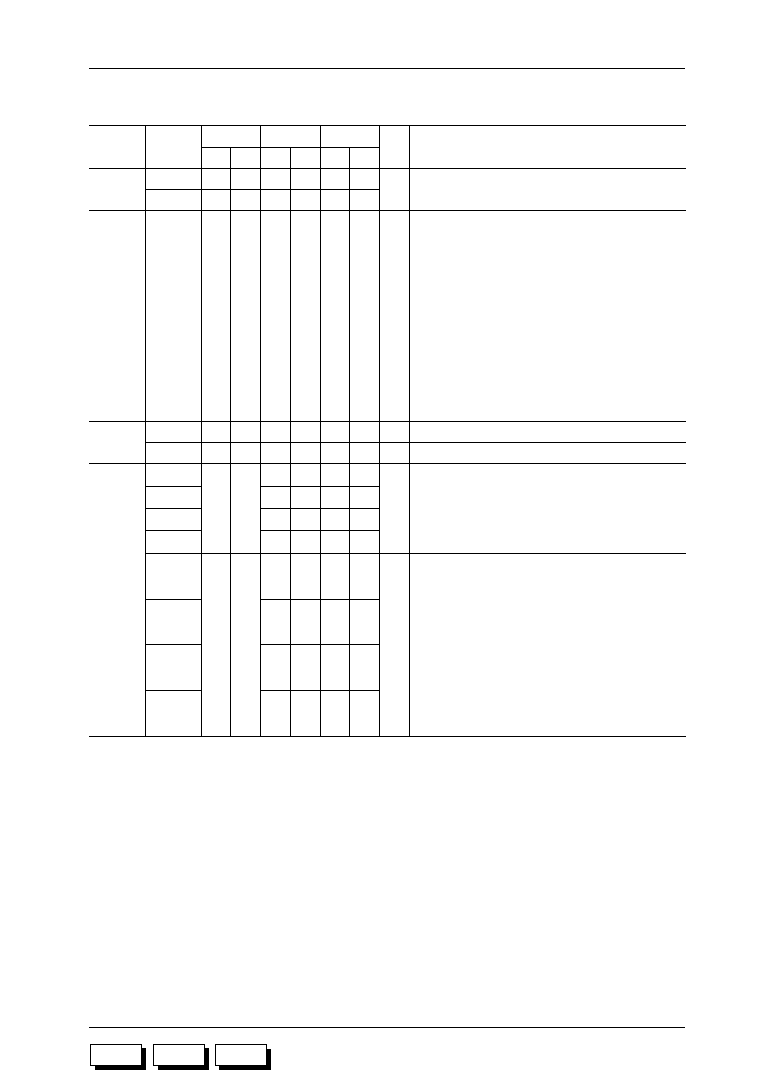

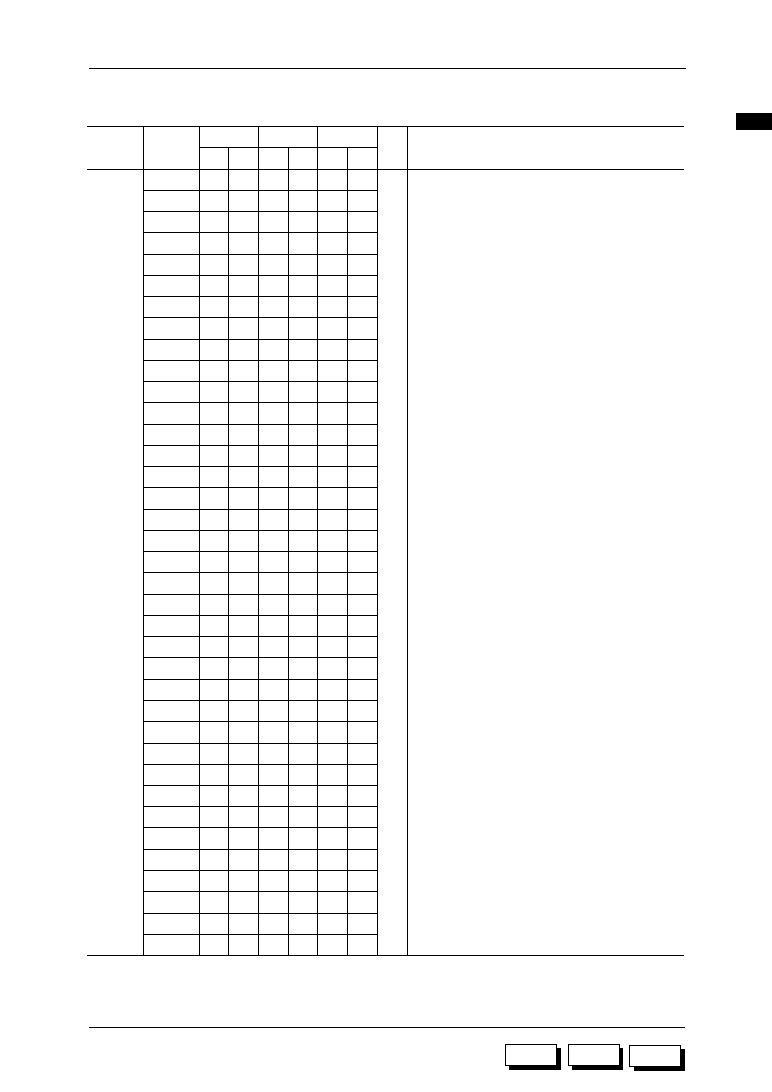

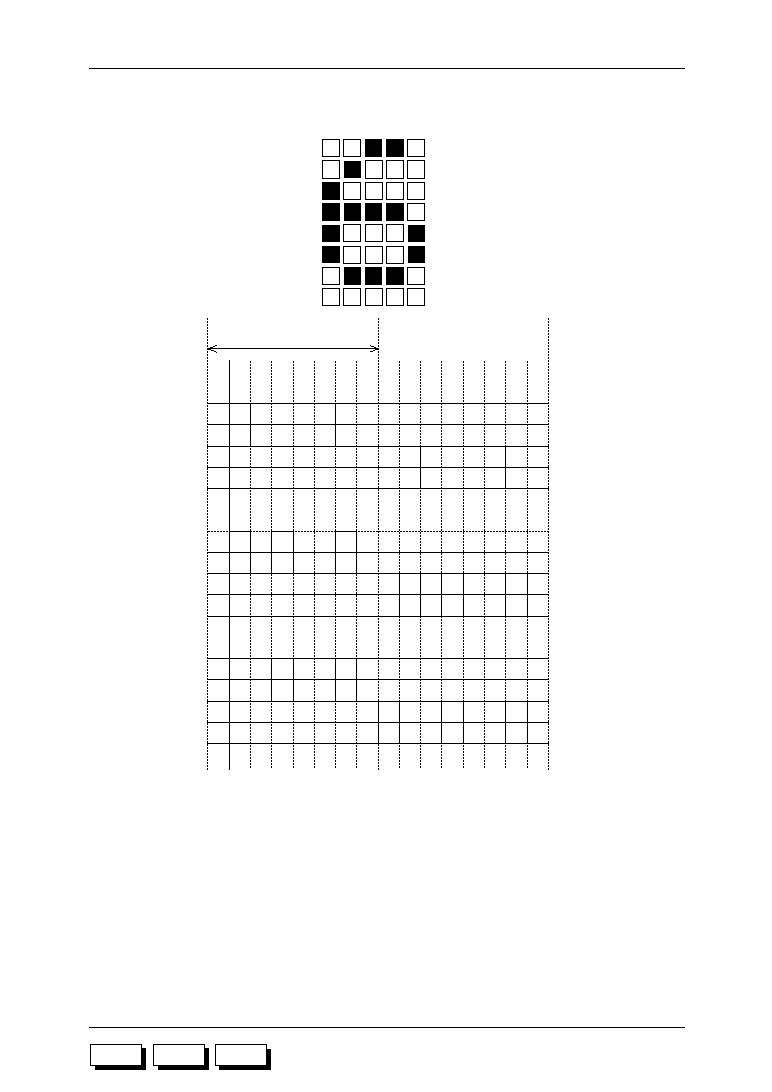

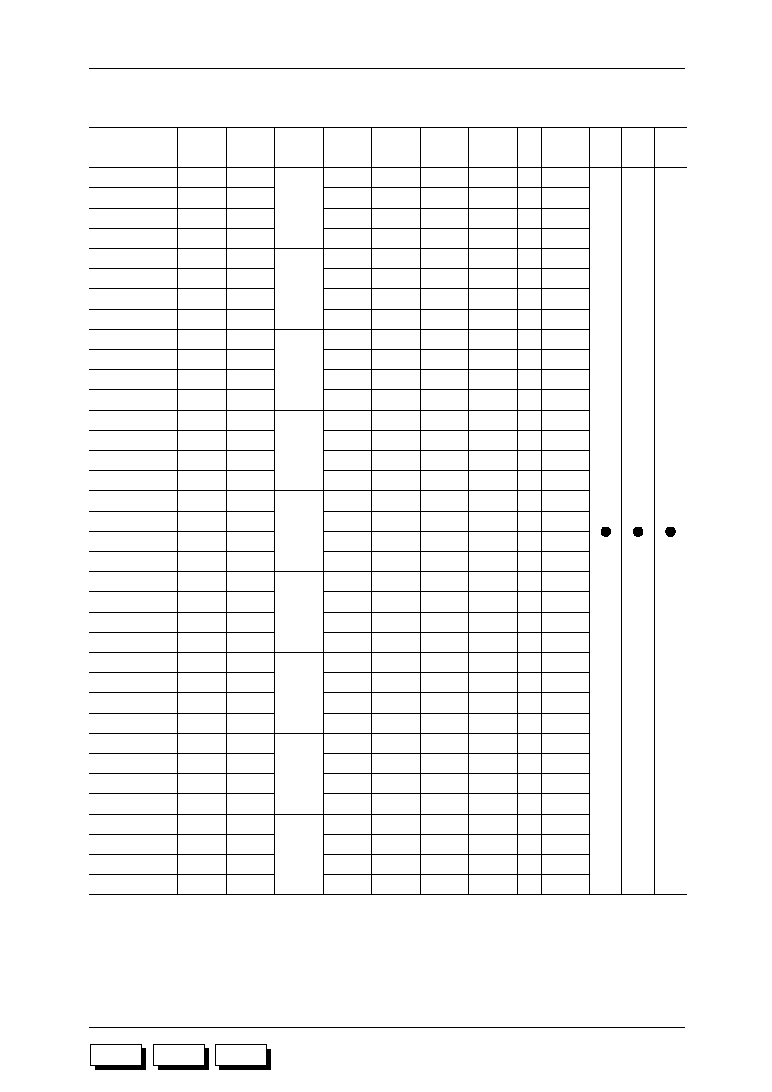

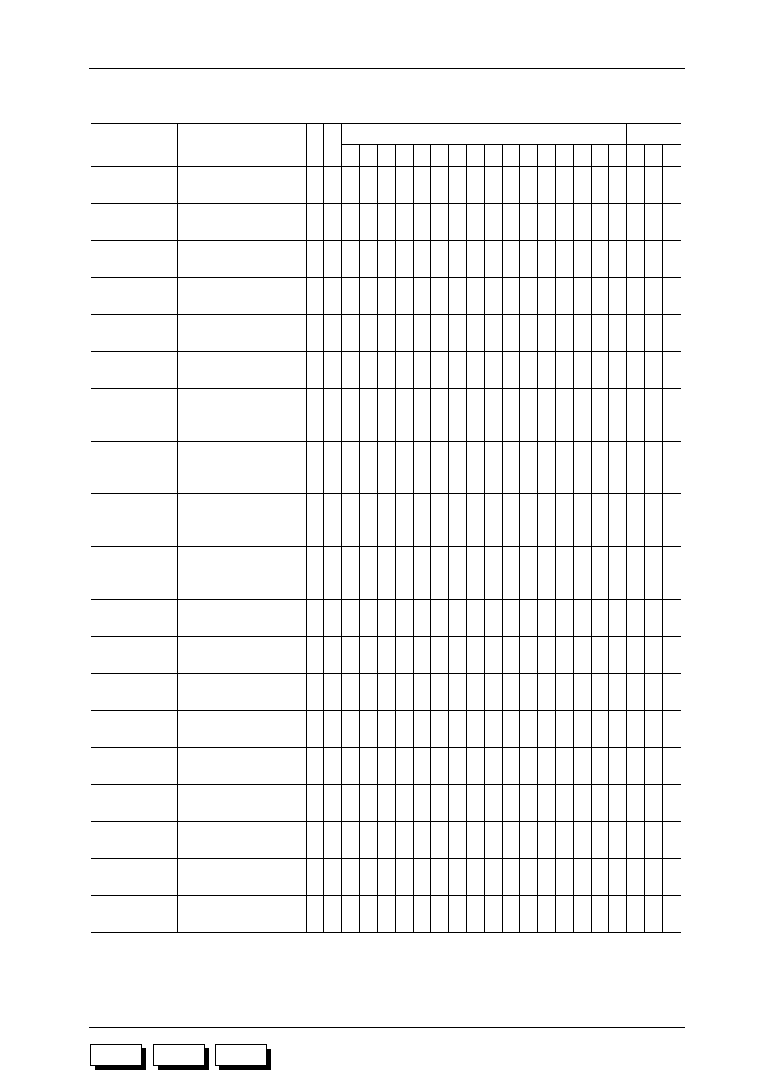

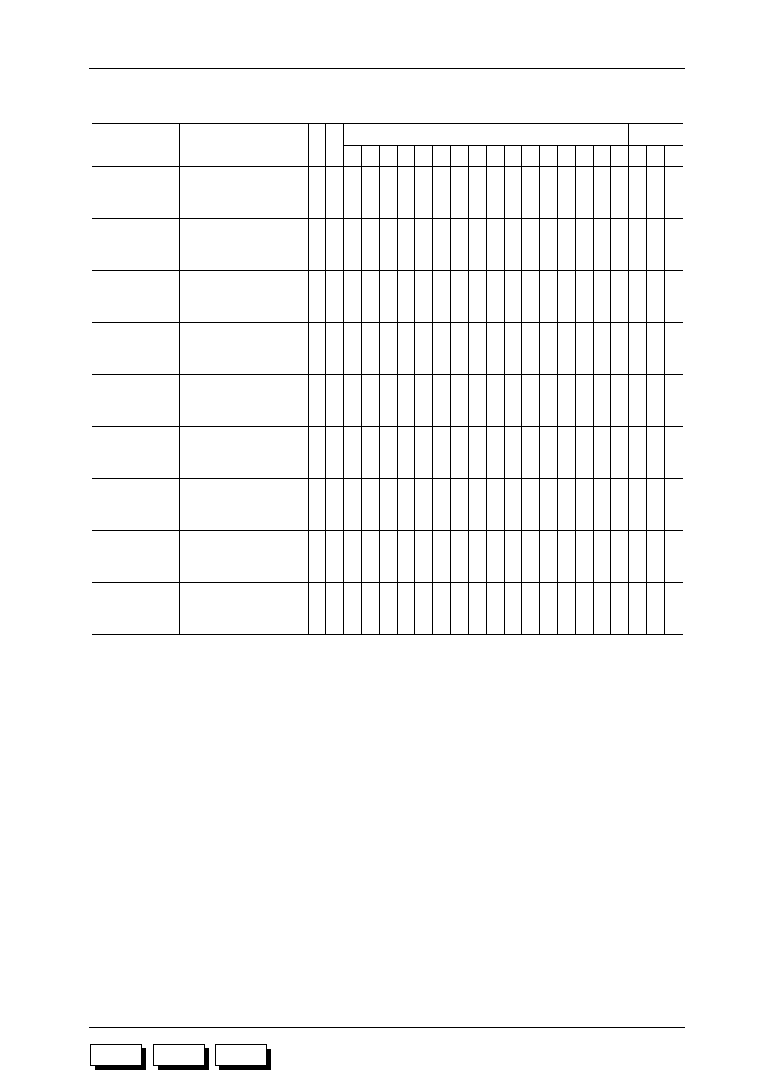

Table 1-3 ML63189B Pad Coordinates

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

≠2259

≠1895

≠1755

≠1615

≠1474

≠1334

≠1193

≠1053

≠913

≠772

≠632

≠491

≠351

≠211

≠70

70

211

351

491

632

772

913

1053

1193

1334

1474

1615

1755

1895

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

Y (

mm)

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2438

≠2176

≠2036

≠1895

≠1755

≠1615

≠1474

≠1334

≠1193

≠1053

≠913

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

V

SS

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDH

CB1

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

2259

1895

1755

1615

1474

1334

1193

1053

913

772

632

491

351

211

70

≠70

≠211

≠351

≠772

≠632

≠491

≠351

≠211

≠70

70

211

351

491

632

772

913

1053

1193

1334

1474

1615

1755

1895

2036

2176

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

M189B

1-16

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

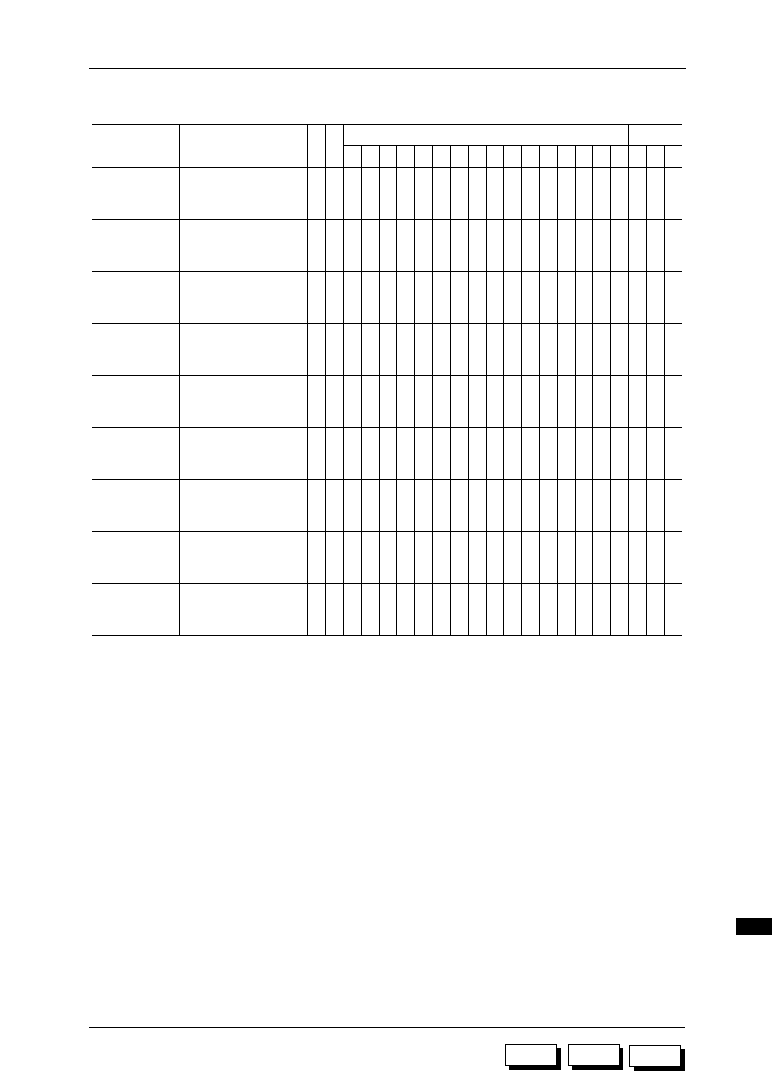

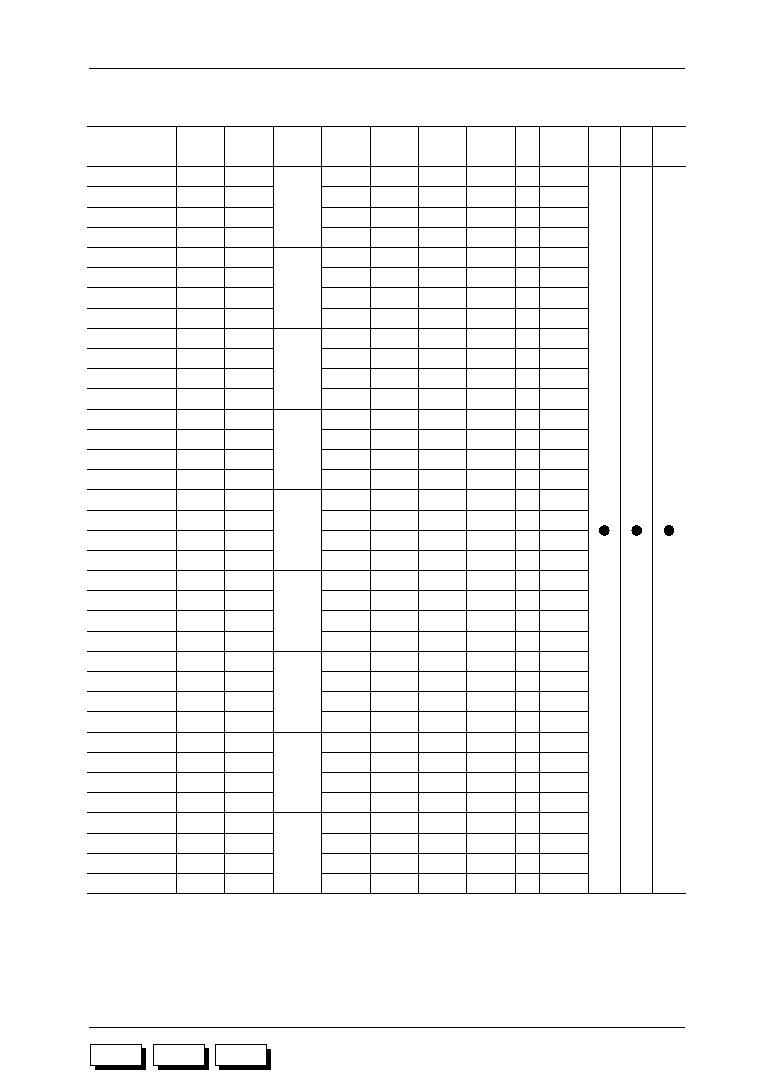

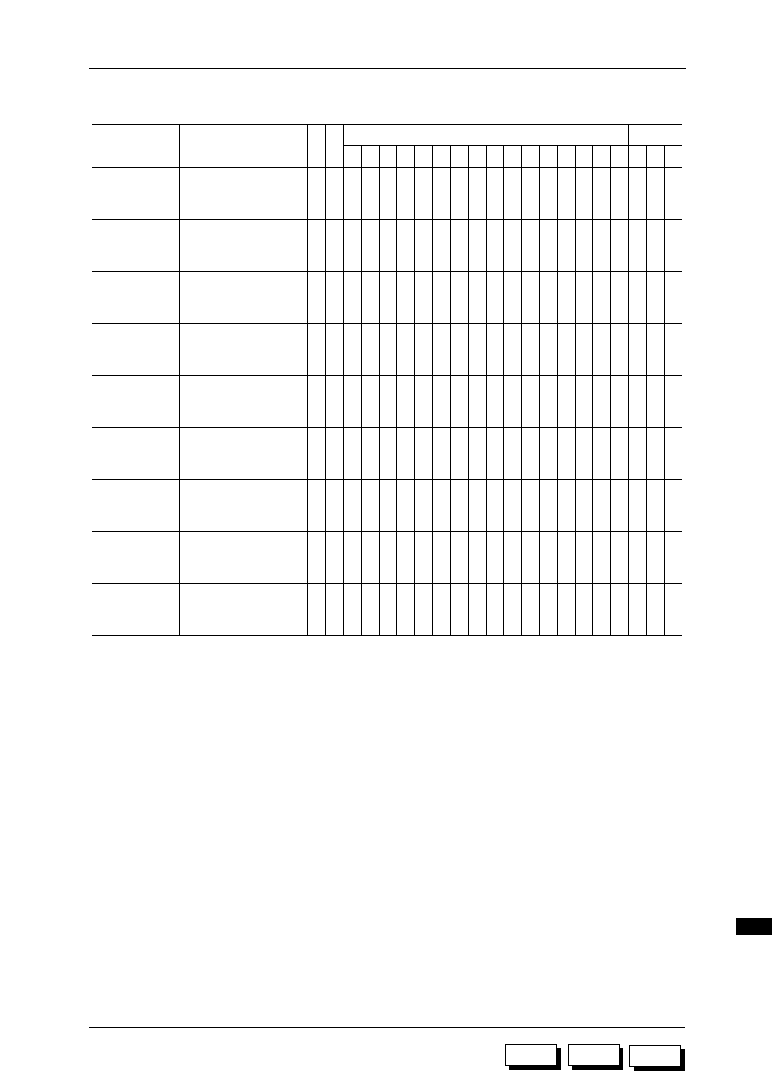

Table 1-3 ML63189B Pad Coordinates (continued)

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

CB2

V

DD

V

DDL

OSC1

OSC0

RESET

XT1

XT0

TST1

TST2

MD

MDB

V

DDI

PE.0

PE.1

PE.2

PE.3

PB.0

PB.1

PB.2

PB.3

PA.0

≠491

≠632

≠772

≠913

≠1053

≠1193

≠1334

≠1474

≠1615

≠1755

≠1895

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

2438

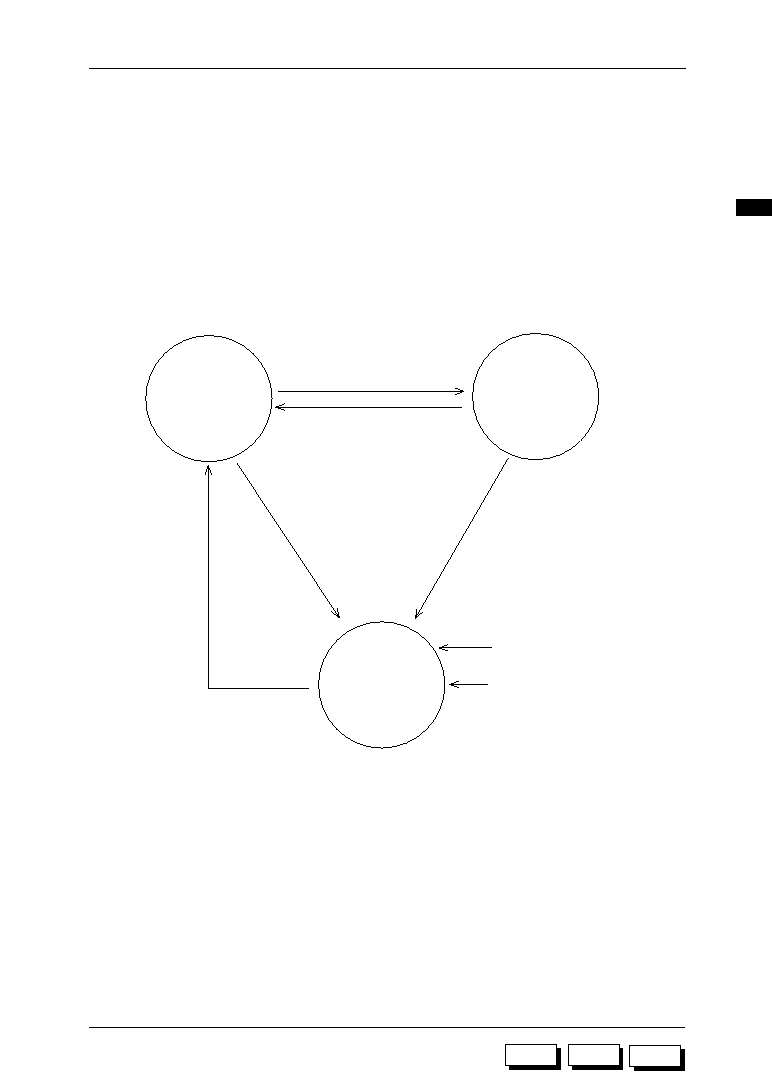

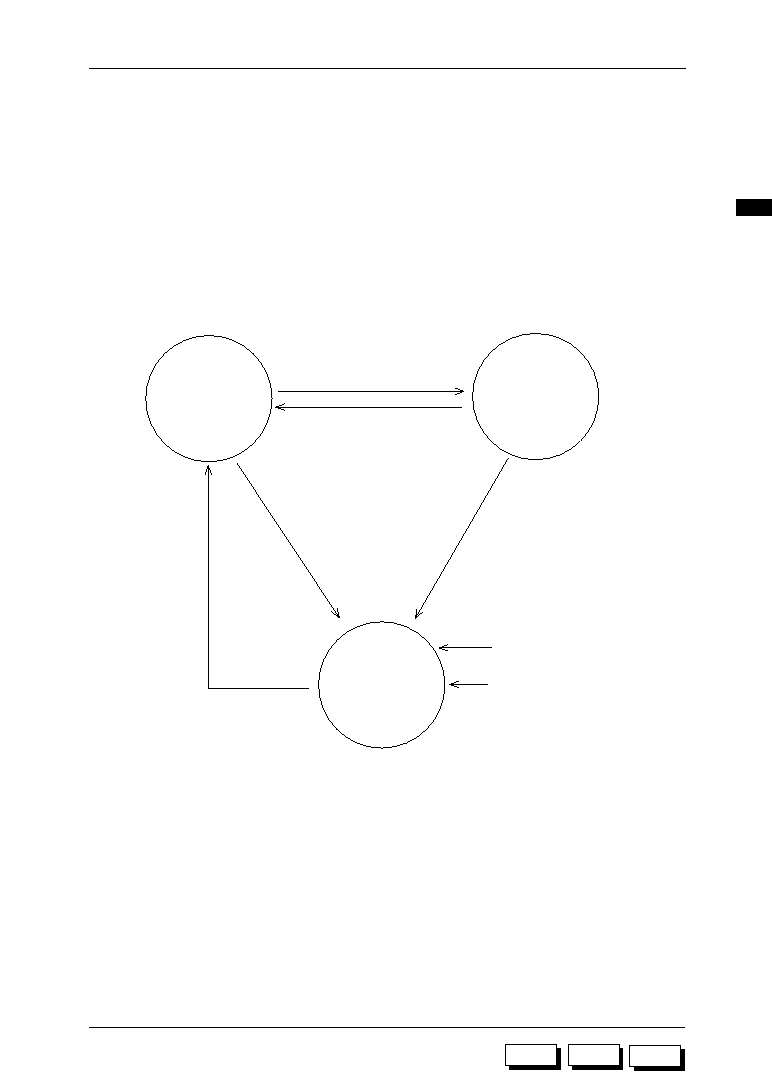

2132

1895

1755

1615

1474

1334

1193

1053

913

772

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

PA.1

PA.2

PA.3

P9.0

P9.1

P9.2

P9.3

P0.0

P0.1

P0.2

P0.3

COM1

COM2

COM3

COM4

COM5

COM6

COM7

COM8

SEG0

SEG1

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

≠2259

632

491

351

211

70

≠70

≠211

≠351

≠491

≠632

≠772

≠913

≠1053

≠1193

≠1334

≠1474

≠1615

≠1755

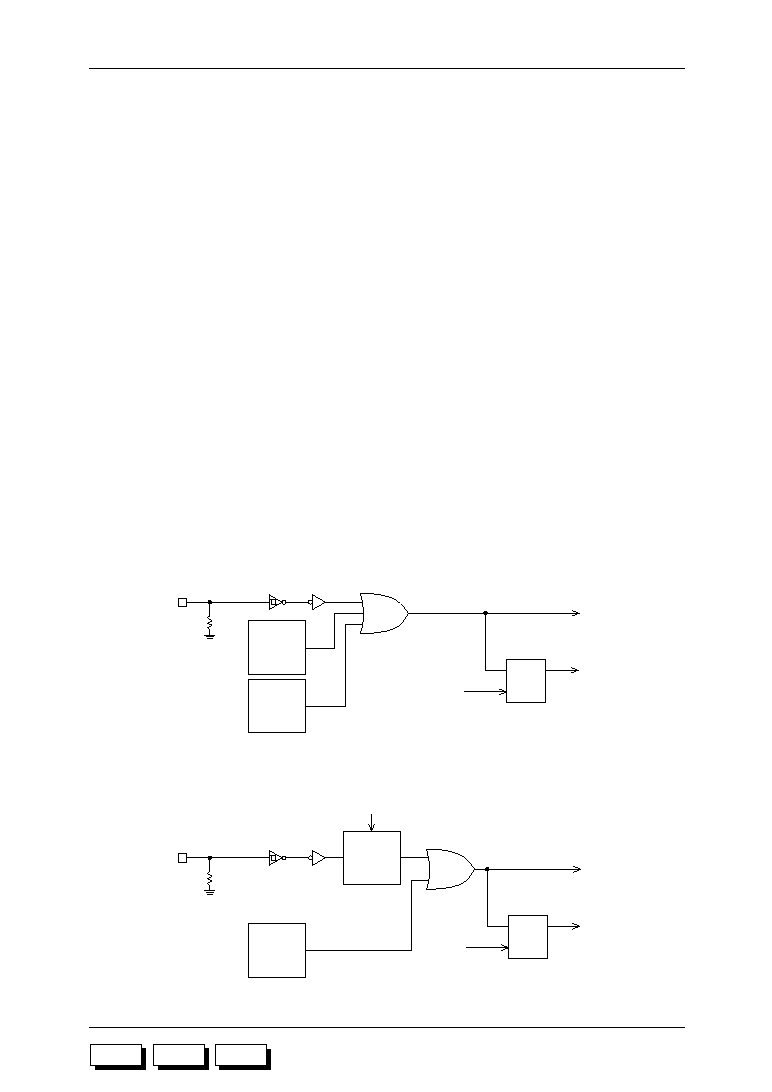

≠1895

≠2036

≠2176

M189B

1-17

ML63187/189B/193 User's Manual

Chapter 1 Overview

1

M187

M189B

M193

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

(NC)

(NC)

SEG40

SEG41

SEG47

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

(NC)

(NC)

PE.2

PE.1

PE.0

V

DDI

MDB

MD

TST2

TST1

XT0

XT1

RESET

OSC0

OSC1

V

DDL

V

DD

CB2

CB1

V

DDH

C2

C1

V

DD5

V

DD4

V

DD3

V

DD2

(NC)

SEG7

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

COM8

COM7

COM6

COM5

COM4

COM3

COM2

COM1

V

SS

P0.3

P0.2

P0.1

PB.1

PB.0

(NC)

(NC)

SEG42

SEG43

SEG44

SEG45

SEG46

V

DD1

V

SS

P0.0

P9.3

P9.2

P9.1

P9.0

PA.3

PA.2

PA.1

PA.0

PB.3

PB.2

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

143

144

38

37

(NC)

(NC)

(NC)

(NC)

109

110

111

112

113

114

115

116

72

71

70

69

68

67

66

65

(NC)

(NC)

(NC)

PC.3

PC.2

PC.1

PC.0

PE.3

(NC)

(NC)

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

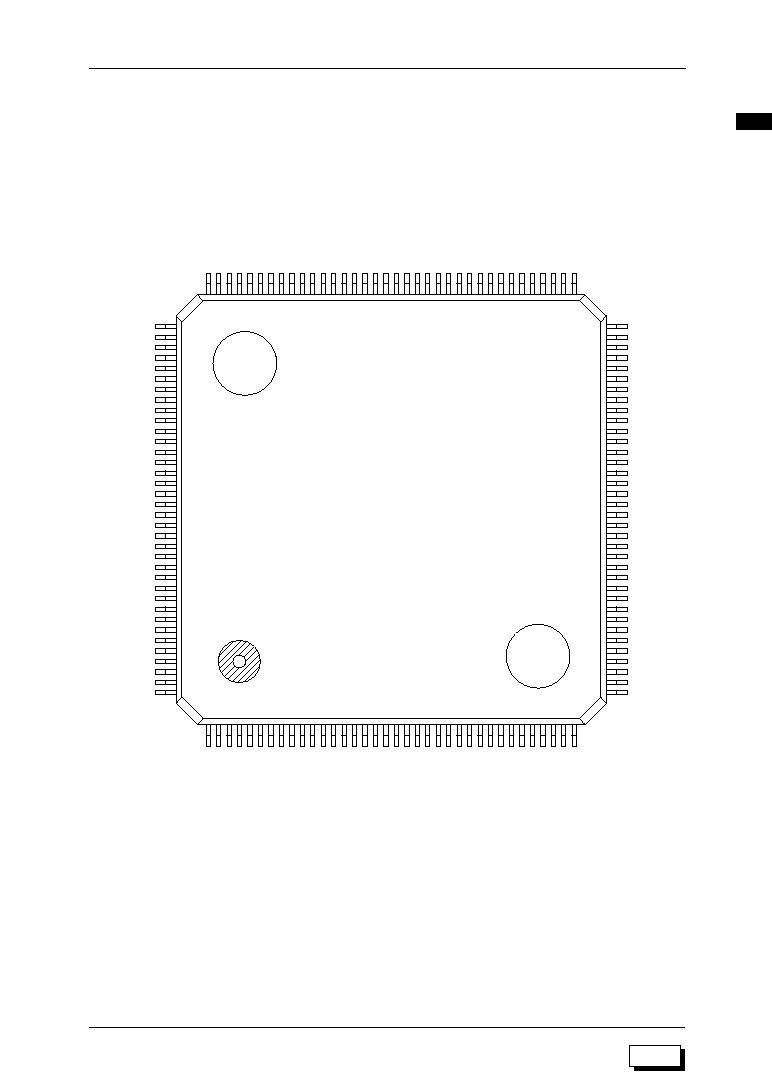

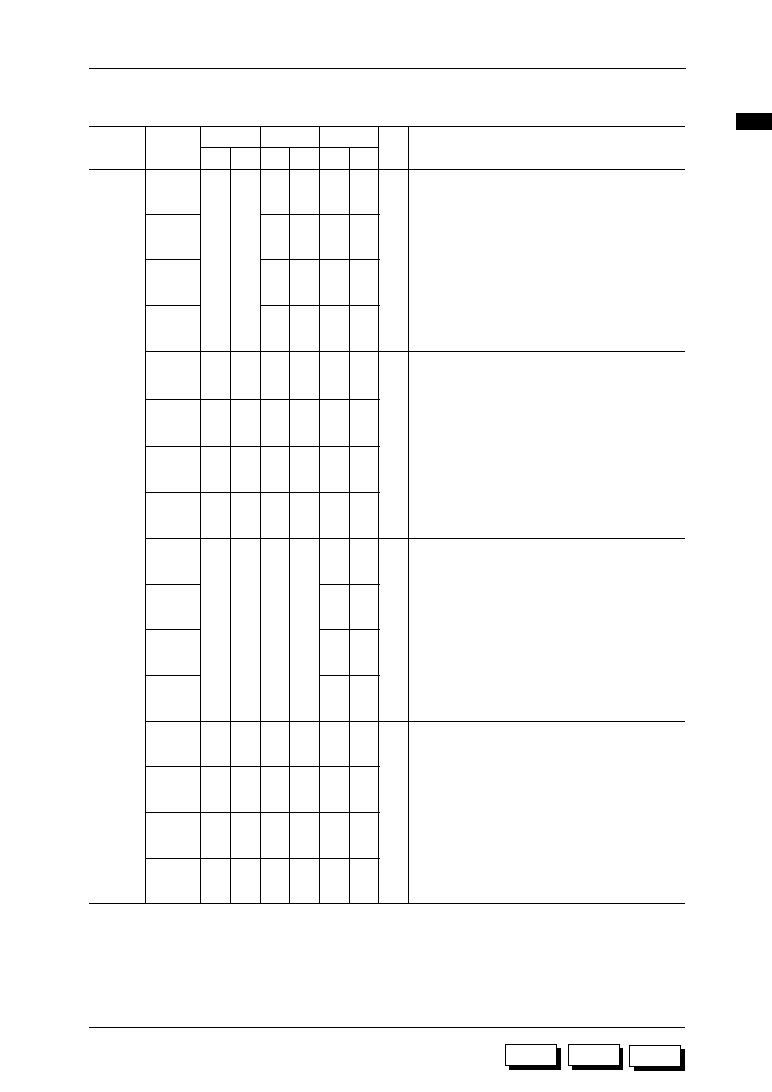

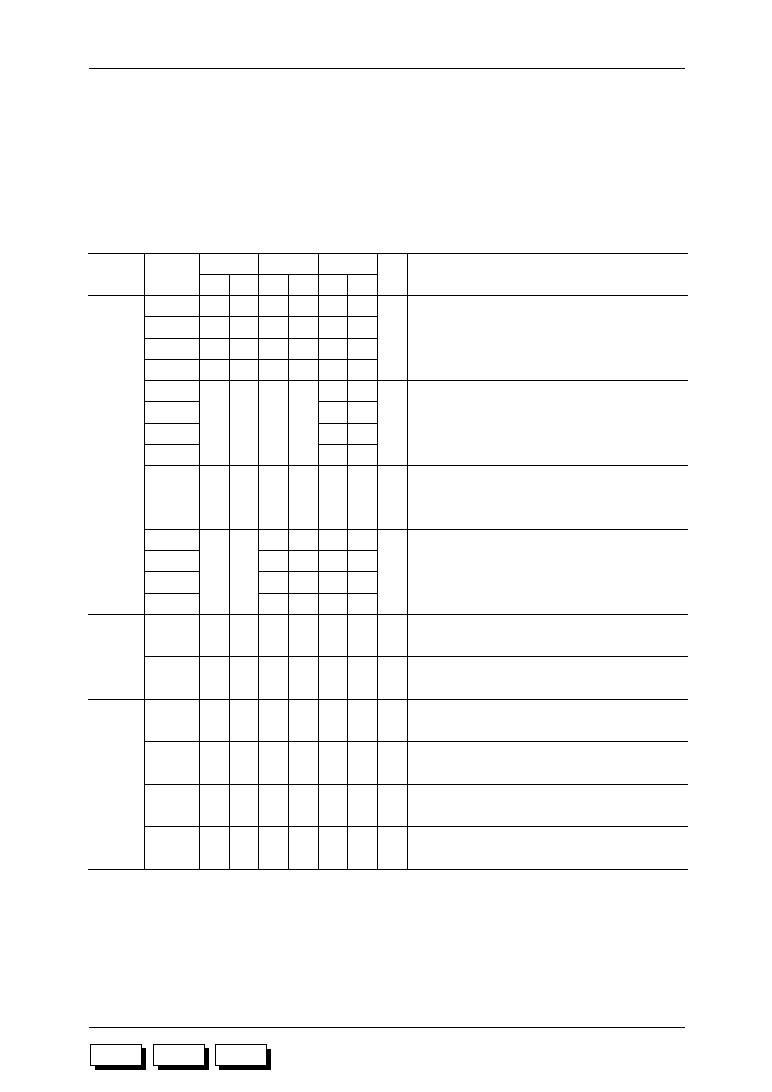

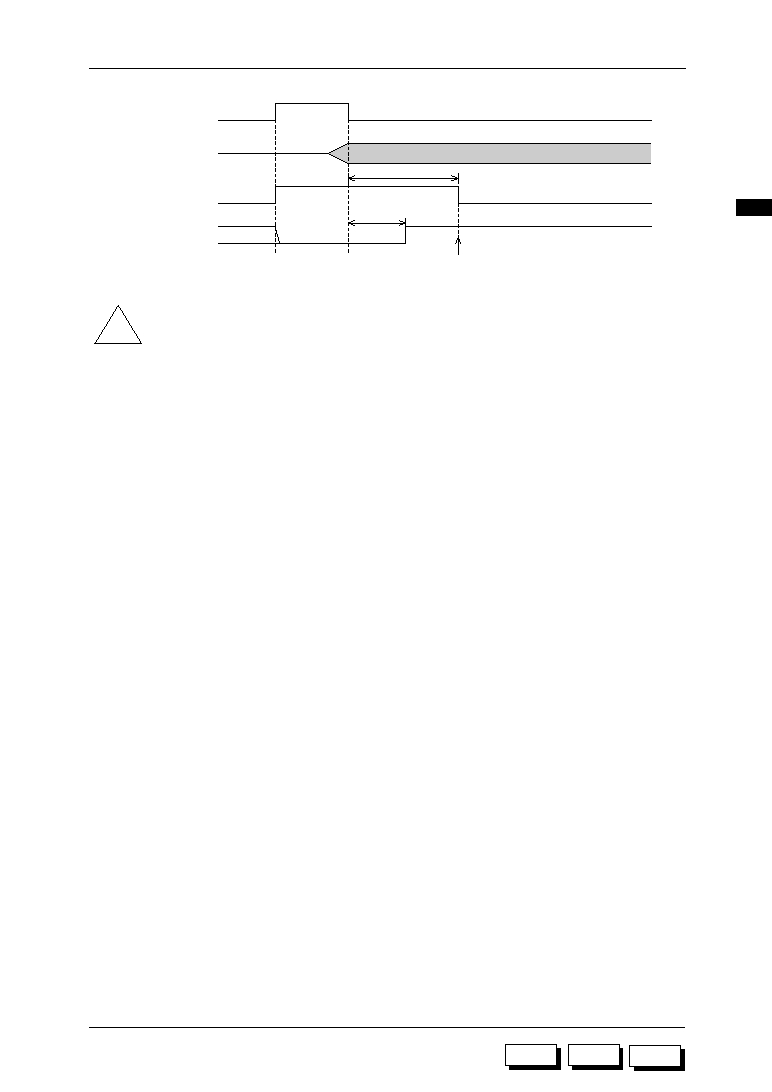

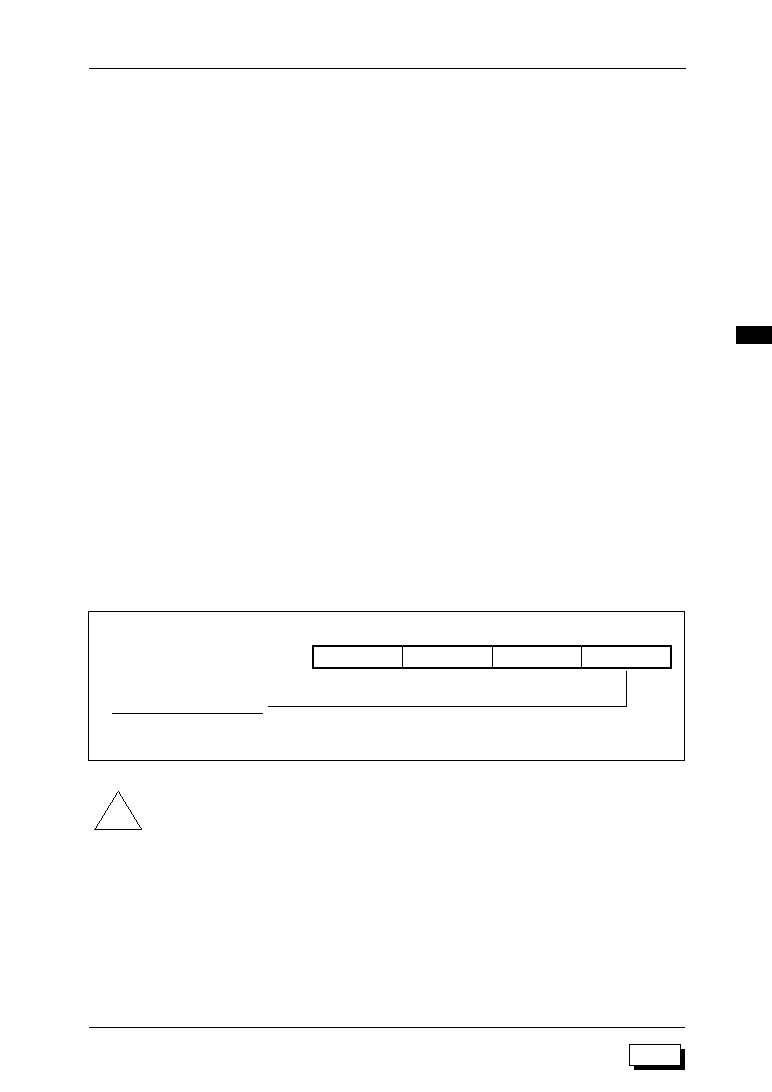

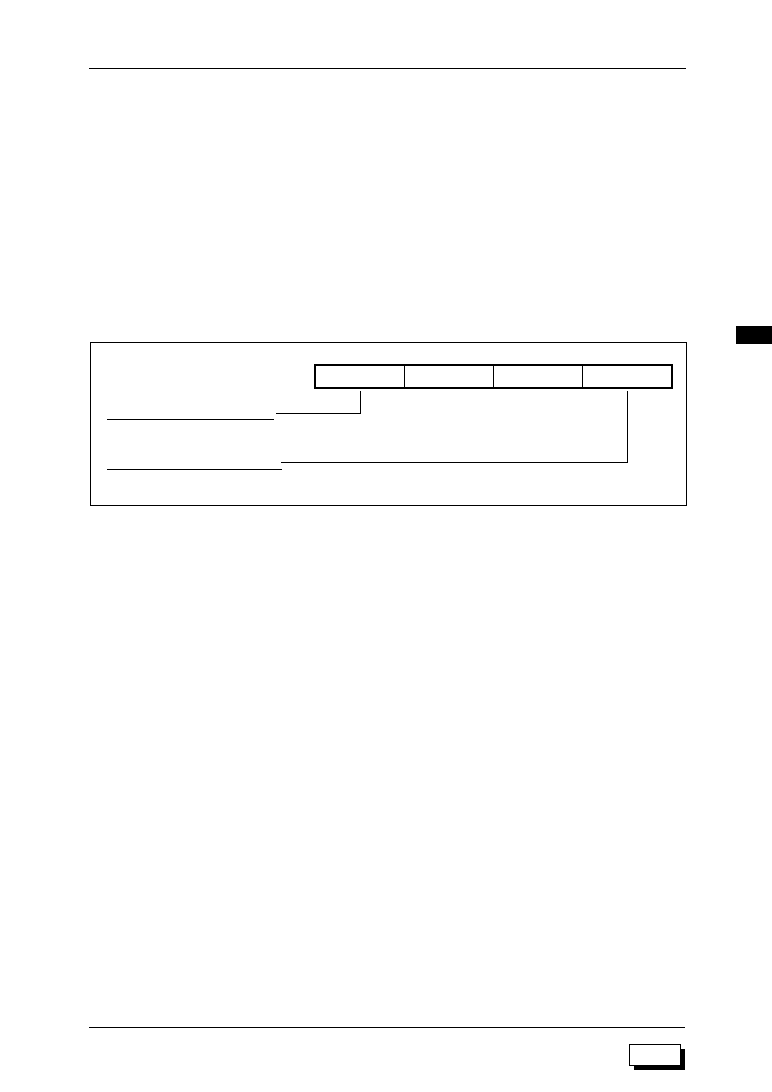

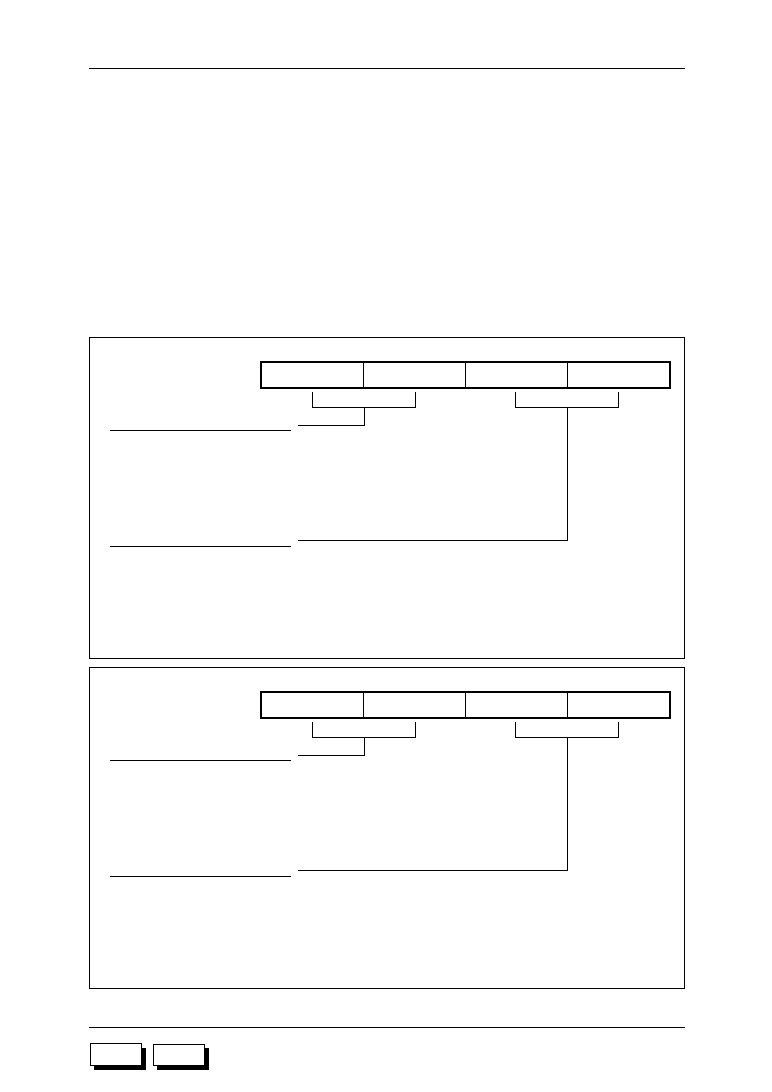

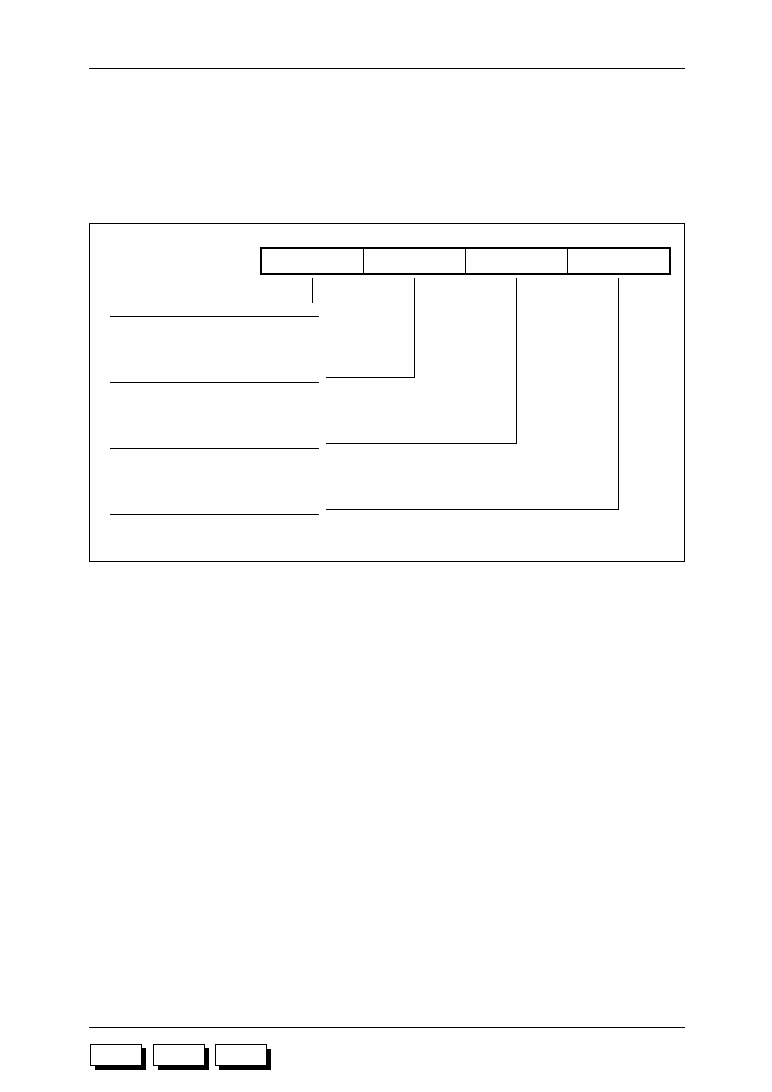

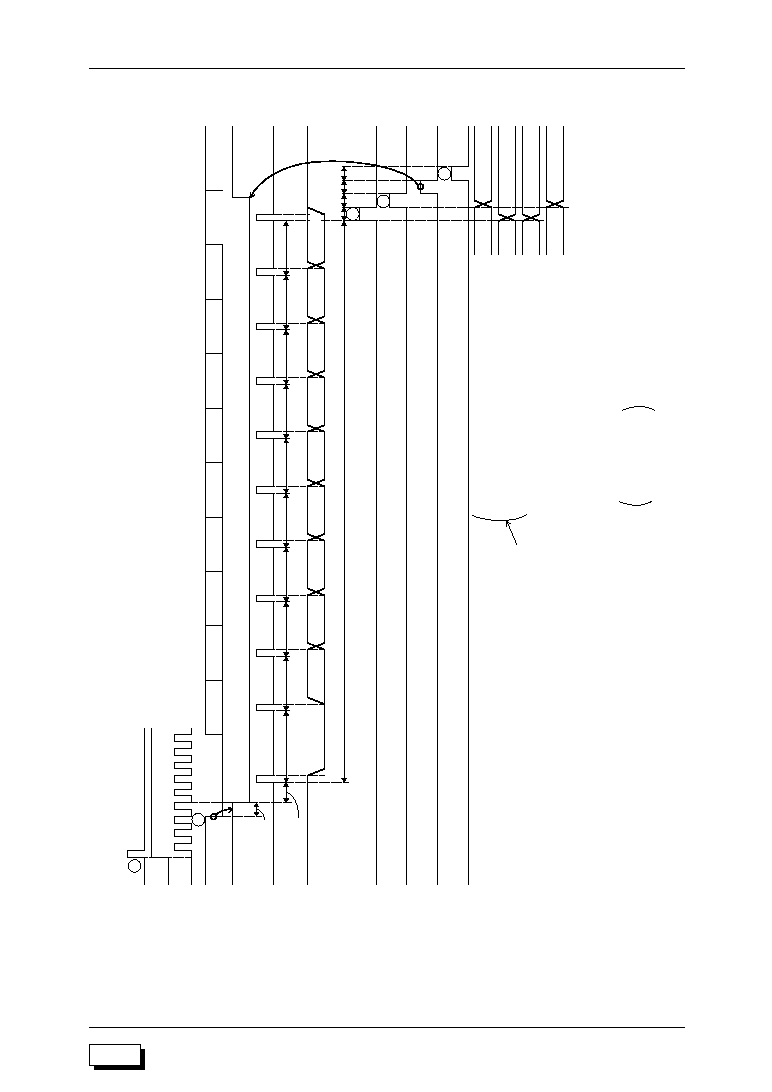

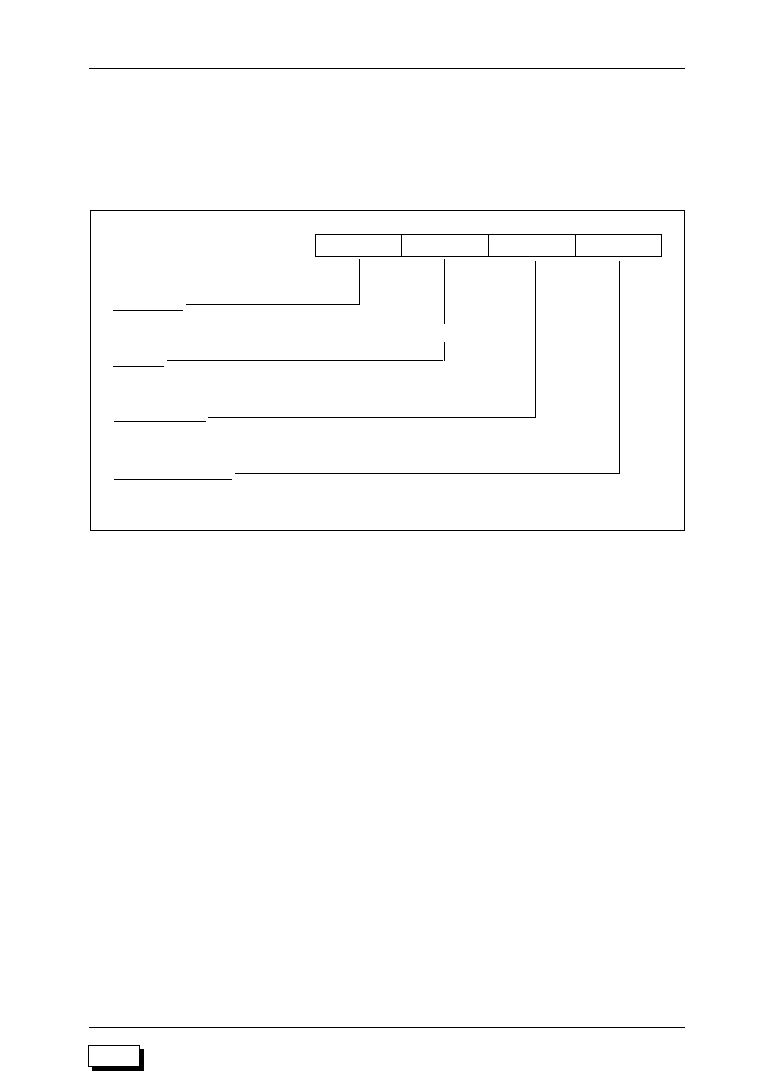

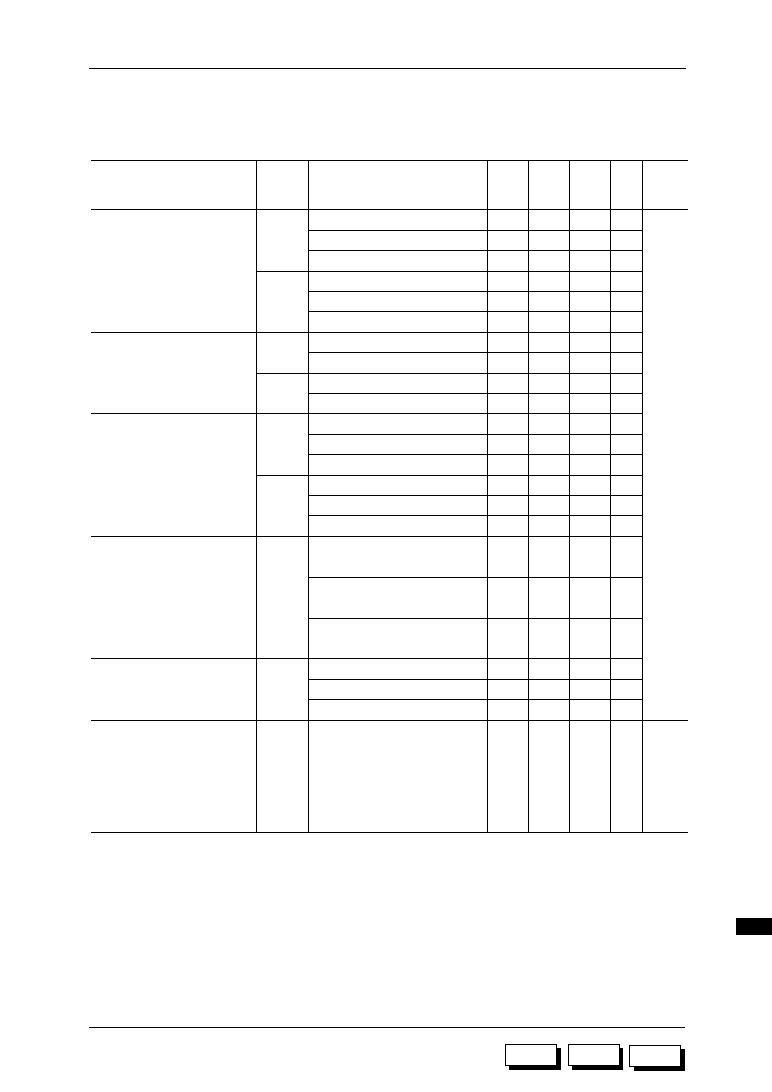

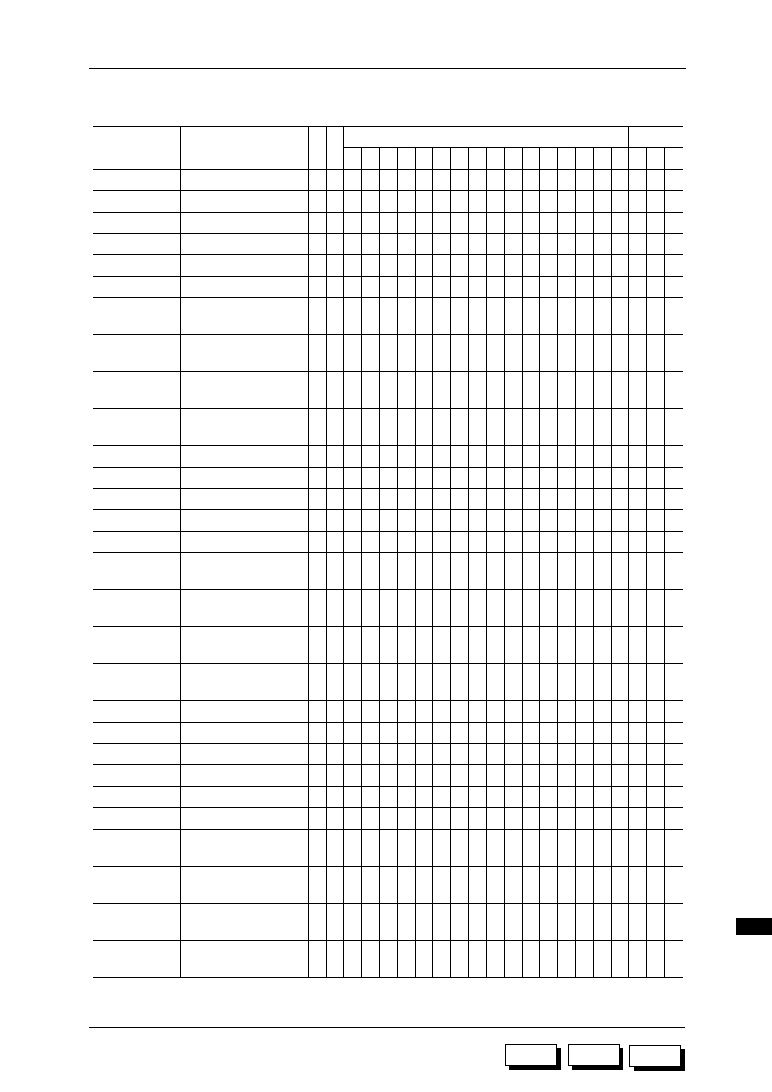

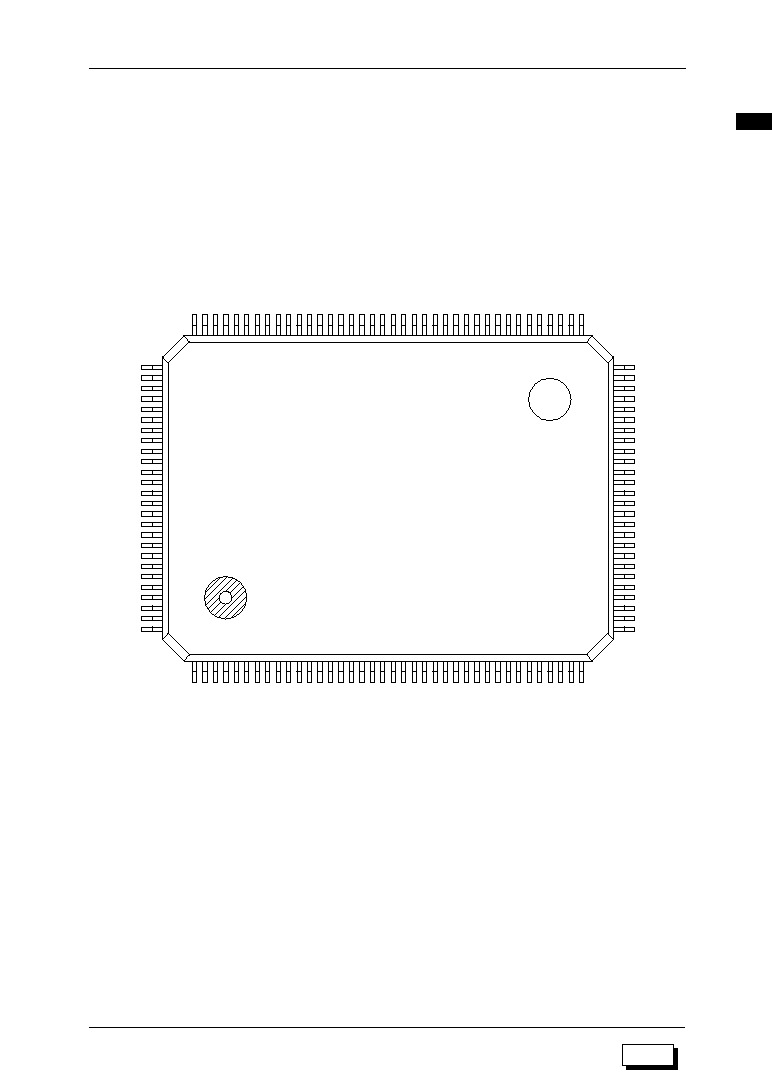

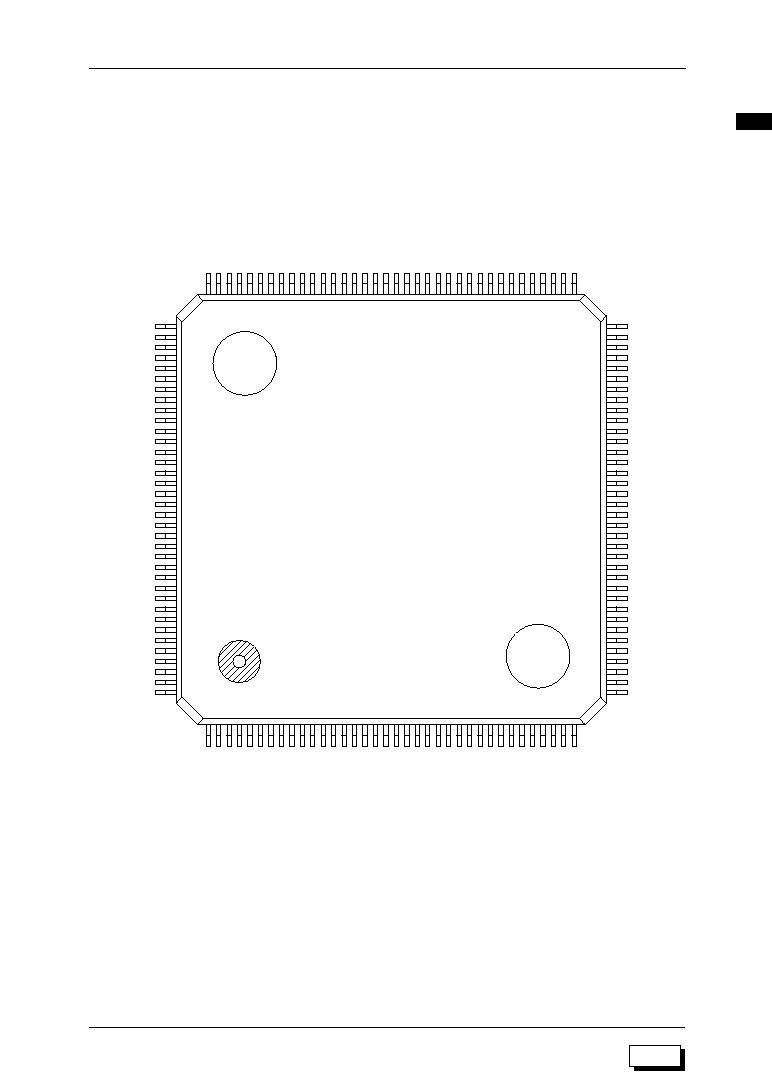

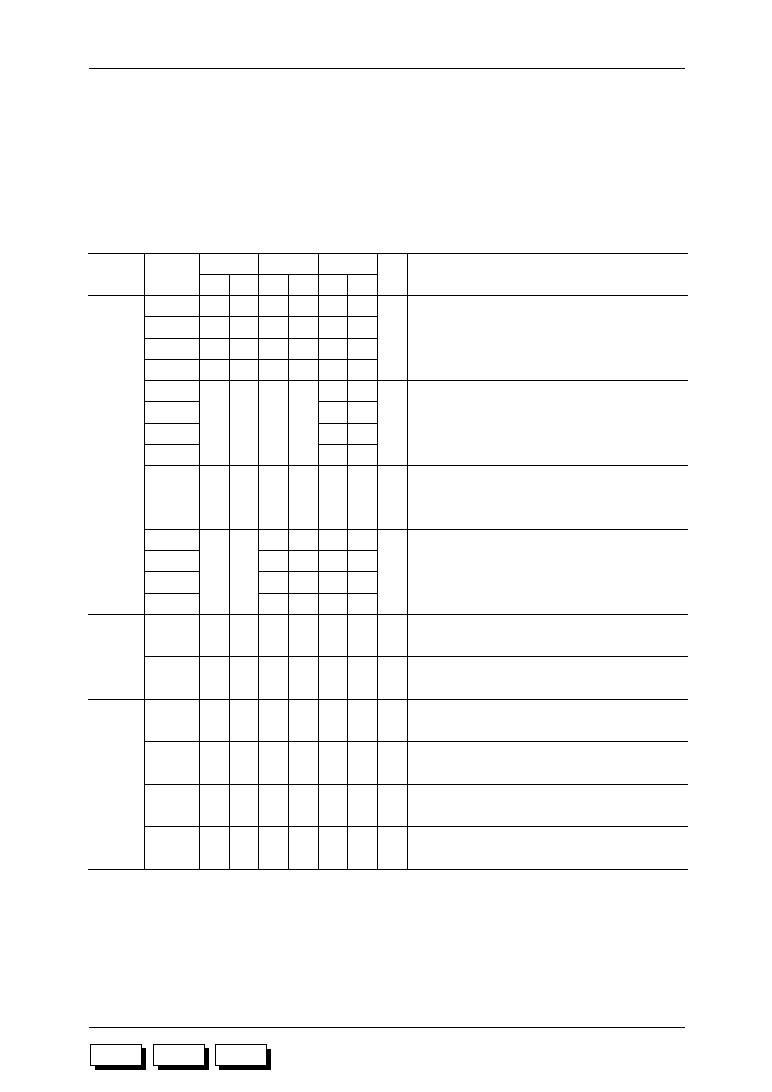

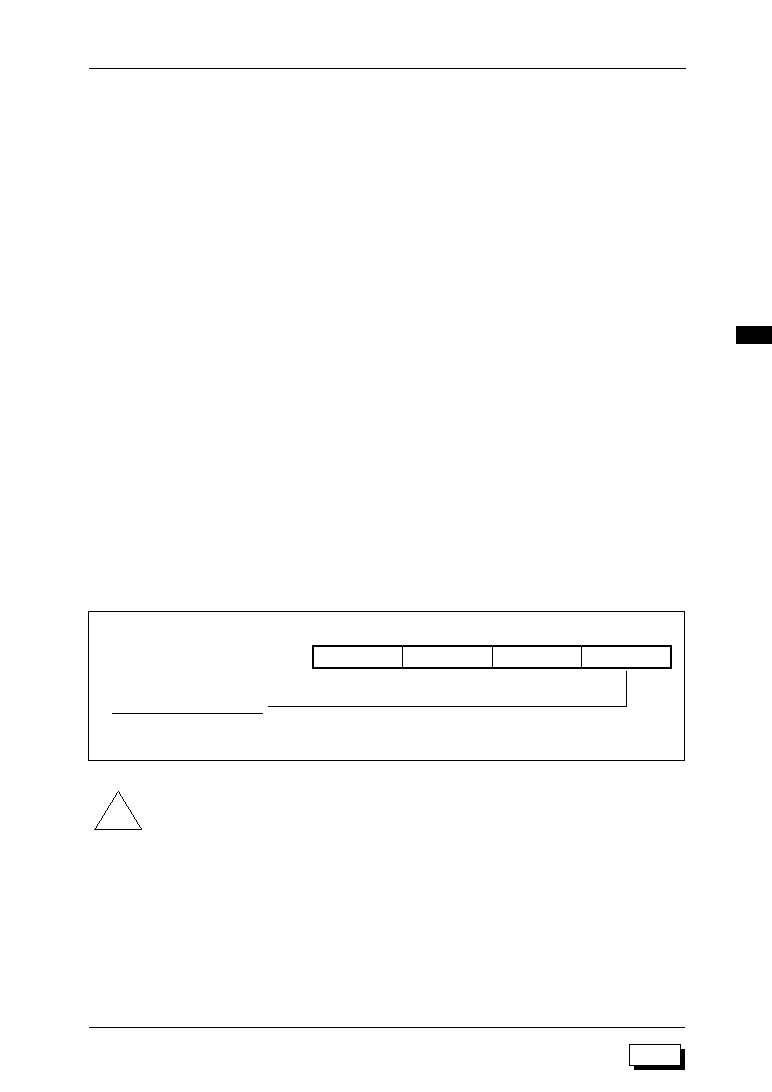

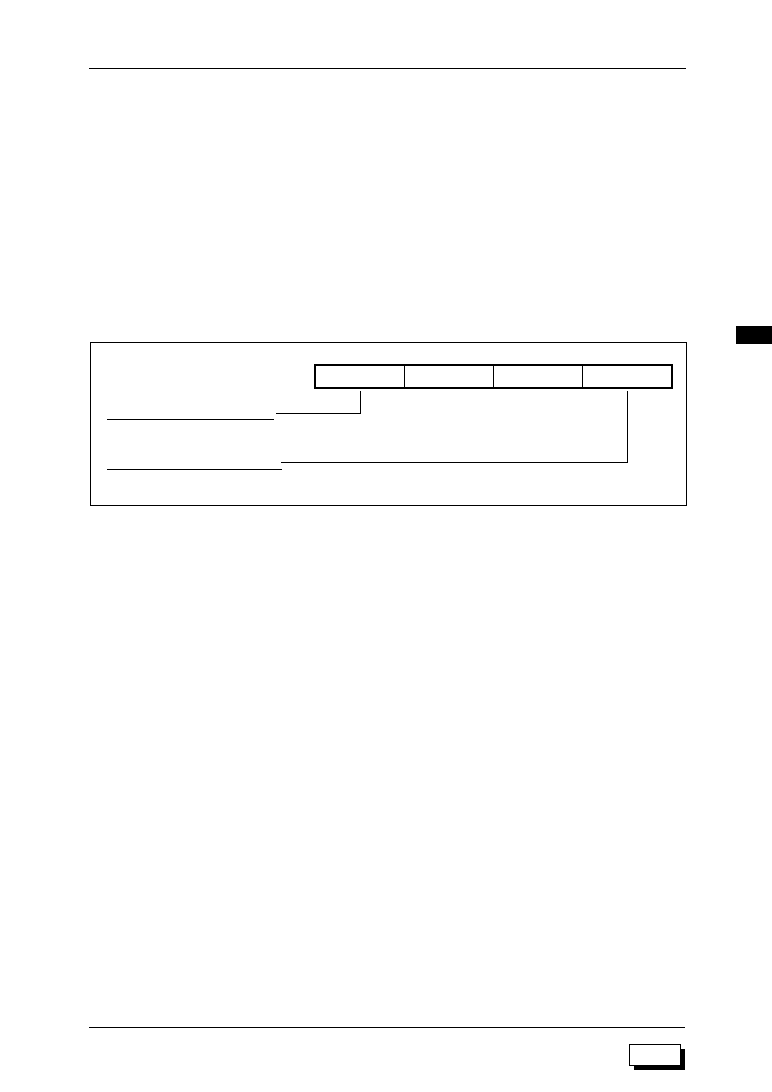

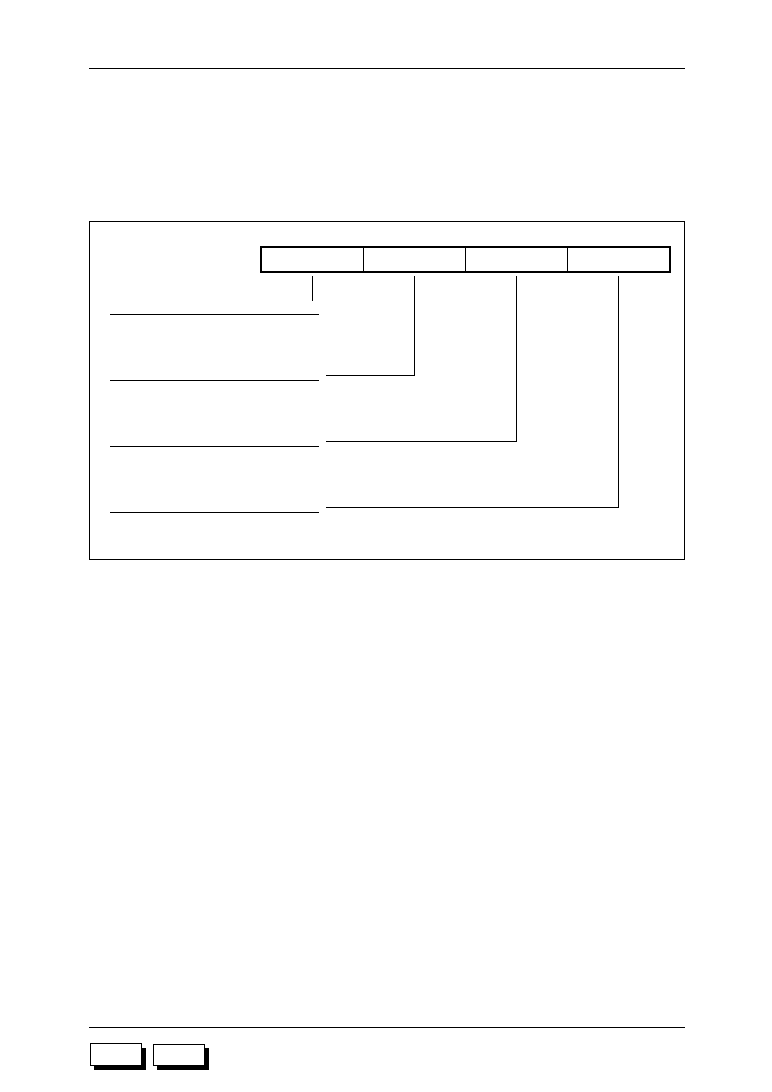

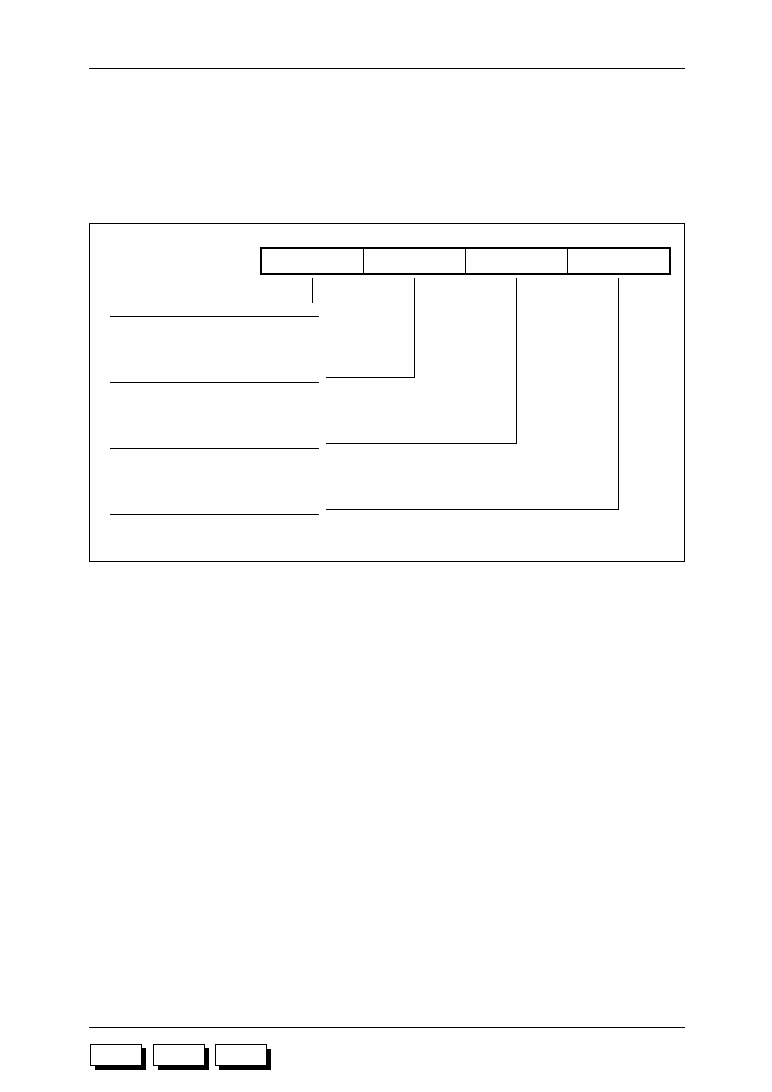

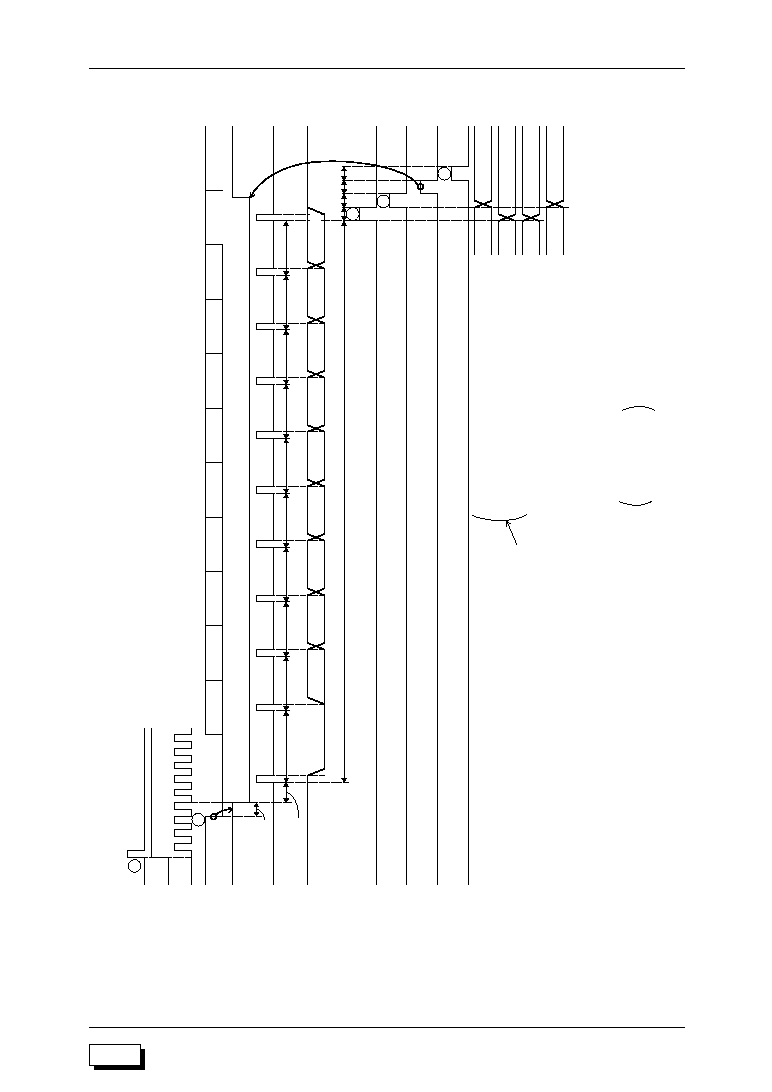

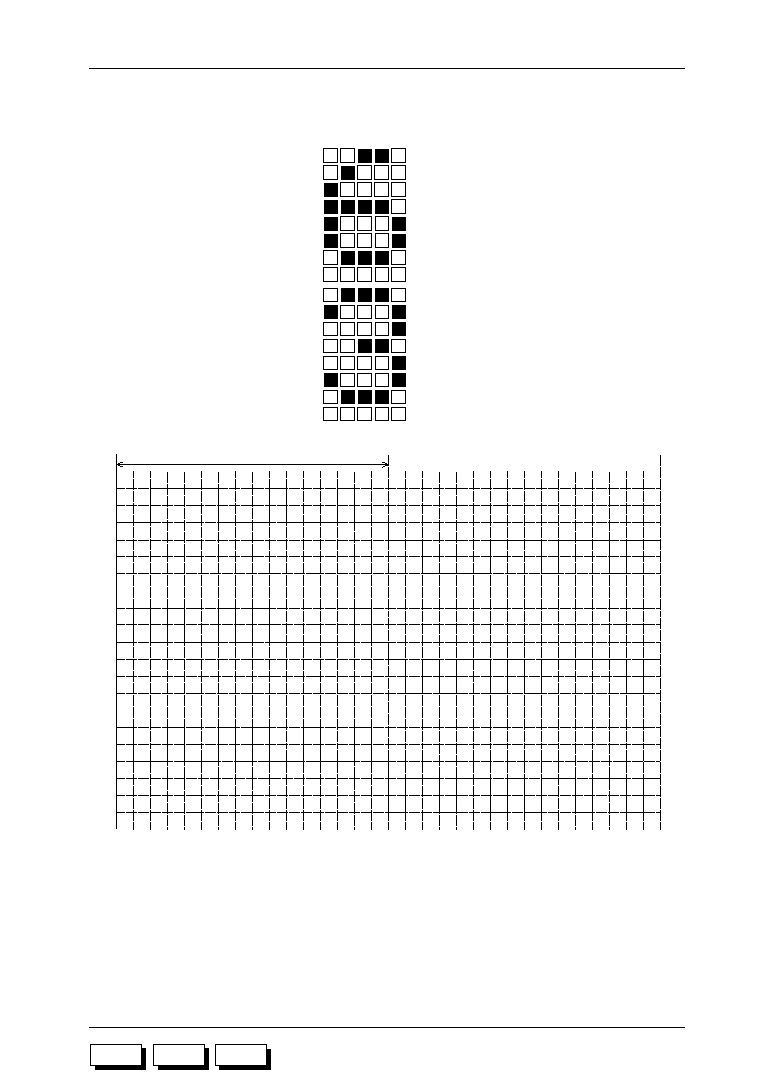

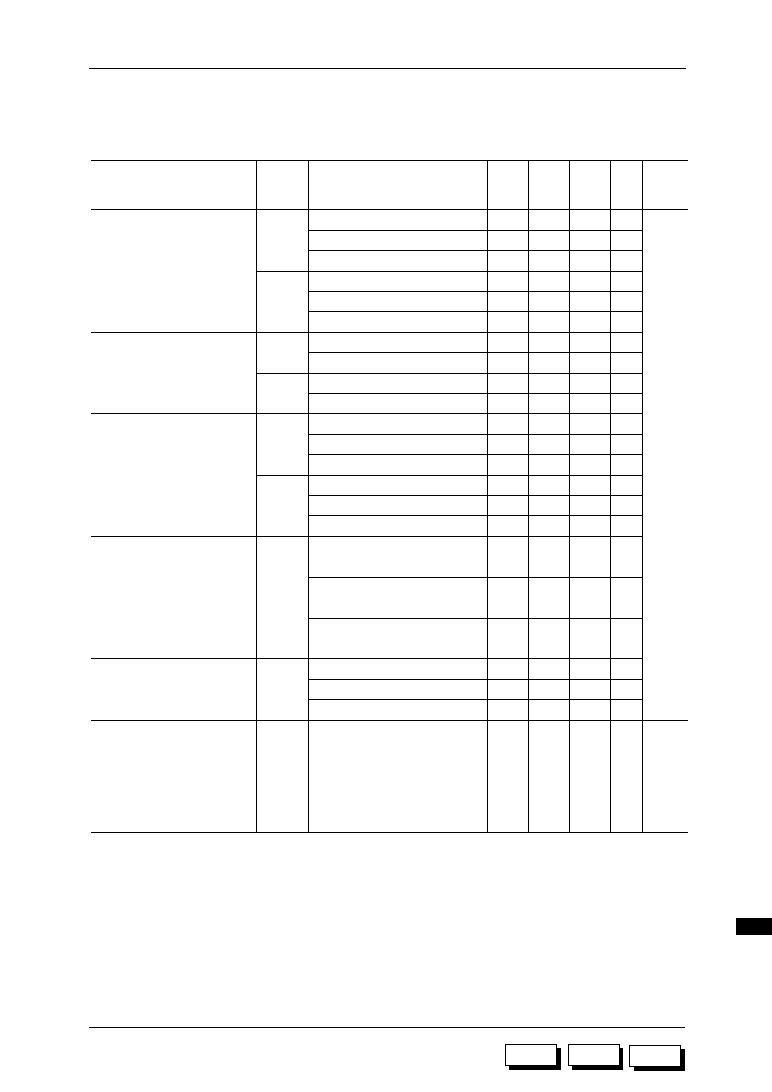

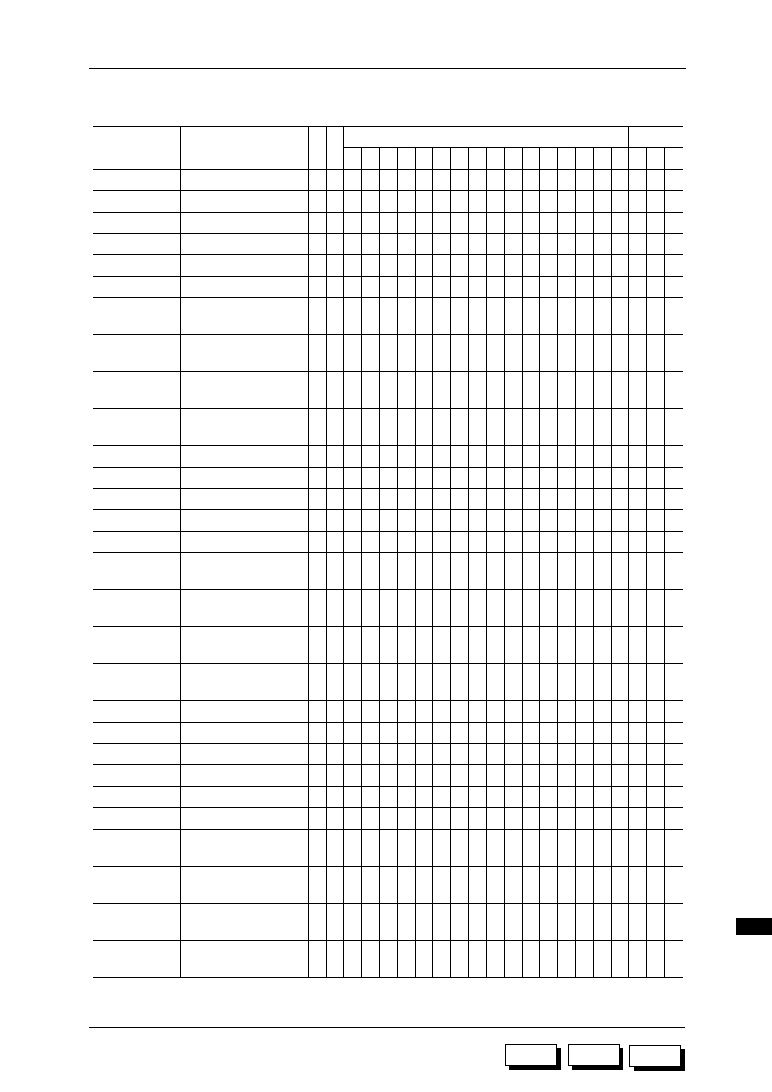

1.5.3 ML63193 Pin Configuration

The ML63193 pin configuration, chip pin configuration, and pad coordinates are shown in

Figures 1-8, 1-9, and Table 1-4, respectively.

NC (not connected) indicates an unused pin that is left unconnected (open).

Figure 1-8 ML63193 144-Pin LQFP Pin Configuration (Top View)

1-18

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

∑ Chip size

: 5.72 mm

•

5.72 mm

∑ Chip thickness

: 350

m

m (280

m

m: available as required)

∑ Coordinate origin

: center of chip

∑ Pad hole size

: 100

m

m

•

100

m

m

∑ Pad size

: 110

m

m

•

110

m

m

∑ Minimum pad pitch

: 140

m

m

!

Note: The chip substrate voltage is V

SS

.

Figure 1-9 ML63193 Chip Pin Configuration (Top View)

Y

X

SEG8 1

SEG36 29

65 V

SS

SEG35 28

66 V

DD1

SEG34 27

67 V

DD2

SEG33 26

68 V

DD3

SEG32 25

69 V

DD4

SEG31 24

70 V

DD5

SEG30 23

71 C1

SEG29 22

72 C2

SEG28 21

73 V

DDH

SEG27 20

74 CB1

SEG26 19

75 CB2

SEG25 18

76 V

DD

SEG24 17

77 V

DDL

SEG23 16

78 OSC1

SEG22 15

79 OSC0

SEG21 14

80 RESET

SEG20 13

81 XT1

SEG19 12

82 XT0

SEG18 11

83 TST1

SEG17 10

84 TST2

SEG16 9

85 MD

SEG15 8

86 MDB

SEG14 7

87 V

DDI

SEG13 6

88 PE.0

SEG12 5

89 PE.1

SEG11 4

90 PE.2

SEG10 3

91 PE.3

SEG9 2

SEG39 32

SEG38 31

SEG37 30

92 PC.0

93 PC.1

94 PC.2

95 PC.3

ML63193

SEG2 123

SEG1 122

33 SEG40

SEG0 121

34 SEG41

COM8 120

35 SEG42

COM7 119

36 SEG43

COM6 118

37 SEG44

COM5 117

38 SEG45

COM4 116

39 SEG46

COM3 115

40 SEG47

COM2 114

41 SEG48

COM1 113

42 SEG49

V

SS

112

43 SEG50

P0.3 111

44 SEG51

P0.2 110

45 SEG52

P0.1 109

46 SEG53

P0.0 108

47 SEG54

P9.3 107

48 SEG55

P9.2 106

49 SEG56

P9.1 105

50 SEG57

P9.0 104

51 SEG58

PA.3 103

52 SEG59

PA.2 102

53 SEG60

PA.1 101

54 SEG61

PA.0 100

55 SEG62

PB.3 99

56 SEG63

PB.2 98

57 COM9

PB.1 97

58 COM10

PB.0 96

59 COM11

60 COM12

61 COM13

62 COM14

63 COM15

64 COM16

SEG7 128

SEG6 127

SEG5 126

SEG4 125

SEG3 124

M193

1-19

ML63187/189B/193 User's Manual

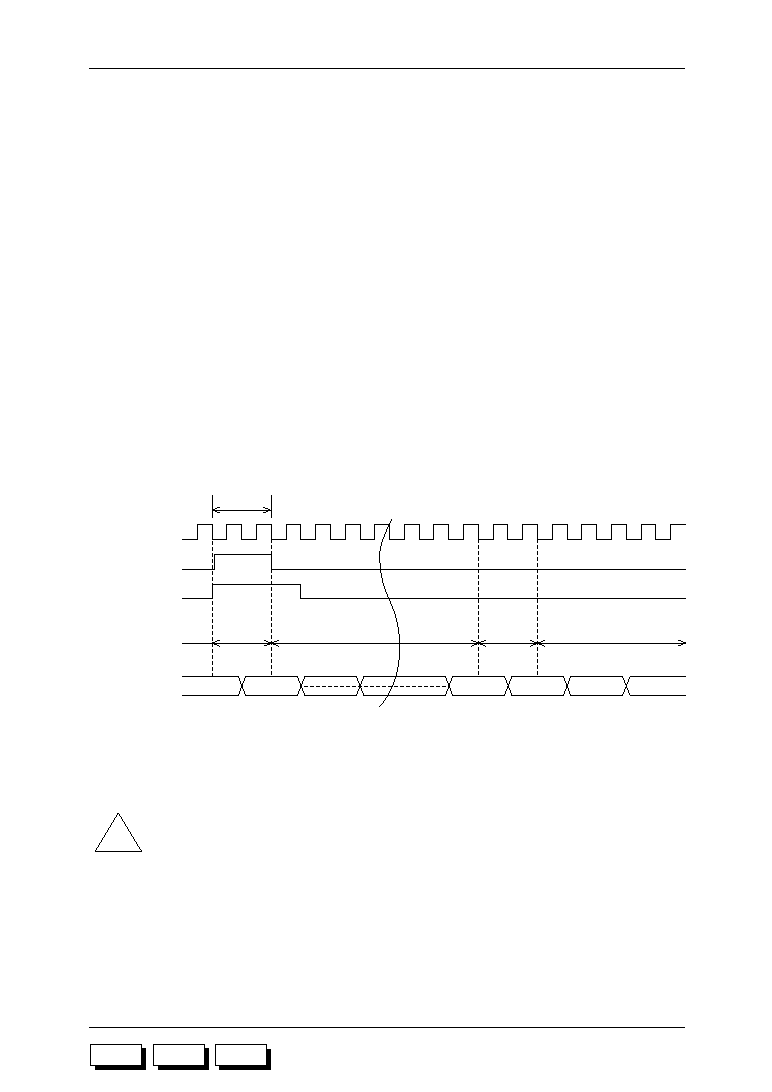

Chapter 1 Overview

1

M187

M189B

M193

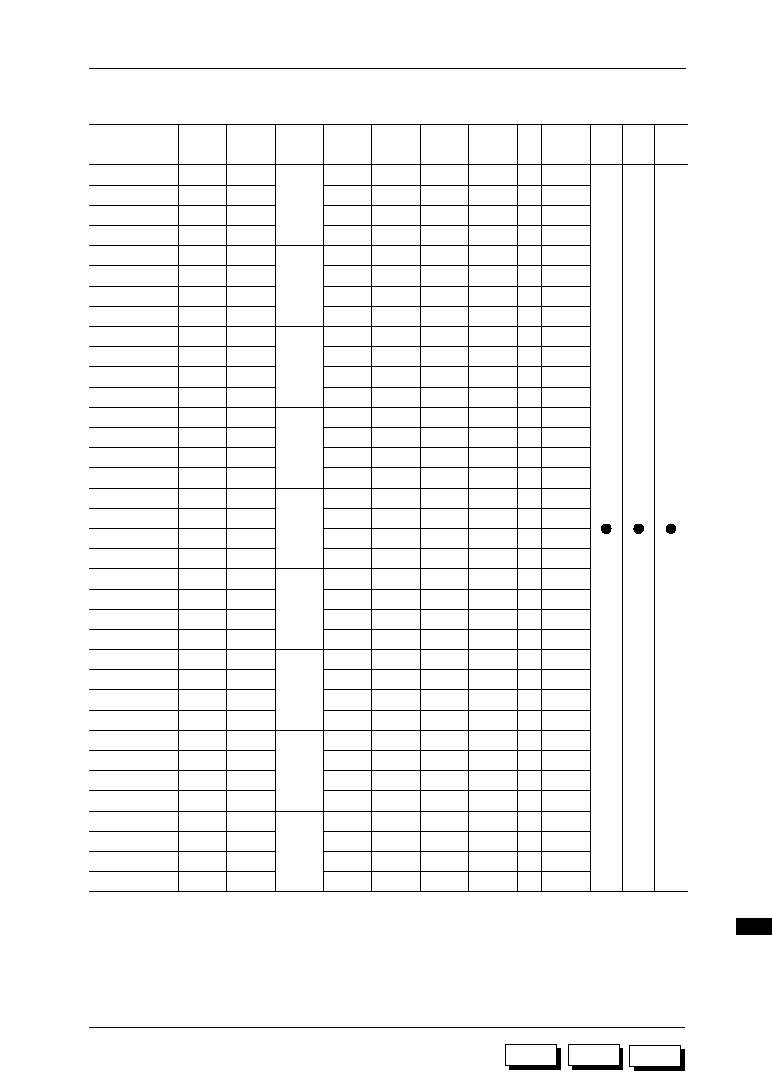

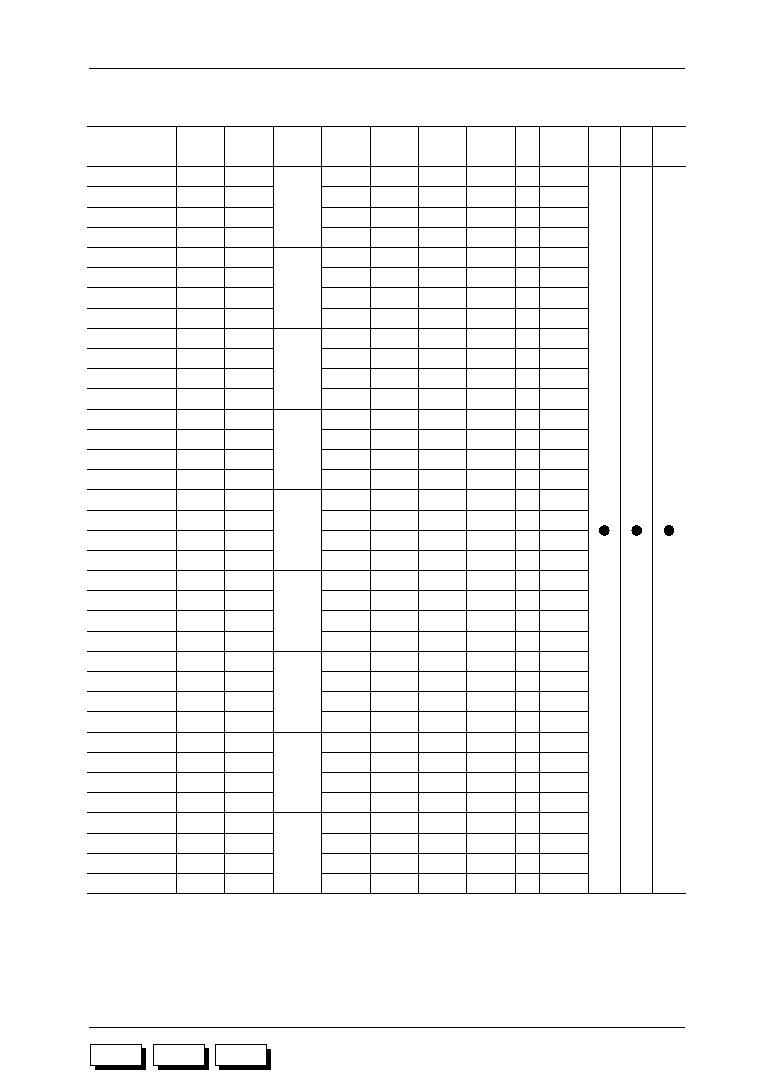

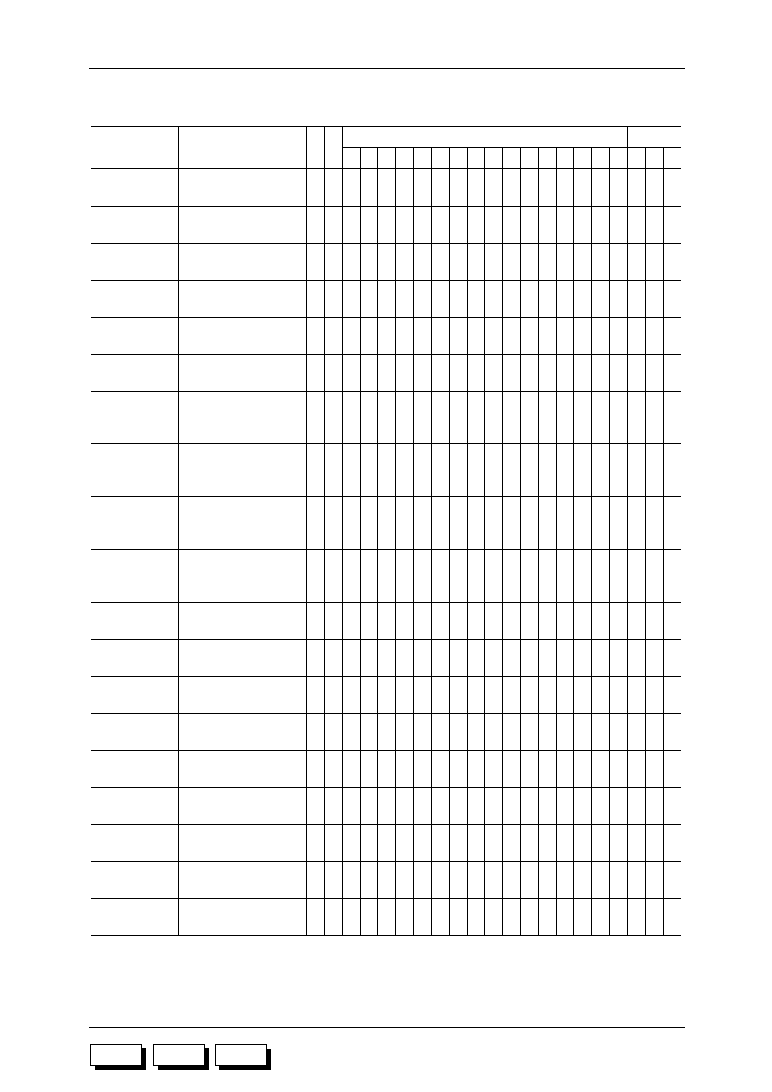

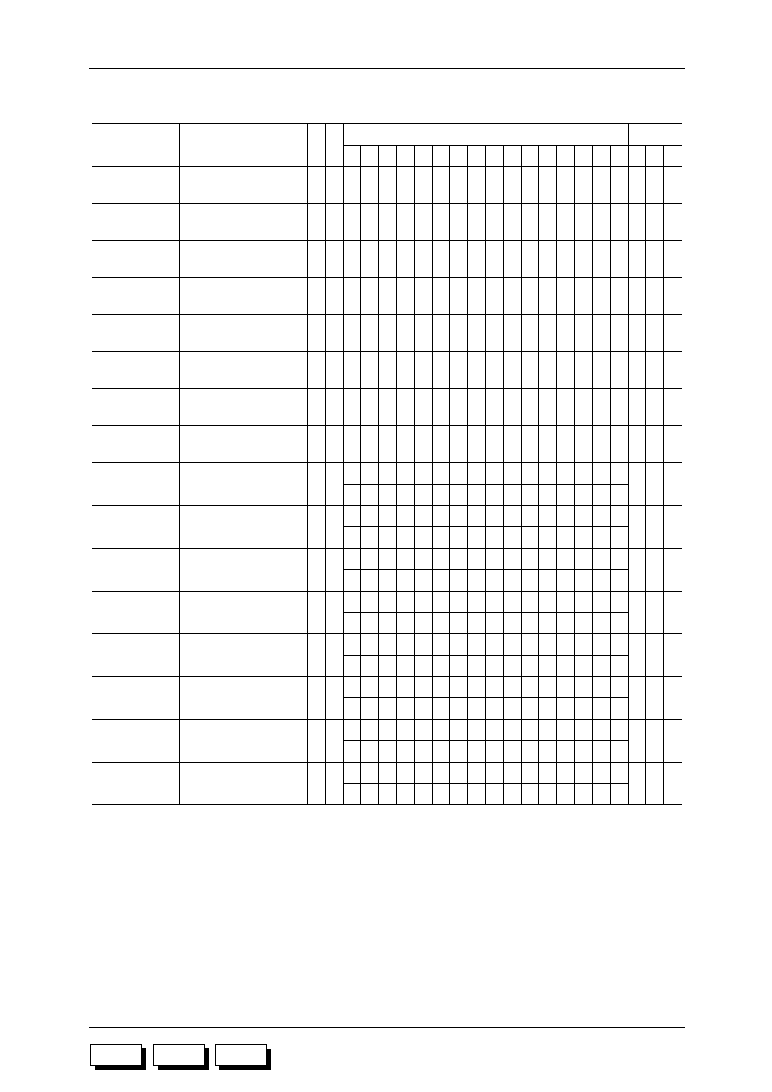

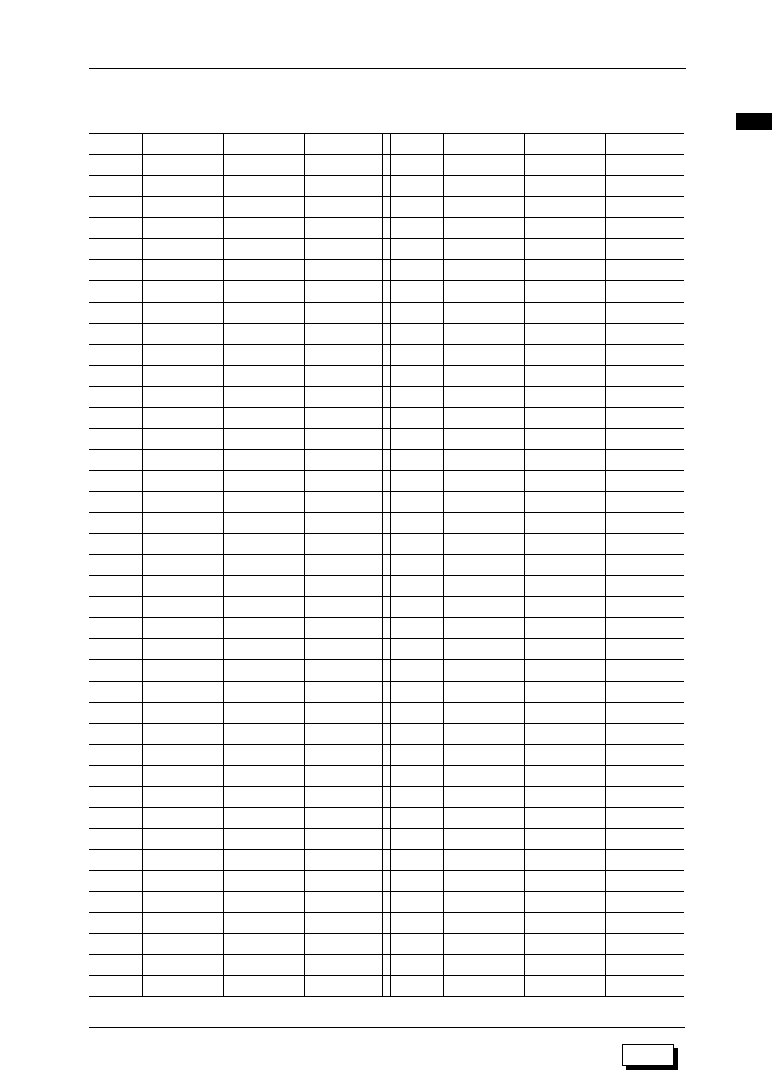

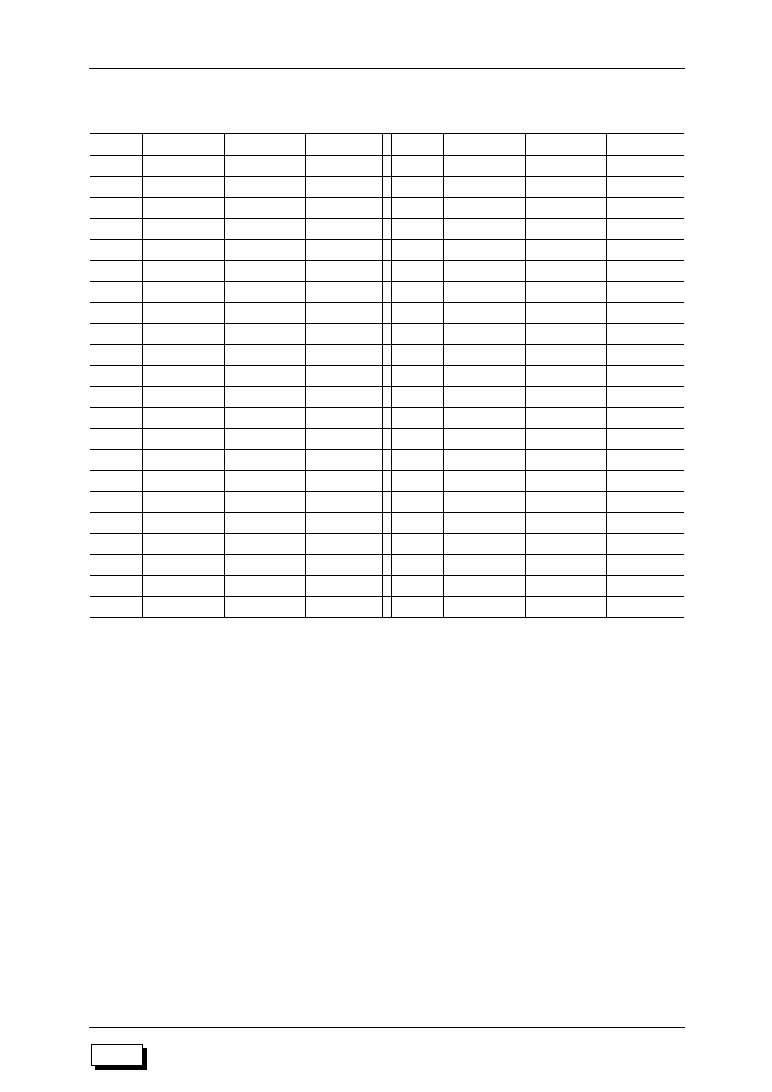

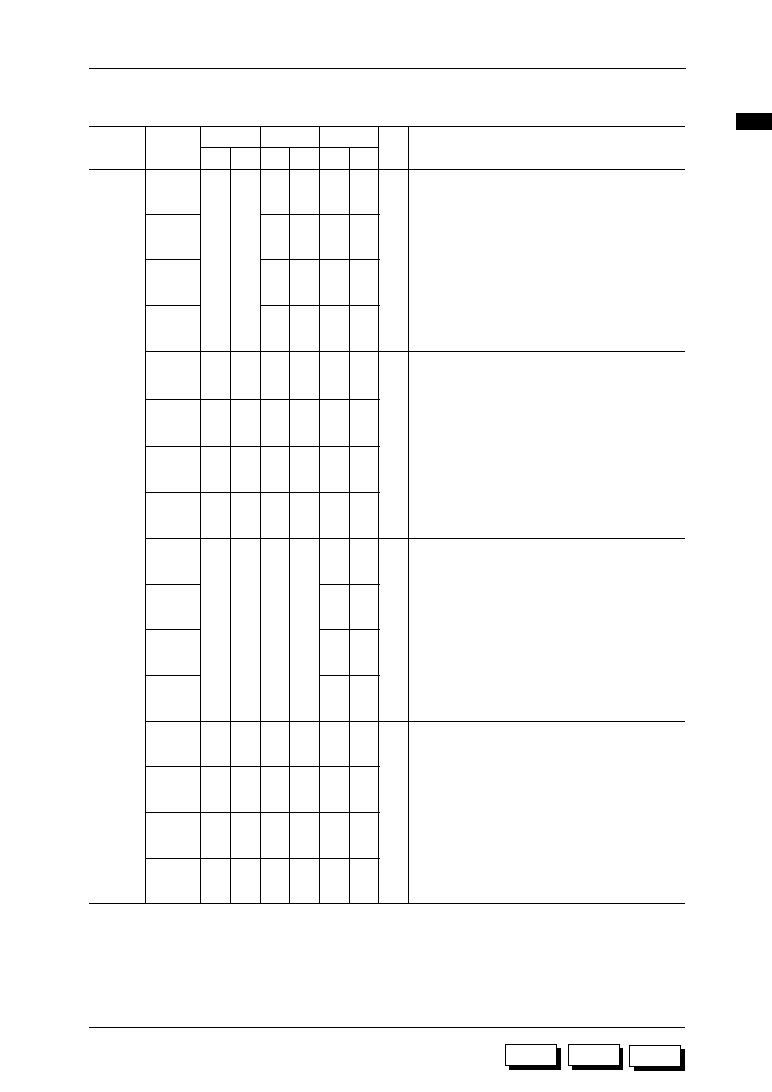

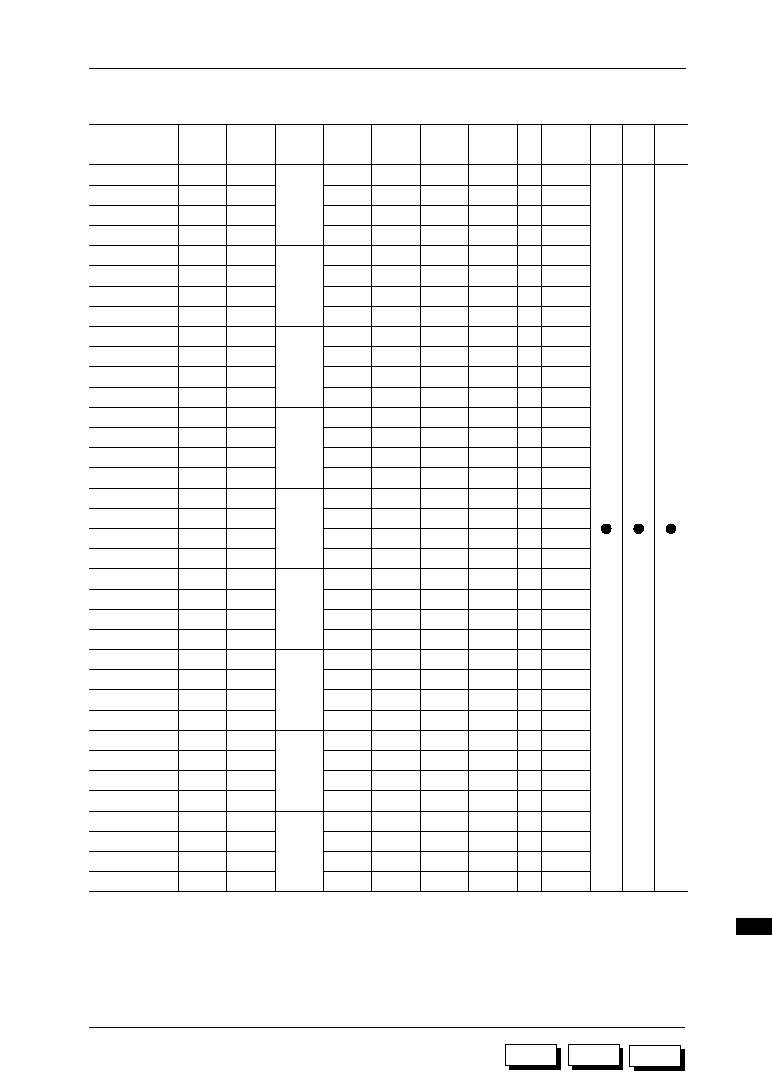

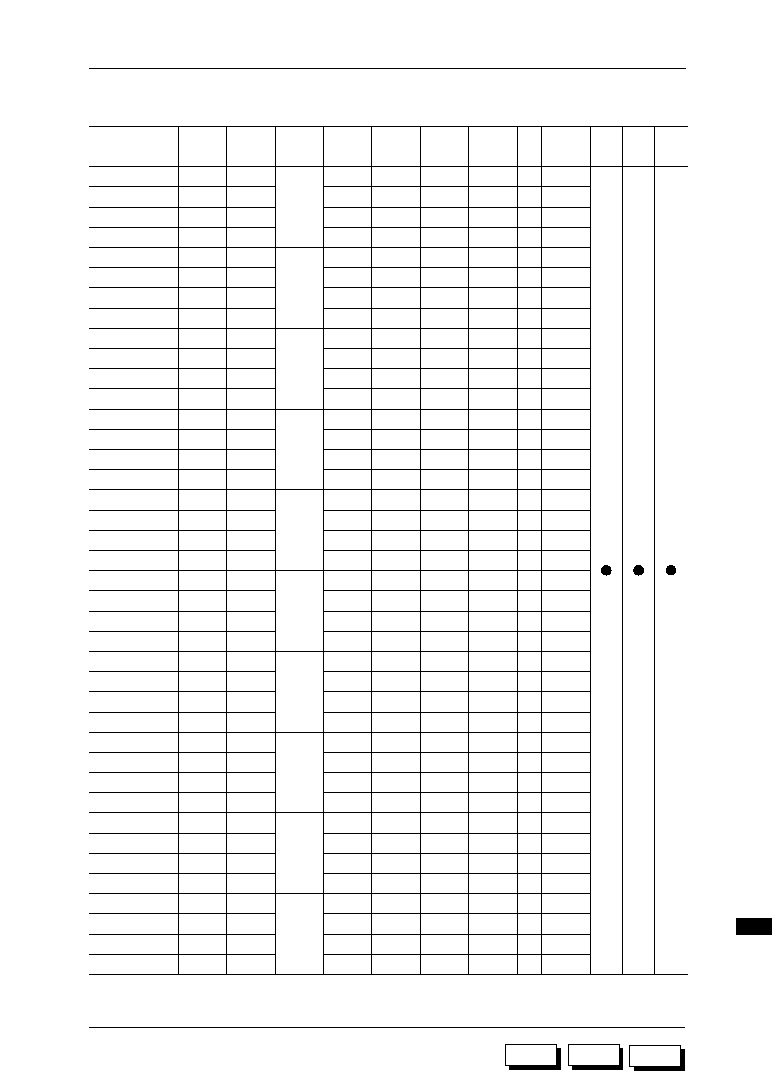

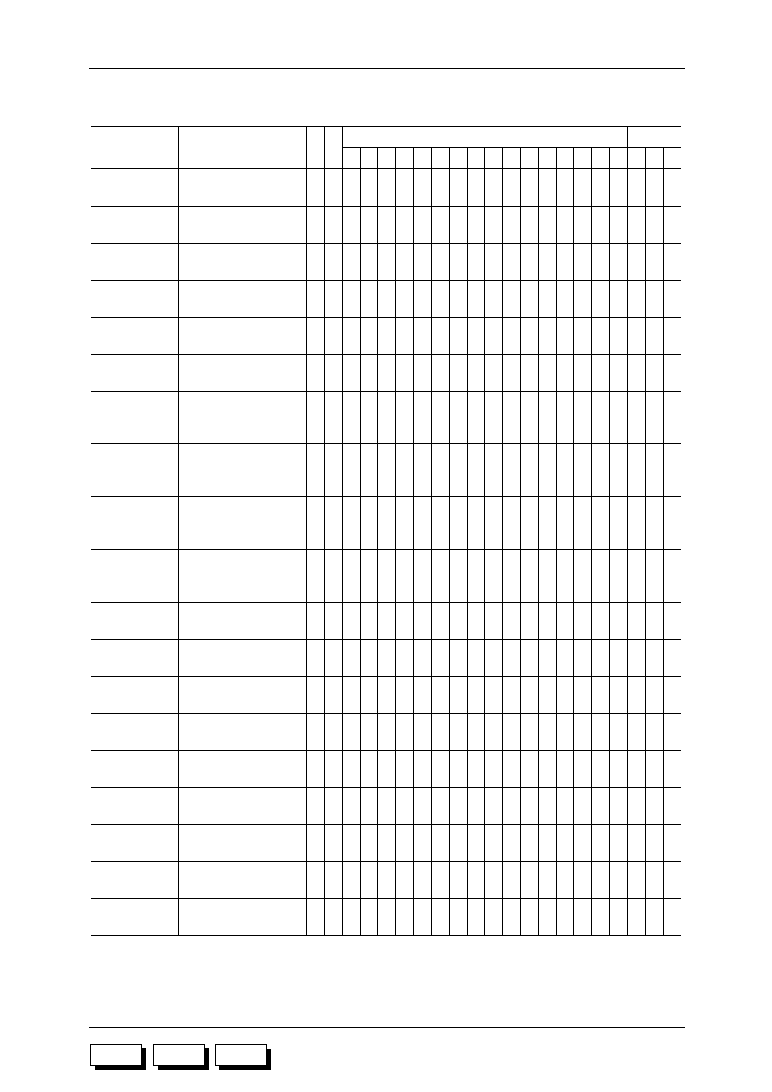

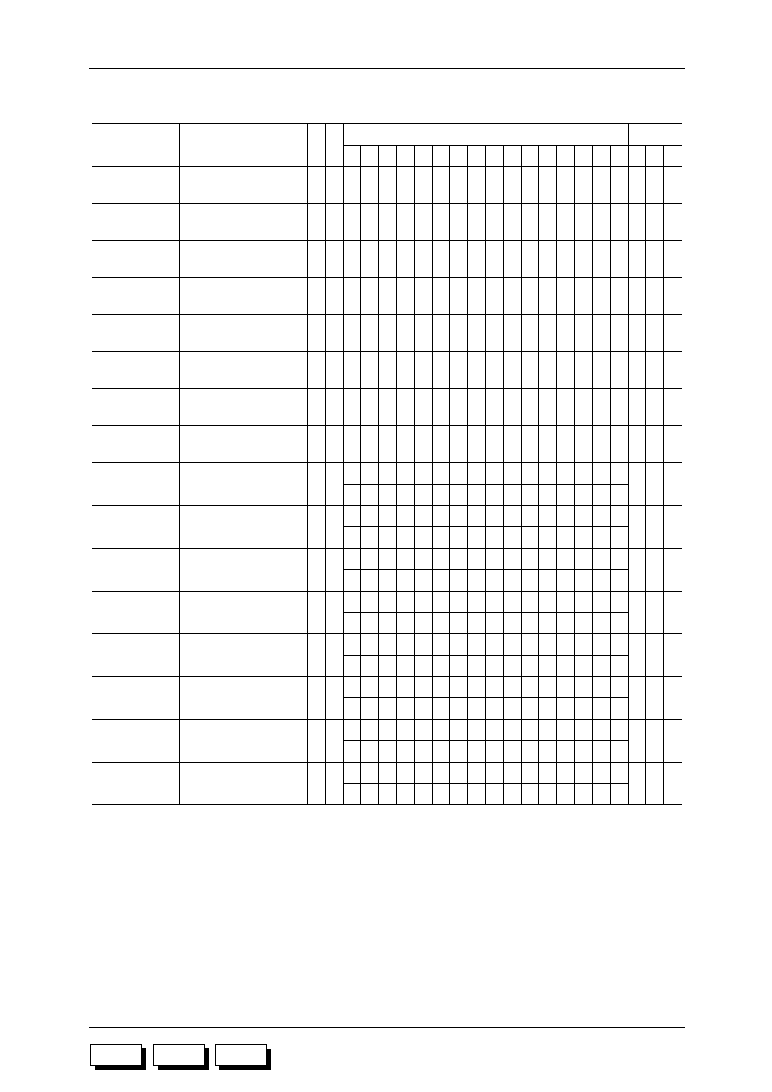

Table 1-4 ML63193 Pad Coordinates

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

SEG21

SEG22

SEG23

SEG24

SEG25

SEG26

SEG27

SEG28

SEG29

SEG30

SEG31

SEG32

SEG33

SEG34

SEG35

SEG36

SEG37

SEG38

SEG39

SEG40

SEG41

SEG42

SEG43

SEG44

SEG45

SEG46

SEG47

≠2204

≠2063

≠1923

≠1783

≠1642

≠1502

≠1361

≠1221

≠1081

≠940

≠800

≠659

≠519

≠379

≠238

≠98

43

183

323

464

604

745

885

1025

1166

1306

1447

1587

1727

1868

2008

2149

2714

2714

2714

2714

2714

2714

2714

2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2149

≠2008

≠1868

≠1727

≠1587

≠1447

≠1306

≠1166

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

SEG48

SEG49

SEG50

SEG51

SEG52

SEG53

SEG54

SEG55

SEG56

SEG57

SEG58

SEG59

SEG60

SEG61

SEG62

SEG63

COM9

COM10

COM11

COM12

COM13

COM14

COM15

COM16

V

SS

V

DD1

V

DD2

V

DD3

V

DD4

V

DD5

C1

C2

V

DDH

CB1

CB2

V

DD

V

DDL

OSC1

OSC0

RESET

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2152

2011

1871

1730

1590

1450

1309

1169

1028

888

748

607

467

326

186

46

≠1025

≠885

≠745

≠604

≠464

≠323

≠183

≠43

98

238

379

519

659

800

940

1081

1221

1361

1502

1642

1783

1923

2063

2204

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

1-20

ML63187/189B/193 User's Manual

Chapter 1 Overview

M187

M189B

M193

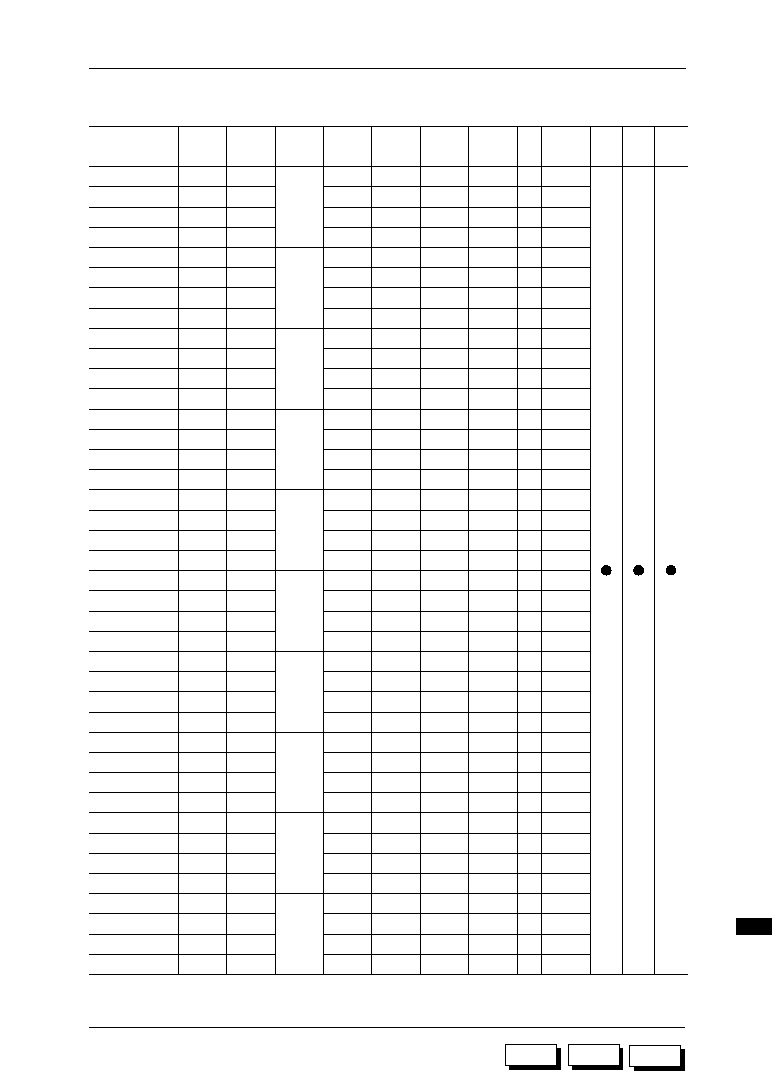

Table 1-4 ML63193 Pad Coordinates (continued)

Pad No.

Pad No.

Pad name

Pad name

X (

mm)

X (

mm)

Y (

mm)

Y (

mm)

Center of chip: x = 0, y = 0

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

XT1

XT0

TST1

TST2

MD

MDB

V

DDI

PE.0

PE.1

PE.2

PE.3

PC.0

PC.1

PC.2

PC.3

PB.0

PB.1

PB.2

PB.3

PA.0

PA.1

PA.2

PA.3

P9.0

≠95

≠235

≠376

≠516

≠656

≠797

≠937

≠1078

≠1218

≠1358

≠1499

≠1639

≠1780

≠1920

≠2060

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

≠2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2714

2246

2106

1966

1825

1685

1544

1404

1264

1123

105

106

107

108

109

110

111

112

113

114

115

116

117

118

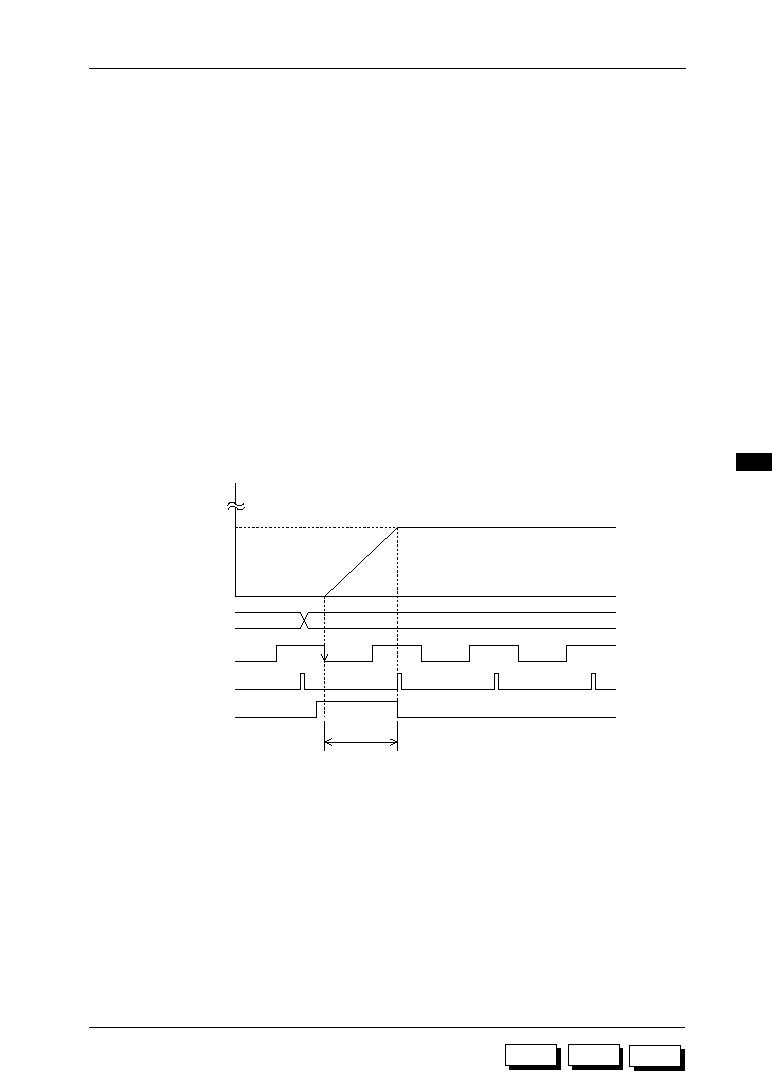

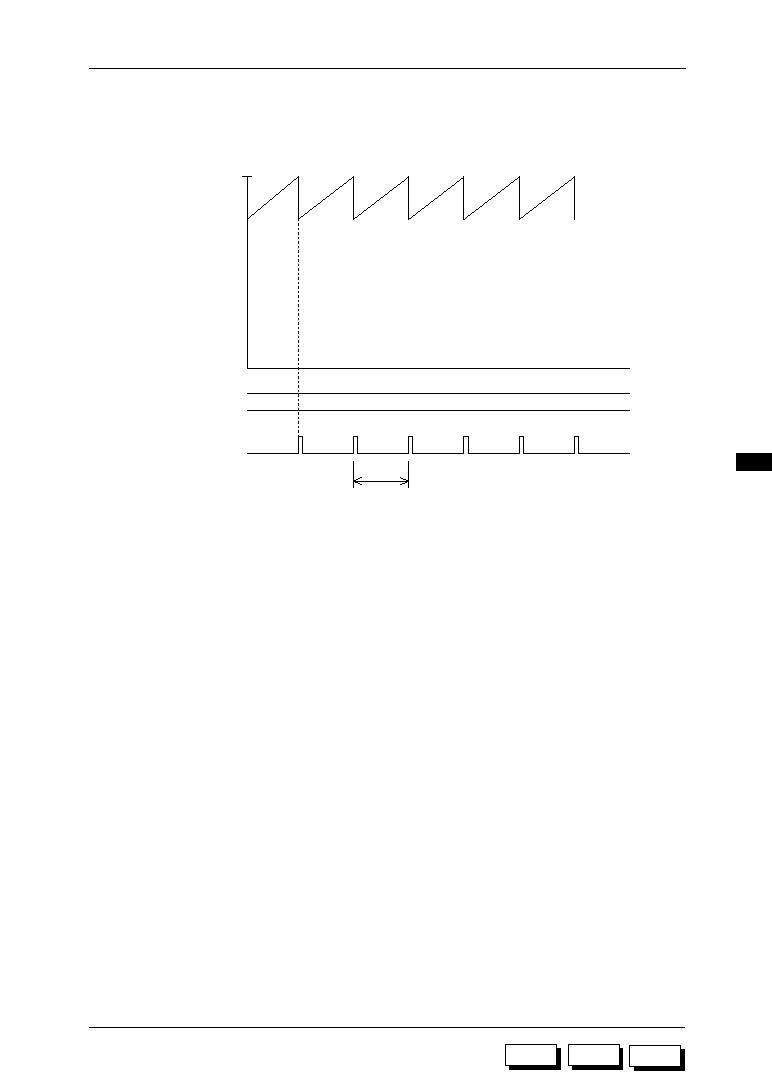

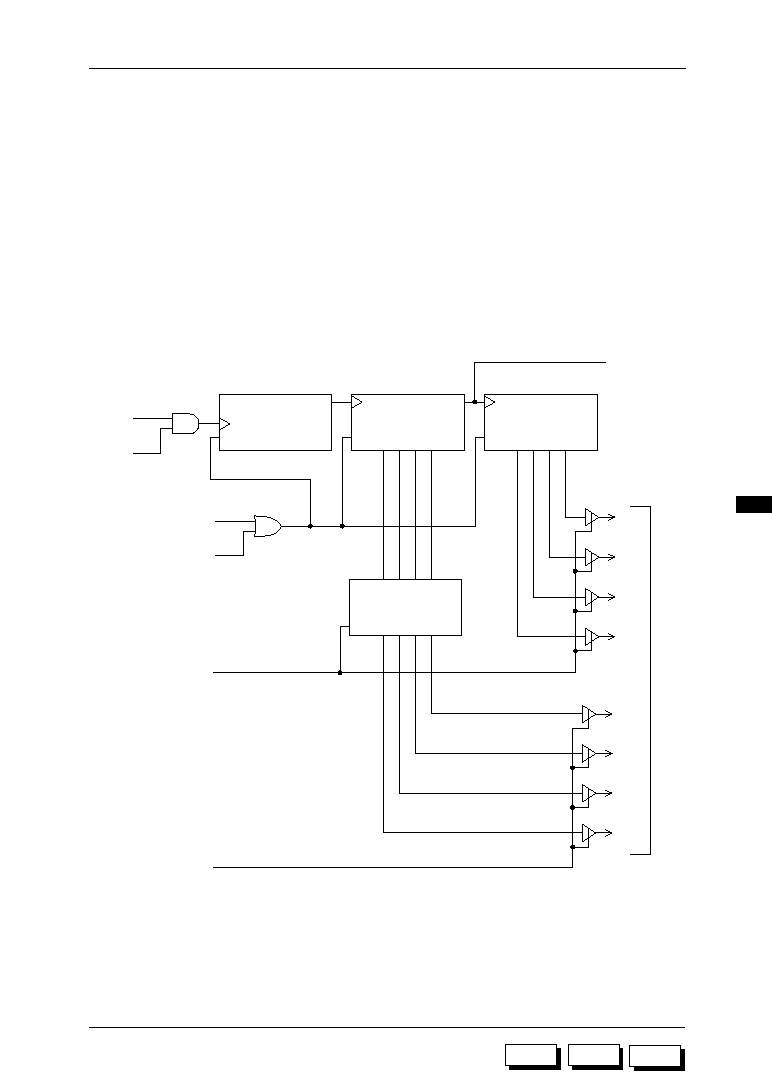

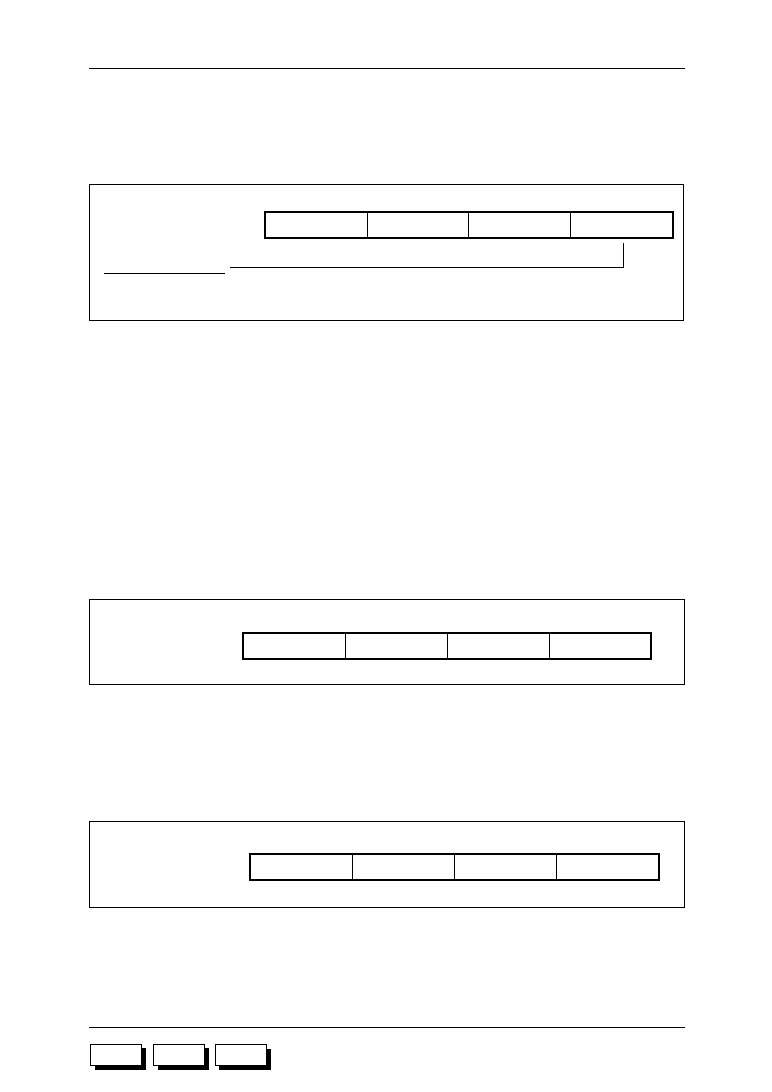

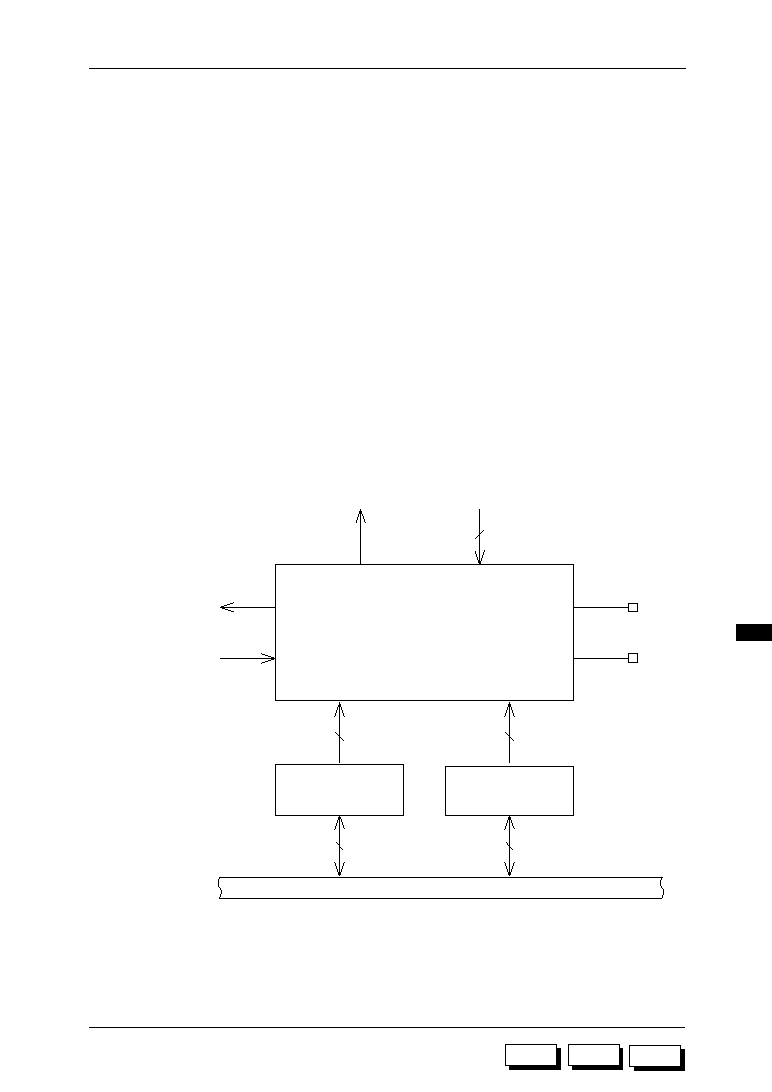

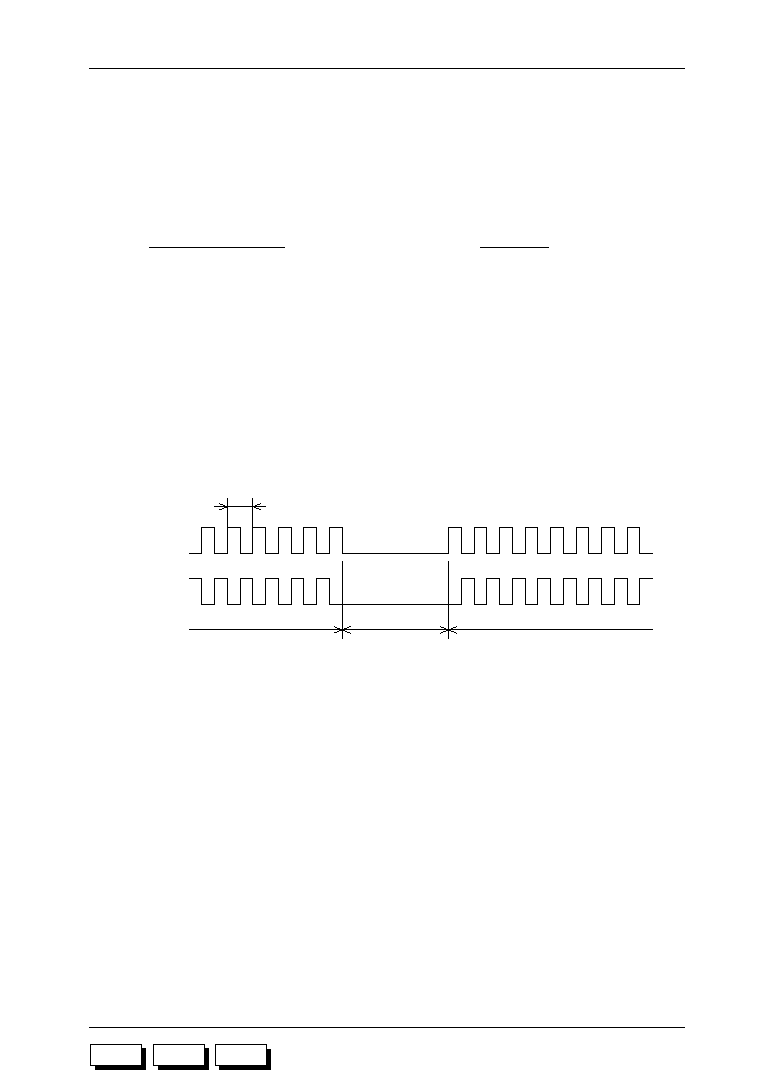

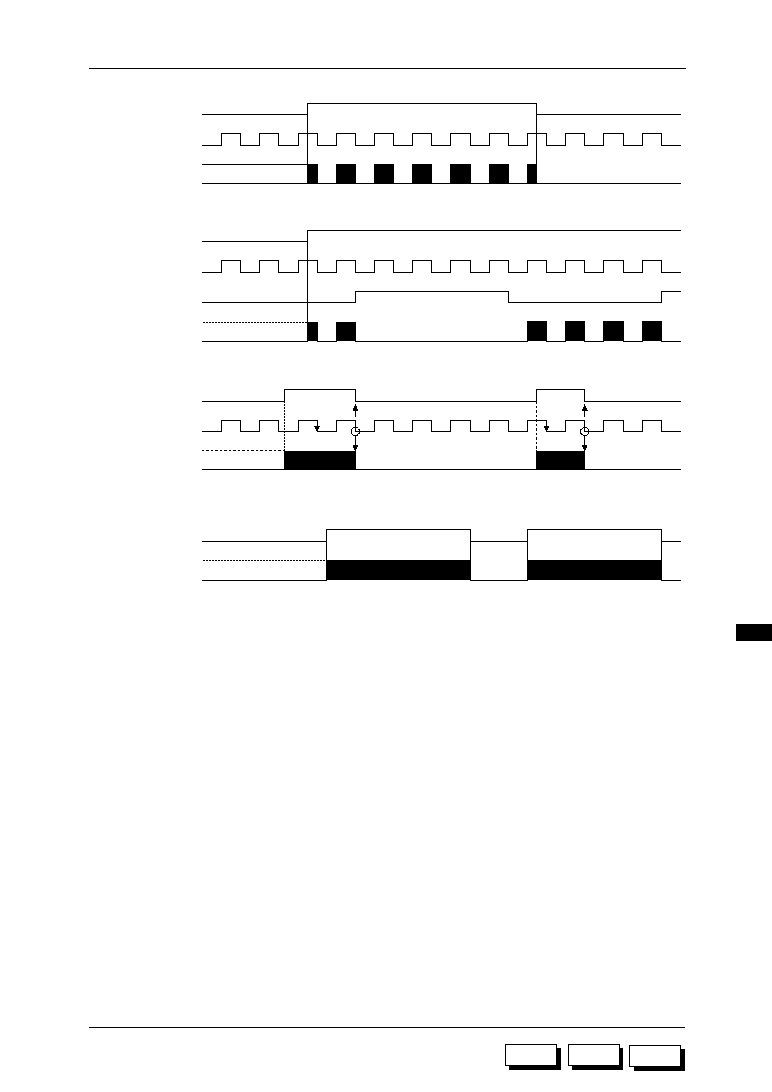

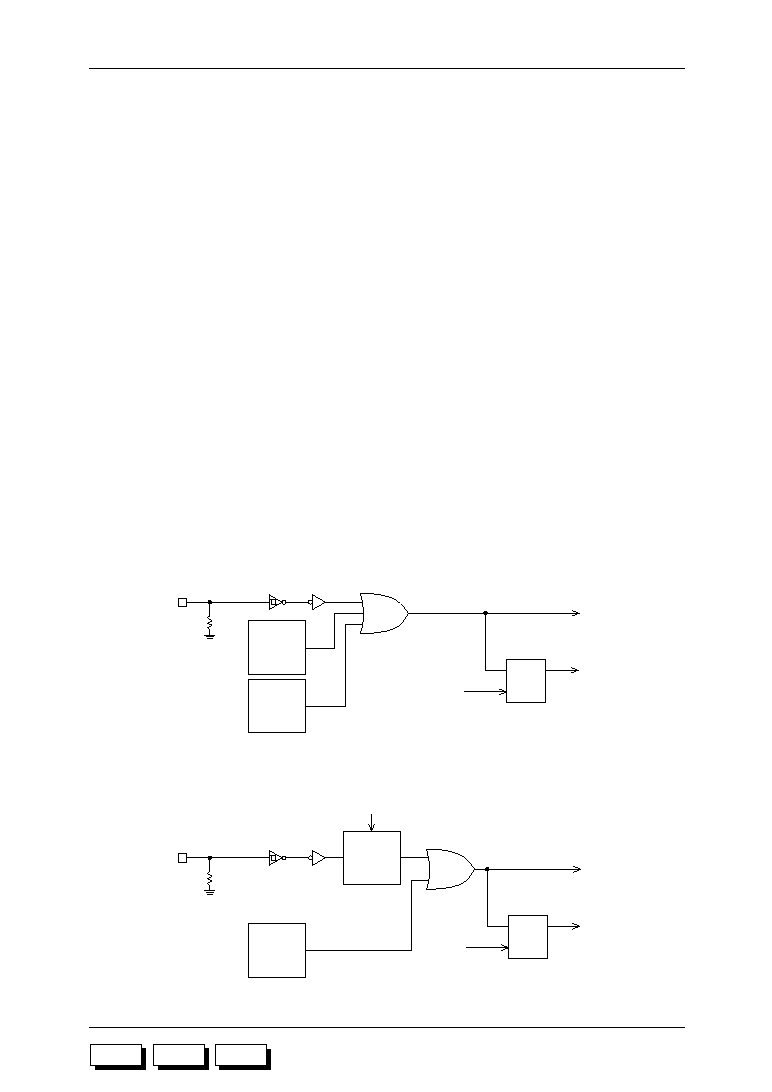

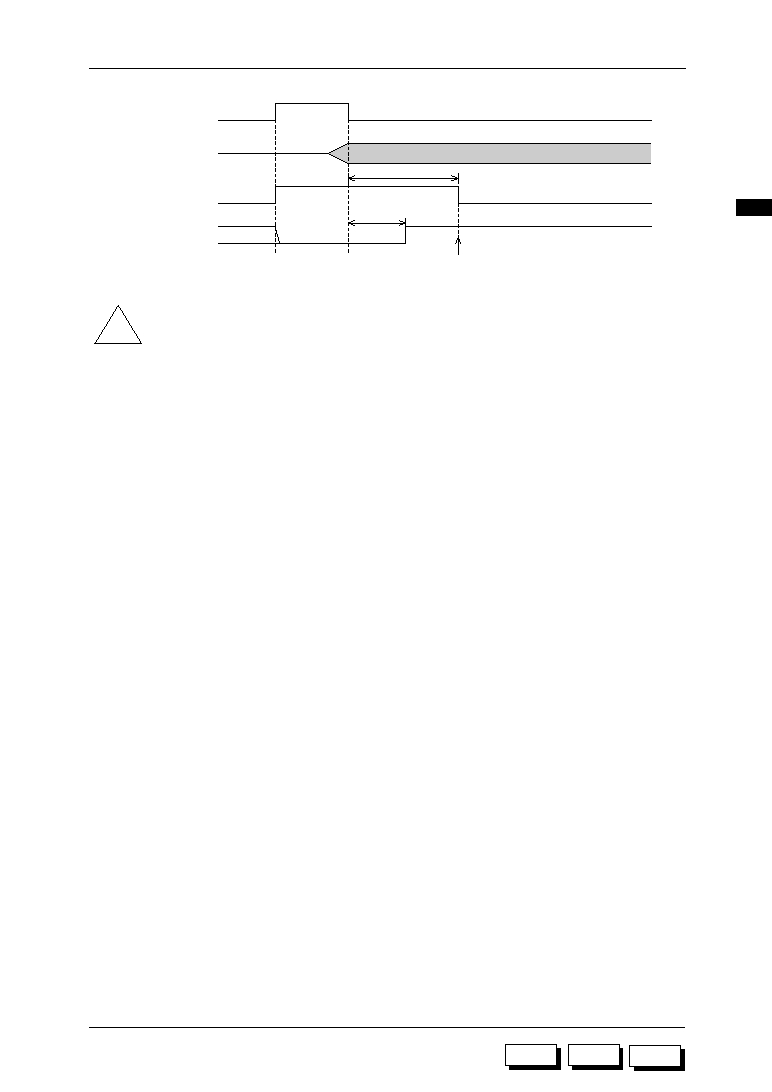

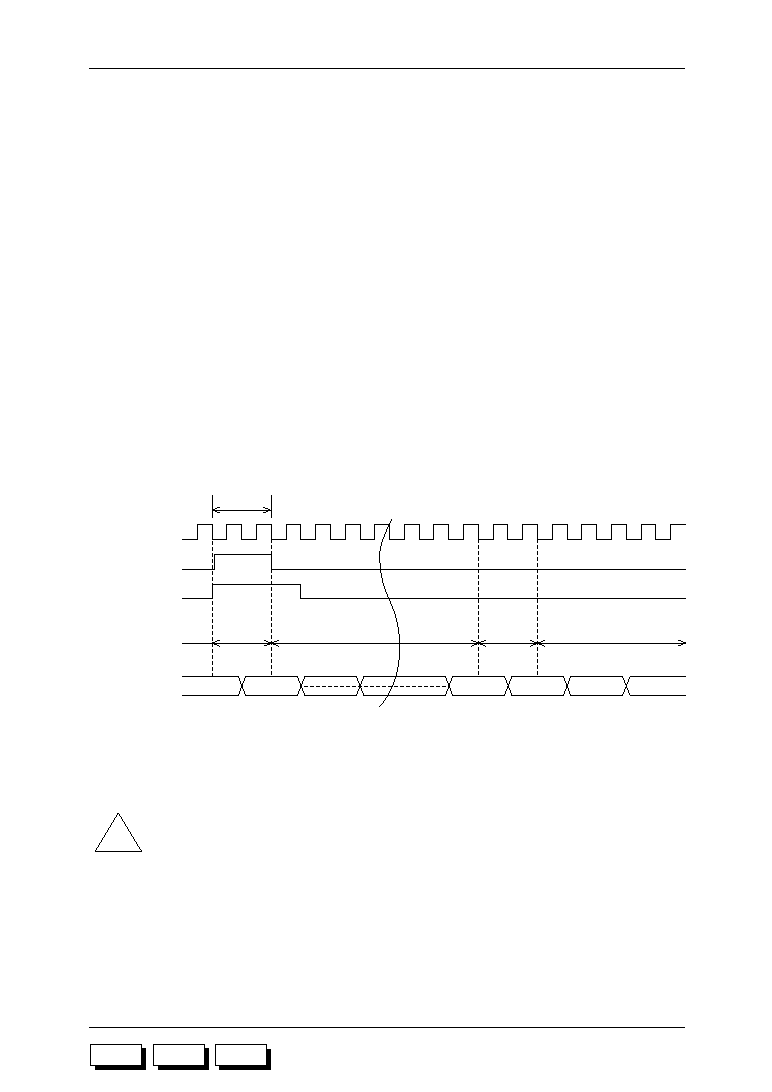

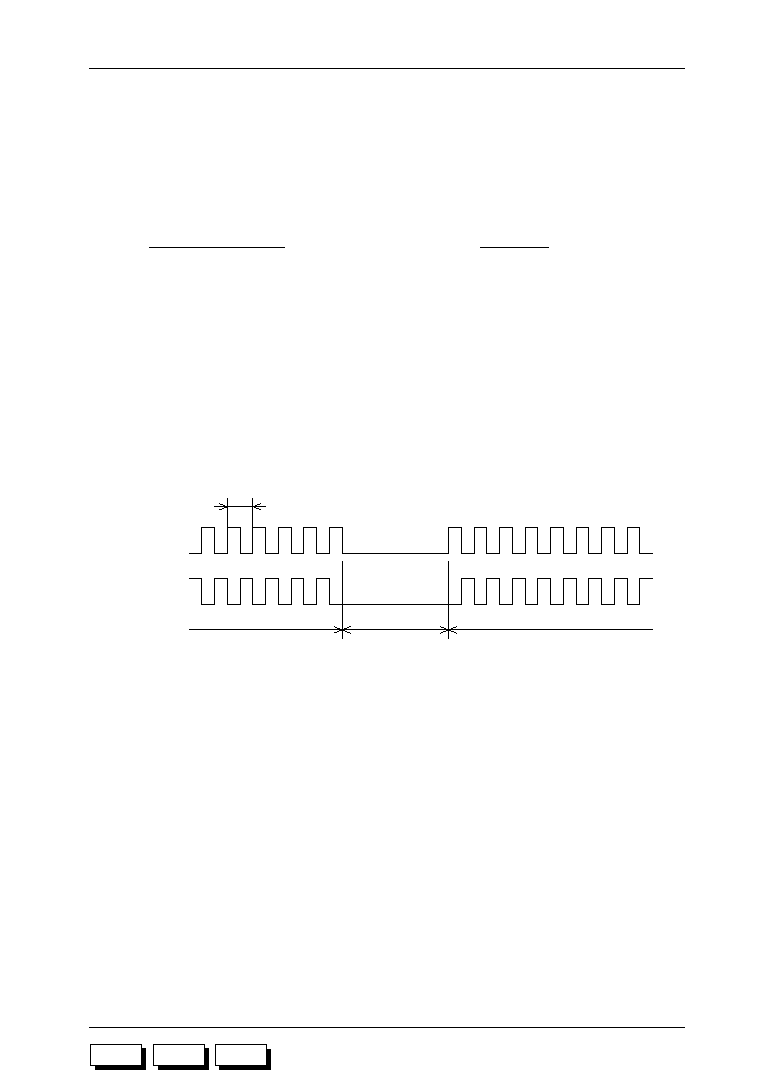

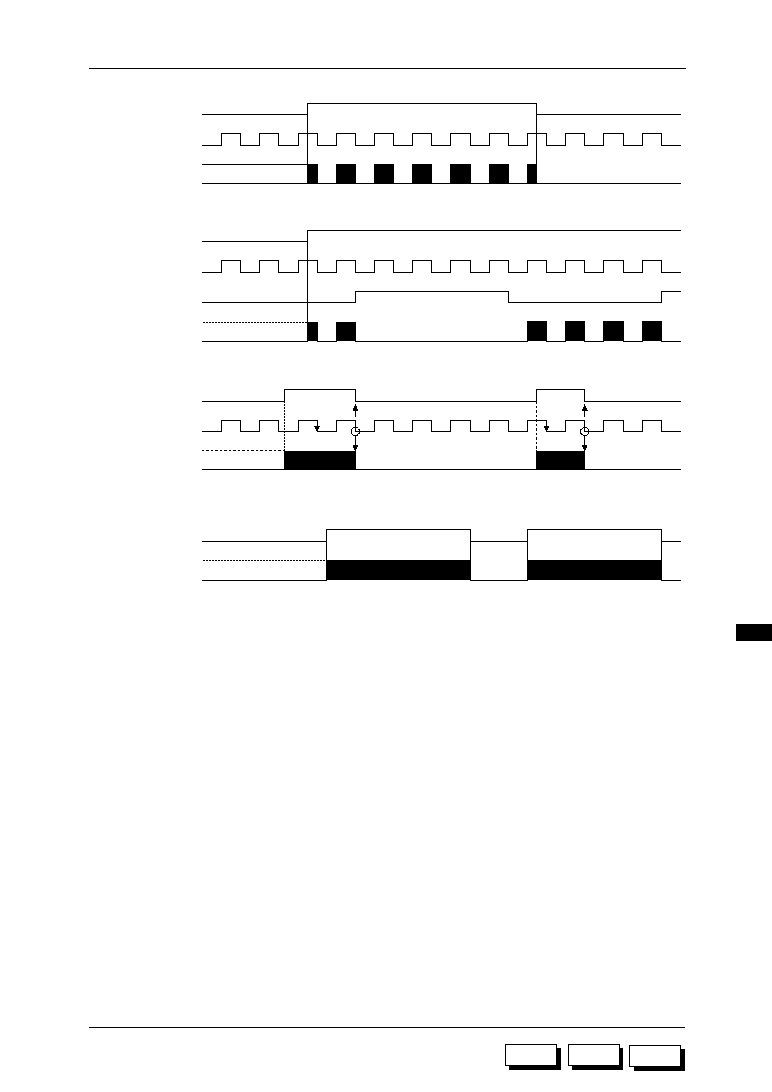

119