° Semiconductor

ML63512A/63514A

1/29

GENERAL DESCRIPTION

The ML63512A/63514A is a CMOS 4-bit microcontroller with built-in level detector and

operates at 0.9 V (min.).

The ML63512A/63514A is an M6351x series mask ROM-version product of OLMS-63K family,

which employs Oki's original CPU core nX-4/250.

The program memory capacity and data memory capacity of the ML63512A differ from those of

the ML63514A.

48-pin TQFP and 64-pin TQFP packages are available for the ML63512A and ML63514A.

FEATURES

∑ Extensive instruction set

407 instructions

Transfer, rotate, increment/decrement, arithmetic operations, comparison, logic operations,

mask operations, bit operations, ROM table reference, stack operations, flag operations,

jump, conditional branch, call/return, control.

∑ Wide variety selection of addressing modes

Indirect addressing of four data memory types, with current bank register, extra bank

register, HL register and XY register.

Data memory bank internal direct addressing mode.

∑ Processing speed

Two clocks per machine cycle, with most instructions executed in one machine cycle.

Minimum instruction execution time

: 61 ms (@ 32.768 kHz system clock)

1 ms (@ 2 MHz system clock)

∑ Clock generation circuit

Low-speed clock

: Crystal oscillation or RC oscillation selectable by

mask option (30 to 80 kHz)

High-speed clock

: Ceramic oscillation or RC oscillation selectable by

mask option (2 MHz max.)

∑ Program memory space

ML63512A: 4K words

ML63514A: 8K words

Basic instruction length is 16 bits/1 word

∑ Data memory space

ML63512A: 128 nibbles

ML63514A: 256 nibbles

° Semiconductor

ML63512A/63514A

4-Bit Microcontroller with Built-in Level Detector, Melody Circuit, and Comparator,

Operating at 0.9 V (Min.)

E2E0057-29-71

This version: Jul. 1999

Previous version: Jun. 1999

° Semiconductor

ML63512A/63514A

2/29

∑ Stack level

Call stack level

: 16 levels

Register stack level

: 16 levels

∑ I/O ports

Input ports: Selectable as input with pull-up resistor/high-impedance input

Output ports: N-channel open drain output (can directly drive LEDs)

Input-output ports: Selectable as input with pull-up resistor/high-impedance input

Selectable as N-channel open drain output/CMOS output

Can be interfaced with external peripherals that use a different power supply than this device

uses. (Power to the output port is supplied from V

DDI

(separate power suply))

Number of ports:

(For 48-pin packages)

Input port

: 1 port • 4 bits

Output port

: 1 port • 4 bits

Input-output port

: 6 ports • 4 bits

(For 64-pin packages)

Input port

: 1 port • 4 bits

Output port

: 1 port • 4 bits

Input-output port

: 9 ports • 4 bits

∑ Melody output function

Melody sound frequency

: 529 to 2979 Hz (@ 32.768 kHz)

Tone length

: 63 varieties

Tempo

: 15 varieties

Melody data

: Stored in the program memory

Number of ports

: 1 (dedicated pin)

Buzzer driver signal output

: 4 kHz (@ 32.768 kHz)

∑ Level detector

Conversion time

: Approx. 183 ms (@ 32.768 kHz)

Dedicated input pins

: 2 pins (switched by software; for the secondary

functions of the input ports)

Detection level

: 12 levels

∑ Comparator

Offset voltage

: 50 mV max. (V

DD

= 1.5 V)

Comparison time

: Approx. 183 ms (@ 32.768 kHz)

Number of channels

: 1 (for the secondary functions of the input ports)

∑ Reset function

Reset through RESETB pin (RESETB pin can be pulled up by mask option)

∑ Power supply backup

Backup circuit (voltage multiplier) enables operation at 0.9 V minimum

° Semiconductor

ML63512A/63514A

3/29

∑ Timers and counter

8-bit timer • 2

Selectable as auto-reload mode/capture mode/clock frequency measurement mode

15-bit time base counter • 1

1 Hz, 2 Hz, 4 Hz, 8 Hz, 16 Hz, 32 Hz, 64 Hz, 128 Hz, 256 Hz, 512 Hz, 1 kHz, and 2 kHz signals

can be read (@ 32.768 kHz)

∑ Serial port

Mode

: Selectable as UART mode/synchronous

mode

UART communication speed

: 2TBCCLK, TBCCLK, 1/2TBCCLK, Timers 0

& 1 overflow

24 kbps Max. (when 2TBCCLK @ 80 kHz

selected)

Clock frequency in synchronous mode

: 30 to 80 kHz (internal clock mode), external

clock frequency

Data length

: 5 to 8 bits

∑ Interrupt sources

External interrupt (4 sources)

: Selectable as rising edge/falling edge/both

rising and falling edges

Internal interrupt (10 sources)

: Time base interrupt • 4 (2, 4, 16, and 32 Hz

@ 32.768 kHz)

Timer interrupt • 2

Level detector interrupt • 1

Serial port reception interrupt • 1

Serial port transmission interrupt • 1

Melody end interrupt • 1

∑ Operating Temperature

≠20 to +70

∞

C

∑ Supply voltage

When backup used

: 0.9 to 1.8 V

(Maximum operating frequency 1 MHz)

When backup not used

: 1.8 to 3.5 V

(When Level detector or Comparator is

used, maximum operating frequency

2 MHz)

1.8 to 5.5 V

(When Level detector and Comparator are

not used, maximum operating frequency

2 MHz)

∑ Package options:

48-pin plastic TQFP (TQFP48-P-0707-0.50-K) : (Product name: ML63512A-xxxTB,

ML63514A-xxxTB)

64-pin plastic TQFP (TQFP64-P-1010-0.50-K) : (Product name: ML63512A-xxxTP,

ML63514A-xxxTP)

xxx indicates a code number.

° Semiconductor

ML63512A/63514A

4/29

BLOCK DIAGRAM

An asterisk (*) indicates the port secondary function. The power to the circuits corresponding

to the signal names inside is supplied from V

DDI

(power supply for interface).

ROM

ML63512A: 4KW

ML63514A: 8KW

BUS

CON-

TROL

MIE

XT0

XT1

OSC0

OSC1

TBCCLK*

HSCLK*

OSC

CBR

EBR

L

C G

Z

ALU

RA

A

IR

INSTRUCTION

DECODER

RAM

ML63512A: 128N

ML63514A: 256N

nX-4/250

RESETB

RST

V

DDI

PC

H

Y

X

TIMING

CON-

TROL

SP

RSP

STACK

CAL: 16-level

REG: 16-level

TIMER

8bit • 2

RXC*

TXC*

RXD*

TXD*

2

INT

SIO

TM0CAP/TM1CAP*

TM0OVF/TM1OVF*

T0CK*

T1CK*

2

INT

I/O

PORT

P0.0-P0.3

P1.0-P1.3

P2.0-P2.3

P3.0-P3.3

P4.0-P4.3

P5.0-P5.3

P6.0-P6.3

=

P9.0-P9.3

=

PA.0-PA.3

=

4

INT

DATA BUS

TBC

4

INT

INT

1

V

SS

MELODY

MD

1

INT

TST1B

TST

TST2B

P7.0-P7.3

INT

INPUT

PORT

P8.0-P8.3

OUTPUT

PORT

LDIN0*

Level

Detector

LDIN1*

CMPIN*

CMP

CMPREF*

V

DDH

V

DD

CB1

CB2

BACK-

UP

V

DDL

VR

=

Port 6 (P6.0 to P6.3), Port 9 (P9.0 to P9.3) and Port A (PA.0 to PA.3) are only provided for the 64-

pin packages.

° Semiconductor

ML63512A/63514A

5/29

PIN CONFIGURATION (TOP VIEW)

48-Pin Plastic TQFP

P3.0/RXD

1

P3.1/TXC

2

P3.2/RXC

3

P3.3/TXD

4

P4.0

5

P4.1

6

P4.2

7

P4.3

8

P5.0

9

P5.1

10

P5.2

11

P5.3

12

MD

RESETB

OSC1

OSC0

V

SS

TST2B

TST1B

XT1

XT0

V

DDL

CB2

CB1

36

35

34

33

32

31

30

29

28

27

26

25

37

38

39

40

41

42

43

44

45

46

47

48

24

23

22

21

20

19

18

17

16

15

14

13

P0.0/INT0

P0.1/INT1

P0.2/INT2

P0.3/INT3

P1.0/TM0CAP/TM0OVF

P1.1/TM1CAP/TM1OVF

P1.2/T0CK

P1.3/T1CK

P2.0/TBCCLK

P2.1/HSCLK

P2.2

P2.3

V

DDH

V

DD

V

SS

V

DDI

P8.3

P8.2

P8.1

P8.0

P7.3/LDIN1

P7.2/LDIN0

P7.1/CMPREF

P7.0/CMPIN

° Semiconductor

ML63512A/63514A

6/29

PIN CONFIGURATION (TOP VIEW) (continued)

64-Pin Plastic TQFP

Note: Pins marked as (NC) are no-connection pins which are left open.

PA.2

1

PA.3

2

P3.0/RXD

3

P3.1/TXC

4

P3.2/RXC

5

P3.3/TXD

6

P4.0

7

P4.1

8

P4.2

9

P4.3

10

P5.0

11

P5.1

12

P5.2

13

P5.3

14

P9.1

P9.0

MD

RESETB

OSC1

OSC0

V

SS

TST2B

TST1B

XT1

XT0

V

DDL

CB2

CB1

48

47

46

45

44

43

42

41

40

39

38

37

36

35

51

52

53

54

55

56

57

58

59

60

61

62

63

64

30

29

28

27

26

25

24

23

22

21

20

19

18

17

P0.0/INT0

P0.1/INT1

P0.2/INT2

P0.3/INT3

P1.0/TM0CAP/TM0OVF

P1.1/TM1CAP/TM1OVF

P1.2/T0CK

P1.3/T1CK

P2.0/TBCCLK

P2.1/HSCLK

P2.2

P2.3

PA.0

PA.1

V

DDH

V

DD

V

SS

V

DDI

P8.3

P8.2

P8.1

P8.0

P7.3/LDIN1

P7.2/LDIN0

P7.1/CMPREF

P7.0/CMPIN

P6.3

P6.2

P6.0

15

P6.1

16

(NC)

(NC)

34

33

49

50

32

31

P9.2

P9.3

(NC)

(NC)

° Semiconductor

ML63512A/63514A

7/29

PIN DESCRIPTIONS

The basic functions of each pin of the ML63512A/63514A are described in Table 1.

A symbol with a slash (/) denotes a pin that has a secondary function.

Refer to Table 2 for secondary functions.

For type, "--" denotes a power supply pin, "I" an input pin, "O" an output pin, and "I/O" an input-

output pin.

For pin, "TB" denotes a 48-pin flat package (48TQFP), and "TP" a 64-pin flat package (64TQFP).

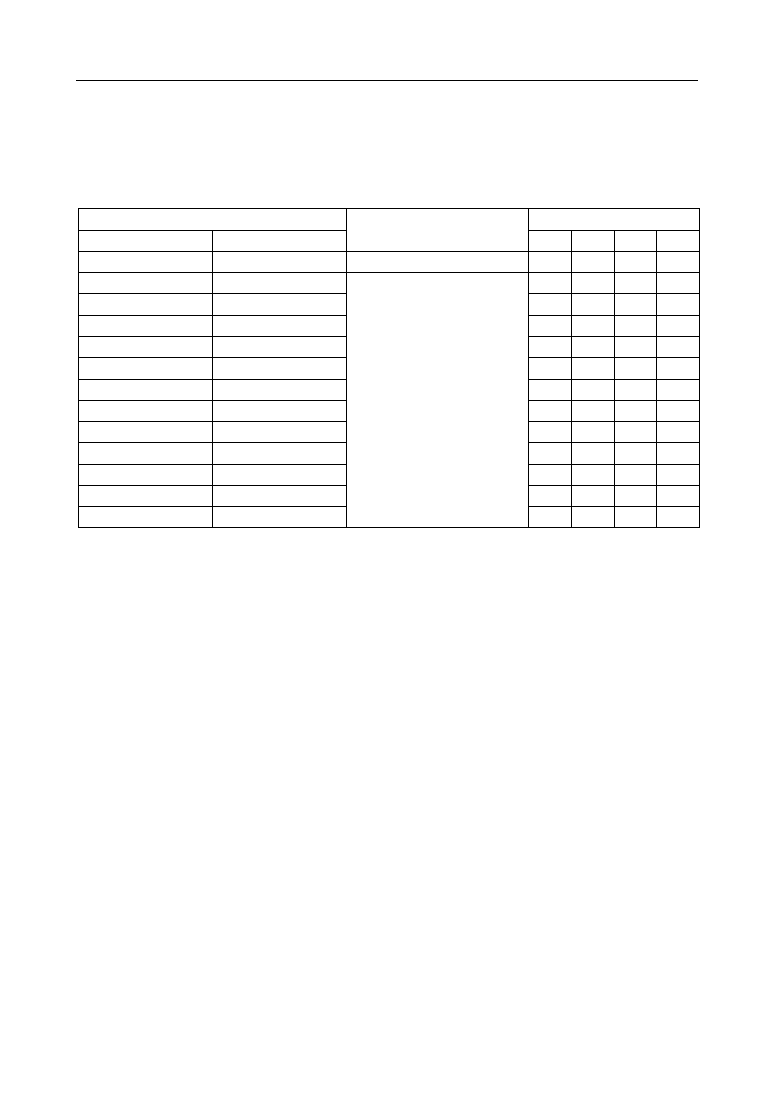

Table 1 Pin Descriptions (Basic Functions)

Function Symbol

TB

Type

V

DD

23

--

V

SS

22, 32

--

Power

Supply

V

DDI

21

--

V

DDL

27

--

V

DDH

24

--

CB1

25

--

CB2

26

--

XT0

28

I

Oscillation

XT1

29

O

OSC0

33

I

OSC1

34

O

Test

TST1B

30

I

TST2B

31

I

Reset

RESETB

35

I

Melody

MD

36

O

Description

Positive power supply

Negative power supply

Positive power supply pin for external interface (PORT8 supply)

Positive power supply pin for internal logic (internally generated).

A capacitor C

l

(0.1 mF) should be connected between this pin and V

SS

.

Voltage multiplier pin for power supply backup (internally generated).

A capacitor C

h

(1.0 mF) should be connected between this pin and V

SS

.

Pins to connect a capacitor for voltage multiplier.

A capacitor (1.0 mF) should be connected between CB1 and CB2.

Low-speed clock oscillation pins.

Crystal oscillation or RC oscillation is selected by the mask option.

If crystal oscillation is selected, connect a crystal between XT0 and

XT1, and connect capacitor (C

G

) between XT0 and V

SS

.

If RC oscillation is selected, connect external oscillation resistor

(R

CRL

) between XT0 and XT1.

High-speed clock oscillation pins.

Ceramic oscillation or RC oscillation is selected by the mask option.

If ceramic oscillation is selected, connect a ceramic resonator

between OSC0 and OSC1, and connect capacitor (C

L0

, C

L1

) between

OSC0 and V

SS

, OSC1 and V

SS

.

If RC oscillation is selected, connect external oscillation resistor

(R

CRH

) between OSC0 and OSC1.

Input pins for testing.

A pull-up resistor is internally connected to these pins.

Reset input pin.

Setting this pin to "L" level puts this device into a reset state.

Then, setting this pin to "H" level starts executing an instruction

from address 0000H.

An internal or external pull-up resistor is selected by mask option.

Melody output pin (non-inverted output)

TP

29

28, 42

27

37

30

35

36

38

39

43

44

40

41

45

46

Pin

° Semiconductor

ML63512A/63514A

8/29

Table 1 Pin Descriptions (Basic Functions) (continued)

Function

Symbol

TB

Type

P0.0/INT0

37

I/O

Port

Description

4-bit input-output ports.

In input mode, pull-up resistor input or high-impedance

input is selectable for each bit.

In output mode, N-channel open drain output or CMOS

output is selectable for each bit.

TP

51

Pin

P0.1/INT1

38

52

P0.2/INT2

39

53

P0.3/INT3

40

54

P1.0/

TM0CAP/

TM0OVF

41

55

P1.1/

TM1CAP/

TM1OVF

42

56

P1.2/T0CK

43

57

P1.3/T1CK

44

58

P2.0/TBCCLK

45

59

P2.1/HSCLK

46

60

P2.2

47

61

P2.3

48

62

P3.0/RXD

1

3

P3.1/TXC

2

4

P3.2/RXC

3

5

P3.3/TXD

4

6

P4.0

5

7

P4.1

6

8

P4.2

7

9

P4.3

8

10

P5.0

9

11

P5.1

10

12

P5.2

11

13

P5.3

12

14

I/O

I/O

I/O

I/O

I/O

° Semiconductor

ML63512A/63514A

9/29

Table 1 Pin Descriptions (Basic Functions) (continued)

4-bit output port.

N-channel open drain output.

Function

Symbol

TB

Type

P6.0

--

I

Port

Description

4-bit input-output port.

In input mode, pull-up resistor input or high-impedance

input is selectable for each bit.

In output mode, N-channel open drain output or CMOS

output is selectable for each bit.

Note that these pins are available for only a 64-pin package.

TP

15

Pin

P7.0/CMPIN

13

19

P7.1/CMPREF

14

20

P7.2/LDIN0

15

21

P7.3/LDIN1

16

22

P8.0

17

23

P8.1

18

24

P8.2

19

25

P8.3

20

26

4-bit input port.

Pull-up resistor input or high-impedance input is selectable

for each bit.

I/O

O

P6.1

--

16

P6.2

--

17

P6.3

--

18

P9.0

--

47

P9.1

--

48

P9.2

--

49

P9.3

--

50

PA.0

--

63

PA.1

--

64

PA.2

--

1

PA.3

--

2

4-bit input-output ports.

In input mode, pull-up resistor input or high-impedance

input is selectable for each bit.

In output mode, N-channel open drain output or CMOS

output is selectable for each bit.

Note that these pins are available for only a 64-pin package.

I/O

I/O

° Semiconductor

ML63512A/63514A

10/29

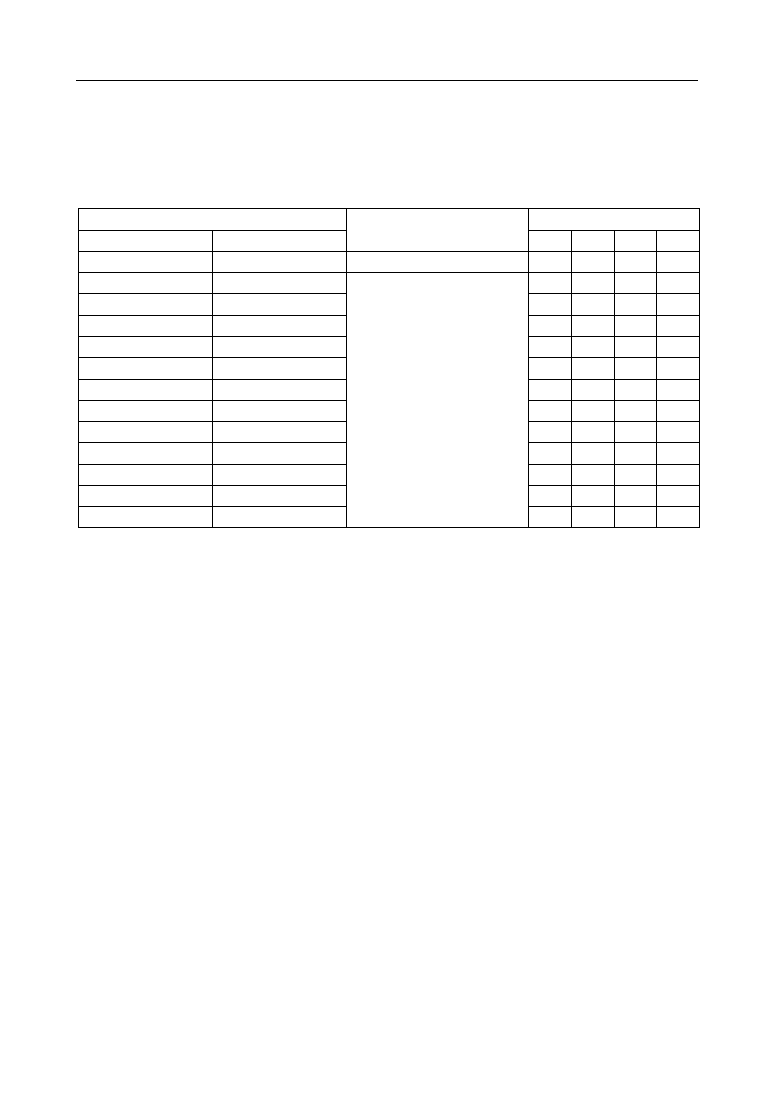

Table 2 shows the secondary functions of each pin of the ML63512A/63514A.

Table 2 Pin Descriptions (Secondary Functions)

Function

Symbol

Type

Description

TB

TP

Pin

P0.0/INT0

37

51

Capture

External 0 interrupt input pin.

Edge detection can be selected from one of a rising edge,

a falling edge, or both rising and falling edges.

I

P0.1/INT1

38

52

External 1 interrupt input pin.

Edge detection can be selected from one of a rising edge,

a falling edge, or both rising and falling edges.

P0.2/INT2

39

53

External 2 interrupt input pin.

Edge detection can be selected from one of a rising edge,

a falling edge, or both rising and falling edges.

P0.3/INT3

40

54

P1.0/TM0CAP

41

55

I

Timer 0 (TM0) capture trigger input pin.

P1.1/TM1CAP

42

56

I

Timer 1 (TM1) capture trigger input pin.

External

Interrupt

External 3 interrupt input pin.

Edge detection can be selected from one of a rising edge,

a falling edge, or both rising and falling edges.

I

I

I

P1.0/TM0OVF

41

55

O

Timer 0 (TM0) overflow flag output pin.

P1.1/TM1OVF

42

56

O

Timer 1 (TM1) overflow flag output pin.

P1.2/T0CK

43

57

I

Timer 0 (TM0) external clock input pin.

P1.3/T1CK

44

58

I

Timer 1 (TM1) external clock input pin.

Timer

P2.0/TBCCLK

45

59

O

Low-speed oscillation clock output pin.

P2.1/HSCLK

46

60

O

High-speed oscillation clock output pin.

Oscillation

Output

P3.0/RXD

1

3

I

Serial port receive data input pin.

Sync serial port clock input-output pin.

Transmit sync clock input-output pin when a serial port is used

synchronously.

Transmit clock output when this device is used as a master processor.

Transmit clock input when this device is used as a slave processor.

P3.1/TXC

2

4

I/O

Sync serial port clock input-output pin.

Receive sync clock input-output pin when a serial port is used

synchronously.

Receive clock output when this device is used as a master processor.

Receive clock input when this device is used as a slave processor.

P3.2/RXC

3

5

I/O

P3.3/TXD

4

6

O

Serial port transmit data output pin.

Serial

Port

P7.0/CMPIN

13

19

I

Comparator analog input pin.

P7.1/CMPREF

14

20

I

Comparator reference voltage input pin.

Comparator

P7.2/LDIN0

15

21

I

Level detector analog input pin.

P7.3/LDIN1

16

22

I

Level detector analog input pin.

Level

Detector

° Semiconductor

ML63512A/63514A

11/29

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Condition

Rating

Unit

Power Supply Voltage 1

V

DD

≠0.3 to +5.8

Power Supply Voltage 2

Ta = 25∞C

V

DDI

V

≠0.3 to +5.8

Power Supply Voltage 3

Ta = 25∞C

V

DDH

V

≠0.3 to V

DD

+ 0.3

Input Voltage 1

V

DD

Input, Ta = 25∞C

V

IN1

V

≠0.3 to V

DDI

+ 0.3

Input Voltage 2

V

DDI

Input, Ta = 25∞C

V

IN2

V

≠0.3 to V

DD

+ 0.3

Output Voltage 1

V

DD

Output, Ta = 25∞C

V

OUT1

V

≠0.3 to V

DDI

+ 0.3

Output Voltage 2

V

DDI

Output, Ta = 25∞C

V

OUT2

V

≠0.3 to V

DDH

+ 0.3

Output Voltage 3

V

DDH

Output, Ta = 25∞C

V

OUT3

V

≠55 to +150

Storage Temperature

--

T

STG

∞C

(V

SS

= 0 V)

≠0.3 to +5.8

Power Supply Voltage 4

Ta = 25∞C

V

DDL

V

≠0.3 to +5.8

Ta = 25∞C

V

60

Power Dissipation

Ta = 25∞C

P

D

mW

° Semiconductor

ML63512A/63514A

12/29

RECOMMENDED OPERATING CONDITIONS

∑ When backup is used

V

DDI

0.9 to 3.5

V

Crystal Oscillation Frequency

f

XT

30 to 80

kHz

Low-Speed RC Oscillator

Frequency

f

CRL

--

--

Parameter

Symbol

Condition

Range

Unit

Operating Temperature

T

op

≠20 to +70

∞C

V

DD

--

0.9 to 1.8

V

Operating Voltage

(V

SS

= 0 V)

--

External High-Speed RC

Oscillator Resistance

R

CRH

32

kHz

R

CRL

= 1 MW ±10%

100 to 300

kW

V

DD

= 0.9 to 1.8 V

V

DDI

1.8 to 5.5

Crystal Oscillation Frequency

f

XT

30 to 80

kHz

Low-Speed RC Oscillator

Frequency

f

CRL

kHz

--

--

Parameter

Symbol

Condition

Range

Unit

Operating Temperature

T

op

≠20 to +70

∞C

V

DD

--

1.8 to 3.5

Operating Voltage

(V

SS

= 0 V)

--

External High-Speed RC

Oscillator Resistance

R

CRH

kW

32

R

CRL

= 1 MW ±10%

15 to 300

V

DD

= 1.8 to 5.5 V

300k to 1M

V

DD

= 2.2 to 5.5 V

200k to 2M

V

DD

= 2.7 to 5.5 V

Ceramic Oscillation Frequency

f

CM

Hz

When Level detector and

Comparator are not used

1.8 to 5.5

V

∑ When backup is not used

° Semiconductor

ML63512A/63514A

13/29

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

5.8

9.0

15.0

5.3

5.3

5.3

4.8

--

--

Supply Current 1

I

DD1

CPU is in HALT state

High-speed oscillation stop

Level detector stop

mA

Supply Current 2

I

DD2

CPU operating

High-speed oscillation stop

Level detector stop

35.0

10.0

--

Supply Current 3

I

DD3

CPU operating at low speed

High-speed oscillation stop

Level detector active

(for a soft duty of about 3%)

mA

750.0

550.0

--

Supply Current 4

I

DD4

CPU operating at high speed

High-speed RC oscillation

R

CRH

= 100 kW

mA

1

Ta = 25∞C

Ta = ≠20 to +50∞C

Ta = ≠20 to +70∞C

14.0

16.0

24.0

13.0

13.0

13.0

12.0

--

--

mA

Ta = 25∞C

Ta = ≠20 to +50∞C

Ta = ≠20 to +70∞C

ELECTRICAL CHARACTERISTICS

DC Characteristics

∑ When backup is used

∑ When backup is not used

Parameter

Symbol

Condition

Mea-

suring

Circuit

(V

DD

= V

DDI

= 3.0 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Unit

Max.

Typ.

Min.

2.7

7.0

10.0

2.4

2.4

2.4

2.1

--

--

Supply Current 1

I

DD1

CPU is in HALT state

High-speed oscillation stop

Level detector stop

mA

Supply Current 2

I

DD2

CPU operating

High-speed oscillation stop

Level detector stop

25.0

6.0

--

Supply Current 3

I

DD3

CPU operating at low speed

High-speed oscillation stop

Level detector active

(for a soft duty of about 3%)

mA

550.0

410.0

--

Supply Current 4

I

DD4

CPU operating at high speed

High-speed RC oscillation

R

CRH

= 100 kW

mA

1

Ta = 25∞C

Ta = ≠20 to +50∞C

Ta = ≠20 to +70∞C

7.0

9.0

15.0

6.0

6.0

6.0

5.0

--

--

mA

Ta = 25∞C

Ta = ≠20 to +50∞C

Ta = ≠20 to +70∞C

1000.0

850.0

--

Supply Current 5

I

DD5

CPU operating at high speed

High-speed ceramic oscillation

(ceramic oscillation, 2 MHz)

mA

° Semiconductor

ML63512A/63514A

14/29

DC Characteristics (continued)

Parameter

(Pin Name)

V

DDH

Voltage

V

DDL

Voltage

Crystal Oscillation Start

Voltage

Crystal Oscillation Hold

Voltage

External Crystal Oscillator

Capacitance

Internal Crystal Oscillator

Capacitance

Internal High-Speed RC

Oscillator Capacitance

Input Pin Capacitance

(P0.0 to P0.3)

(P1.0 to P1.3)

(P7.0 to P7.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

High-speed clock stop

V

DD

= 1.5 V

2.8

--

3.0

V

DDH

High-speed clock oscillation

(RC oscillation, R

CRH

= 100 kW)

2.0

--

--

V

DDL

High-speed clock stop

1.0

1.5

2.0

High-speed clock oscillation

2.0

--

2.7

V

STA

Oscillation start time: within 5 seconds

1.2

--

--

V

HOLD

--

0.9

--

--

C

G

--

5.0

--

25.0

C

D

--

20.0

25.0

30.0

C

OS

--

8.0

12.0

16.0

C

IN

--

--

--

5.0

Symbol

Condition

Typ.

Min.

Max.

Mea-

suring

Circuit

1

Internal Low-Speed RC

Oscillator Capacitance

C

XT

--

10.0

15.0

20.0

V

V

V

V

V

V

pF

pF

pF

pF

Unit

pF

∑∑∑

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

° Semiconductor

ML63512A/63514A

15/29

DC Characteristics (continued)

≠0.2

≠1.3

≠2.5

Output Current 1

(P0.0 to P0.3)

(P1.0 to P1.3)

(P6.0 to P6.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

(MD)

I

OH1

V

DD

= 1.5 V

≠1.0

≠3.5

≠6.0

I

OL1

1.0

--

--

I

OH2Z

Output Current 2

(P8.0 to P8.3)

Output Current 3

(OSC1)

14.0

7.5

3.0

I

OL2

20.0

12.0

6.0

V

DD

= 3.0 V

V

DDI

= 1.5 V

V

DDI

= 3.0 V

V

OH1

= V

DD

≠ 0.5 V

V

OL1

= 0.5 V

V

OH2

= V

DD

V

OL2

= 0.5 V

I

OH3R

V

DD

= V

DDH

= 3.0 V

V

OH3R

= V

DDH

≠ 0.5 V

V

DD

= V

DDH

= 5.0 V

≠0.2

≠1.5

≠2.5

≠0.5

≠1.8

≠3.5

Parameter

(Pin Name)

Symbol

Condition

Typ.

Min.

Max.

Mea-

suring

Circuit

mA

mA

mA

mA

mA

mA

mA

Unit

2

∑∑∑

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

≠1.5

≠5.0

≠8.5

V

DD

= 5.0 V

mA

2.5

1.3

0.2

V

DD

= 1.5 V

6.0

3.0

1.0

V

DD

= 3.0 V

mA

mA

8.5

3.7

1.5

V

DD

= 5.0 V

mA

28.0

15.0

8.0

V

DDI

= 5.0 V

mA

I

OL3R

V

DD

= V

DDH

= 3.0 V

V

OL3R

= 0.5 V

V

DD

= V

DDH

= 5.0 V

2.5

1.5

0.2

3.5

1.8

0.5

mA

mA

I

OH3C

V

DD

= V

DDH

= 3.0 V

V

OH3C

= V

DDH

≠ 0.5 V

V

DD

= V

DDH

= 5.0 V

≠60

≠160

≠300

≠100

≠240

≠400

mA

mA

I

OL3C

V

DD

= V

DDH

= 3.0 V

V

OL3C

= 0.5 V

V

DD

= V

DDH

= 5.0 V

300

170

60

400

210

100

mA

mA

Output Leakage

(P0.0 to P0.3)

(P1.0 to P1.3)

(P6.0 to P6.3)

(P8.0 to P8.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

1.0

--

--

I

OOH

V

OH

= V

DD

--

--

≠1.0

I

OOL

V

OL

= V

SS

mA

mA

∑∑∑

° Semiconductor

ML63512A/63514A

16/29

DC Characteristics (continued)

I

IH4

V

IH4

= V

DD

V

DD

= 1.5 V

≠10.0

≠60.0

≠120.0

mA

≠100.0

≠350.0

≠600.0

I

IL4

V

IL4

= V

SS

(when pulled up)

mA

Parameter

(Pin Name)

Symbol

Condition

Mea-

suring

Circuit

Unit

1.0

--

--

Input Current 1

(P0.0 to P0.3)

(P1.0 to P1.3)

(P7.0 to P7.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

I

IH1U

mA

≠1.0

≠4.0

≠8.0

I

IL1U

mA

≠10.0

≠30.0

≠60.0

mA

1.0

--

--

I

IH1Z

V

IH1

= V

DD

(in a high-impedance state)

mA

--

--

≠1.0

I

IL1Z

V

IL1

= V

SS

(in a high-impedance state)

mA

≠30.0

≠170.0

≠350.0

I

IL3

V

IL3

= V

SS

(when pulled up)

mA

1.0

--

--

I

IH3R

V

IH3

= V

DDH

mA

--

--

≠1.0

I

IL3R

V

IL3

= V

SS

mA

V

DD

= 1.5 V

V

DD

= 3.0 V

V

IH1

= V

DD

(when pulled up)

V

IL1

= V

SS

(when pulled up)

I

IH2

V

IH2

= V

DD

V

DD

= 1.5 V

1.0

--

--

mA

≠2.0

≠20.0

≠45.0

mA

3

V

DD

= V

DDH

= 3.0 V

≠70.0

≠300.0

≠870.0

I

IL2

V

IL2

= V

SS

(when pulled up)

mA

Input Current 3

(OSC0)

Input Current 2

(RESETB)

Input Current 4

(TST1B, TST2B)

Max.

Typ.

Min.

V

DD

= 5.0 V

0.1

--

--

mA

V

DD

= 3.0 V

∑∑∑

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

≠23.0

≠90.0

≠150.0

mA

V

DD

= 5.0 V

≠30.0

≠120.0

≠260.0

mA

V

DD

= 3.0 V

≠200.0

≠450.0

≠750.0

mA

V

DD

= V

DDH

= 5.0 V

≠220.0

≠770.0

≠1320.0

mA

V

DD

= 5.0 V

° Semiconductor

ML63512A/63514A

17/29

DC Characteristics (continued)

Parameter

(Pin Name)

Symbol

Condition

Mea-

suring

Circuit

Unit

Max.

Typ.

Min.

0.30

0.10

0.05

V

T

V

1.0

0.5

0.2

V

V

DD

= 3.0 V

V

DD

= 1.5 V

Hysteresis Width

(P0.0 to P0.3)

(P1.0 to P1.3)

(P7.0 to P7.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

(RESETB)

(TST1B, TST2B)

1.5

--

1.2

V

IH1

V

3.0

--

2.4

V

V

DD

= 3.0 V

V

DD

= 1.5 V

0.3

--

0.0

V

IL1

V

0.6

--

0.0

V

V

DD

= 3.0 V

V

DD

= 1.5 V

Input Voltage 1

(P0.0 to P0.3)

(P1.0 to P1.3)

(P7.0 to P7.3)

(P9.0 to P9.3)

(PA.0 to PA.3)

∑∑∑

∑∑∑

(V

DD

= V

DDI

= 1.5 V, V

SS

= 0 V, Ta = ≠20 to +70∞C unless otherwise specified)

Input Voltage 2

(OSC0)

3.0

--

2.4

V

IH2

V

5.0

--

4.0

V

V

DD

= V

DDH

= 5.0 V

V

DD

= V

DDH

= 3.0 V

0.6

--

0.0

V

1.0

--

0.0

V

V

DD

= V

DDH

= 5.0 V

V

DD

= V

DDH

= 3.0 V

5.0

--

4.0

V

V

DD

= 5.0 V

1.0

--

0.0

V

V

DD

= 5.0 V

V

IL2

0.15

--

0.00

V

IL3

V

0.6

--

0.0

V

V

DD

= 3.0 V

V

DD

= 1.5 V

4

1.50

--

1.35

V

IH3

V

3.0

--

2.4

V

V

DD

= 3.0 V

V

DD

= 1.5 V

Input Voltage 3

(RESETB)

(TST1B, TST2B)

5.0

--

4.0

V

V

DD

= 5.0 V

1.0

--

0.0

V

V

DD

= 5.0 V

1.50

1.00

0.25

V

V

DD

= 5.0 V

° Semiconductor

ML63512A/63514A

18/29

Hysteresis width

Input Signal

V

T

V

DD

V

SS

Internal Signal

V

DDL

V

SS

° Semiconductor

ML63512A/63514A

19/29

Measuring circuit 1

V

C

l

V

C

h

A

V

SS

V

DD

V

DDH

V

DDL

V

DDI

CB1

CB2

XT0

XT1

q

w

*1

OSC0

e

OSC1

r

C

G

C

b12

, C

h

C

l

C

O

Ceramic Resonator

C

L0

C

L1

: CSA2.00MG (2 MHz)

CSB1000J (1 MHz)

(Murata MFG.-make)

C

b12

C

G

q

w

q

w

R

CRL

*1

Crystal oscillator

e

r

R

CRH

RC oscillator

*2

RC oscillator

C

L0

e

r

Ceramic oscillator

C

L1

: 15 pF

: 1 mF

: 0.1 mF

: 12 pF

: 30 pF

: 30 pF

Ceramic resonator

*2

° Semiconductor

ML63512A/63514A

20/29

Measuring circuit 2

A

*4

V

SS

V

DD

V

DDH

V

DDL

V

DDI

*3

V

IH

V

IL

*3 Input logic circuit to determine the specified measuring conditions.

*4 Measured at the specified output pins.

INPUT

OUTPUT

Measuring circuit 3

V

SS

V

DD

V

DDH

V

DDL

V

DDI

A

*5

INPUT

OUTPUT

° Semiconductor

ML63512A/63514A

21/29

Measuring circuit 4

V

SS

V

DD

V

DDH

V

DDL

V

DDI

*5

V

IH

V

IL

*5 Measured at the specified input pins.

INPUT

OUTPUT

Waveform

Monitoring

° Semiconductor

ML63512A/63514A

22/29

TXD (P3.3)

RXD (P3.0)

t

CYC

t

DDR

t

r

t

f

t

CWH

t

CWL

t

DDR

t

DS

t

DS

t

DH

V

DD

(5.0 V)

V

SS

V

DD

(5.0 V)

V

SS

V

DD

(5.0 V)

V

SS

TXC (P3.1)/

RXC (P3.2)

AC Characteristics (Serial Interface, Serial Port)

(V

DD

= 0.9 to 5.5 V, V

DDH

= 1.8 to 5.5 V, V

SS

= 0 V, V

DDI

= 0.9 to 5.5 V, Ta = ≠20 to +70

∞

C unless

otherwise specified)

(1) Synchronous Communication

Parameter

Symbol

Condition

Unit

--

TXC/RXC Input Fall Time

Max.

Typ.

Min.

t

f

--

ms

--

1.0

--

TXC/RXC Input Rise Time

t

r

--

ms

--

1.0

0.8

TXC/RXC Input "L" Level

Pulse Width

t

CWL

--

ms

--

--

0.8

TXC/RXC Input "H" Level

Pulse Width

t

CWH

--

ms

--

--

2.0

TXC/RXC Input Cycle Time

t

CYC

--

ms

--

--

--

TXC/RXC Output Cycle Time

t

CYC1(O)

CPU operating at 32.768 kHz

ms

30.5

--

--

t

CYC2(O)

CPU operating at 2 MHz

V

DD

= V

DDH

= 2.7 to 5.5 V

ms

0.5

--

--

TXD Output Delay Time

t

DDR

Output load capacitance 10 pF

ms

--

0.4

0.5

RXD Input Setup Time

t

DS

--

ms

--

--

0.8

RXD Input Hold Time

t

DH

--

ms

--

--

Synchronous communication timing

("H" level = 4.0 V, "L" level = 1.0 V)

° Semiconductor

ML63512A/63514A

23/29

TXD (P3.3)

T

BRT

V

DD

(5.0 V)

V

SS

RXD (P3.0)

R

BRT

V

DD

(5.0 V)

V

SS

(2) UART Communication

Parameter

Symbol

Condition

Unit

T

BRT

≠T

CR

Transmit Baud Rate

Max.

Typ.

Min.

T

BRT

T

BRT

= 1/f

BRT

T

CR

= 1/f

OSC

s

T

BRT

T

BRT

+T

CR

R

BRT

•0.97

Receive Baud Rate

R

BRT

s

R

BRT

R

BRT

•1.03

R

BRT

= 1/f

BRT

f

BRT

: Baud rates (2TBCCLK, TBCCLK, 1/2TBCCLK, Timer 0/1 overflow)

UART communication timing

("H" level = 4.0 V, "L" level = 1.0 V)

° Semiconductor

ML63512A/63514A

24/29

AC Characteristics

Parameter

Symbol

Condition

Unit

20

External Interrupt Enable

Pulse Width (Rising Edge)

Max.

Typ.

Min.

t

WH

--

ns

--

--

(V

DD

= V

DDI

= 0.9 to 5.5 V, V

SS

= 0 V, Ta = ≠20 to + 70∞C unless otherwise specified)

20

External Interrupt Enable

Pulse Width (Falling Edge)

t

WL

--

ns

--

--

13.0

External Interrupt Disable

Time

t

NUL

Interrupt enable, MIE = 1

CPU operating under

the NOP instruction

System clock: 32.768 kHz

ms

--

65.1

AC characteristics timing

t

WH

t

NUL

t

WL

t

NUL

P0.0 to P0.3

(Interrupt on the rising edge)

P0.0 to P0.3

(Interrupt on the falling edge)

P0.0 to P0.3

(Interrupt on both rising and falling edges)

t

NUL

° Semiconductor

ML63512A/63514A

25/29

Comparator Electrical Characteristics

Conceptual diagram of comparator supply current

The conceptual diagram of the comparator supply current I

DDCMP

and I

DSCMP

is shown below.

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Comparator Offset

Voltage

Vcoff

--

--

--

30

mV

Comparator Conversion

Time

T

C

System clock: 32.768 kHz

--

183

--

ms

Comparator Supply

Current

I

DDCMP

Comparator operating

--

30

90

mA

(V

DD

= 0.9 V, V

SS

= 0 V, Ta = ≠20 to +70∞C)

Comparator Input

Voltage

Vcin

--

V

SS

--

V

DD

V

I

DSCMP

Comparator stopped

--

--

0.1

mA

Remarks

CMPIN

CMPREF

Sampling reference voltage

Comparing

reference

voltage with

input voltage

t [ms]

I

DDCMP

I

DSCMP

I

DD

(V

SS

)

[mA]

Level detector operating

Level detector stopped

Level detector stopped

° Semiconductor

ML63512A/63514A

26/29

Level Detector Electrical Characteristics

Conceptual diagram of level detector supply current

The conceptual diagram of the level detector supply current I

DDLD

and I

DSLD

is shown below.

Parameter

Symbol

Condition

Min.

Typ.

Max.

Unit

Level Detector Input

Voltage

V

LD

--

V

SS

--

V

DD

V

Level Dtector Supply

Current

T

C

System clock: 32.768 kHz

--

183

--

ms

I

DDLD

Level detector operating

--

80

130

mA

(V

DD

= 0.9 V, V

SS

= 0 V, Ta = ≠20 to +70∞C)

Level Detector Conversion

Time

I

DSLD

Level detector stopped

--

--

0.1

mA

Remarks

LDIN0, 1

Sampling reference voltage

Comparing

reference

voltage with

input voltage

t [ms]

I

DDLD

I

DSLD

I

DD

(V

SS

)

[mA]

Level detector operating

Level detector stopped

Level detector stopped

° Semiconductor

ML63512A/63514A

27/29

Level Detector Input Levels and Output Codes

(V

DD

= 0.9 to 1.8 V: when backup is used, V

DD

= 1.8 to 3.5 V: when backup is not used;

V

SS

= 0 V, Ta = ≠20 to +70

∞

C)

Input Level [V]

Min.

Max.

1440/1500 • V

DD

V

DD

1306/1500 • V

DD

1366/1500 • V

DD

1190/1500 • V

DD

1250/1500 • V

DD

1074/1500 • V

DD

1134/1500 • V

DD

958/1500 • V

DD

1018/1500 • V

DD

842/1500 • V

DD

902/1500 • V

DD

726/1500 • V

DD

786/1500 • V

DD

610/1500 • V

DD

670/1500 • V

DD

494/1500 • V

DD

554/1500 • V

DD

378/1500 • V

DD

438/1500 • V

DD

262/1500 • V

DD

322/1500 • V

DD

146/1500 • V

DD

206/1500 • V

DD

V

SS

88/1500 • V

DD

LDOUT

bit 0

1

1

0

1

0

1

0

1

0

1

0

1

0

bit 1

1

1

1

0

0

1

1

0

0

1

1

0

0

bit 2

1

0

0

0

0

1

1

1

1

0

0

0

0

bit 3

1

1

1

1

1

0

0

0

0

0

0

0

0

Level Detector

Operation State

OFF state

ON state

° Semiconductor

ML63512A/63514A

28/29

(Unit : mm)

PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, TQFP, LQFP, SOJ, QFJ (PLCC), SHP, and BGA are surface mount type

packages, which are very susceptible to heat in reflow mounting and humidity absorbed in

storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person

on the product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

TQFP48-P-0707-0.50-K

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.13 TYP.

Mirror finish

° Semiconductor

ML63512A/63514A

29/29

(Unit : mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, TQFP, LQFP, SOJ, QFJ (PLCC), SHP, and BGA are surface mount type

packages, which are very susceptible to heat in reflow mounting and humidity absorbed in

storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person

on the product name, package name, pin number, package code and desired mounting conditions

(reflow method, temperature and times).

TQFP64-P-1010-0.50-K

Package material

Lead frame material

Pin treatment

Solder plate thickness

Package weight (g)

Epoxy resin

42 alloy

Solder plating

5 mm or more

0.26 TYP.

Mirror finish

NOTICE

1.

The information contained herein can change without notice owing to product and/or

technical improvements. Before using the product, please make sure that the information

being referred to is up-to-date.

2.

The outline of action and examples for application circuits described herein have been

chosen as an explanation for the standard action and performance of the product. When

planning to use the product, please ensure that the external conditions are reflected in the

actual circuit, assembly, and program designs.

3.

When designing your product, please use our product below the specified maximum

ratings and within the specified operating ranges including, but not limited to, operating

voltage, power dissipation, and operating temperature.

4.

Oki assumes no responsibility or liability whatsoever for any failure or unusual or

unexpected operation resulting from misuse, neglect, improper installation, repair, alteration

or accident, improper handling, or unusual physical or electrical stress including, but not

limited to, exposure to parameters beyond the specified maximum ratings or operation

outside the specified operating range.

5.

Neither indemnity against nor license of a third party's industrial and intellectual property

right, etc. is granted by us in connection with the use of the product and/or the information

and drawings contained herein. No responsibility is assumed by us for any infringement

of a third party's right which may result from the use thereof.

6.

The products listed in this document are intended for use in general electronics equipment

for commercial applications (e.g., office automation, communication equipment,

measurement equipment, consumer electronics, etc.). These products are not authorized

for use in any system or application that requires special or enhanced quality and reliability

characteristics nor in any system or application where the failure of such system or

application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety

devices, aerospace equipment, nuclear power control, medical equipment, and life-support

systems.

7.

Certain products in this document may need government approval before they can be

exported to particular countries. The purchaser assumes the responsibility of determining

the legality of export of these products and will take appropriate and necessary steps at their

own expense for these.

8.

No part of the contents contained herein may be reprinted or reproduced without our prior

permission.

9.

MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.

Printed in Japan

E2Y0002-29-62