° Semiconductor

ML7000-01/02/03/ML7001-01/02/03

1/19

° Semiconductor

ML7000-01/02/03

ML7001-01/02/03

Single Rail CODEC

GENERAL DESCRIPTION

The ML7000/ML7001 are single-channel CMOS CODEC LSI devices for voice signals ranging

from 300 to 3400 Hz with filters for A/D and D/A conversion.

Designed especially for a single-power supply and low-power applications, the devices are

optimized for ISDN terminals, digital wireless systems, and digital PBXs.

The devices use the same transmission clocks as those used in the MSM7507.

With the differential analog signal outputs which can drive 60 W load, the devices can directly

drive a handset receiver.

FEATURES

∑ Single power supply: +5 V (ML7000-xx)

+3 V (ML7001-xx)

∑ Low power consumption

Operating mode:

25 mW Typ.

V

DD

= 5.0 V (ML7000-xx)

20 mW Typ.

V

DD

= 3.0 V (ML7001-xx)

Power-down mode:

0.05 mW Typ.

V

DD

= 5.0 V (ML7000-xx)

0.03 mW Typ.

V

DD

= 3.0 V (ML7001-xx)

∑ Conforms to ITU-T Companding law

ML7000-01/ML7001-01:

m/A-law pin selectable

ML7000-02/ML7001-02:

m-law

ML7000-03/ML7001-03:

A-law

∑ Transmission characteristics conform to ITU-T G.714

∑ Short frame sync timing operation

∑ Built-in PLL eliminates a master clock

∑ Serial data rate: 64/96/128/192/200/256/384/512/

768/1024/1536/1544/2048 kHz

∑ Adjustable transmit gain

∑ Adjustable receive gain

∑ Built-in reference voltage supply

∑ Package options:

24-pin plastic SOP (SOP24-P-430-1.27-K)

(Product name: ML7000-01MA/ML7001-01MA)

(Product name: ML7000-02MA/ML7001-02MA)

(Product name: ML7000-03MA/ML7001-03MA)

20-pin plastic SSOP (SSOP20-P-250-0.95-K) (Product name: ML7000-01MB/ML7001-01MB)

(Product name: ML7000-02MB/ML7001-02MB)

(Product name: ML7000-03MB/ML7001-03MB)

E2U0062-18-84

This version: Aug. 1998

Preliminary

° Semiconductor

ML7000-01/02/03/ML7001-01/02/03

2/19

BLOCK DIAGRAM

RC

LPF

8th

BPF

A/D

CONV.

TCONT

AUTO

ZERO

5th

LPF

D/A

CONV.

PWD

Logic

PLL

RTIM

RCONT

PCMOUT

PCMIN

PDN

V

DD

AG

DG

SG

GEN

SGC

SG

PWD

≠

+

AIN≠

AIN+

GSX

≠

+

VFRO

RSYNC

BCLK

XSYNC

(ALAW)

VR

GEN

≠

+

AOUT≠

PWI

≠

+

AOUT+

° Semiconductor

ML7000-01/02/03/ML7001-01/02/03

3/19

PIN CONFIGURATION (TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

SG

AOUT+

AOUT≠

PWI

VFRO

V

DD

DG

PDN

SGC

AIN+

AIN≠

GSX

AG

BCLK

20-Pin Plastic SSOP

RSYNC

PCMIN

XSYNC

PCMOUT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

SG

AOUT+

AOUT≠

PWI

VFRO

DG

PDN

SGC

AIN+

AIN≠

GSX

AG

24-Pin Plastic SOP

RSYNC

PCMIN

XSYNC

PCMOUT

V

DD

BCLK

(ALAW)*

NC

NC

NC

(ALAW)*

NC

NC

NC

* The ALAW pin is only supported by the ML7000-01MA/ML7000-01MB/ML7001-01MA/

ML7001-01MB.

NC : No connect pin

° Semiconductor

ML7000-01/02/03/ML7001-01/02/03

4/19

PIN FUNCTIONAL DESCRIPTION

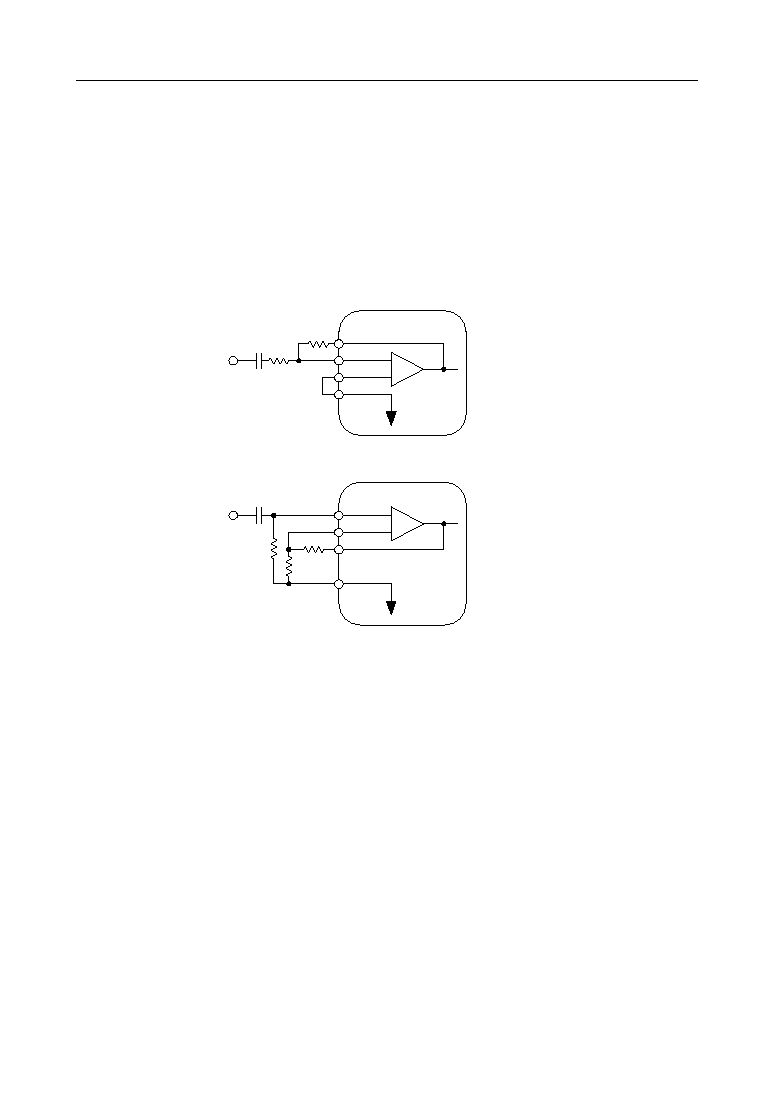

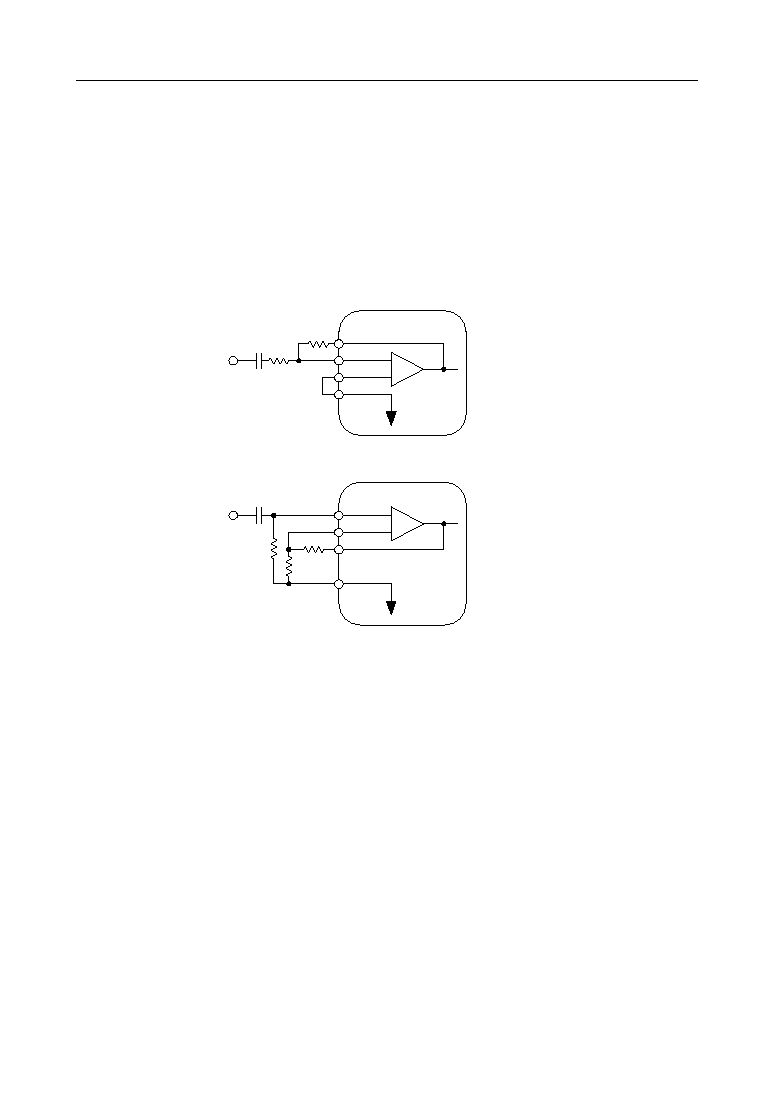

AIN+, AIN≠, GSX

Transmit analog input and transmit level adjustment.

AIN+ is a non-inverting input to the op-amp; AIN≠ is an inverting input to the op-amp; GSX is

connected to the output of the op-amp.

The level adjustment should be performed using any of the methods shown below. During

power-saving and power-down modes, the GSX output is at AG voltage.

AG

Analog ground.

VFRO

Receive filter output.

The output signal has an amplitude of 2.4 V

PP

for ML7000-xx and 2.0 V

PP

for ML7001-xx above

and below the signal ground voltage (SG) when the digital signal of +3 dBm0 is input to PCMIN

and can drive a load of 20 kW or more.

For driving a load of less than 20 kW, connect a resistor of 20 kW or more between the pins VFRO

and PWI.

During power-saving or power-down mode, the VFRO output is at an SG level.

When adjusting the receive signal on the basis of frequency characteristics, refer to the Frequency

Characteristics Adjustment Circuit.

≠

+

AIN≠

AIN+

C1

Analog input

R1 : variable

R2 > 20 kW

C1 > 1/(2 • 3.14 • 30 • R1)

R2

GSX

SG

+

≠

AIN+

AIN≠

R3 > 20 kW

R4 > 20 kW

R5 > 50 kW

C2 > 1/ (2 • 3.14 • 30 • R5)

R4

GSX

SG

C2

Analog input

R3

R5

R1

° Semiconductor

ML7000-01/02/03/ML7001-01/02/03

5/19

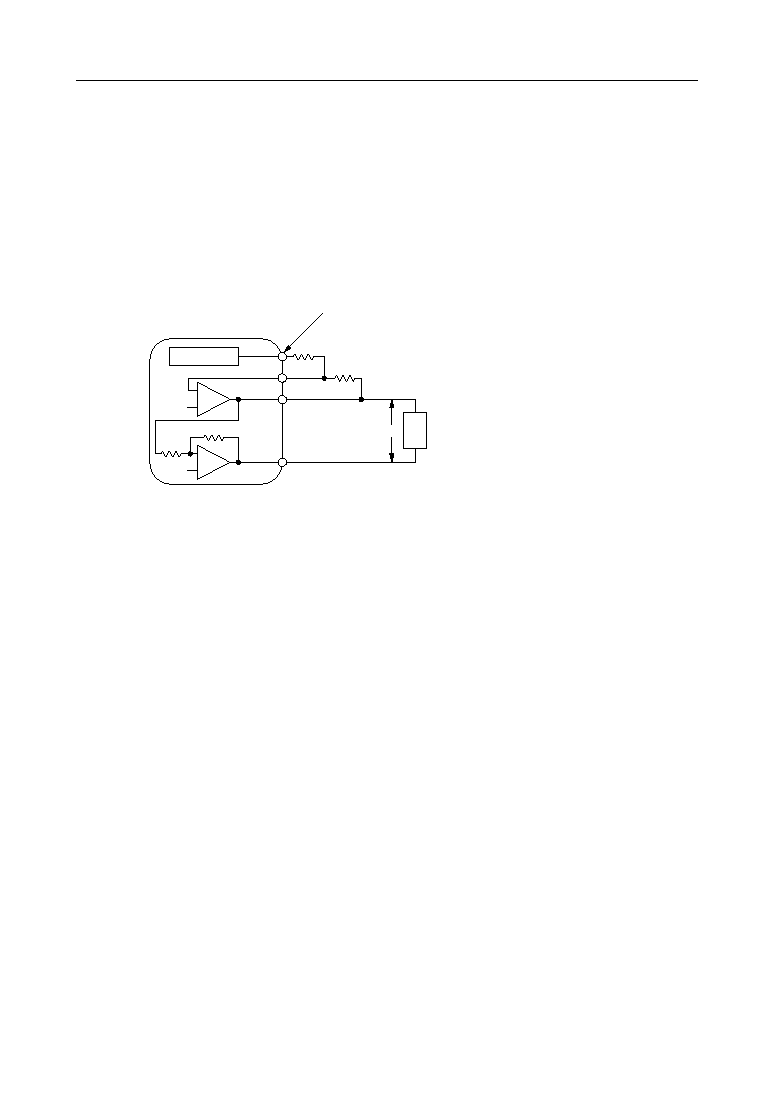

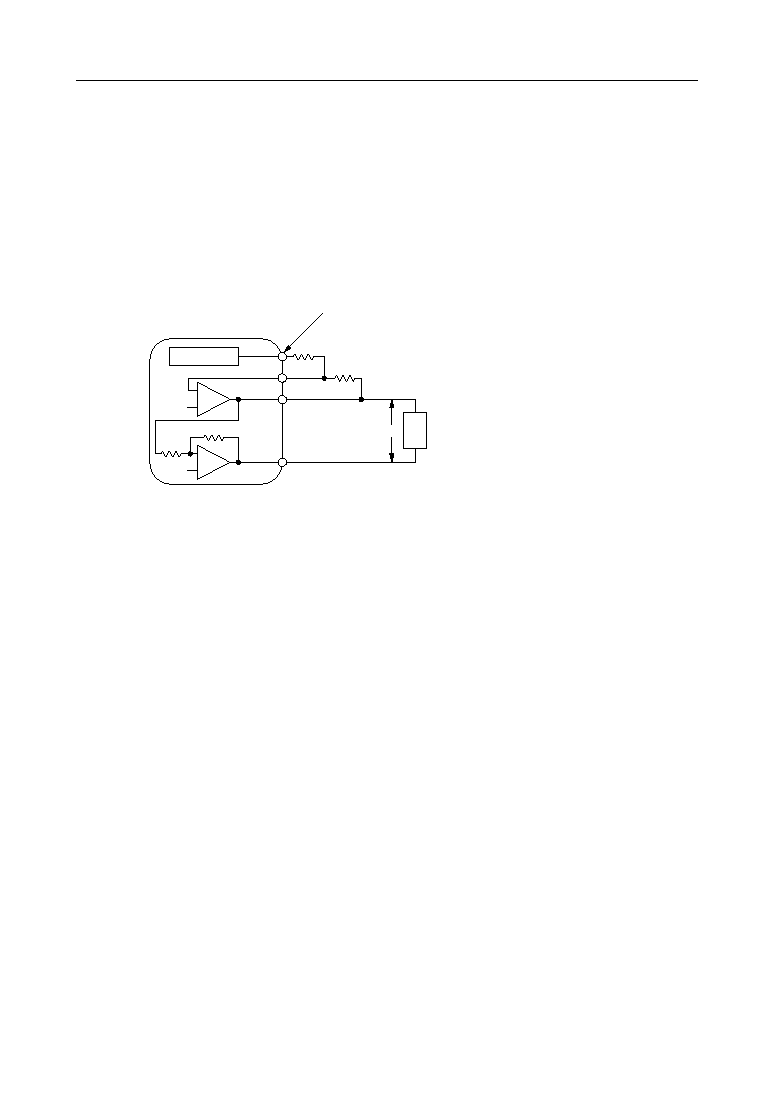

PWI, AOUT+, AOUT≠

PWI is connected to the inverting input of the receive driver.

The receive driver output is connected to the AOUT≠ pin. Therefore, the receive level can be

adjusted with the pins VFRO, PWI, and AOUT≠. During power-saving or power down-mode,

the outputs of AOUT+ and AOUT≠ are in a high impedance state. The output of AOUT+ is

inverted with respect to the output of AOUT≠. Since these outputs provide differential drive of

an impedance of 1.2 kW, they can directly be connected to a handset using a piezoelectric

earphone or a line transformer. Refer to the application example.

V

DD

Power supply for +5 V (ML7000-xx) or +3 V (ML7001-xx)

PCMIN

PCM data input.

A serial PCM data input to this pin is converted to an analog signal in synchronization with the

RSYNC signal and BCLK signal.

The data rate of PCM is equal to the frequency of the BCLK signal.

PCM signal is shifted in at the falling edge of the BCLK signal and latched into the internal

register when shifted by eight bits.

The start of the PCM data (MSD) is identified at the rising edge of RSYNC.

BCLK

Shift clock signal input for the PCMIN and PCMOUT signals.

The frequency, equal to the data rate, is 64, 96, 128, 192, 256, 384, 512, 768, 1024, 1536, 1544, or 2048

kHz. Setting this signal to logic "1" or "0" drives both transmit and receive circuits to the power

saving state.

R6 > 20 kW

ZL > 1.2 kW

Gain = VO/VI = 2 5 R7/R6 £ 2

R6

R7

≠

+

SG

≠

+

SG

VFRO

PWI

AOUT≠

AOUT+

ZL

Receive filter

VI

VO

20 kW

20 kW