5-1

FAST AND LS TTL DATA

OCTAL BUFFER/LINE DRIVER

WITH 3-STATE OUTPUTS

The SN54 / 74LS540 and SN54 / 74LS541 are octal buffers and line drivers

with the same functions as the LS240 and LS241, but with pinouts on the

opposite side of the package.

These device types are designed to be used as memory address drivers,

clock drivers and bus-oriented transmitters / receivers. These devices are

especially useful as output ports for the microprocessors, allowing ease of

layout and greater PC board density.

∑

Hysteresis at Inputs to Improve Noise Margin

∑

PNP Inputs Reduce Loading

∑

3-State Outputs Drive Bus Lines

∑

Inputs and Outputs Opposite Side of Package, Allowing Easier

Interface to Microprocessors

∑

Input Clamp Diodes Limit High-Speed Termination Effects

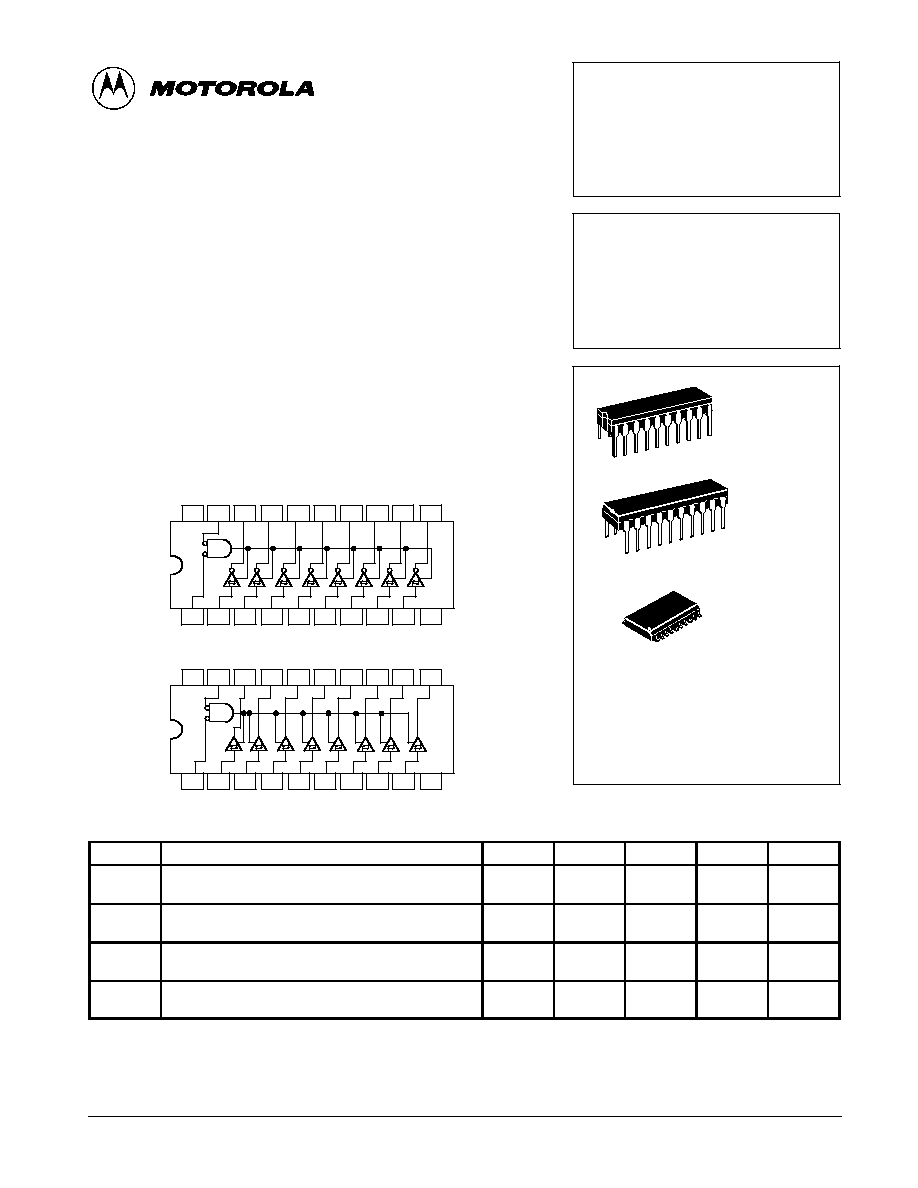

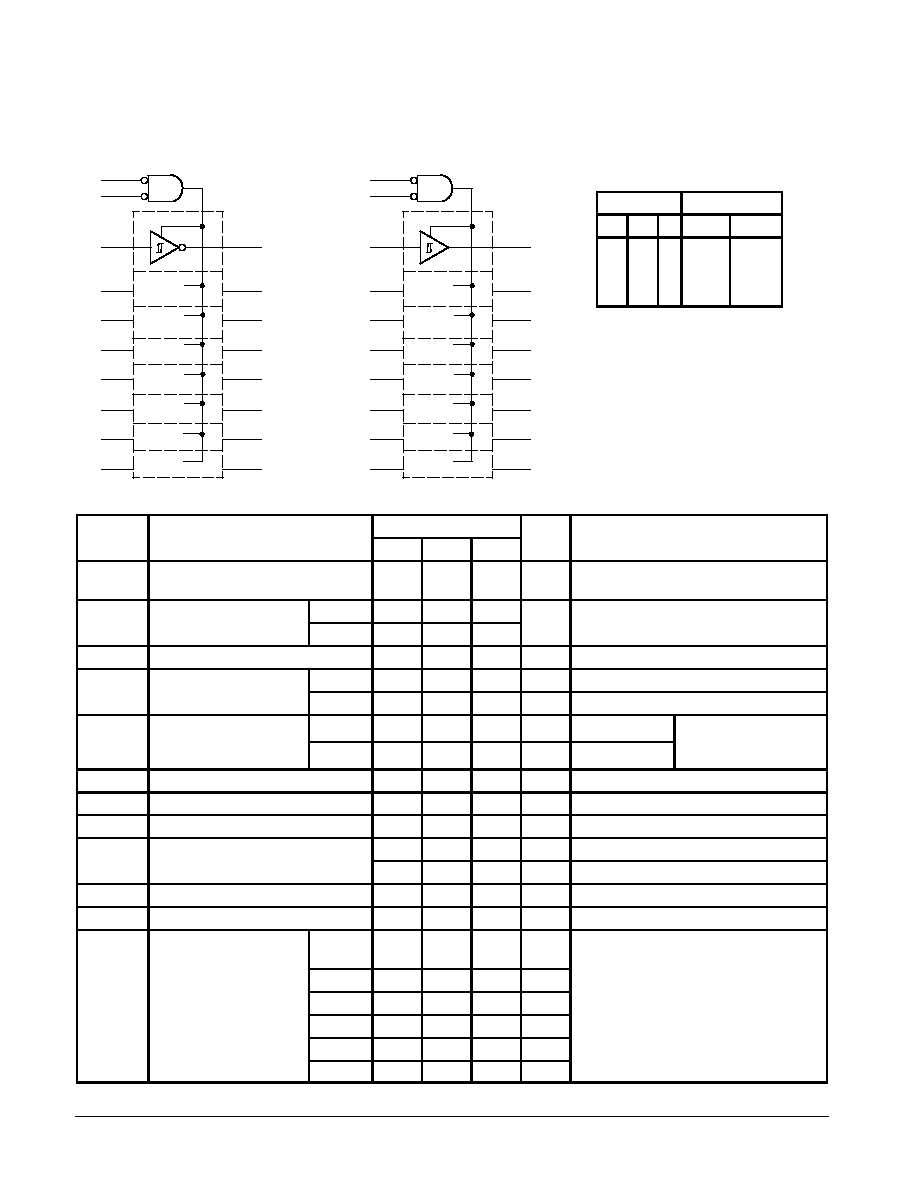

LOGIC AND CONNECTION DIAGRAMS DIP (TOP VIEW)

18

17

16

15

14

13

1

2

3

4

5

6

7

20

19

8

VCC

9

10

GND

12

11

SN54 / 74LS540

SN54 / 74LS541

18

17

16

15

14

13

1

2

3

4

5

6

7

20

19

8

VCC

9

10

GND

12

11

GUARANTEED OPERATING RANGES

Symbol

Parameter

Min

Typ

Max

Unit

VCC

Supply Voltage

54

74

4.5

4.75

5.0

5.0

5.5

5.25

V

TA

Operating Ambient Temperature Range

54

74

≠ 55

0

25

25

125

70

∞

C

IOH

Output Current -- High

54

74

≠ 12

≠ 15

mA

IOL

Output Current -- Low

54

74

12

24

mA

SN54/74LS540

SN54/74LS541

OCTAL BUFFER / LINE DRIVER

WITH 3-STATE OUTPUTS

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ

Ceramic

SN74LSXXXN

Plastic

SN74LSXXXDW SOIC

20

1

J SUFFIX

CERAMIC

CASE 732-03

20

1

N SUFFIX

PLASTIC

CASE 738-03

20

1

DW SUFFIX

SOIC

CASE 751D-03

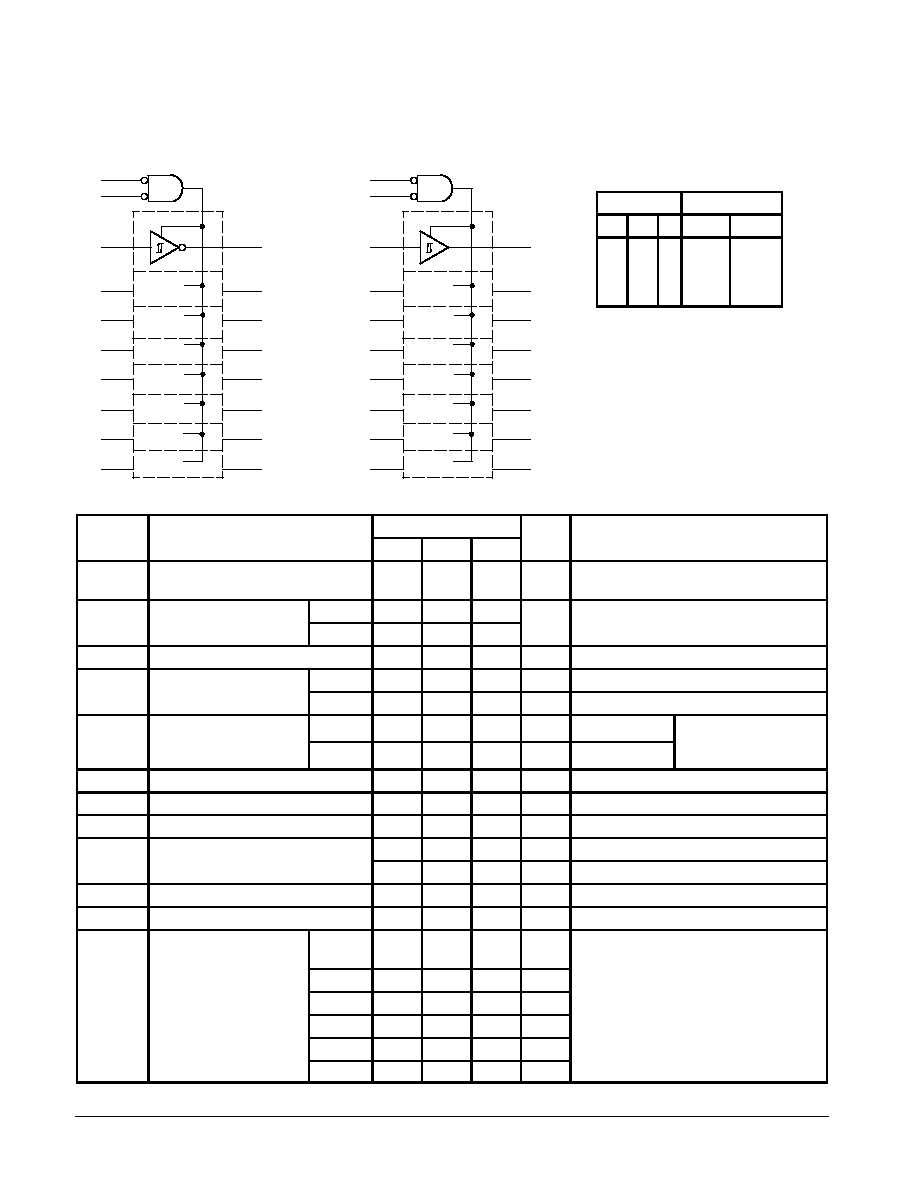

BLOCK DIAGRAM

LS540

LS541

E1

E2

D1

D2

D3

D4

D5

D6

D7

D8

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

(1)

(19)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(11)

(12)

(13)

(14)

(15)

(16)

(17)

(18)

E1

E2

D1

D2

D3

D4

D5

D6

D7

D8

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

(1)

(19)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(11)

(12)

(13)

(14)

(15)

(16)

(17)

(18)

5-2

FAST AND LS TTL DATA

SN54/74LS540

∑

SN54/74LS541

INPUTS

OUTPUTS

E1

E2

D

LS540

LS541

L

L

H

L

H

H

X

X

Z

Z

X

H

X

Z

Z

L

L

L

H

L

L = LOW Voltage Level

H = HIGH Voltage Level

X = Immaterial

Z = High Impedance

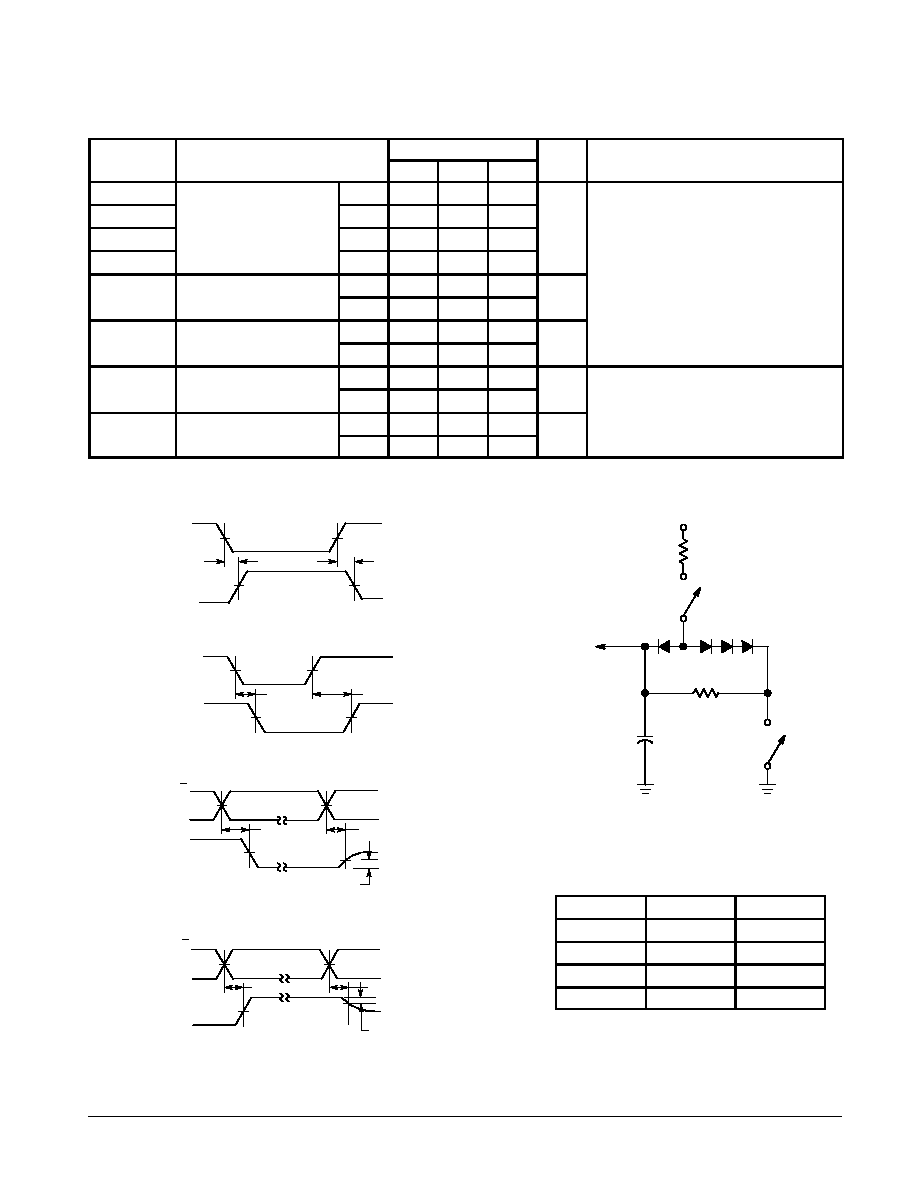

DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

(unless otherwise specified)

S

b l

P

Limits

U i

T

C

di i

Symbol

Parameter

Min

Typ

Max

Unit

Test Conditions

VIH

Input HIGH Voltage

2.0

V

Guaranteed Input HIGH Voltage for

All Inputs

VIL

Input LOW Voltage

54

0.7

V

Guaranteed Input LOW Voltage for

VIL

Input LOW Voltage

74

0.8

V

p

g

All Inputs

VIK

Input Clamp Diode Voltage

≠ 0.65

≠ 1.5

V

VCC = MIN, IIN = ≠ 18 mA

VOH

Output HIGH Voltage

54, 74

2.4

3.4

V

VCC = MIN, IOH = ≠ 3.0 mA

VOH

Output HIGH Voltage

54, 74

2.0

V

VCC = MIN, IOH = MAX, VIL = 0.5 V

VOL

Output LOW Voltage

54, 74

0.25

0.4

V

IOL = 12 mA

VCC = VCC MIN,

VIN = VIL or VIH

VOL

Output LOW Voltage

74

0.35

0.5

V

IOL = 24 mA

VIN = VIL or VIH

per Truth Table

VT+≠VT≠

Hysteresis

0.2

0.4

V

VCC = MIN

IOZH

Output Off Current HIGH

20

µ

A

VCC = MAX, VOUT = 2.7 V

IOZL

Output Off Current LOW

≠ 20

µ

A

VCC = MAX, VOUT = 0.4 V

IIH

Input HIGH Current

20

µ

A

VCC = MAX, VIN = 2.7 V

IIH

Input HIGH Current

0.1

mA

VCC = MAX, VIN = 7.0 V

IIL

Input LOW Current

≠ 0.2

mA

VCC = MAX, VIN = 0.4 V

IOS

Short Circuit Current (Note 1)

≠ 40

≠ 225

mA

VCC = MAX

I

Power Supply Current

Total, Output HIGH

LS540

25

mA

V

MAX

I

LS541

32

mA

V

MAX

ICC

Total Output LOW

LS540

45

mA

VCC = MAX

CC

Total, Output LOW

LS541

52

mA

CC

Total Output 3-State

LS540

52

mA

Total Output 3-State

LS541

55

mA

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.