| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: PI3C16215 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1

PS8409D 03/19/01

Product Description

Pericom Semiconductors PI3C series of logic circuits are produced

using the Companys advanced submicron CMOS technology,

achieving industry leading performance.

The PI3C16215 is a 20-bit bus switch with low ON-State resistance.

The bus switch creates no additional propagation delay. To minimize

live-insertion noise, the device also precharges the B port to a user-

selectable bias voltage (BIASV).

The switch is turned on by a single enable (OE) input. When OE is

LOW, the switch is on and port A is connnected to port B. When

OE is HIGH, the switch between port A and port B is open and

the B port is precharged to BIASV through the equivalent of a

10k-ohm resistor.

BIASV

1

1A1

2

1A2

3

1A3

4

1A4

5

1A5

6

1A6

7

GND

GND

8

1A7

9

1A8

10

1A9

11

1A10

12

2A1

13

2A2

14

VCC

15

2A3

16

2A4

17

2A5

18

2A6

19

2A7

20

2A8

21

2A9

22

2A10

23

24

1OE

2OE

1B1

1B2

1B3

1B4

1B5

GND

1B6

48

1B7

47

1B8

46

1B9

45

1B10

44

2B1

43

2B2

42

2B3

41

GND

40

2B4

39

2B5

38

2B6

37

2B7

36

2B8

35

2B9

34

2B10

33

32

31

30

29

28

27

26

25

Product Pin Configuration

Logic Diagram

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PI3C16215

3.3V, 2-Port, 20-Bit Bus Switch

with Precharged Outputs

for Live Insertion

Product Features

Near zero propagation delay

5-ohm switch connection between two ports

High Bandwidth (>200 MHz)

Rail-to-Rail 3.3V Switching

Outputs are precharged by bias voltage to

minimize signal distortion during live insertion

5V I/O Tolerant

Package options:

48-pin 150 mil wide plastic BQSOP (B)

48-pin 240 mil wide plastic TSSOP (A)

E

O

n

o

it

c

n

u

F

L

tr

o

p

B

=

tr

o

p

A

H

V

S

A

I

B

=

tr

o

p

A

,

Z

=

tr

o

p

A

Truth Table

Note:

1. H= High Voltage Level 2. L= Low Voltage Level

2

B

1

2

B

10

2

OE

1

B

1

1

B

10

BIASV

1

OE

SW

SW

SW

SW

1

A

1

1

A

10

2

12

48

13

24

47

25

35

46

36

1

48-Pin

A,B

2

PS8409D 03/19/01

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

PI3C16215

3.3V, 2-Port, 20-Bit Bus Switch with

Precharged Outputs for Live Insertion

Electrical Characteristics

(Over Recommended Operating Free-Air Temperature Range)

Storage Temperature...................................... 65∞C to +150∞C

Supply Voltage Range .......................................... 0.5V to 4.6V

DC Input Voltage

(1)

............................................ 0.5V to +5.5V

Input Clamp Current, I

IK

(V

1

< 0) .....................................50mA

DC Output Current .......................................................... 120mA

Power Dissipation

(2)

..........................................................0.5W

Note:

Stresses greater than those listed under MAXIMUM

RATINGS may cause permanent damage to the device. This

is a stress rating only and functional operation of the device

at these or any other conditions above those indicated in

the operational sections of this specification is not implied.

Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

Recommended Operating Conditions

Notes:

1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2. The maximum package power dissipation is calculated using a junction temperatue of 150∞C and a board trace length of 750 mils.

Absolute Maximum Ratings Over Free-Air Temperature Range

*

(Above which the useful life may be impaired. For user guidelines, not tested.)

Notes:

* Measured by the voltage drop between the A and B terminals at the indicated current through the switch.

On-state resistance is determined by the lower of the voltages of the two (A or B) terminals.

This is the increase in supply current for control input.

All typical values are at V

CC

= 3.3V, T

A

= 25∞C.

s

r

e

t

e

m

a

r

a

P

n

o

it

p

i

r

c

s

e

D

s

n

o

it

i

d

n

o

C

t

s

e

T

.

n

i

M

p

y

T .

.

x

a

M

s

ti

n

U

V

K

I

e

g

a

tl

o

V

e

d

o

i

D

p

m

al

C

V

C

C

I

,

V

0

.

3

=

N

I

8

1

=

mA

3

7

.

0

2

.

1

V

I

I

t

n

e

rr

u

C

t

u

p

n

I

V

C

C

,

V

6

.

3

=

V

N

I

V

=

C

C

D

N

G

r

o

5

±

µ

A

I

O

t

n

e

rr

u

C

t

u

p

t

u

O

V

C

C

V

,

V

4

.

2

=

V

S

A

I

B

,

V

0

.

3

=

O

0

=

5

2

.

0

A

m

I

C

C

t

n

e

rr

u

C

y

l

p

p

u

S

r

e

w

o

P

t

n

e

c

s

ei

u

Q

V

C

C

I

,

V

6

.

3

=

O

,

0

=

V

N

I

V

=

C

C

D

N

G

r

o

0

6

2

0

5

8

µ

A

I

C

C

t

u

p

n

I

r

e

p

t

n

e

rr

u

C

y

l

p

p

u

S

r

e

w

o

P

V

C

C

,

V

6

.

3

=

V

7

.

2

t

a

t

u

p

n

i

e

n

O

t

a

r

e

h

t

O

V

C

C

D

N

G

r

o

5

.

2

A

m

C

N

I

e

c

n

a

ti

c

a

p

a

C

t

u

p

n

I

V

C

C

V

0

=

5

.

3

F

p

C

F

F

O

e

c

n

a

ti

c

a

p

a

C

B

/

A

V

C

C

,

V

0

=

ff

O

h

c

ti

w

S

0

.

5

R

N

O

*

e

c

n

a

t

si

s

e

R

n

o

h

c

ti

w

S

V

C

C

V

0

.

3

=

V

N

I

I

,

0

=

N

I

4

6

=

A

m

5

5

.

8

V

N

I

I

,

V

4

.

2

=

N

I

0

3

=

A

m

0

.

8

5

1

V

N

I

I

,

V

4

.

2

=

N

I

5

1

=

A

m

0

.

8

5

1

.

n

i

M

.

x

a

M

s

ti

n

U

V

C

C

e

g

a

tl

o

v

y

l

p

p

u

S

0

.

3

3

.

3

V

V

S

A

I

B

e

g

a

tl

o

v

y

l

p

p

u

S

3

.

1

V

C

C

V

H

I

e

g

a

tl

o

v

t

u

p

n

i

l

e

v

el

-

h

g

i

H

2

V

L

I

e

g

a

tl

o

v

t

u

p

n

i

l

e

v

el

-

w

o

L

8

.

0

T

A

e

r

u

t

a

r

e

p

m

e

t

ri

a

-

e

e

rf

g

n

it

a

r

e

p

O

0

4

5

8

C

∞

3

PS8409D 03/19/01

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

PI3C16215

3.3V, 2-Port, 20-Bit Bus Switch with

Precharged Outputs for Live Insertion

Switching Characteristics

(Over Recommended Operating Free-air Temperature Range, C

L

= 50pF)

Note:

1. This parameter is warranted but not production tested. The propagation delay is based on the RC time constant of the typical on

state resistance of the switch and a load capacitance of 50pF, when driven by an ideal voltage source (zero output impedance).

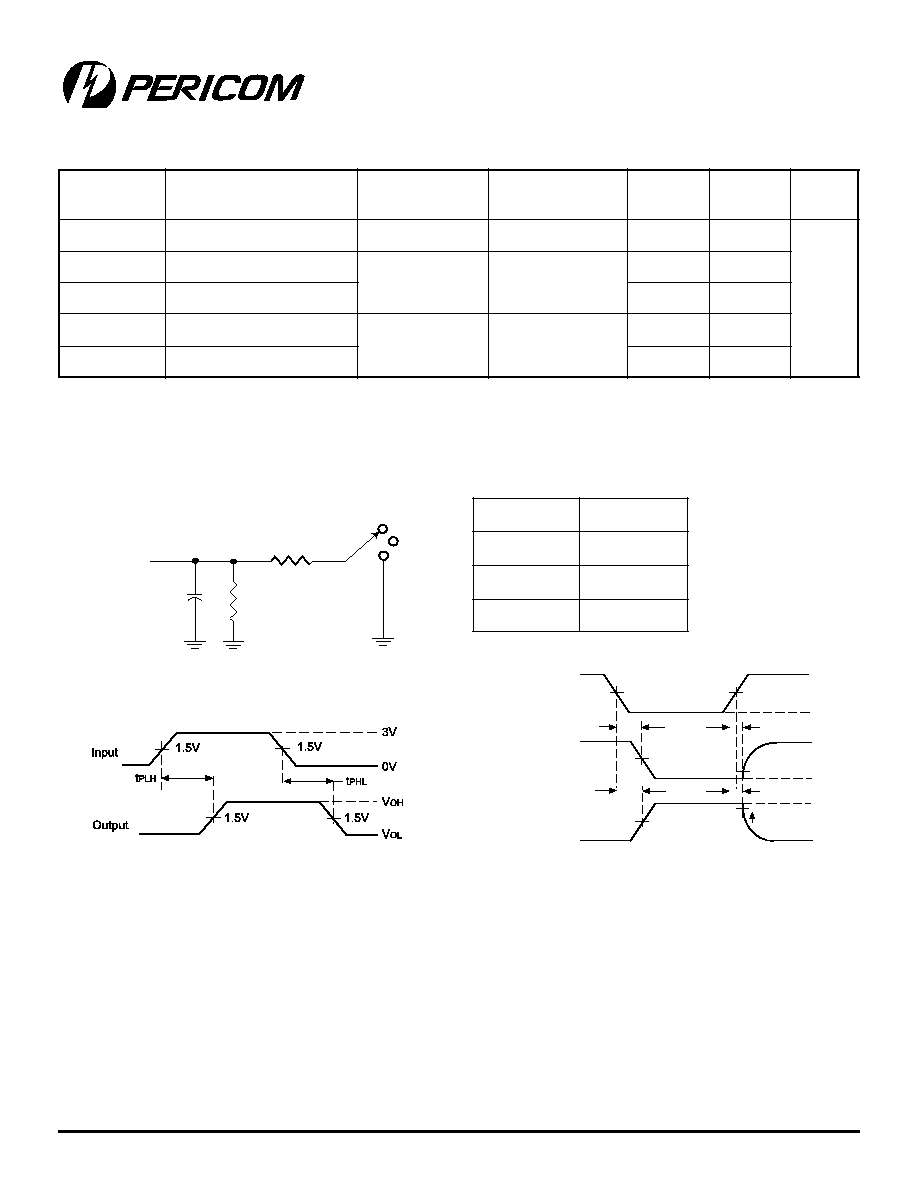

Parameter Measurements

VOLTAGE WAVEFORMS

PROPAGATION DELAY TIMES

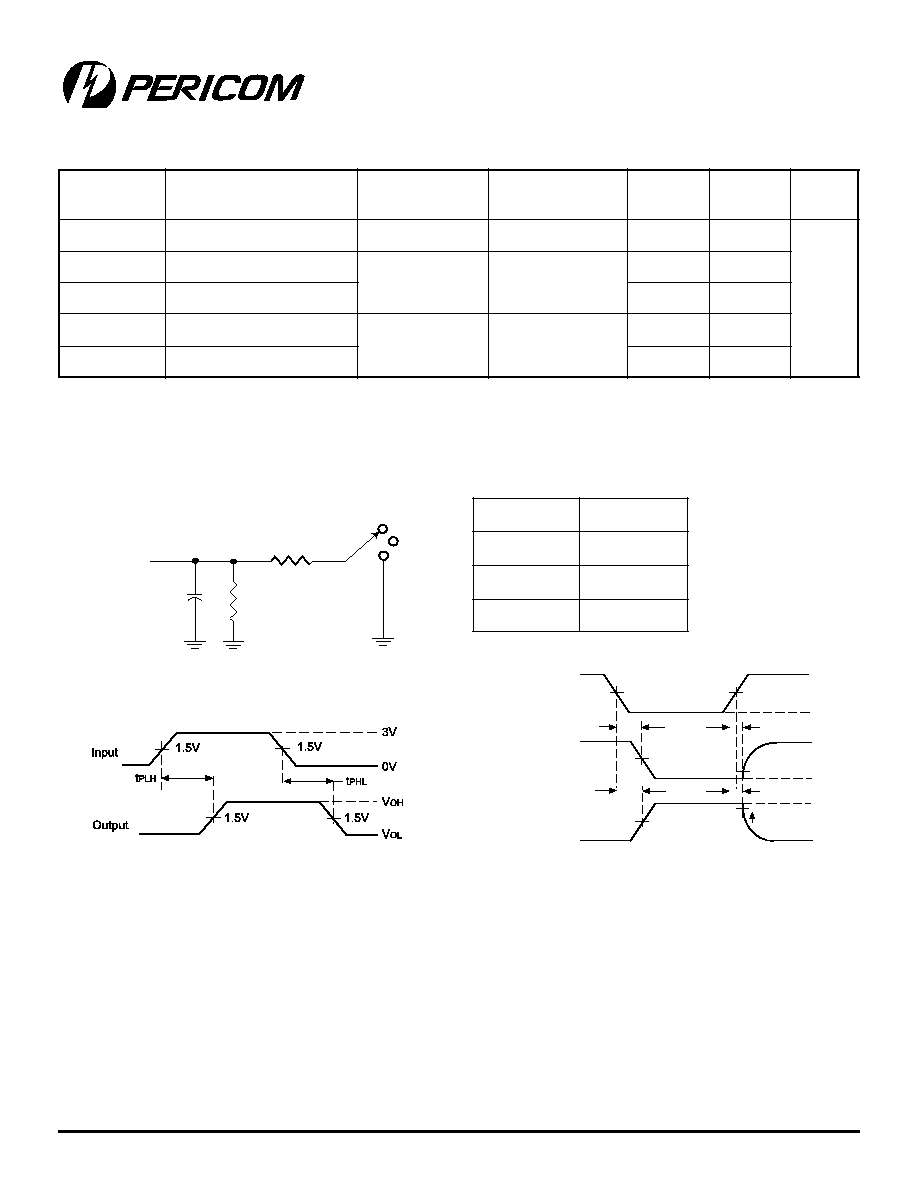

VOLTAGE WAVEFORMS

ENABLE AND DISABLE TIMES

t

s

e

T

1

S

t

D

P

n

e

p

O

t

Z

L

P

t/

L

Z

P

V

6

t

Z

H

P

t/

H

Z

P

D

N

G

Notes:

1. C

L

includes probe and jig capacitance.

2. Waveform 1 is for an output with internal conditions such that the output is LOW except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is HIGH except when disabled by the output control.

3. All input pulses are supplied by generators having the following characteristics: PRR<10MHz, Z

O

= 50

, t

R

2.5ns, t

F

2.5ns.

4. The outputs are measured one at a time with one transition per measurement.

5. t

PLZ

and t

PHZ

are the same as t

DIS

.

6. t

PZL

and t

PZH

are the same as t

EN

.

7. t

PLH

and t

PHL

are the same as t

PD

.

t

PZL

Output

Control

(Low Level

Enabling)

0V

1.5V

1.5V

1.5V

1.5V

t

PLZ

t

PHZ

V

OL

3.5V

0V

t

PZH

+0.3V

-0.3V

Output

Waveform 1

S1 at 6V

(see Note 2)

Output

Waveform 2

S1 at Open

(see Note 2)

V

OH

V

OH

V

OL

3V

r

e

t

e

m

a

r

a

P

s

n

o

it

i

d

n

o

C

t

s

e

T

)t

u

p

n

I

(

m

o

r

F

)t

u

p

t

u

O

(

o

T

.

n

i

M

.

x

a

M

s

ti

n

U

t

D

P

)

1

(

B

r

o

A

A

r

o

B

5

2

.

0

s

n

t

H

Z

P

D

N

G

=

V

S

A

I

B

N

O

B

r

o

A

5

.

1

5

.

6

t

L

Z

P

V

3

=

V

S

A

I

B

5

.

1

5

.

6

t

Z

H

P

D

N

G

=

V

S

A

I

B

N

O

B

r

o

A

5

.

1

5

.

5

t

Z

L

P

V

3

=

V

S

A

I

B

5

.

1

5

.

5

#Ohm

#Ohm

6V

Open

GND

S1

LOAD CIRCUIT

From Output

Under Test

CL = 50pF

(See note 1)

4

PS8409D 03/19/01

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

PI3C16215

3.3V, 2-Port, 20-Bit Bus Switch with

Precharged Outputs for Live Insertion

Ordering Information

t

r

a

P

e

g

a

k

c

a

P

-

n

i

P

h

t

d

i

W

e

r

u

t

a

r

e

p

m

e

T

A

5

1

2

6

1

C

3

I

P

)

8

4

A

(

P

O

S

S

T

-

8

4

li

m

-

0

4

2

C

∫

5

8

+

o

t

C

∫

0

4

B

5

1

2

6

1

C

3

I

P

)

8

4

B

(

P

O

S

Q

B

-

8

4

li

m

-

0

4

2

Pericom Semiconductor Corporation

2380 Bering Drive ∑ San Jose, CA 95131 ∑ 1-800-435-2336 ∑ Fax (408) 435-1100 ∑ http://www.pericom.com

48-Pin TSSOP (A) Package

48-Pin BQSOP (B) Package

.236

.244

.488

.496

.002

.006

SEATING PLANE

.007

.010

.0197

BSC

.004

.008

.319

1

48

12.4

12.6

6.0

6.2

0.50

0.17

0.27

8.1

0.05

0.15

0.09

0.20

X.XX

X.XX

DENOTES DIMENSIONS

IN MILLIMETERS

.018

.030

0.45

0.75

.047

1.20 Max

BSC

.014

.0157 BSC

0.40

0.356

.008 0.20

.002

.009

5

∞

0.05

0.25

.079

2.0

.010 0.25

Gauge Plane

.150

.157

X.XX

X.XX

DENOTES DIMENSIONS

IN MILLIMETERS

3.80

4.00

.228

.244

5.80

6.20

.020

.029

0.50

0.75

.063

1.60

.015 0.381

.386

.394

9.80

10.00

.0051

.009

0.13

0.23

1

48

x 45

∞

BSC

Nom

Max

Nom

REF

Applications Information

Logic Inputs

The logic control inputs can be driven up to +3.6V regardless of the

supply voltage. For example, given a +3.3V supply, IN may be driven

low to 0V and high to 3.6V. Driving IN Rail-to-RailÆ minimizes power

consumption.

Power-Supply Sequencing

Proper power-supply sequencing is recommended for all CMOS

devices. Always apply V

CC

before applying V

BIAS

and signals to

input/output or control pins.

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd