1

PS2020A 03/11/96

PI74FCT543T/544T

(25

Series) PI74FCT2543T

LATCHED TRANSCEIVERS

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Product Description:

Pericom Semiconductor's PI74FCT series of logic circuits are

produced in the Company's advanced 0.8 micron CMOS

technology, achieving industry leading speed grades. All

PI74FCT2XXX devices have a built-in 25 ohm series resistor on

all outputs to reduce noise because of reflections, thus eliminating

the need for an external terminating resistor.

The PI74FCT543T/544T and PI74FCT2543T is an 8-bit wide

non-inverting transceiver designed with two sets of eight D-type

latches with separate input and output controls for each set. For

data flow from A to B, for example, the A-to-B Enable (CEAB)

input must be LOW in order to enter data from A0≠A7 or to take

data from B0≠B7, as indicated in the Truth Table. With CEAB

LOW, a LOW signal makes the A-to-B latches transparent; a

subsequent LOW-to-HIGH transition of the LEAB signal puts the

A latches in the storage mode and their outputs no longer change

the A inputs. With CEAB and OEAB both LOW, the 3-state B

output buffers are active and reflect the data present at the output

of the A latches. Control of data from B to A is similar, but uses the

CEAB, LEAB, and OEAB inputs. The PI74FCT543T is a non-

inverting of the PI74FCT544T.

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

NOTE: PI74FCT543/2543T function is shown.

PI74FCT543/544/2543T Logic Block Diagram

Product Features:

∑ PI74FCT543T/544/2543T is pin compatible with bipolar

FASTTM Series at a higher speed and lower power

consumption

∑ 25

series resistor on all outputs

∑ TTL input and output levels

∑ Low ground bounce outputs

∑ Extremely low static power

∑ Hysteresis on all inputs

∑ Industrial operating temperature range: ≠40∞C to +85∞C

∑ Packages available:

≠ 24-pin 300 mil wide plastic DIP (P)

≠ 24-pin 150 mil wide plastic QSOP (Q)

≠ 24-pin 150 mil wide plastic TQSOP (R)

≠ 24-pin 300 mil wide plastic SOIC (S)

∑ Device models available on request

PI74FCT543T/544T

(25

Series) PI74FCT2543T

Fast CMOS

Latched Transceivers

B

0

A

0

D

LE

Q

D

LE

Q

OEAB

CEAB

LEAB

B

1

B

2

B

3

B

4

B

5

B

6

B

7

OEBA

CEBA

LEBA

A

1

A

2

A

3

A

4

A

5

A

6

A

7

DETAIL A x 7

DETAIL A

2

PI74FCT543T/544T

(25

Series) PI74FCT2543T

LATCHED TRANSCEIVERS

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PS2020A 03/11/96

Pin Name

Description

OEAB

A-to-B Output Enable Input (Active LOW)

OEBA

B-to-A Output Enable Input (Active LOW)

CEAB

A-to-B Enable Input (Active LOW)

CEBA

B-to-A Enable Input (Active LOW)

LEAB

A-to-B Latch Enable Input (Active LOW)

LEBA

B-to-A Latch Enable Input (Active LOW)

A

0

-A

7

A-to-B Data Inputs or B-to-A 3-State Outputs

B

0

-B

7

B-to-A Data Inputs or A-to-B 3-State Outputs

GND

Ground

V

CC

Power

Product Pin Description

PI74FCT543/544/2543T Product Pin Configuration

Latch

Output

Inputs

Status

Buffers

CEAB

LEAB

OEAB

A-to-B

B

0

≠B

7

H

--

--

Storing

High-Z

--

H

--

Storing

--

--

--

H

--

High Z

L

L

L

Transparent

Current A Inputs

L

H

L

Storing

Previous* A Inputs

PI74FCT543/2543T Truth Table (Non-Inverting)

(1,2)

For A-to-B (Symmetric with B-to-A)

1.

*Before LEAB LOW-to-HIGH Transition

H = HIGH Voltage Level

L = LOW Voltage Level

-- = Don't Care or Irrevelant

2.

A-to-B data flow shown; B-to-A flow control is the same,

except using CEBA, LEBA, and OEBA.

24-PIN

P24

Q24

R24

S24

3

PS2020A 03/11/96

PI74FCT543T/544T

(25

Series) PI74FCT2543T

LATCHED TRANSCEIVERS

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

Maximum Ratings

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature ................................................................. ≠65∞C to +150∞C

Ambient Temperature with Power Applied ................................. -40∞C to +85∞C

Supply Voltage to Ground Potential (Inputs & Vcc Only) .......... ≠0.5V to +7.0V

Supply Voltage to Ground Potential (Outputs & D/O Only) ....... ≠0.5V to +7.0V

DC Input Voltage ......................................................................... ≠0.5V to +7.0V

DC Output Current ................................................................................... 120 mA

Power Dissipation ......................................................................................... 0.5W

Note:

Stresses greater than those listed under

MAXIMUM RATINGS may cause permanent

damage to the device. This is a stress rating

only and functional operation of the device at

these or any other conditions above those

indicated in the operational sections of this

specification is not implied. Exposure to

absolute maximum rating conditions for

extended periods may affect reliability.

DC Electrical Characteristics

(Over the Operating Range, T

A

= ≠40∞C to +85∞C, V

CC

= 5.0V ± 5%)

Parameters Description

Test Conditions

(1)

Min. Typ

(2)

Max. Units

V

OH

Output HIGH Voltage

V

CC

= Min., V

IN

= V

IH

or V

IL

I

OH

= ≠15.0 mA

2.4

3.0

V

V

OL

Output LOW Current

V

CC

= Min., V

IN

= V

IH

or V

IL

I

OL

= 64 mA

0.3

0.55

V

V

OL

Output LOW Current

V

CC

= Min., V

IN

= V

IH

or V

IL

I

OL

= 12 mA (25

Series)

0.3

0.50

V

V

IH

Input HIGH Voltage

Guaranteed Logic HIGH Level

2.0

V

V

IL

Input LOW Voltage

Guaranteed Logic LOW Level

0.8

V

I

IH

Input HIGH Current

(Except I/O pins) V

CC

= Max.

V

IN

= V

CC

1

µA

I

IL

Input LOW Current

(Except I/O pins) V

CC

= Max.

V

IN

= GND

≠1

µA

I

IH

Input HIGH Current

(I/O pins Only) V

CC

= Max.

V

IN

= V

CC

1

µA

I

IL

Input LOW Current

(I/O pins Only) V

CC

= Max.

V

IN

= GND

≠1

µA

I

OZH

High Impedance

V

CC

= M

AX

.

V

OUT

= 2.7V

1

µA

I

OZL

Output Current

V

OUT

= 0.5V

≠1

µA

V

IK

Clamp Diode Voltage

V

CC

= Min., I

IN

= ≠18 mA

≠0.7

≠1.2

V

I

OFF

Power Down Disable

V

CC

= GND, V

OUT

= 4.5V

--

--

100

µA

I

OS

Short Circuit Current

V

CC

= Max.

(3)

, V

OUT

= GND

≠60

≠120

mA

V

H

Input Hysteresis

200

mV

Capacitance

(T

A

= 25∞C, f = 1 MHz)

Parameters

(4)

Description

Test Conditions

Typ

Max.

Units

C

IN

Input Capacitance

V

IN

= 0V

6

10

pF

C

OUT

Output Capacitance

V

OUT

= 0V

8

12

pF

Notes:

1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V, +25∞C ambient and maximum loading.

3. Not more than one output should be shorted at one time. Duration of the test should not exceed one second.

4. This parameter is determined by device characterization but is not production tested.

4

PI74FCT543T/544T

(25

Series) PI74FCT2543T

LATCHED TRANSCEIVERS

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PS2020A 03/11/96

Power Supply Characteristics

Parameters Description

Test Conditions

(1)

Min.

Typ

(2)

Max.

Units

I

CC

Quiescent Power

V

CC

= Max.

V

IN

= GND

0.1

500

µA

Supply Current

or V

CC

I

CC

Supply Current per

V

CC

= Max.

V

IN

= 3.4V

(3)

0.5

2.0

mA

Input @ TTL HIGH

I

CCD

Supply Current per

V

CC

= Max.,

V

IN

= V

CC

0.15

0.25

mA/

Input per MHz

(4)

Outputs Open

V

IN

= GND

MHz

CEAB and OEAB = GND

CEBA = VCC

One Input Toggling

50% Duty Cycle

I

C

Total Power Supply

V

CC

= Max.,

V

IN

= V

CC

1.5

3.5

(5)

mA

Current

(6)

Outputs Open

V

IN

= GND

f

CP

= 10 MH

Z

(LEAB)

50% Duty Cycle

V

IN

= 3.4V

2.0

5.5

(5)

CEAB and OEAB = GND

V

IN

= GND

CEBA = V

CC

f

I

= 5 MH

Z

One Bit Toggling

V

CC

= Max.,

V

IN

= V

CC

3.8

7.3

(5)

Outputs Open

V

IN

= GND

f

CP

= 10 MH

Z

(LEAB)

50% Duty Cycle

V

IN

= 3.4V

6.0

16.3

(5)

CEAB and OEAB = GND

V

IN

= GND

CEBA = Vcc

Eight Bits Toggling

f

I

= 2.5 MH

Z

50% Duty Cycle

Notes:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device.

2. Typical values are at Vcc = 5.0V, +25∞C ambient.

3. Per TTL driven input (V

IN

= 3.4V); all other inputs at Vcc or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

5. Values for these conditions are examples of the Icc formula. These limits are guaranteed but not tested.

6. I

C

=I

QUIESCENT

+ I

INPUTS

+ I

DYNAMIC

I

C

= I

CC

+

I

CC

D

H

N

T

+ I

CCD

(f

CP

/2 + f

I

N

I

)

I

CC

= Quiescent Current

I

CC

= Power Supply Current for a TTL High Input (V

IN

= 3.4V)

D

H

= Duty Cycle for TTL Inputs High

N

T

= Number of TTL Inputs at D

H

I

CCD

= Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

f

CP

= Clock Frequency for Register Devices (Zero for Non-Register Devices)

f

I

= Input Frequency

N

I

= Number of Inputs at f

I

All currents are in milliamps and all frequencies are in megahertz.

5

PS2020A 03/11/96

PI74FCT543T/544T

(25

Series) PI74FCT2543T

LATCHED TRANSCEIVERS

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

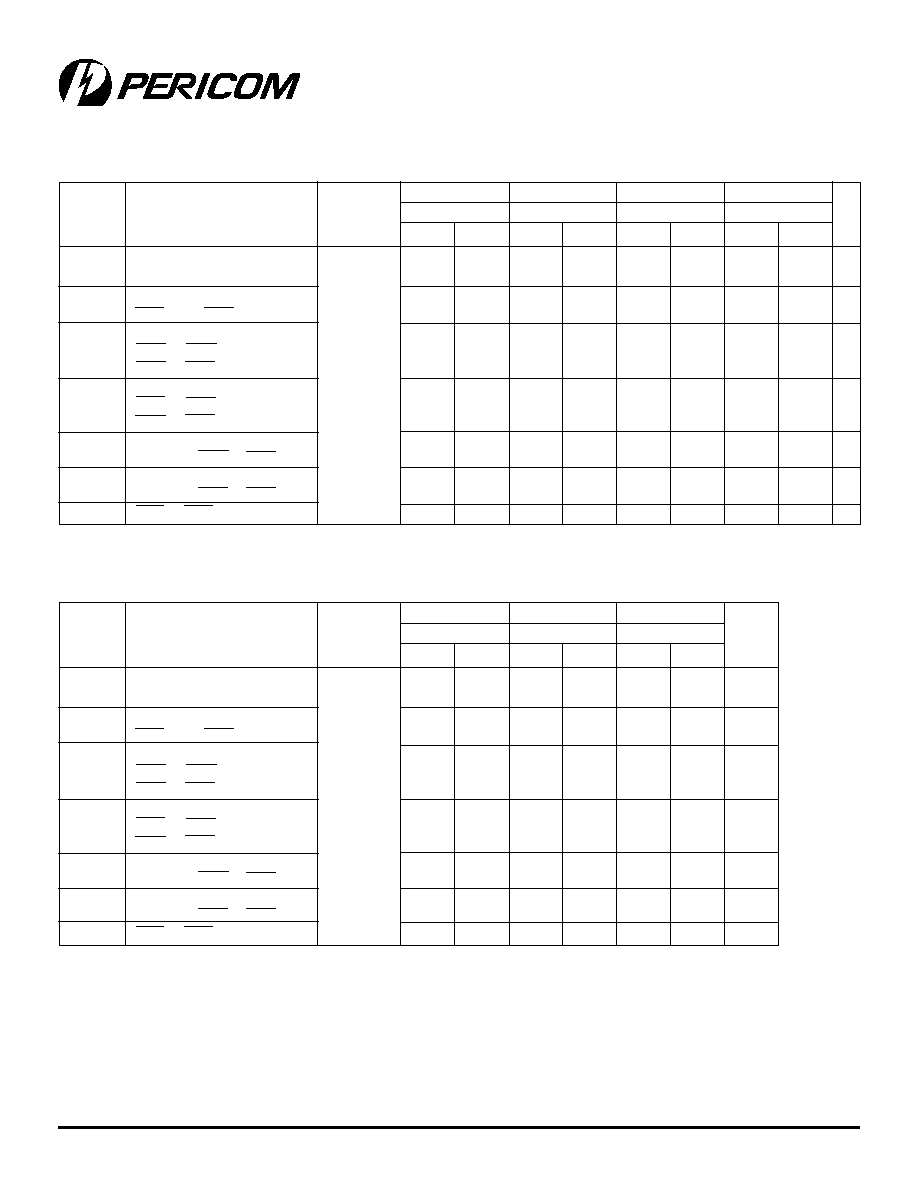

543T/2543T

543AT/2543AT

543CT/2543CT

543DT

Com.

Com.

Com.

Com.

Parameters Description

Conditions

(1)

Min

Max

Min

Max

Min

Max

Min

Max

Unit

t

PLH

Propagation Delay Transparent

C

L

= 50 pF

2.5

8.5

2.5

6.5

2.5

5.3

2.5

4.4

ns

t

PHL

Mode A

N

to B

N

or B

N

to A

N

R

L

= 500

t

PLH

Propagation Delay

2.5

12.5

2.5

8.0

2.5

7.0

2.5

5.0

ns

t

PHL

LEBA to A

N

, LEAB to B

N

t

PZH

Output Enable Time

2.0

12.0

2.0

9.0

2.0

8.0

2.0

5.4

ns

t

PZL

OEBA or OEAB to A

N

or B

N

CEBA or CEAB to A

N

or B

N

t

PZH

Output Disable Time

(3)

2.0

9.0

2.0

7.5

2.0

6.5

2.0

4.3

ns

t

PZL

OEBA or OEAB to A

N

or B

N

CEBA or CEAB to A

N

or B

N

t

SU

Setup Time, HIGH or LOW

3.0

--

2.0

--

2.0

--

1.5

--

ns

A

N

or B

N

to LEBA or LEAB

t

H

Hold Time, HIGH or LOW

2.0

--

2.0

--

2.0

--

1.5

--

ns

A

N

or B

N

to LEBA or LEAB

t

W

LEBA or LEAB Pulse Width LOW

(3)

5.0

--

5.0

--

5.0

--

3.0

--

ns

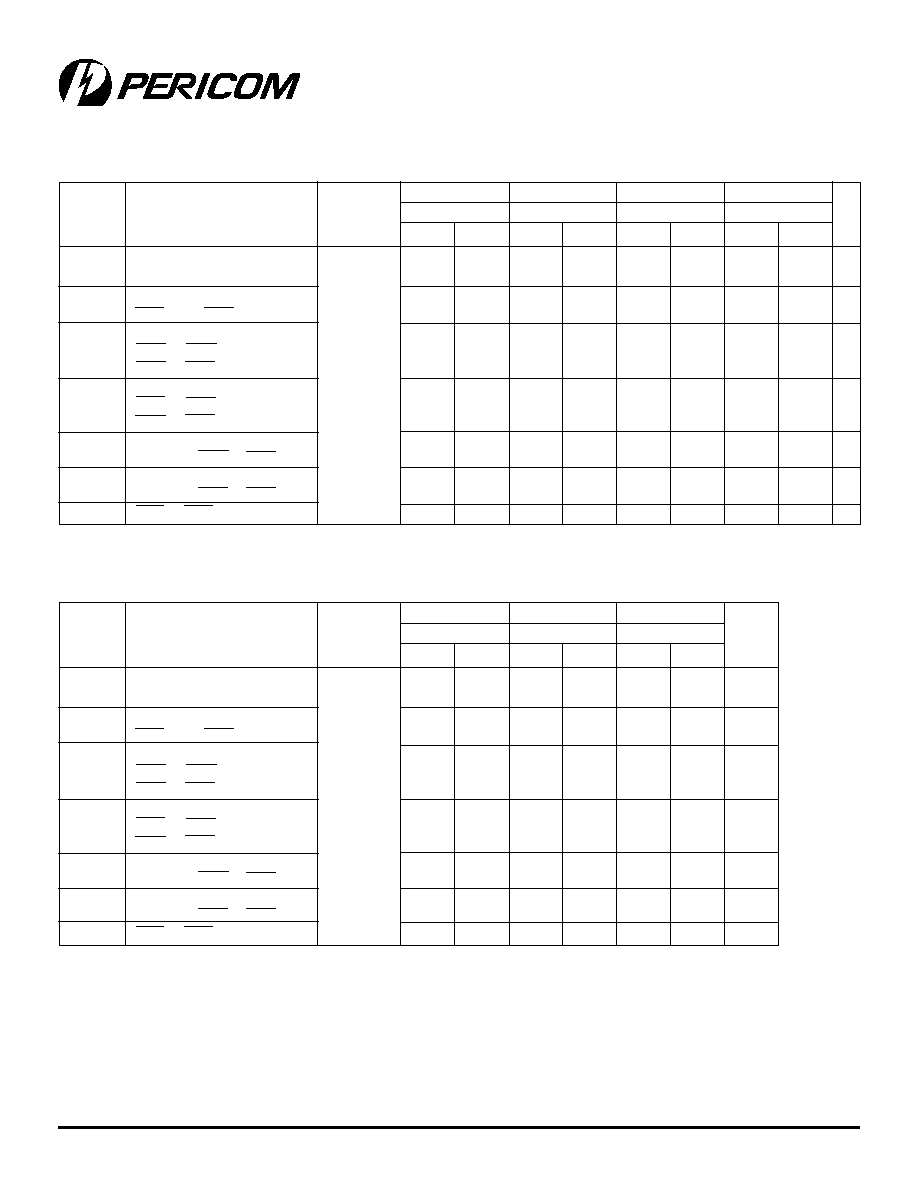

544T

544AT

544CT

Com.

Com.

Com.

Parameters Description

Conditions

(1)

Min

Max

Min

Max

Min

Max

Unit

t

PLH

Propagation Delay Transparent

C

L

= 50 pF

2.5

8.5

2.5

6.5

2.5

5.3

ns

t

PHL

Mode A

N

to B

N

or B

N

to A

N

R

L

= 500

t

PLH

Propagation Delay

2.5

12.5

2.5

8.0

2.5

7.0

ns

t

PHL

LEBA to A

N

, LEAB to B

N

t

PZH

Output Enable Time

2.0

12.0

2.0

9.0

2.0

8.0

ns

t

PZL

OEBA or OEAB to A

N

or B

N

CEBA or CEAB to A

N

or B

N

t

PZH

Output Disable Time

(3)

2.0

9.0

2.0

7.5

2.0

6.5

ns

t

PZL

OEBA or OEAB to A

N

or B

N

CEBA or CEAB to A

N

or B

N

t

SU

Setup Time, HIGH or LOW

3.0

--

2.0

--

2.0

--

ns

A

N

or B

N

to LEBA or LEAB

t

H

Hold Time, HIGH or LOW

2.0

--

2.0

--

2.0

--

ns

A

N

or B

N

to LEBA or LEAB

t

W

LEBA or LEAB Pulse Width LOW

(3)

5.0

--

5.0

--

5.0

--

ns

Notes:

1. See test circuit and wave forms.

2. Minimum limits are guaranteed but not tested on Propagation Delays.

3. This parameter is guaranteed but not production tested.

PI74FCT543/2543T (non-inverting) Switching Characteristics over Operating Range

PI74FCT544T (inverting) Switching Characteristics over Operating Range

Pericom Semiconductor Corporation

2380 Bering Drive ∑ San Jose, CA 95131 ∑ 1-800-435-2336 ∑ Fax (408) 435-1100 ∑ http://www.pericom.com