DATA SHEET

Product specification

Supersedes data of 1997 Dec 15

File under Integrated Circuits, IC20

1998 Apr 07

INTEGRATED CIRCUITS

P89C738; P89C739

8-bit Flash microcontrollers

1998 Apr 07

2

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

CONTENTS

1

FEATURES

2

GENERAL DESCRIPTION

3

ORDERING INFORMATION

4

BLOCK DIAGRAM

5

FUNCTIONAL DIAGRAM

6

PINNING INFORMATION

6.1

Pin configuration

6.2

Pin description

7

FUNCTIONAL DESCRIPTION

7.1

General

7.2

Instruction set execution

8

MEMORY ORGANIZATION

8.1

Program memory

8.2

Internal data memory

8.3

Addressing

9

INTERRUPT SYSTEM

9.1

Interrupt Enable Register (IE)

9.2

Interrupt Priority Register (IP)

10

TIMERS/COUNTERS

10.1

Timer 0 and Timer 1

10.2

Timer 2

10.3

Watchdog Timer (T3)

11

I/O FACILITIES

12

FULL DUPLEX SERIAL PORT (UART)

12.1

The Serial Port operating modes

12.2

Serial Port Control Register (SCON)

13

REDUCED POWER MODES

13.1

Idle mode

13.2

Power-down mode

13.3

Wake-up from Power-down mode

13.4

Status of external pins

13.5

Power Control Register (PCON)

14

OSCILLATOR CIRCUIT

15

RESET

15.1

Power-on reset

16

MULTIPLE PROGRAMMING ROM

(MTP-ROM)

16.1

Features

16.2

General description

16.3

Automatic programming and Automatic chip

erase

16.4

Command definitions

16.5

Silicon-ID-Read command

16.6

Set-up of Automatic chip erase and Automatic

erase commands

16.7

Set-up of the Automatic program and Program

commands

16.8

Reset command

16.9

Write operation status

16.10

Write operation

16.11

System considerations

16.12

Command programming/data programming

and erase operation

17

SPECIAL FUNCTION REGISTERS

OVERVIEW

18

INSTRUCTION SET

19

LIMITING VALUES

20

DC CHARACTERISTICS

21

AC CHARACTERISTICS

21.1

Serial Port characteristics

21.2

Timing waveforms

21.3

Timing symbol naming conventions

22

PACKAGE OUTLINES

23

SOLDERING

23.1

Introduction

23.2

DIP

23.3

PLCC and QFP

24

DEFINITIONS

25

LIFE SUPPORT APPLICATIONS

1998 Apr 07

3

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

1

FEATURES

∑

80C51 CPU

∑

64-kbyte on-chip Multiple Programming ROM

(MTP-ROM), expandable externally to 64 kbytes

program memory address space

∑

512-byte on-chip RAM, expandable externally to

64 kbytes data memory address space

∑

P89C738 pin outs fully compatible to the standard

8051/8052

∑

8-bit I/O ports for P89C738: 4 and P89C739: 6

∑

Full-duplex UART compatible with the standard 80C51

and the 8052

∑

Two standard 16-bit timers/event counters

∑

An additional 16-bit timer (functionally equivalent to the

Timer 2 of the 8052)

∑

On-chip Watchdog Timer (T3)

∑

6-source and 6-vector interrupt structure with 2 priority

levels

∑

Up to 3 external interrupt request inputs

∑

Two programmable power reduction modes: Idle and

Power-down

∑

Termination of Idle mode by any interrupt, external or

Watchdog Timer reset

∑

Wake-up from Power-down by external interrupt,

external or Watchdog Timer reset

∑

Packages,

≠ P89C738: DIP40, PLCC44 and QFP44

≠ P89C739: PLCC68 and QFP64

∑

Improved Electromagnetic Compatibility (EMC)

∑

Frequency range: 3.5 to 40 MHz

∑

ROM code protection.

2

GENERAL DESCRIPTION

The P89C738 and P89C739 (hereafter generally referred

to as P89C738 unless the P89C739 is specifically

mentioned) are 8 8-bit Flash microcontrollers

manufactured in an advanced CMOS process and is a

derivative of the PCB80C51 microcontroller family. This

device provides architectural enhancements that make it

applicable in a variety of applications in general control

systems, especially in those systems which need a large

on-chip ROM and RAM capacity.

The P89C738 contains a non-volatile 64-kbyte Multiple

Programming ROM (MTP-ROM) program memory, a

volatile 512 bytes read/write data memory, four 8-bit I/O

ports (six for the P89C739), two 16-bit timer/event

counters (identical to the timers of the 80C51), a 16-bit

timer (identical to the Timer 2 of the 8052), a multi-source

two-priority-level nested interrupt structure, one serial

interface (UART), a Watchdog Timer (T3), an on-chip

oscillator and timing circuits. For systems that require

extra capability, the P89C738 can be expanded using

standard TTL compatible memories and logic.

The device also functions as an arithmetic processor

having facilities for both binary and BCD arithmetic plus

bit-handling capabilities. The P89C738 has the same

instruction set as the PCB80C51 which consists of over

100 instructions: 49 one-byte, 46 two-byte and

16 three-byte. With a 16 MHz crystal, 58% of the

instructions are executed in 750 ns and 40% in 1.5

µ

s.

Multiply and divide instructions require 3

µ

s.

3

ORDERING INFORMATION

Notes

1. Temperature and frequency range for all types: 0 to 70

∞

C and 3.5 to 40 MHz.

2. For more information on the package outline of this version, please contact the Philips Semiconductors Sales office.

TYPE

NUMBER

(1)

PACKAGE

NAME

DESCRIPTION

VERSION

P89C738ABA

PLCC44

plastic leaded chip carrier; 44 leads

note 2

P89C738ABP

DIP40

plastic dual in-line package; 40 leads (600 mil)

SOT129-1

P89C738ABB

QFP44

plastic quad flat package; 44 leads

note 2

P89C739ABA

PLCC68

plastic leaded chip carrier; 68 leads

note 2

P89C739ABB

QFP64

plastic quad flat package; 64 leads (lead length 1.95 mm);

body 14

◊

20

◊

2.7 mm; high stand-off height

SOT319-1

1998

Apr

07

4

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

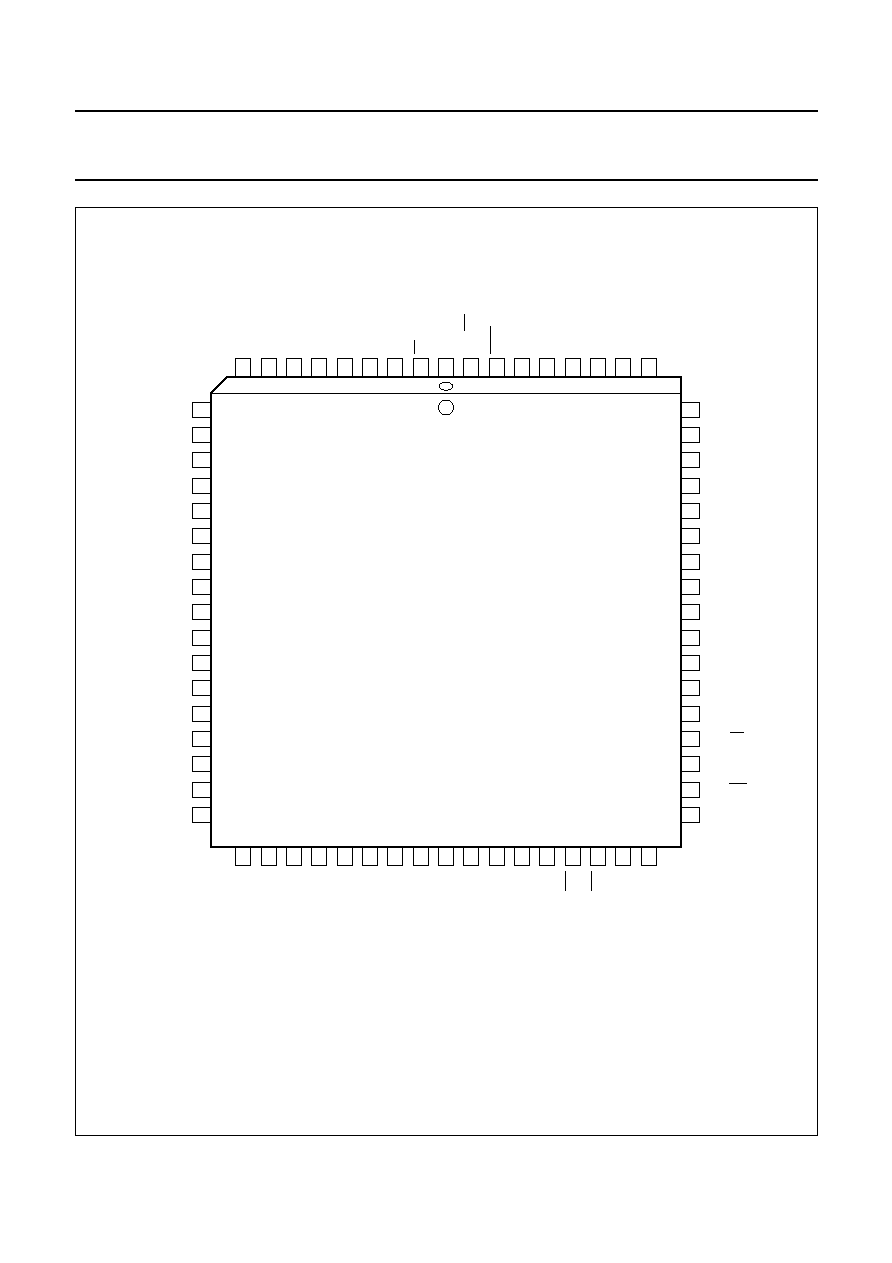

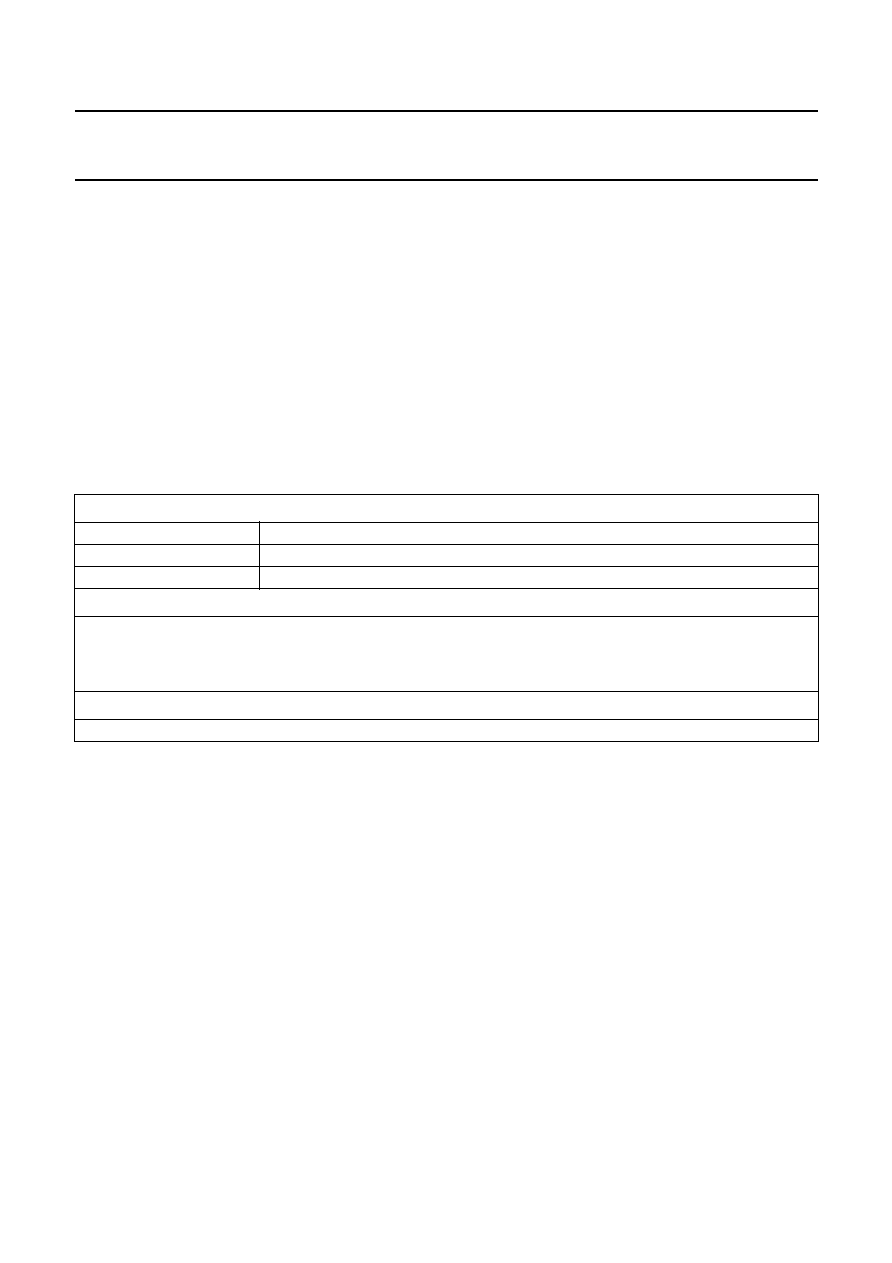

4

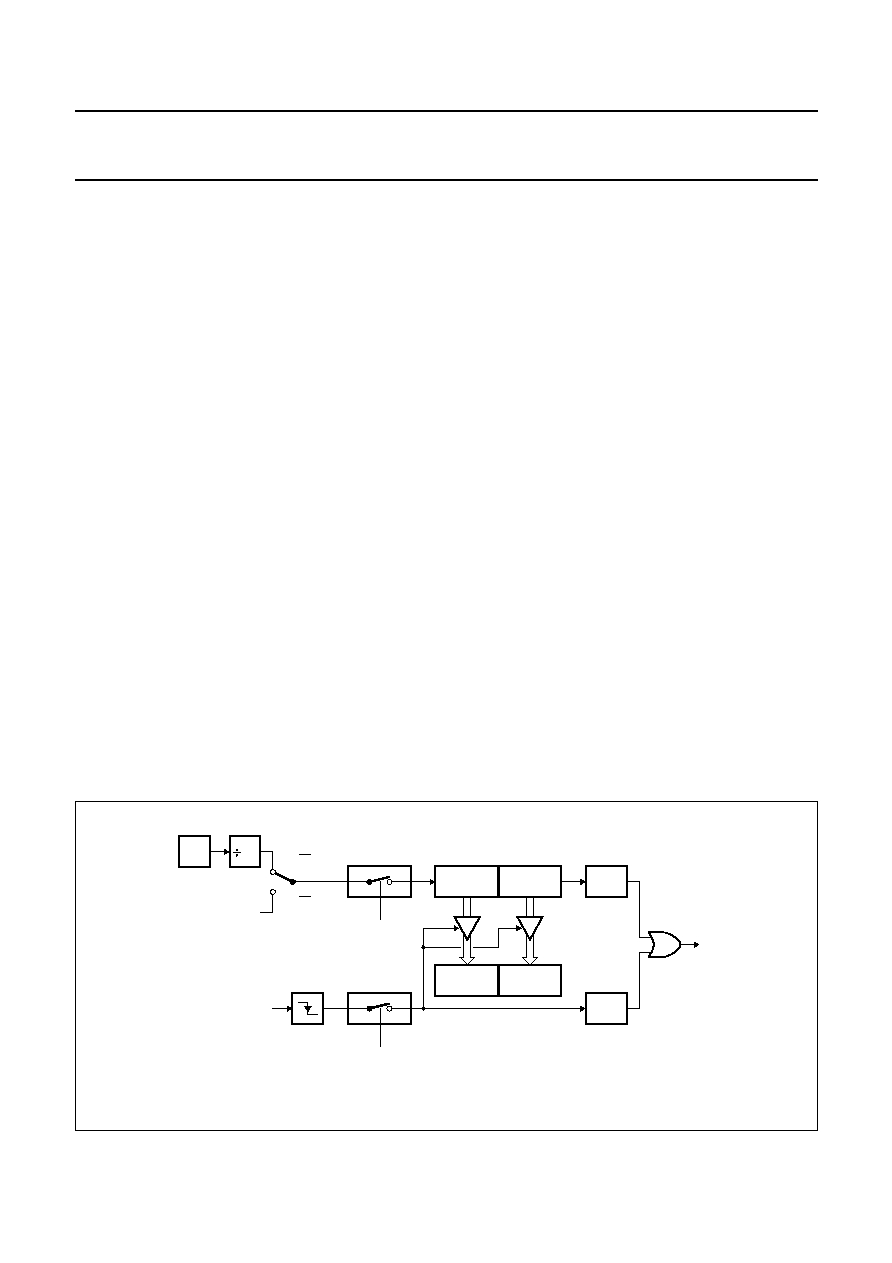

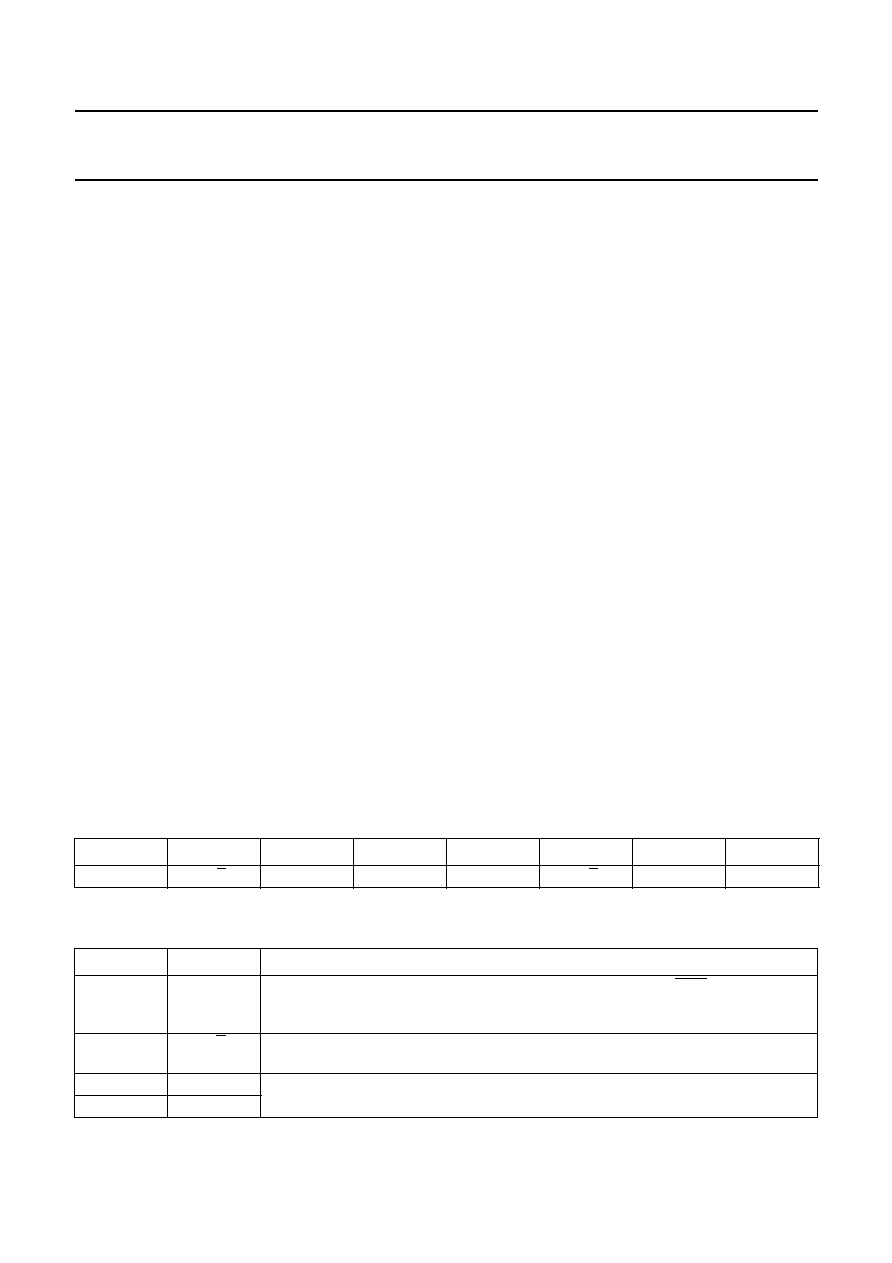

BLOCK DIAGRAM

d

book, full pagewidth

MGK189

XTAL2

XTAL1

P3

P2

P1

P0

PARALLEL I/O PORTS

AND

EXTERNAL BUS

WATCHDOG

TIMER

(T3)

TWO 16-BIT

TIMERS/

EVENT

COUNTERS

(T0, T1)

80C51 core

excluding

ROM/RAM

CPU

PROGRAM

MEMORY

64-kbyte

MTP-ROM

16-BIT

TIMER/

EVENT

COUNTER

(T2)

16 kbytes BUS

EXPANSION CONTROL

DATA

MEMORY

256-byte

RAM

DATA

MEMORY

256-byte

AUX-RAM

PROGRAMMABLE

SERIAL PORT

FULL DUPLEX

UART

SYNCHRONOUS

SHIFT

8-bit

internal bus

internal

reset

P89C738

P89C739

8

8

8

8

8

8

P5

(3)

P4

(3)

RST

VDD

VSS

RXD

(2)

TXD

(2)

INT1

(2)

internal

interrupts

INT0

(2)

T1

(2)

T0

(2)

PSEN

EA

ALE/WE

WR

(2)

T2EX

(1)

T2

(1)

RD

(2)

Fig.1 Block diagram.

(1) Alternative function for Port 1.

(2) Alternative function for Port 3.

(3) P4 and P5 are only available on the P89C738ABA and P89C739ABB (PLCC68 and QFP64).

1998 Apr 07

5

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

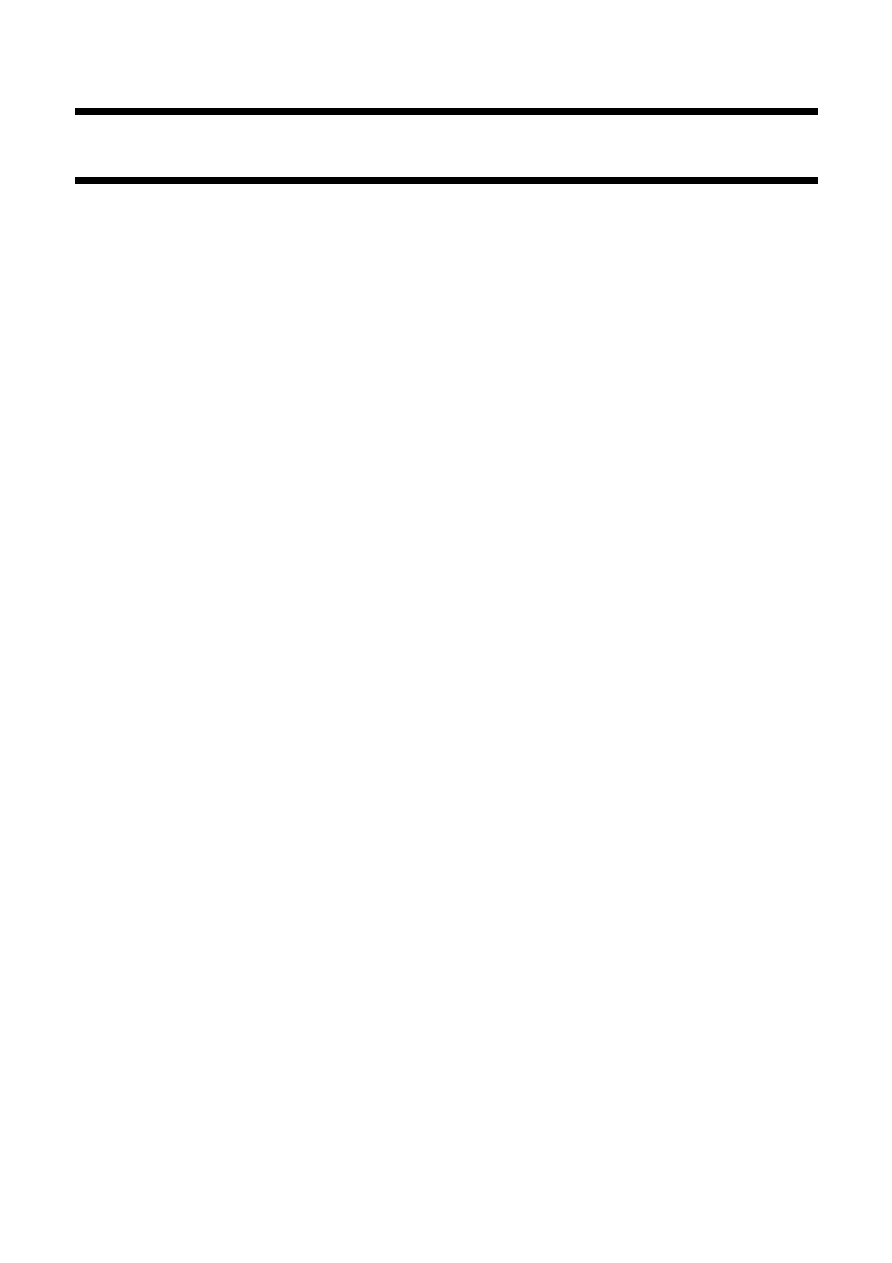

5

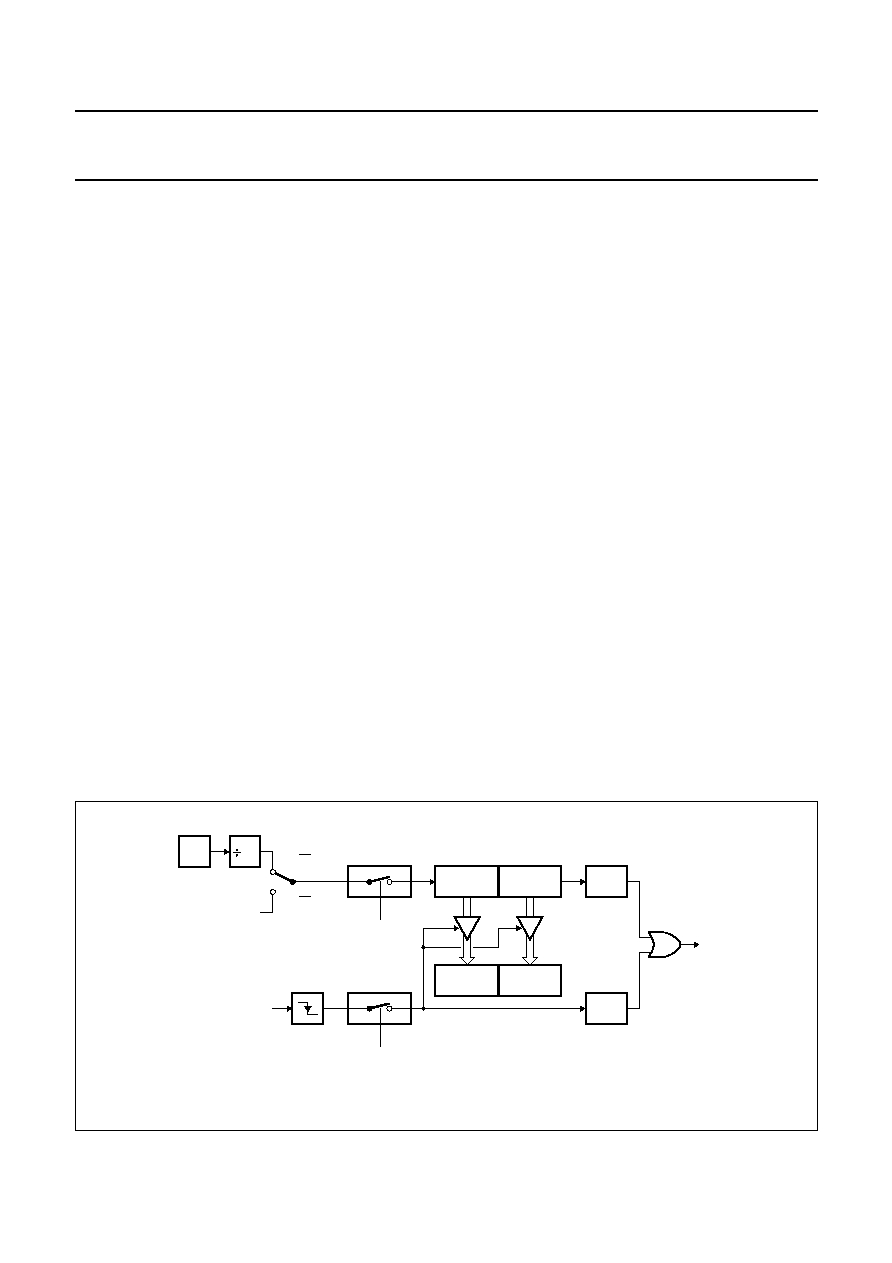

FUNCTIONAL DIAGRAM

Fig.2 Functional diagram.

handbook, full pagewidth

MGK191

PORT 0

SS

V

DD

V

PORT 1

PORT 3

ADDRESS

AND

DATA BUS

PORT 2

ADDRESS

BUS

secondary

functions

T2

T2EX

PORT 4

PORT 5

RST

XTAL1

XTAL2

RXD

TXD

T0

T1

RD

WR

INT1

INT0

P89C738

P89C739

PSEN

EA

ALE

1998 Apr 07

6

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

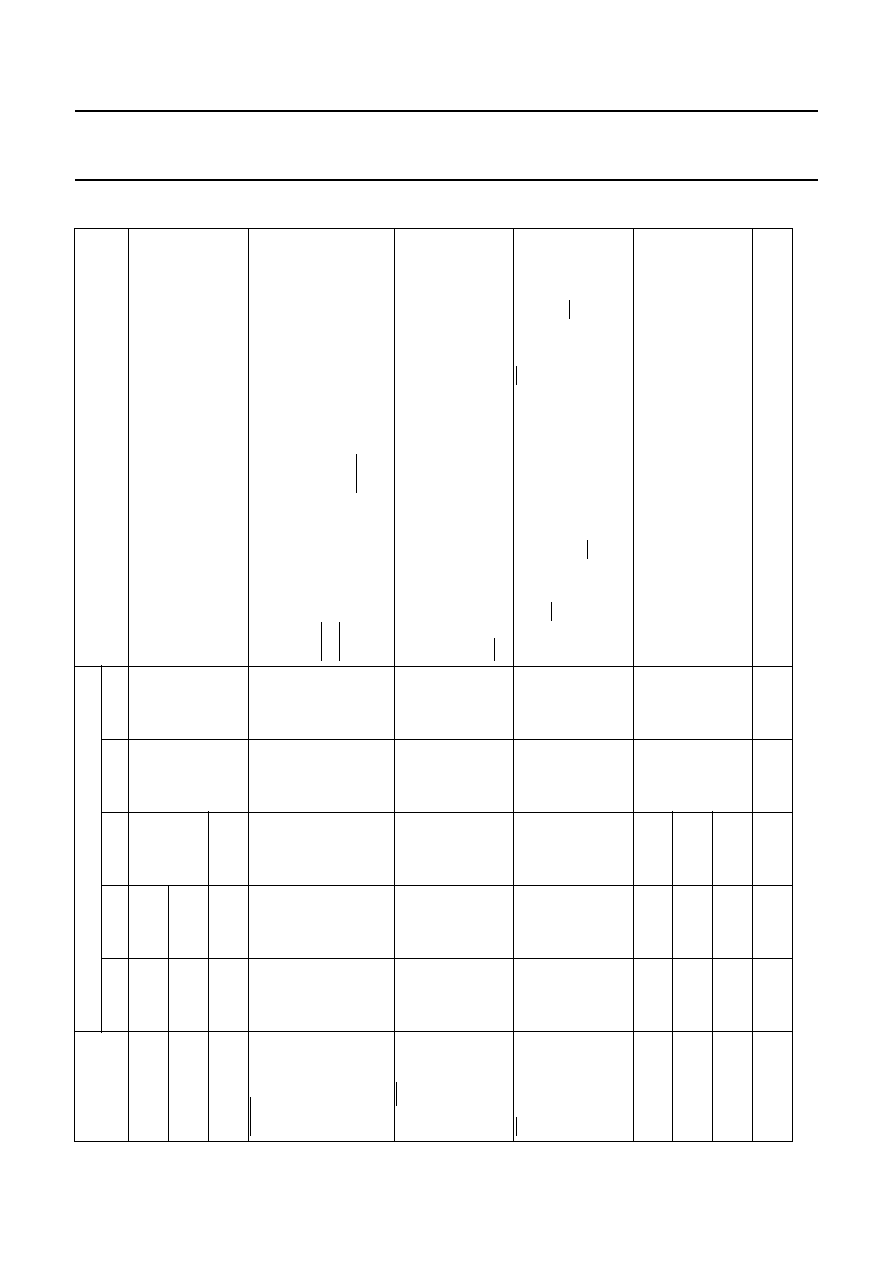

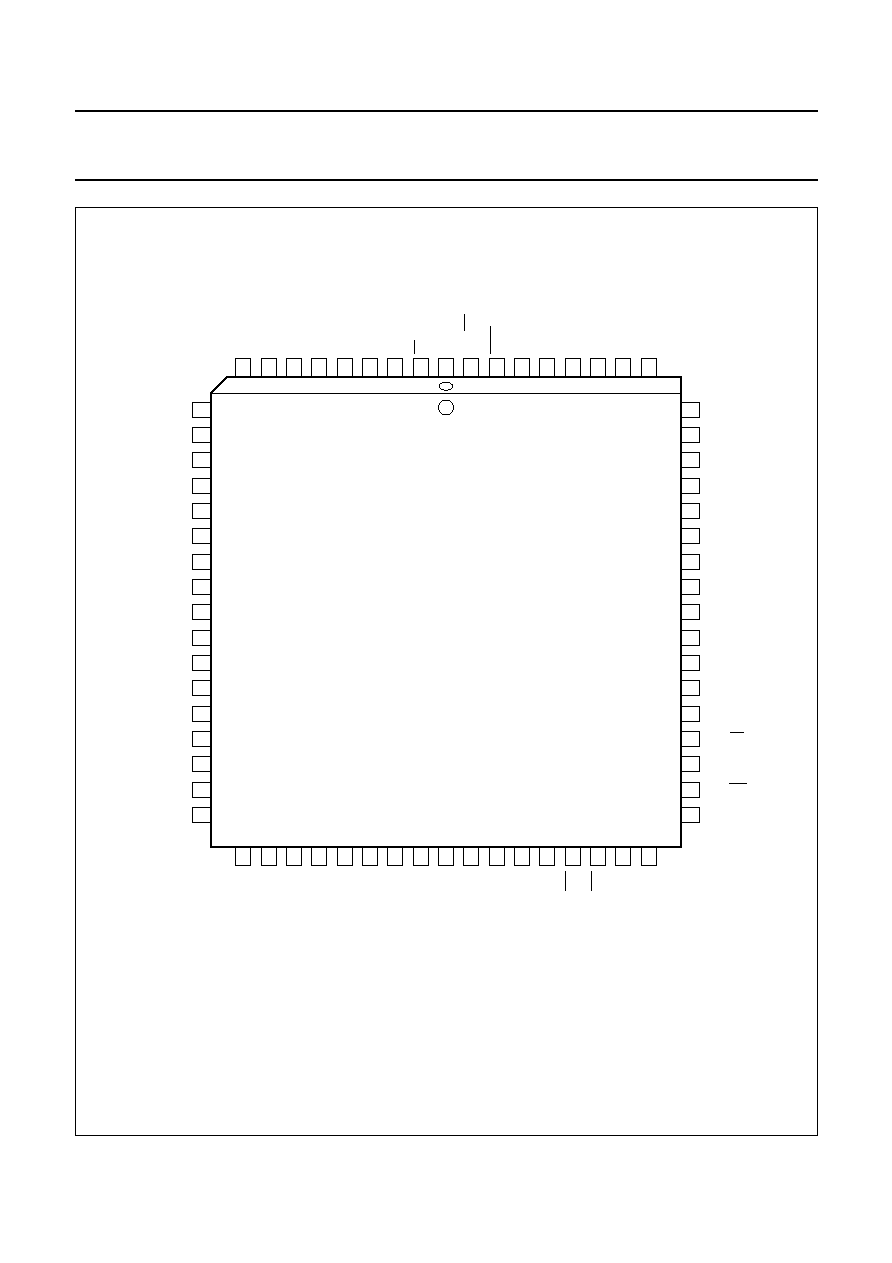

6

PINNING INFORMATION

6.1

Pin configuration

handbook, full pagewidth

12

13

14

15

16

17

7

8

9

10

11

39

38

37

36

35

34

33

32

31

30

29

18

19

20

21

22

23

24

25

26

27

28

6

5

4

3

2

1

44

43

42

41

40

MGK185

n.c.

P2.7/A15

P2.6/A14

P2.5/A13

P1.5

P1.6

P1.7

RST

P3.0/RXD/data

n.c.

P3.5/T1

EA/VPP

P3.1/TXD/clock

P3.4/T0

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

P3.2/INT0

P3.3/INT1

PSEN

ALE/WE

n.c.

P2.0/A8

P2.2/A10

P2.3/A11

P2.4/A12

P2.1/A9

V

SS

XTAL2

XTAL1

P3.6/WR

P3.7/RD

n.c.

P1.4

P1.3

P1.2

P1.1/T2EX

P1.0/T2

V

DD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P89C738ABA

Fig.3 Pin configuration for PLCC44 package; for more information on the version see Chapter 3.

1998 Apr 07

7

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.4 Pin configuration for DIP40 package (SOT129-1).

handbook, halfpage

P89C738ABP

MGK184

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VDD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

P2.6/A14

P2.5/A13

P2.4/A12

P2.3/A11

P2.2/A10

P2.1/A9

P2.7/A15

P2.0/A8

P1.0/T2

P1.1/T2EX

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

P3.0/RXD/data

P3.1/TXD/clock

P3.4/T0

P3.5/T1

RST

XTAL2

XTAL1

VSS

P3.2/INT0

EA/VPP

ALE/WE

PSEN

P3.6/WR

P3.3/INT1

P3.7/RD

1998 Apr 07

8

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.5 Pin configuration for QFP44 package; for more information on the version see Chapter 3.

handbook, full pagewidth

1

2

3

4

5

6

7

8

9

10

11

33

32

31

30

29

28

27

26

25

24

23

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

MGK186

n.c.

P2.7/A15

P2.6/A14

P2.5/A13

P1.5

P1.6

P1.7

RST

P3.0/RXD/data

n.c.

P3.5/T1

EA/VPP

n.c.

P2.0/A8

P2.2/A10

P2.3/A11

P2.4/A12

P2.1/A9

n.c.

P1.4

P1.3

P1.2

P1.1/T2EX

P1.0/T2

P3.1/TXD/clock

P3.4/T0

P89C738ABB

V

DD

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

V

SS

XTAL2

XTAL1

P3.2/INT0

P3.3/INT1

PSEN

ALE/WE

P3.6/WR

P3.7/RD

1998 Apr 07

9

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.6 Pin configuration for PLCC68 package; for more information on the version see Chapter 3.

handbook, full pagewidth

P89C739ABA

MGK187

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

P5.5

P5.6

P5.7

P1.0/T2

P4.0

P1.1/T2EX

P1.2

P1.3

P4.1

P1.4

P4.2

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

P5.0

P2.4/AD12

P2.3/AD11

P4.7

P2.2/AD10

P2.1/AD9

P2.0/AD8

P4.6

P4.5

P4.4

P4.3

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

P1.5

P1.6

P1.7

RST

P3.0/RXD/data

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

n.c.

P3.1/TXD/clock

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1

9

8

7

6

5

4

3

2

1

68

67

66

65

64

63

62

61

P0.4/AD4

P5.4

P5.3

P0.5/AD5

P0.6/AD6

P0.7/AD7

P2.7/AD15

P2.6/AD14

P5.2

P5.1

P2.5/AD13

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

n.c.

XTAL2

XTAL1

VSS

VDD

n.c.

EA/V

PP

ALE/WE

PSEN

P3.7/RD

P3.6/WR

1998 Apr 07

10

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.7 Pin configuration for QFP64 package (SOT319-1).

handbook, full pagewidth

MGK188

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

P0.4/AD4

P1.5

P2.5/AD13

P3.5/T1

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

P89C739ABB

P5.5

P5.6

P5.7

P1.0/T2

P4.0

P1.1/T2EX

P1.2

P1.3

P4.1

P1.4

P4.2

P5.0

P2.4/AD12

P2.3/AD11

P4.7

P2.2/AD10

P2.1/AD9

P2.0/AD8

P4.6

P4.5

P4.4

P4.3

P1.6

P1.7

RST

P3.0/RXD/data

n.c.

n.c.

n.c.

n.c.

n.c.

P3.1/TXD/clock

P3.2/INT0

P3.3/INT1

P3.4/T0

P0.0/AD0

P0.1/AD1

P0.2/AD2

P0.3/AD3

n.c.

XTAL2

XTAL1

VSS

VDD

VSS

P3.7/RD

P3.6/WR

n.c.

P5.3

P5.4

P0.5/AD5

P0.6/AD6

P0.7/AD7

P2.7/AD15

P2.6/AD14

P5.1

P5.2

EA/V

PP

ALE/WE

PSEN

1998

Apr

07

11

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

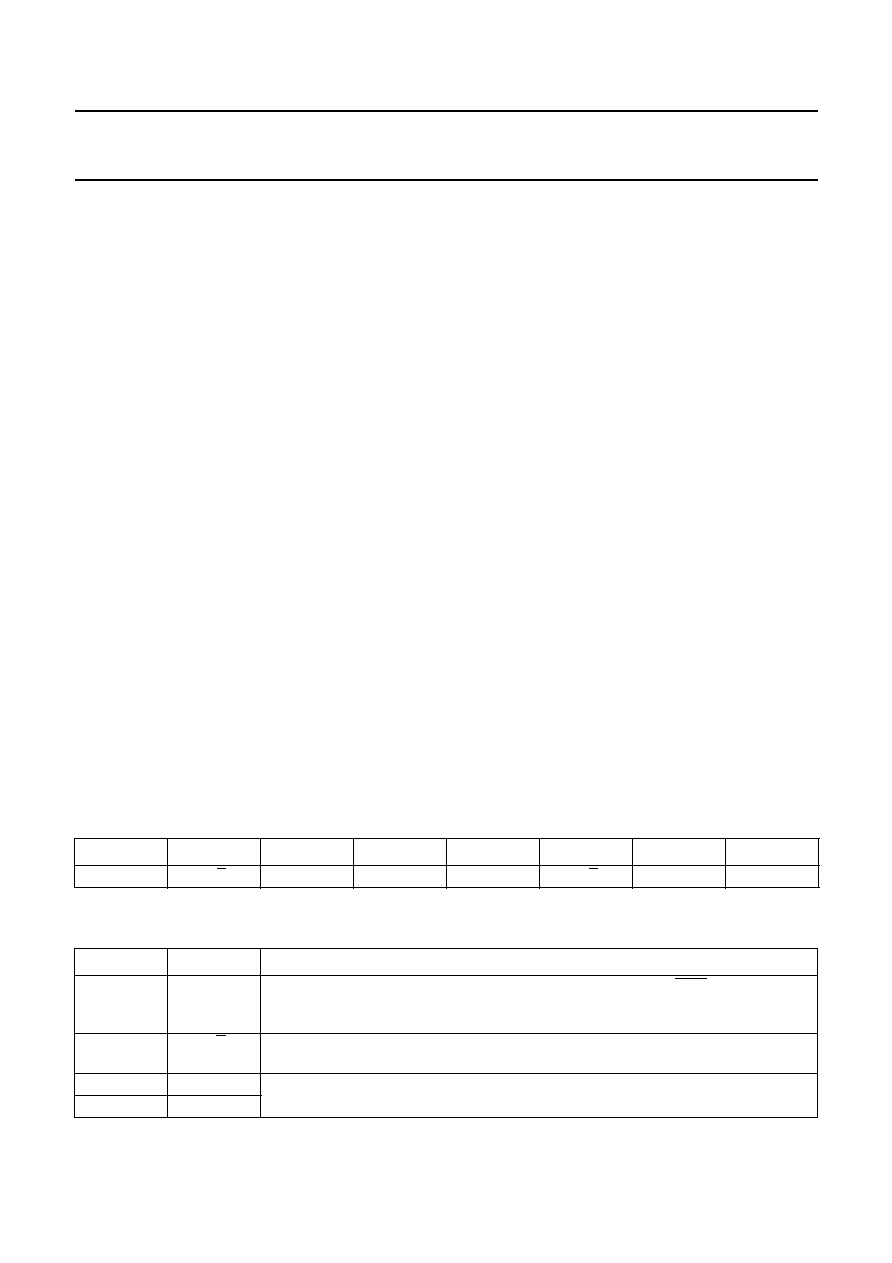

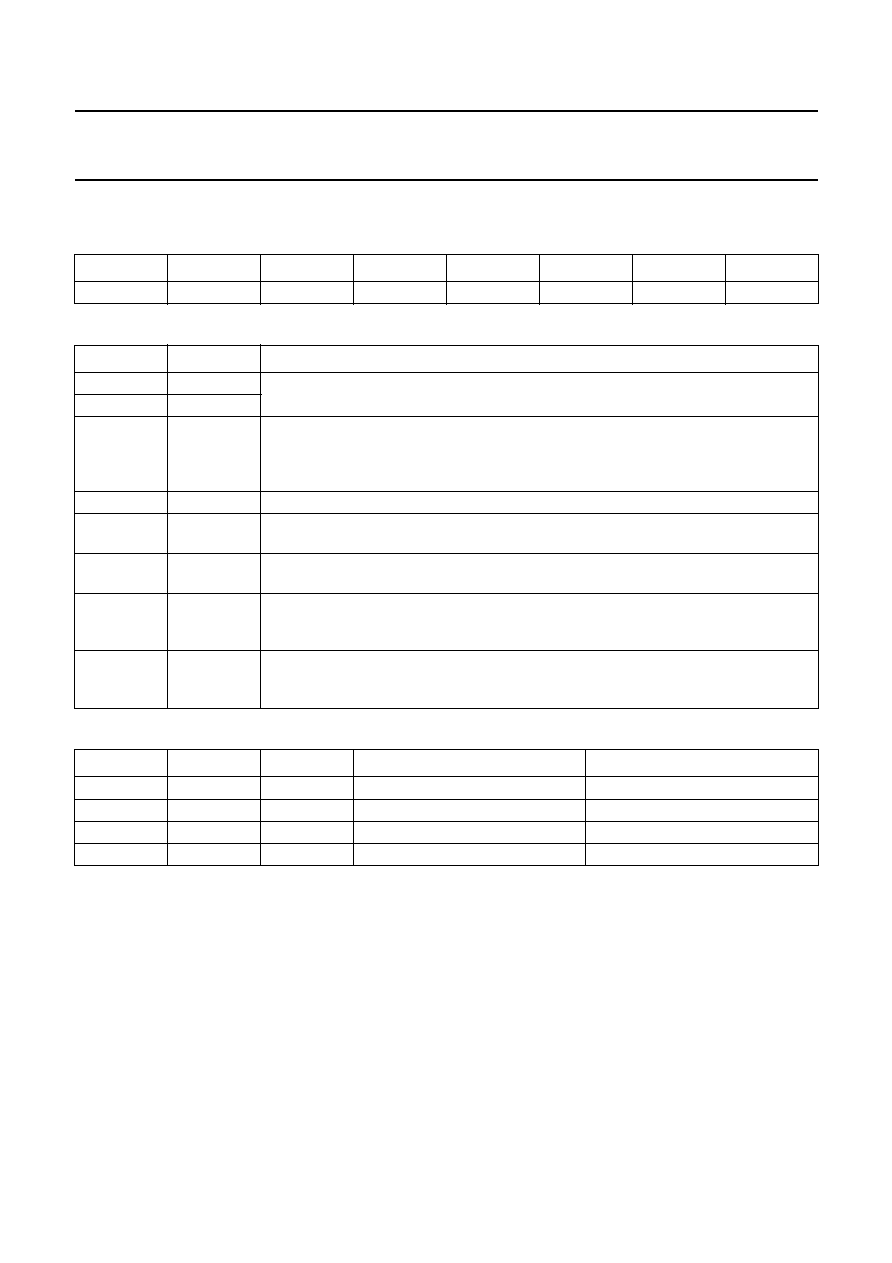

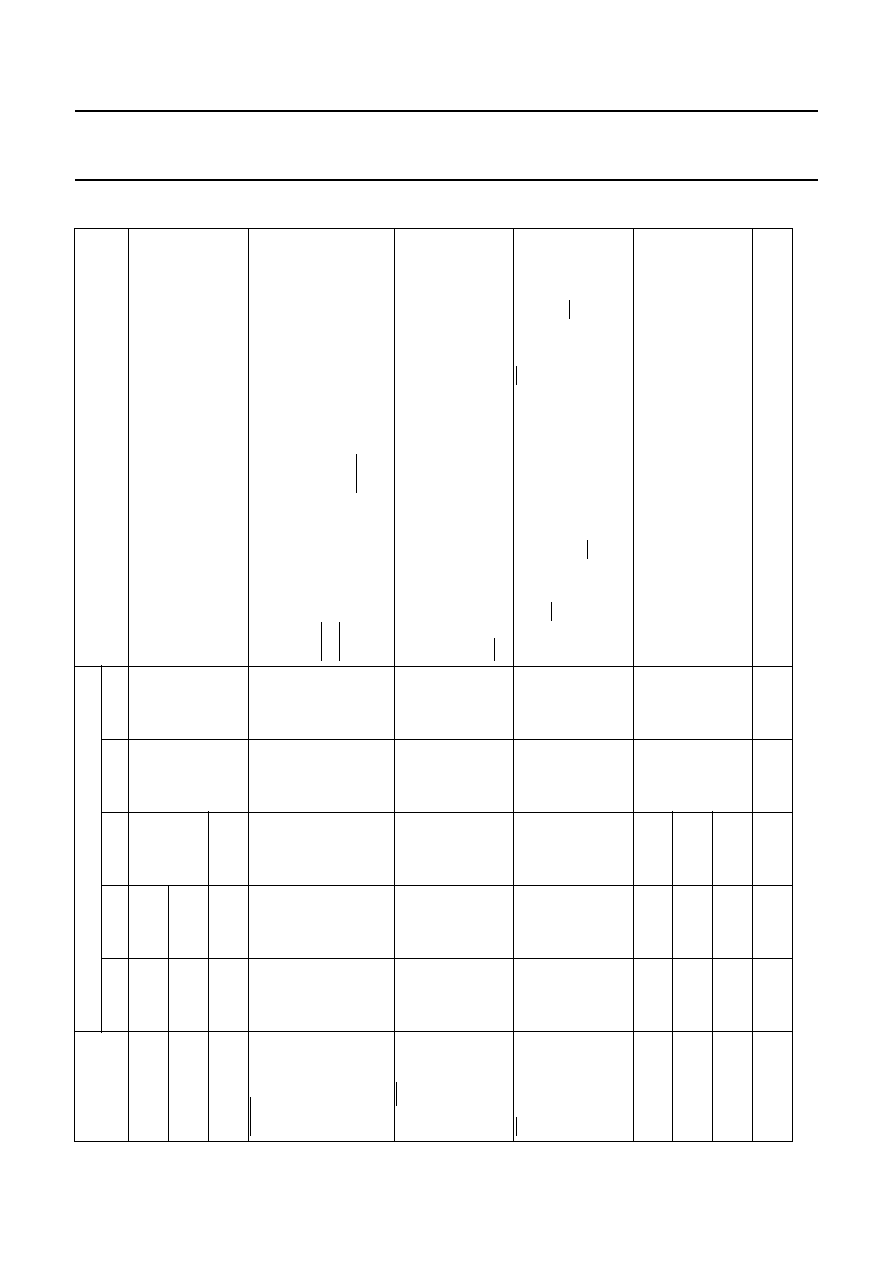

6.2

Pin description

Table 1

Pin description for DIP40; QFP44; PLC44; QFP64 and PLCC68.

SYMBOL

PIN

(1)

DESCRIPTION

PLCC68

QFP64

PLCC44

QFP44

DIP40

P1.0/T2

19

11

16

2

1

Port 1: P1.0 to P1.7; 8-bit quasi-bidirectional I/O port. Port 1 can

sink/source one TTL (= 4 LSTTL) input. It can drive CMOS inputs

without external pull-ups.

Port 1 alternative functions are: T2; Timer/event counter 2 external

event counter input (falling edge triggered). T2EX; Timer/event

counter 2 capture/reload trigger or external interrupt 2 input (falling

edge triggered).

P1.1/T2EX

21

13

15

3

2

P1.2

22

14

14

4

3

P1.3

23

15

13

5

4

P1.4

25

17

12

6

5

P1.5

27

19

1

7

6

P1.6

28

20

2

8

7

P1.7

29

21

3

9

8

RST

30

22

4

10

9

Reset; a HIGH level on this pin for two machine cycles while the

oscillator is running, resets the device. An internal pull-down resistor

permits power-on reset using only a capacitor connected to V

DD

.

After a Watchdog Timer overflow this pin is pulled HIGH while the

internal reset signal is active.

P3.0/RXD/data

34

26

5

11

10

Port 3: P3.0 to P3.7; 8-bit quasi-bidirectional I/O Port with internal

pull-ups. Port 3 can sink/source one TTL (= 4 LSTTL) input. It can

drive CMOS inputs without external pull-ups.

Port 3 alternative functions are: RXD/data; Serial Port data input

(asynchronous) or data input/output (synchronous).

TXD/clock; Serial Port data output (asynchronous) or clock output

(synchronous). INT0; External interrupt 0 or gate control input for

Timer/event counter 0. INT1; External interrupt 1 or gate control

input for Timer/event counter 1. T0; external input for Timer/event

counter 0. T1; external input for Timer/event counter 1.

WR; external data memory write strobe. RD; external data memory

read strobe.

P3.1/TXD/clock 39

29

7

13

11

P3.2/INT0

40

30

8

14

12

P3.3/INT1

41

31

9

15

13

P3.4/T0

42

32

10

16

14

P3.5/T1

43

33

11

17

15

P3.6WR

45

35

44

18

16

P3.7/RD

47

37

43

19

17

XTAL2

48

38

42

20

18

Crystal input 2: output of the inverting amplifier that forms the

oscillator. This pin left open-circuit when an external oscillator clock

is used (see Figs 18 and 20).

XTAL1

49

39

41

21

19

Crystal input 1: input to the inverting amplifier that forms the

oscillator, and input to the internal clock generator. Receives the

external oscillator clock signal when an external oscillator is used

(see Figs 18 and 20).

V

SS

51

41

40

22

20

Ground: circuit ground potential.

1998

Apr

07

12

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

P2.0/A8 to

P2.2/A10

54 to 56

44 to 46

38 to 34

24 to 31

21 to 28

Port 2: P2.0 to P2.7; 8-bit quasi-bidirectional I/O Port with internal

pull-ups. Port 2 can sink/source one TTL (= 4 LSTTL) input. It can

drive CMOS inputs without external pull-ups.

Port 2 alternative functions are: A8 to A15; during access to

external memories (RAM/ROM) that use 16-bit addresses (MOVX

@DPTR) Port 2 emits the high-order address byte (A8 to A15).

P2.3/A11 to

P2.4/A12

58 to 59

48 to 49

P2.5/A13 to

P2.7/A15

61, 64

and 65

51, 54

and 55

23 to 25

PSEN

67

56

26

32

29

Program Store Enable output: read strobe to the external program

memory via Port 0 and Port 2. It is activated twice each machine

cycle during fetches from external program memory.

When executing out of external program memory two activations of

PSEN are skipped during each access to external data memory.

PSEN is not activated (remains HIGH) during no fetches from

external program memory. PSEN can sink/source 8 LSTTL inputs. It

can drive CMOS inputs without external pull-ups.

ALE/WE

(2)

68

57

27

33

30

Address Latch Enable output: latches the lower byte of the

address during access to external memory in normal operation. It is

activated every six oscillator periods except during an external data

memory access. ALE can sink/source 8 LSTTL inputs. It can drive

CMOS inputs without an external pull-up.

WE: Write Enable.

EA/V

PP

2

59

29

35

31

External Access input: when during reset, EA is held at a TTL

HIGH level, the CPU executes from the internal program ROM.

When EA is held at a TTL LOW level during reset, the CPU executes

out of external program memory via Port 0 and Port 2. EA is not

allowed to float. EA is latched during reset and don't care after reset.

V

PP

: programming supply voltage.

P0.7/AD7 to

P0.4/AD4

3, 5, 6

and 9

60, 61, 62

and 1

30 to 33

36 to 43

32 to 39

Port 0: P0.7 to P0.0; 8-bit open-drain bidirectional I/O port. It is also

the multiplexed low-order address and data bus during accesses to

external memory: AD0 to AD7. During these accesses internal

pull-ups are activated. Port 0 can sink/source 8 LSTTL inputs.

P0.3/AD3 to

P0.2/AD2

11 to 12

3 to 4

22 to 21

P0.1/AD1 to

P0.0/AD0

14 to 15

6 to 7

20 to 19

V

DD

17

9

18

44

40

Power supply (+5 V) pin for normal operation, Idle mode and

Power-down mode.

SYMBOL

PIN

(1)

DESCRIPTION

PLCC68

QFP64

PLCC44

QFP44

DIP40

1998

Apr

07

13

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Notes

1. To avoid a `latch-up' effect at power-on, the voltage on any pin (at any time) must not be higher than V

DD

+ 0.5 V or lower than V

SS

-

0.5 V

respectively.

2. To prohibit the toggling of the ALE/WE pin (RFI noise reduction) the bit RFI in the PCON register (PCON.5) must be set by software. This bit is

cleared on reset and can be cleared by software. When set, ALE/WE pin will be pulled down internally, switching an external address latch to a

quiet state. The MOVX instruction will still toggle ALE/WE as a normal MOVX. ALE/WE will retain its normal HIGH value during Idle mode and a

LOW value during Power-down mode while in the `RFI' mode. Additionally during internal access (EA = 1) ALE/WE will toggle normally when the

address exceeds the internal program memory size. During external access (EA = 0) ALE/WE will always toggle normally, whether the flag `RFI' is

set or not.

3. n.a. = not applicable.

P4.0 to P4.7

20, 24,

26, 44,

46, 50, 53

and 57

12, 16,

18, 34,

36, 40, 43

and 47

n.a.

(3)

n.a.

n.a.

Port 4: P4.0 to P4.7; 8-bit quasi-bidirectional I/O port with internal

pull-ups. Port 4 can sink/source 4 LSTTL inputs. It can drive CMOS

inputs without external pull-ups.

P5.0 to P5.7

60, 62,

63, 7, 8,

10, 13

and 16

50, 52,

53, 63,

64, 2, 5

and 8

n.a.

n.a.

n.a.

Port 5: P5.0 to P5.7; 8-bit quasi-bidirectional I/O port with internal

pull-ups. Port 5 can sink/source 4 LSTTL inputs. It can drive CMOS

inputs without external pull-ups.

n.c.

1, 4, 18,

31, 32,

33, 35,

36, 37, 38

52 and 66

23, 24,

25, 27,

28, 42

and 58

6, 17, 28

and 39

1, 12, 23

and 34

n.a.

Not connected.

SYMBOL

PIN

(1)

DESCRIPTION

PLCC68

QFP64

PLCC44

QFP44

DIP40

1998 Apr 07

14

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

7

FUNCTIONAL DESCRIPTION

This chapter gives a brief overview of the device.

Detailed functional descriptions are given in the following

chapters:

Chapter 8 "Memory organization"

Chapter 9 "Interrupt system"

Chapter 10 "Timers/counters"

Chapter 11 "I/O facilities"

Chapter 12 "Full duplex Serial Port (UART)"

Chapter 13 "Reduced power modes"

Chapter 14 "Oscillator circuit"

Chapter 15 "Reset"

Chapter 16 "Multiple Programming ROM (MTP-ROM)".

7.1

General

The P89C738 is a stand-alone high-performance

microcontroller designed for use in real time applications

such as instrumentation, industrial control and medium to

high-end consumer applications.

In addition to the 80C51 standard functions, the device

provides a number of dedicated hardware functions for

these applications. The P89C738 is a control-oriented

CPU with on-chip Program and data memory. It can

execute programs with internal or external program

memory up to 64 kbytes. It can also access up to

64 kbytes of external data memory. For systems requiring

extra capability, the P89C738 can be expanded using

standard memories and peripherals.

The P89C738 has two software selectable modes of

reduced activity for further power reduction: Idle and

Power-down. The Idle mode freezes the CPU while

allowing the RAM, timers, serial ports and interrupt system

to continue functioning. The Power-down mode saves the

RAM contents but freezes the oscillator causing all other

chip functions to be inoperative except the Watchdog

Timer if it is enabled. The Power-down mode can be

terminated by an external reset, a Watchdog Timer

overflow and in addition, by either of the two external

interrupts.

7.2

Instruction set execution

The P89C738 uses the powerful instruction set of the

80C51. Additional Special Function Registers (SFRs) are

incorporated to control the on-chip peripherals.

The instruction set consists of 49 single-byte, 46 two-byte

and 16 three-byte instructions. When using a 16 MHz

oscillator, 64 instructions execute in 750 ns and

45 instructions execute in 1.5

µ

s. Multiply and divide

instructions execute in 3

µ

s (see Chapter 18).

1998 Apr 07

15

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

8

MEMORY ORGANIZATION

The Central Processing Unit (CPU) manipulates operands

in three memory spaces; these are the 64 kbytes external

data memory (of which the lower 256 bytes reside in the

internal AUX-RAM), 512 bytes internal data memory

(consisting of 256 bytes standard RAM and 256 bytes

AUX-RAM) and the 64 kbytes internal and external

program memory.

8.1

Program memory

The program memory address space of the P89C738

comprises an internal and an external memory portion.

The P89C738 has 64 kbytes of program memory on-chip.

The program memory can also be externally addressed up

to 64 kbytes. If the EA pin is held HIGH, the P89C738

executes out of the internal program memory. If EA pin is

held LOW, the P89C738 fetches all instructions from the

external program memory. Figure 8 illustrates the program

memory address space.

The security bit is always set in the P89C738 and

P89C739 to protect the ROM code. Table 2 lists the

access to the internal and external program memory by the

MOVC instructions when the security bit has been set to a

logic 1. If the security bit has been set to a logic 0 there are

no restrictions for the MOVC instructions.

Table 2

Internal and external program memory access

MOVC

INSTRUCTION

PROGRAM MEMORY ACCESS

INTERNAL

EXTERNAL

MOVC in internal

program memory

YES

YES

MOVC in external

program memory

NO

YES

Fig.8 Program memory address space.

handbook, halfpage

MGK190

EXTERNAL

(EA = 0)

INTERNAL

(EA = 1)

PROGRAM MEMORY

65535

0

8.2

Internal data memory

The internal data memory is divided into three physically

separated parts: 256 bytes of RAM, 256 bytes of

AUX-RAM, and a 128 bytes Special Function Registers

(SFRs) area. These parts can be addressed as follows

(see Fig.9 and Table 3):

∑

RAM locations 0 to 127 can be addressed directly and

indirectly as in the 80C51. Address pointers are R0 and

R1 of the selected register bank.

∑

RAM locations 128 to 255 can only be addressed

indirectly. Address pointers are R0 and R1 of the

selected register bank.

∑

AUX-RAM locations 0 to 255 are indirectly addressable

as the external data memory locations 0 to 255 with the

MOVX instructions. Address pointers are R0 and R1 of

the selected register bank and DPTR. When executing

from internal program memory, an access to AUX-RAM

0 to 255 will not affect the ports Port 0, Port 2,

P3.6 and P3.7.

∑

The SFRs can only be addressed directly in the address

range from 128 to 255.

An access to external data memory locations higher than

255 will be performed with the MOVX DPTR instructions in

the same way as in the 80C51 structure, i.e. with Port 0

and Port 2 as data/address bus and P3.6 and P3.7 as write

and read timing signals. Note that the external data

memory cannot be accessed with R0 and R1 as address

pointer.

Figure 9 shows the internal and external data memory

address space. Chapter 17 shows the Special Function

Registers overview. Four 8-bit register banks occupy

locations 0 through 31 in the lower RAM area. Only one of

these banks may be enabled at a time. The next 16 bytes,

locations 32 through 47, contain 128 directly addressable

bit locations.

The stack can be located anywhere in the internal

256-byte RAM. The stack depth is only limited by the

available internal RAM space of 256 bytes. All registers

except the Program Counter and the four 8-bit register

banks reside in the SFR address space.

Table 3

Internal data memory access

MEMORY

LOCATION

ADDRESS MODE

RAM

0 to 127

direct and indirect

128 to 255

indirect only

SFR

128 to 255

direct only

AUX-RAM

0 to 255

indirect only with MOVX

1998 Apr 07

16

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.9 Internal and external data memory address space.

handbook, full pagewidth

MBK524

INDIRECT ONLY

DIRECT AND

INDIRECT

AUXILIARY

RAM

SFRs

255

127

0

EXTERNAL

(EA = 0)

INTERNAL

(EA = 1)

MAIN RAM

INTERNAL DATA MEMORY

EXTERNAL

DATA MEMORY

PROGRAM MEMORY

64 kbytes

64 kbytes

64 kbytes

0

OVERLAPPED SPACE

256

8.3

Addressing

The P89C738 has five modes for addressing:

∑

Register

∑

Direct

∑

Register-Indirect

∑

Immediate

∑

Base-Register plus Index-Register-Indirect.

The first three methods can be used for addressing

destination operands. Most instructions have a

`destination/source' field that specifies the data type,

addressing methods and operands involved.

For operations other than MOVs, the destination operand

is also a source operand.

Access to memory addresses is as follows:

∑

Register in one of the four 8-bit register banks through

Register, Direct or Register-Indirect addressing

∑

512 bytes of internal RAM through Direct or

Register-Indirect addressing. Bytes 0 to 127 of internal

RAM may be addressed directly/indirectly. Bytes

128 to 255 of internal RAM share their address location

with the SFRs and so may only be addressed indirectly

as data RAM. Bytes 0 to 255 of AUX-RAM can only be

addressed indirectly via MOVX.

∑

SFR through Direct addressing at address locations

128 to 255

∑

External data memory through Register-Indirect

addressing

∑

Program memory look-up tables through Base-Register

plus Index-Register-Indirect addressing.

1998 Apr 07

17

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

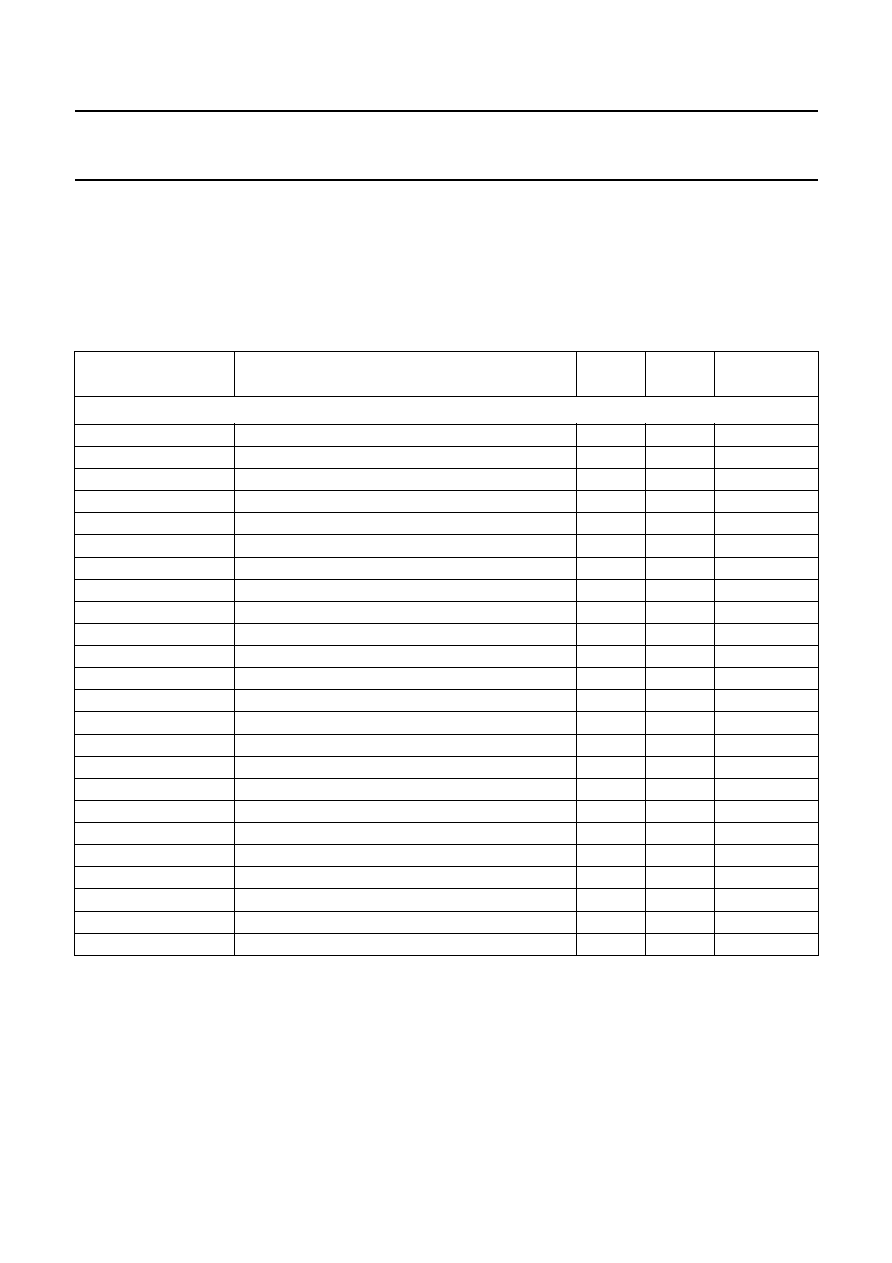

9

INTERRUPT SYSTEM

The P89C738 contains the same interrupt structure as the

PCB80C51BH, but with a six-source interrupt structure

with two priority levels (see Fig.10).

The external interrupts INT0 and INT1 can each be either

level-activated or transition-activated, depending on bits

IT0 and IT1 in SFR TCON. The flags that actually generate

these interrupts are bits IE0 and IE1 in TCON. When an

external interrupt is generated, the corresponding request

flag is cleared by the hardware when the service routine is

vectored to, only if the interrupt was transition-activated.

If the interrupt was level-activated the external source has

to hold the request active until the requested interrupt is

actually generated. Then it has to deactivate the request

before the interrupt service routine is completed, or else

another interrupt will be generated.

The Timer 0 and Timer 1 interrupts are generated by TF0

and TF1, which are set by a roll-over in their respective

timer/counter register (except for Timer 0 in Mode 3 of the

serial interface). When a timer interrupt is generated, the

flag that generated it is cleared by the on-chip hardware

when the service routine is vectored to.

The Serial Port interrupt is generated by the logical `OR' of

RI and TI. Neither of these flags is cleared by hardware.

The service routine will normally have to determine

whether it was RI or TI that generated the interrupt, and the

bit will have to be cleared by software.

The Timer 2 interrupt is generated by the logical OR of TF2

and EXF2. Neither of these flags is cleared by hardware.

In fact the service routine may have to determine whether

it was TF2 or EXF2 that generated the interrupt, and the bit

will have to be cleared by software.

An additional (third) external interrupt is available, if

Timer 2 is not used as timer/counter or if Timer 2 is used

in the baud rate generator mode. That external interrupt 2

is falling-edge triggered. It shares the Timer 2 interrupt

vector, interrupt enable and interrupt priority bits. If bit

EXEN2 = 1 (T2CON.3), a HIGH-to-LOW transition at pin

P1.1/T2EX sets the interrupt request flag EXF2

(T2CON.6) and can be used to generate an external

interrupt.

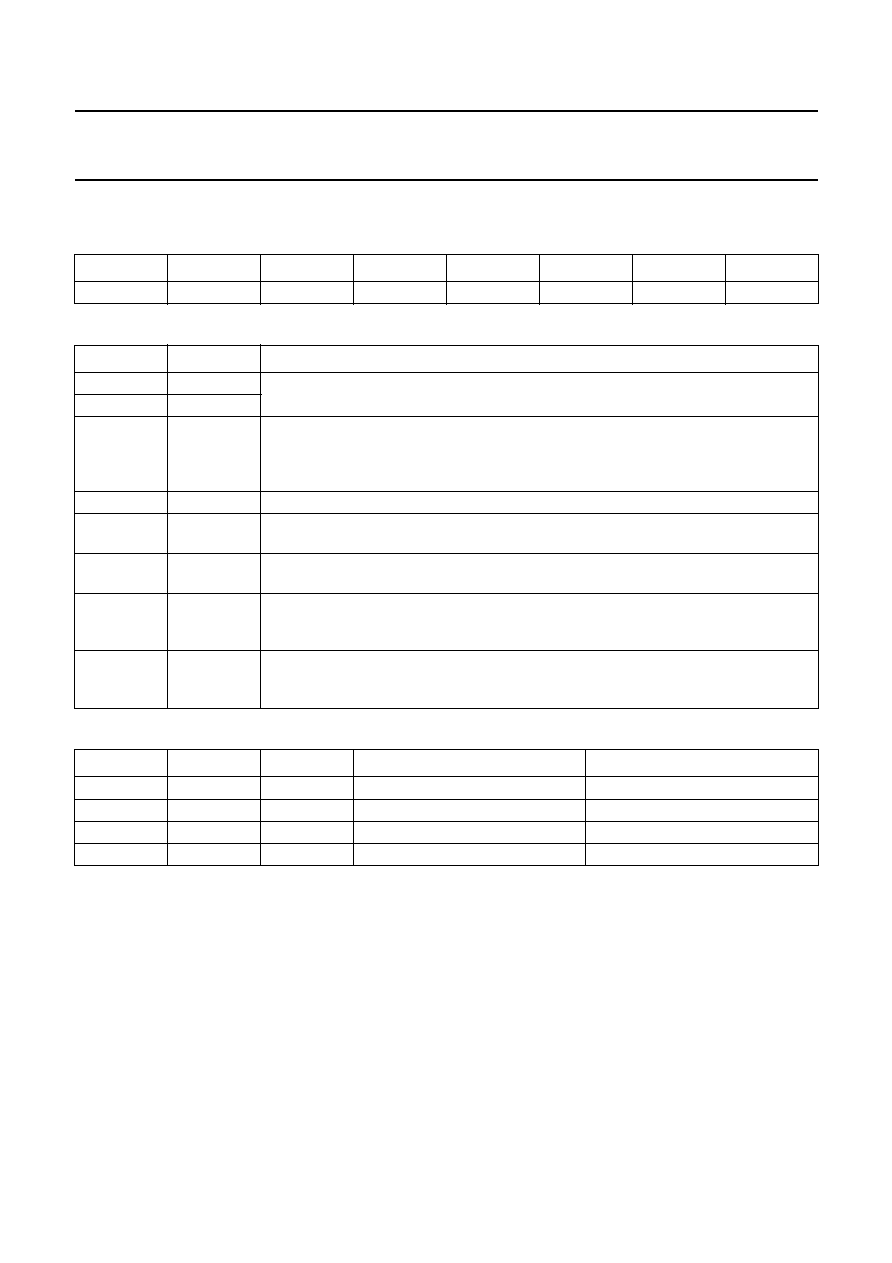

The interrupt vectors are listed in Table 4.

Table 4

Interrupt vectors

SOURCE

PRIORITY

WITHIN LEVEL

VECTOR

ADDRESS

IE0

1 (highest)

0003H

TF0

2

000BH

IE1

3

0013H

TF1

4

001BH

RI + TI

5

0023H

TF2 + EXF2

6 (lowest)

002BH

Fig.10 P89C738/P89C739 interrupt sources.

handbook, halfpage

MGK193

IT1

INT1

TF1

TF0

TI

RI

TF2

EXF2

IE1

IT0

INT0

IE0

1

0

interrupt

sources

1

0

1998 Apr 07

18

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

9.1

Interrupt Enable Register (IE)

Table 5

Interrupt Enable Register (SFR address A8H)

Table 6

Description of IE bits

9.2

Interrupt Priority Register (IP)

Table 7

Interrupt Priority Register (SFR address B8H)

Table 8

Description of IP bits

7

6

5

4

3

2

1

0

EA

-

ET2

ES

ET1

EX1

ET0

EX0

BIT

SYMBOL

DESCRIPTION

7

EA

General enable/disable control. If EA = 0, no interrupt is enabled. If EA = 1, any

individually enabled interrupt will be accepted.

6

-

reserved

5

ET2

enable Timer 2 interrupt

4

ES

enable Serial Port interrupt

3

ET1

enable Timer 1 interrupt

2

EX1

enable external interrupt 1

1

ET0

enable Timer 0 interrupt

0

EX0

enable external interrupt 0

7

6

5

4

3

2

1

0

-

-

PT2

PS

PT1

PX1

PT0

PX0

BIT

SYMBOL

DESCRIPTION

7

-

reserved

6

-

reserved

5

PT2

Timer 2 interrupt priority level

4

PS

Serial Port interrupt priority level

3

PT1

Timer 1 interrupt priority level

2

PX1

external interrupt 1 priority level

1

PT0

Timer 0 interrupt priority level

0

PX0

external interrupt 0 priority level

1998 Apr 07

19

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

10 TIMERS/COUNTERS

The P89C738 contains three 16-bit timer/counters:

Timer 0, Timer 1 and Timer 2; and one 8-bit timer, the

Watchdog Timer (T3). Timer 0, Timer 1 and Timer 2 may

be programmed to carry out the following functions:

∑

Measure time intervals and pulse durations

∑

Count events

∑

Generate interrupt requests.

10.1

Timer 0 and Timer 1

Timers 0 and 1 each have a control bit in SFR TMOD that

selects the timer or counter function of the corresponding

timer. In the timer function, the register is incremented

every machine cycle. Thus, one can think of it as counting

machine cycles. Since a machine cycle consists

of 12 oscillator periods, the count rate is

1

/

12

of the

oscillator frequency.

In the counter function, the register is incremented in

response to a HIGH-to-LOW transition at the

corresponding external input pin, T0 or T1. In this function,

the external input is sampled during S5P2 of every

machine cycle. When the samples show a HIGH in one

cycle and a LOW in the next cycle, the counter is

incremented. Thus, it takes two machine cycles

(24 oscillator periods) to recognize a HIGH-to-LOW

transition. There are no restrictions on the duty cycle of the

external input signal, but to ensure that a given level is

sampled at least once before it changes, it should be held

for at least one full machine cycle.

Timer 0 and Timer 1 can be programmed independently to

operate in one of four modes:

Mode 0 8-bit timer/counter with divide-by-32 prescaler

Mode 1 16-bit timer/counter

Mode 2 8-bit timer/counter with automatic reload

Mode 3 Timer 0: one 8-bit timer/counter and one 8-bit

timer. Timer 1: stopped.

When Timer 0 is in Mode 3, Timer 1 can be programmed

to operate in Modes 0, 1 or 2 but cannot set an interrupt

request flag and generate an interrupt. However, the

overflow from Timer 1 can be used to pulse the Serial Port

transmission-rate generator. With a 16 MHz crystal, the

counting frequency of these timer/counters is as follows:

∑

In the timer function, the timer is incremented at a

frequency of 1.33 MHz (

1

/

12

◊

oscillator frequency)

∑

In the counter function, the frequency handling range for

external inputs is 0 to 0.66 MHz.

Both internal and external inputs can be gated to the timer

by a second external source for directly measuring pulse

duration.

The timers are started and stopped under software control.

Each one sets its interrupt request flag when it overflows

from all logic 1's to all logic 0's (respectively, the automatic

reload value), with the exception of Mode 3 as previously

described.

10.1.1

Timer/Counter Mode Control Register (TMOD)

Table 9

Timer/Counter Mode Control Register (SFR address 89H)

Table 10 Description of TMOD bits for Timer 1 and Timer 0

Timer 0: bit TMOD.0 to TMOD.3; Timer 1: bit TMOD.4 to TMOD.7; n = 0, 1.

7

6

5

4

3

2

1

0

GATE

C/T

M1

M0

GATE

C/T

M1

M0

BIT

SYMBOL

DESCRIPTION

7 and 3

GATE

Gating control. When set Timer/counter `n' is enabled only when INTn pin is HIGH and

control bit TRn (TR1 or TR0) is set. When cleared Timer n is enabled whenever TRn

control bit is set.

6 and 2

C/T

Timer or Counter Selector. Cleared for Timer operation; input from internal system

clock. Set for Counter operation; input from pin Tn (T1 or T0).

5 and 1

M1

Timer 0, Timer 1 mode select; see Table 11.

4 and 0

M0

1998 Apr 07

20

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Table 11 Timer 0; Timer 1 mode select

10.1.2

Timer/Counter Control Register (TCON)

Table 12 Timer/Counter Control Register (SFR address 88H)

Table 13 Description of TCON bits

M1

M0

OPERATING

0

0

Timer TL0; TL1 serves as 5-bit prescaler.

0

1

16-bit Timer/Counter TH0; TH1 and TL0; TL1 are cascaded; there is no prescaler.

1

0

8-bit auto-reload Timer/Counter TH0; TH1 holds a value which is to be reloaded into

TL0; TL1 each time it overflows.

1

1

Timer 0: TL0 is an 8-bit Timer/Counter controlled by the standard Timer 0 control bits.

TH0 is an 8-bit timer only controlled by Timer 1 control bits.

1

1

Timer 1: Timer/Counter 1 stopped.

7

6

5

4

3

2

1

0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

BIT

SYMBOL

DESCRIPTION

7 and 5

TF1 and TF0 Timer 1 and Timer 0 overflow flags. Set by hardware on Timer/Counter overflow.

Cleared by hardware when processor vectors to interrupt routine.

6 and 4

TR1 and TR0 Timer 1 and Timer 0 run control bits. Set/cleared by software to turn Timer/Counter

on/off.

3 and 1

IE1 and IE0

Interrupt 1 and Interrupt 0 edge flags. Set by hardware when external interrupt edge

detected. Cleared when interrupt processed.

2 and 0

IT1 and IT0

Interrupt 1 and Interrupt 0 type control bits. Set/cleared by software to specify falling

edge/LOW level triggered external interrupts.

1998 Apr 07

21

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

10.2

Timer 2

Timer 2 is functionally similar to the Timer 2 of the 8052AH. Timer 2 is a 16-bit timer/counter which is formed by two

SFRs, TL2 and TH2. Another pair of SFRs, RCAP2L and RCAP2H, form a 16-bit capture register or a 16-bit reload

register.

Like Timer 0 and Timer 1, Timer 2 can operate either as timer or as event counter. This is selected by bit C/T2 in SFR

T2CON. The timer has three operating modes: `capture', `autoload' and `baud rate generator', which are selected by bits

in SFR T2CON (see Tables 14 and 15).

10.2.1

T

IMER

/C

OUNTER

2 C

ONTROL

R

EGISTER

(T2CON)

Table 14 Timer/Counter 2 Control Register (SFR address C8H)

Table 15 Description of T2CON bits

Table 16 Timer 2 operating modes

X = don't care.

7

6

5

4

3

2

1

0

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/T2

CP/RL2

BIT

SYMBOL

DESCRIPTION

7

TF2

Timer 2 overflow flag. Set by a Timer 2 overflow and must be cleared by software. TF2

will not be set when either RCLK = 1 or TCLK = 1. When Timer 2 interrupt is enabled,

TF2 = 1 will cause the CPU to vector to Timer 2 interrupt routine.

6

EXF2

Timer 2 external flag. Set when either a capture or reload is caused by a negative

transition on T2EX and when EXEN2 = 1. When Timer T2 interrupt is enabled,

EXF2 = 1 will cause the CPU to vector to Timer 2 interrupt routine.

5

RCLK

Receive clock flag. When set, causes the Serial Port to use Timer 2 overflow pulses

for its receive clock in Modes 1 and 3. RCLK = 0 causes Timer 1 overflows to be used

for the receive clock.

4

TCLK

Transmit clock flag. When set, causes the Serial Port to use Timer 2 overflow pulses

for its transmit clock in Modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used

for the transmit clock.

3

EXEN2

Timer 2 external enable flag. When set, allows a capture or reload to occur as a result

of a negative transition on T2EX, if Timer 2 is not being used to clock the Serial Port.

EXEN2 = 0, causes Timer 2 to ignore events at T2EX.

2

TR2

Timer 2 start/stop control. TR2 = 1 starts Timer 2; TR2 = 0 stops Timer 2.

1

C/T2

Timer 2 timer or counter select. C/T2 = 0 selects the internal timer with a clock

frequency of

1

/

12

f

clk

. C/T2 = 1 selects the external event counter; falling edge triggered.

0

CP/RL2

Capture/reload flag. When set, capture will occur on negative transitions at T2EX if

EXEN2 = 1. When cleared, reloads will occur upon either Timer 2 overflows or negative

transitions at T2EX if EXEN2 = 1. When either RCLK = 1 or TCLK = 1, this bit is ignored

and the timer is forced to reload upon overflow.

RCLK

TCLK

CP/RL2

TR2

MODE

0

0

0

1

16-bit automatic reload

0

0

1

1

16-bit capture

1

1

X

1

baud rate generator

X

X

X

0

off

1998 Apr 07

22

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

10.2.2

C

APTURE MODE

In the capture mode (see Fig.11) there are two options

which are selected by bit EXEN2 in T2CON. If EXEN2 = 0,

then Timer 2 is a 16-bit timer/counter which on overflow

sets bit TF2 (Timer 2 overflow bit). TF2 can be used to

generate an interrupt. If EXEN2 = 1, Timer 2 operates as

above, with the added feature that a HIGH-to-LOW

transition at the external input T2EX causes the current

value in Timer 2 registers (TL2 and TH2) to be captured

into registers RCAP2L and RCAP2H, respectively. The

HIGH-to-LOW transition of T2EX also causes bit EXF2 in

T2CON to be set. EXF2 can be used to generate an

interrupt.

10.2.3

A

UTOMATIC RELOAD MODE

In the automatic reload mode (see Fig.12) there are two

options which are selected by bit EXEN2 in SFR T2CON.

If EXEN2 = 0, then a Timer 2 overflow sets TF2 and

causes the Timer 2 registers to be reloaded with the 16-bit

value in registers RCAP2L and RCAP2H, which are preset

by software.

If EXEN2 = 1, Timer 2 operates as above, with the added

feature that a HIGH-to-LOW transition at the external input

T2EX triggers the 16-bit reload and sets EXF2.

10.2.4

B

AUD RATE GENERATOR MODE

The baud rate generator mode (see Fig.13) is selected by

RCLK = 1 and/or TCLK = 1 in SFR T2CON. Overflows of

either Timer 2 or Timer 1 can be used independently for

generating baud rates for transmit and receive.

The baud rate generation by Timer 1 and/or Timer 2 is

used for the Serial Port in Mode 1 and Mode 3. The baud

rate generation mode is similar to the automatic reload

mode, in that a roll-over in TH2 causes the Timer 2

registers to be reloaded with the 16-bit value in registers

RCAP2L and RCAP2H, which are preset by software.

The baud rates for the Serial Port in Modes 1 and 3 are

determined by Timer 2 overflow rate as follows:

Timer 2 can be configured for either `timer' or `counter'

operation. Normally, as a timer it would increment every

machine cycle (thus at

1

/

12

f

clk

). As a baud rate generator,

however it increments every state time (thus at

1

/

2

f

clk

).

The baud rate is given by the formula:

In this mode an overflow of Timer 2 does not set TF2.

If EXEN2 = 1, a HIGH-to-LOW transition at pin T2EX sets

EXF2 and can be used to generate an interrupt.

Baud rate

Timer 2 overflow rate

16

--------------------------------------------------------

=

Baud rate

f

clk

32

65536

RCAP2H, RCAP2L

(

)

≠

[

]

◊

----------------------------------------------------------------------------------------------------

=

Fig.11 Timer 2 in capture mode.

handbook, full pagewidth

MLA608

TL2

(8 BITS)

TR2

control

TH2

(8 BITS)

RCAP2L

RCAP2H

EXF2

TF2

Timer 2

interrupt

EXEN2

control

C/T2 = 1

T2 PIN

12

OSC

transition

detector

T2EX PIN

C/T2 = 0

capture

1998 Apr 07

23

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.12 Timer 2 in automatic reload mode.

handbook, full pagewidth

MLA609

TL2

(8 BITS)

TR2

control

TH2

(8 BITS)

RCAP2L

RCAP2H

EXF2

TF2

Timer 2

interrupt

EXEN2

control

C/T2 = 0

C/T2 = 1

T2 PIN

12

OSC

transition

detector

T2EX PIN

reload

Fig.13 Timer 2 in baud rate generator mode.

handbook, full pagewidth

MGK192

TL2

(8 BITS)

TR2

control

TH2

(8 BITS)

RCAP2L

RCAP2H

EXF2

EXEN2

control

C/T2 = 0

C/T2 = 1

T2 pin

˜

2

˜

2

OSC

transition

detector

T2EX pin

timer 2

interrupt

(note: oscillator frequency

is divided by 2 not by 12)

RCLK

reload

RX clock

SMOD

1

0

1

0

timer 1

overflow

˜

16

TCLK

TX clock

1

0

˜

16

1998 Apr 07

24

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

10.3

Watchdog Timer (T3)

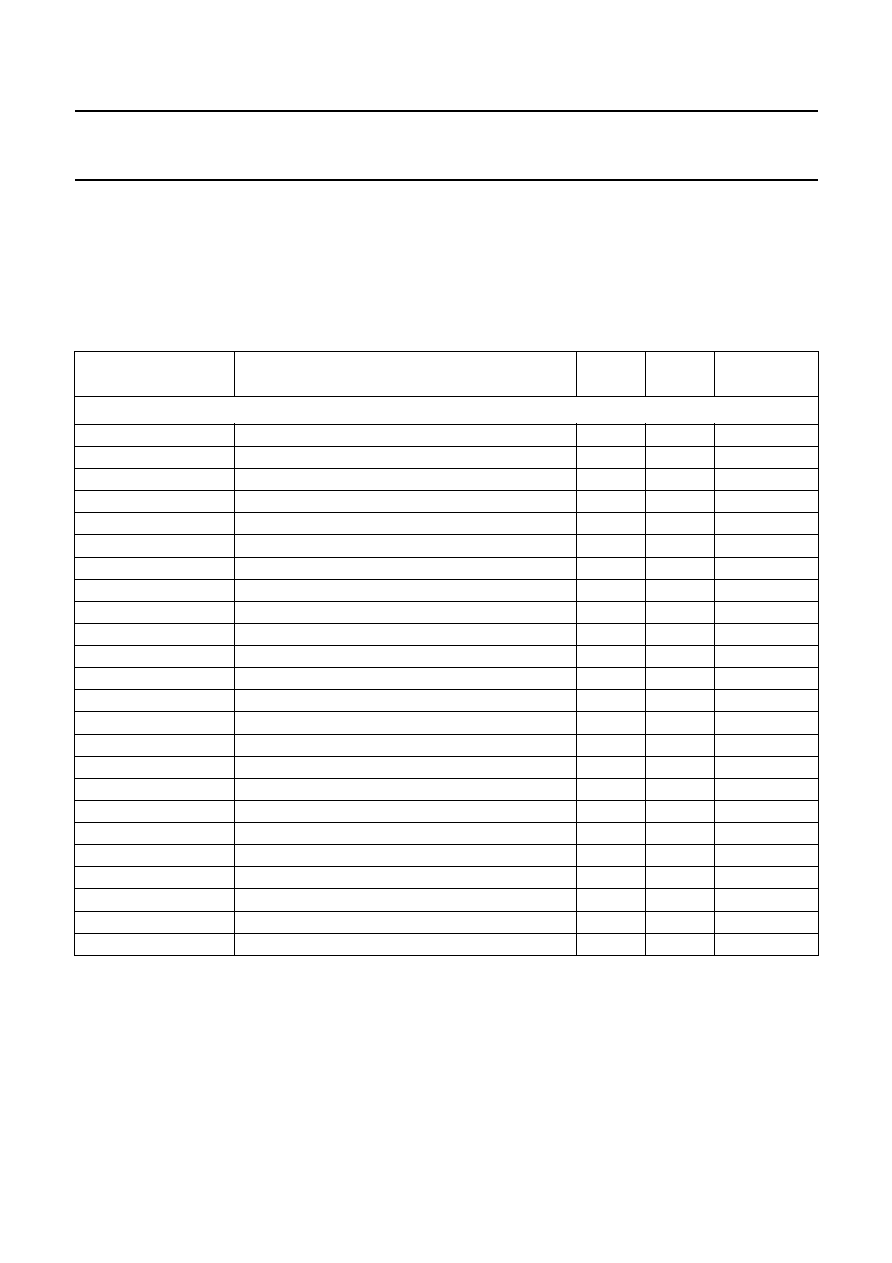

The Watchdog Timer (see Fig.14), consists of an 11-bit

prescaler and an 8-bit timer formed by SFR T3. The timer

is incremented every 1.5 ms, which is derived from the

system clock frequency of 16 MHz by the following

formula:

The 8-bit timer increments every 12

◊

2048 cycles of the

on-chip oscillator. When a timer overflow occurs, the

microcontroller is reset. The internal reset signal is not

inhibited when the external RST pin is kept LOW, e.g. by

an external reset circuit. The reset signal drives Ports 1, 2,

3, 4 and 5 outputs into the HIGH state and Port 0 into

high-impedance, no matter whether the clock oscillator is

running or not.

To prevent a system reset the timer must be reloaded in

time by the application software. If the processor suffers a

hardware/software malfunction, the software will fail to

reload the timer. This failure will result in a reset upon

overflow thus preventing the processor running out of

control.

f

timer

f

clk

12

2048

◊

(

)

---------------------------------

=

This time interval is determined by the 8-bit reload value

that is written into register T3:

The Watchdog Timer can only be reloaded if the condition

flag WLE (PCON.4) has been previously set HIGH by

software. At the moment the counter is loaded WLE is

automatically cleared.

In the Idle mode the Watchdog Timer and reset circuitry

remain active.

The Watchdog Timer is controlled by the Watchdog enable

signal EW (EBTCON.1). A HIGH level enables the

Watchdog Timer and disables the Power-down mode.

A LOW level disables the Watchdog Timer and enables

the Power-down mode.

Watchdog time interval

T3

[

]

12

◊

2048

◊

f

clk

----------------------------------------------

=

Fig.14 Watchdog Timer block diagram.

handbook, full pagewidth

MBH081

INTERNAL BUS

1/12 fclk

write

T3

PRESCALER

11-BIT

TIMER T3 (8-BIT)

LOAD

CLEAR

to reset circuitry

LOADEN

EW

LOADEN

PCON.4

PCON.1

CLEAR

WLE

PD

INTERNAL BUS

(1)

(1) See Fig.21.

1998 Apr 07

25

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

11 I/O FACILITIES

The P89C738 has 4 and P89C739 has 6 8-bit ports.

Ports 0 to 3 are the same as in the 80C51, with the

exception of the additional function of Port 1. Port lines

P1.0 and P1.1 may be used as inputs for Timer 2, P1.1

may also be used as an additional (third) external interrupt

request input.

Ports 0, 1, 2, and 3 perform the following alternative

functions:

Port 0 Provides the multiplexed low-order address and

data bus used for expanding the P89C738 with

standard memories and peripherals.

Port 1 Pins can be configured individually to provide:

external interrupt request input (external

interrupt 2); external inputs for Timer/counter 2.

Port 2 Provides the high-order address bus when

expanding the P89C738 with external program

memory and/or external data memory.

Port 3 Pins can be configured individually to provide:

external interrupt request inputs (external

interrupt 0/1); external inputs for Timer/counter 0

and Timer/counter 1; Serial Port receiver input and

transmitter output control signals to read and write

external data memory.

Bits which are not used for the alternative functions may be

used as normal bidirectional I/O pins. The generation or

use of a Port 1 or Port 3 pin as an alternative function is

carried out automatically by the P89C738 provided the

associated SFR bit is HIGH. Otherwise the port pin is held

at a logical LOW level.

Fig.15 I/O buffers in the P89C738; P89C739 (Ports 1, 2, 3, 4 and 5).

handbook, full pagewidth

MGG025

p1

p2

p3

input data

read port pin

2 oscillator

periods

n

strong pull-up

I/O PIN

VDD

I1

Q

from port latch

INPUT

BUFFER

1998 Apr 07

26

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

12 FULL DUPLEX SERIAL PORT (UART)

The serial port is functionally similar to the implementation

in the 8052AH, with the possibility of two different baud

rates for receive and transmit with Timer 1 and Timer 2 as

baud rate generators. It is full duplex, meaning it can

receive and transmit simultaneously. It is also

receive-buffered, meaning it can commence reception of a

second byte before a previously received byte has been

read from the receive register. However, if the first byte still

has not been read by the time the reception of the second

byte is complete, one of the bytes will be lost. The Serial

Port receive and transmit registers are both accessed as

SFR SBUF. Writing to SBUF loads the transmit register,

and reading SBUF accesses the physically separate

receive register.

12.1

The Serial Port operating modes

The serial port can operate in one of 4 modes:

Mode 0 Serial data enters and exits through RXD.

TXD outputs the shift clock. Eight bits are

transmitted/received (LSB first). The baud rate is

fixed at

1

/

12

f

clk

.

Mode 1 10 bits are transmitted (through TXD) or received

(through RXD): a start bit (logic 0), 8 data bits

(LSB first), and a stop bit (logic 1). On receive,

the stop bit goes into RB8 in SFR SCON.

The baud rate is variable.

Mode 2 11 bits are transmitted (through TXD) or received

(through RXD): start bit (logic 0), 8 data bits (LSB

first), a programmable 9th data bit, and a stop bit

(logic 1). On transmit, the 9th data bit (TB8 in

SFR SCON) can be assigned the value of a

logic 0 or logic 1. For example, the parity bit (P in

the PSW) could be moved into TB8. On receive,

the 9th data bit goes into RB8 in SFR SCON,

while the stop bit is ignored. The baud rate is

programmable to either

1

/

32

or

1

/

64

f

clk

.

Mode 3 11 bits are transmitted (through TXD) or received

(through RXD): a start bit (logic 0), 8 data bits

(LSB first), a programmable 9th data bit and a

stop bit (logic 1). In fact, Mode 3 is the same as

Mode 2 in all respects except the baud rate.

The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any

instruction that uses SFR SBUF as a destination register.

In Mode 0, reception is initiated by the condition RI = 0 and

REN = 1. Reception is initiated by incoming start bit if

REN = 1 in the other modes.

1998 Apr 07

27

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

12.2

Serial Port Control Register (SCON)

Table 17 Serial Port Control Register (SFR address 98H)

Table 18 Description of SCON bits

Table 19 Selection of the Serial Port modes

7

6

5

4

3

2

1

0

SMO

SM1

SM2

REN

TB8

RB8

TI

RI

BIT

SYMBOL

DESCRIPTION

7

SM0

These bits are used to select the Serial Port mode; see Table 19.

6

SM1

5

SM2

Enables the multiprocessor communication feature in Modes 2 and 3. In these

modes, if SM2 = 1, then RI will not be activated if the received 9th data bit (RB8) is a

logic 0. In Mode 1, if SM2 = 1, then RI will not be activated unless a valid stop bit was

received. In Mode 0, SM2 should be a logic 0.

4

REN

Enables serial reception. Set and cleared by software as required.

3

TB8

The 9th data bit that will be transmitted in Modes 2 and 3. Set or cleared by software

as required.

2

RB8

In Modes 2 and 3, RB8 is the 9th data bit received. In Mode 1, if SM2 = 0 then RB8 is

the stop bit that was received. In Mode 0, RB8 is not used.

1

TI

Transmit Interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at

the beginning of the stop bit time in the other modes, in any serial transmission. TI must

be cleared by software.

0

RI

Receive Interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or

halfway through the stop bit time in the other modes, in any serial transmission (except:

see SM2). RI must be cleared by software.

SMO

SM1

MODE

DESCRIPTION

BAUD RATE

0

0

Mode 0

shift register

1

/

12

f

clk

0

1

Mode 1

8-bit UART

variable

1

0

Mode 2

9-bit UART

1

/

32

or

1

/

64

f

clk

1

1

Mode 3

9-bit UART

variable

1998 Apr 07

28

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

13 REDUCED POWER MODES

Two software selectable modes of reduced power

consumption are implemented: Idle and Power-down

mode.

Idle mode operation permits the interrupt, serial ports and

timer blocks to function while the CPU is halted. The

following functions remain active during Idle mode:

∑

Timer 0, Timer 1, Timer 2, Watchdog Timer

∑

UART

∑

External interrupt.

These functions may generate an interrupt or reset and

thus end the Idle mode.

The Power-down mode operation freezes the oscillator.

and can only be activated by setting the PD bit in the SFR

PCON (see Fig.17).

13.1

Idle mode

The instruction that sets IDL (PCON.0) is the last

instruction executed in the normal operating mode before

Idle mode is activated. Once in the Idle mode, the CPU

status is preserved in its entirety: the Stack Pointer,

Program Counter, Program Status Word, Accumulator,

RAM and all other registers maintain their data during Idle

mode. The status of external pins during Idle mode is

shown in Table 20.

There are three ways to terminate the Idle mode:

∑

Activation of any enabled interrupt will cause IDL

(PCON.0) to be cleared by hardware terminating Idle

mode. The interrupt is serviced, and following return

from interrupt instruction RETI, the next instruction to be

executed will be the one which follows the instruction

that wrote a logic 1 to PCON.0.

The flag bits GF0 (PCON.2) and GF1 (PCON.3) may be

used to determine whether the interrupt was received

during normal execution or during the Idle mode.

For example, the instruction that writes to PCON.0 can

also set or clear one or both flag bits. When Idle mode is

terminated by an interrupt, the service routine can

examine the status of the flag bits.

∑

The second way of terminating the Idle mode is with an

external hardware reset. Since the oscillator is still

running, the hardware reset is required to be active for

two machine cycles (24 oscillator periods) to complete

the reset operation.

∑

The third way of terminating the Idle mode is by internal

watchdog reset.

13.2

Power-down mode

The instruction that sets PD (PCON.1) is the last executed

prior to going into the Power-down mode. The oscillator is

stopped. Note that the Power-down mode also can be

entered when the watchdog has been disabled.

The Power-down mode can be terminated by an external

reset in the same way as in the 80C51 or in addition by any

one of the two external interrupts, IE0 or IE1

(see Section 9.1).

The status of the external pins during Power-down mode

is shown in Table 20. If the Power-down mode is activated

while in external program memory, the port data that is

held in the SFR P2 is restored to Port 2. If the data is a

logic 1, the port pin is held HIGH during the Power-down

mode by the strong pull-up transistor `p1' (see Fig.15).

13.3

Wake-up from Power-down mode

The Power-down mode of the P89C738 can also be

terminated by any one of the two external interrupts, IE0 or

IE1. A termination with an external interrupt does not affect

the internal data memory and does not affect the Special

Function Registers (SFRs). This gives the possibility to

exit Power-down without changing the port output levels.

To terminate the Power-down mode with an external

interrupt, IE0 or IE1 must be switched to be level-sensitive

and must be enabled. The external interrupt input signal

INT0 and INT1 must be kept LOW until the oscillator has

restarted and stabilized (see Fig.16).

In order to prevent any interrupt priority problems during

wake-up, the priority of the desired wake-up interrupt

should be higher than the priorities of all other enabled

interrupt sources. The instruction following the one that put

the device into the Power-down mode will be the first one

which will be executed after an interrupt has been

serviced.

1998 Apr 07

29

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

Fig.16 Wake-up by external interrupt input.

handbook, full pagewidth

MGK195

oscillator start_up

>

10 ms

interrupts are polled

Idle mode

LCALL

interrupt routine

Power

-

down mode

internal timing stopped

XTAL1, 2 oscillator stopped

C1

INT0

INT1

C1

C1

C2

INT0: 2 cycles

INT1: 1 cycle

set external interrupt latch

>

560 ms

32 kHz oscillator stopped

>

10 ms

32 kHz oscillator running

Fig.17 Internal Idle and Power-down clock configuration.

handbook, full pagewidth

OSCILLATOR

CLOCK

GENERATOR

interrupts,

serial port,

timer blocks

CPU

IDL

PD

XTAL1

XTAL2

MGK194

1998 Apr 07

30

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

13.4

Status of external pins

Table 20 Status of the external pins during Idle and Power-down modes

13.5

Power Control Register (PCON)

Special modes are activated by software via the SFR PCON. PCON is not bit addressable. The reset value of PCON is

00H.

Table 21 Power Control Register (SFR address 87H)

Table 22 Description of PCON bits

Note

1. If logic 1s are written to PD and IDL at the same time, PD takes precedence.

MODE

MEMORY

ALE

PSEN

PORT 0

PORT 1

PORT 2

PORT 3

PORT 4

PORT 5

Idle

internal

HIGH

HIGH

port data

port data

port data

port data

port data

port data

external

HIGH

HIGH

floating

port data

address

port data

port data

port data

Power-down

internal

LOW

LOW

port data

port data

port data

port data

port data

port data

external

LOW

LOW

floating

port data

port data

port data

port data

port data

7

6

5

4

3

2

1

0

SMOD

ARE

RFI

WLE

GF1

GF0

PD

IDL

BIT

SYMBOL

DESCRIPTION

7

SMOD

Double baud rate bit. When set to a logic 1 the baud rate is doubled when Timer 1 is

used to generate baud rate, and the Serial Port is used in Modes 1, 2 or 3.

6

ARE

AUX-RAM enable bit. When set to a logic 1 the AUX-RAM is disabled, so that all

MOVX-instructions access the external data memory.

5

RFI

Reduced Radio Frequency Interference bit. When set to a logic 1 the toggling of the

ALE pin is prohibited. This bit is cleared on reset. See also Chapters 1 "Features": on

EMC and 6 "Pinning information": note 2.

4

WLE

Watchdog Load Enable. This flag must be set by software prior to loading the

Watchdog Timer (T3). It is cleared when timer T3 is loaded.

3

GF1

General-purpose flag bit.

2

GF0

1

PD

(1)

Power-down select. Setting this bit activates the Power-down mode.

0

IDL

(1)

Idle mode select. Setting this bit activates the Idle mode.

1998 Apr 07

31

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

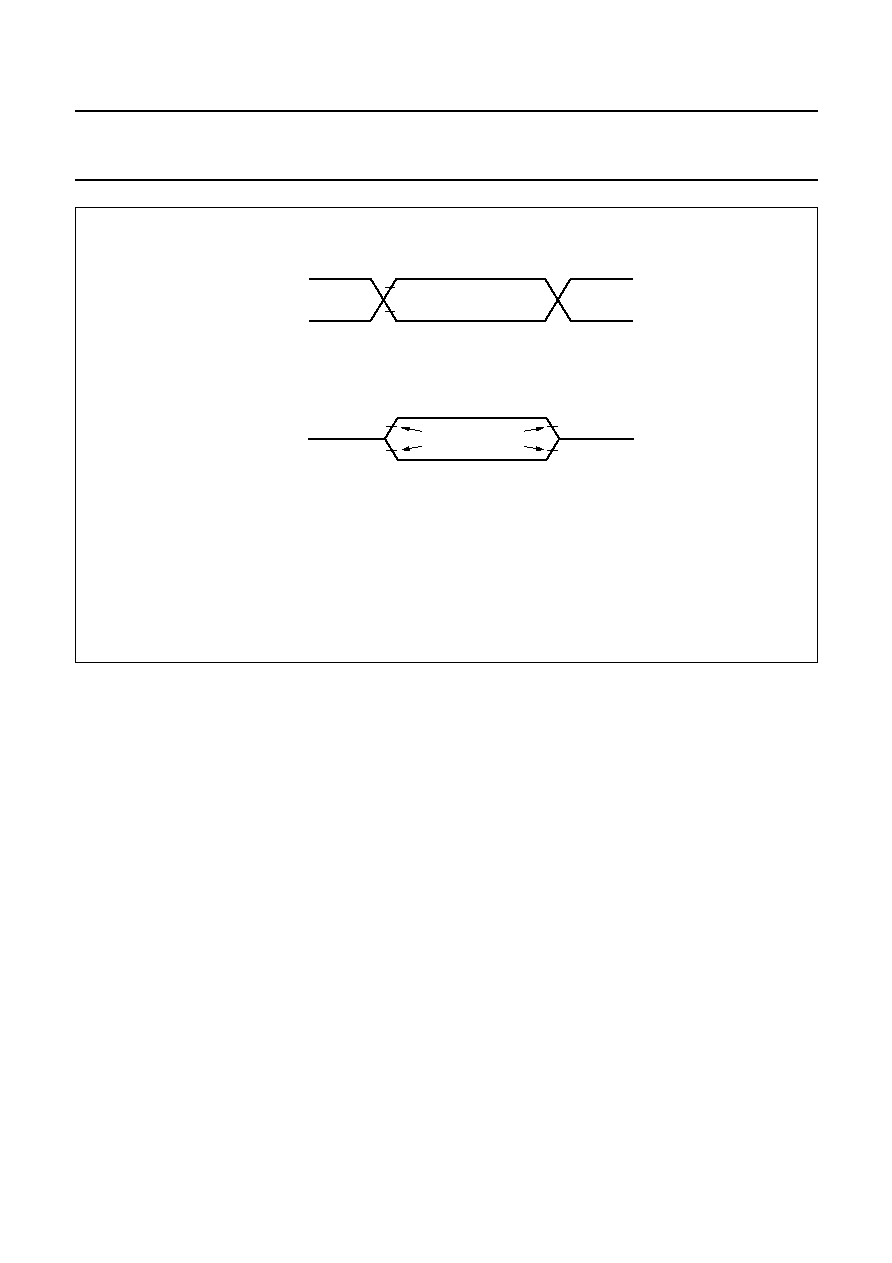

14 OSCILLATOR CIRCUIT

The oscillator circuit of the P89C738 is a single-stage

inverting amplifier in a Pierce oscillator configuration.

The circuitry between the XTAL 1 and XTAL 2 is basically

an inverter biased to the transfer point. Either a crystal or

ceramic resonator can be used as the feedback element to

complete the oscillator circuitry (see Fig.19).

Both are operated in parallel resonance. XTAL 1 is the

high gain amplifier input, and XTAL 2 is the output (see

Fig.18).

To drive the P89C738 externally, XTAL 1 is driven from an

external source and XTAL 2 left open-circuit (see Fig.20).

Fig.18 P89C738/P89C739 oscillator internal circuit.

handbook, full pagewidth

MGK196

400

XTAL1

XTAL2

Q1

Q3

Q4

to internal

timing circuits

D1

D2

Q2

PO

VSS

VDD

R1

Fig.19 P89C738/P89C739 oscillator circuit

with crystal/ceramic resonator.

handbook, halfpage

C1

20 pF

C2

MBK775

20 pF

XTAL1

XTAL2

Fig.20 Driving the P89C738/P89C739 from an

external source.

handbook, halfpage

MGK197

CMOS gate

external

oscillator

signal

XTAL1

VSS

XTAL2

NC

1998 Apr 07

32

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

15 RESET

The reset circuitry for the P89C738 is connected to the

reset pin RST. A Schmitt trigger is used at the input for

noise rejection. The output of the Schmitt trigger is

sampled by the reset circuitry every machine cycle.

A reset is accomplished by holding the RST pin HIGH for

at least two machine cycles (24 oscillator periods).

The CPU responds by executing an internal reset. During

reset ALE and PSEN output are at a HIGH level. In order

to perform a correct reset, this level must not be affected

by external elements.

In the P89C738 the internal reset can also be activated by

the Watchdog Timer (T3). If the Watchdog Timer is also

used to reset external devices, the usual capacitor

arrangement should not be connected to RST pin. Instead,

an extra circuit should be used to perform the power-on

reset operation. It should be remembered that a timer T3

overflow, if enabled, will force a reset condition to the

P89C738 by an internal connection, whether the output

RST is tied to LOW or not (see Fig.21).

The internal reset is executed during the second cycle in

which RST is pulled HIGH and is repeated every cycle until

RST goes LOW. It leaves the internal registers as shown

in Chapter 17.

15.1

Power-on reset

Figure 21 shows the on-chip reset configuration.

When V

DD

is turned on, and provided its rise time does not

exceed 10 ms, an automatic reset can be obtained by

connecting the RST pin to V

DD

via a 2.2

µ

F capacitor.

When the power is switched on, the voltage on the RST pin

is equal to V

DD

minus the capacitor voltage, and

decreases from V

DD

as the capacitor charges through the

internal resistor (R

RST

) to ground. The larger the capacitor,

the more slowly V

RST

decreases. V

RST

must remain above

the lower threshold of the Schmitt trigger long enough to

effect a complete reset. The time required is the oscillator

start-up time, plus 2 machine cycles.

Fig.21 On-chip reset configuration.

handbook, full pagewidth

MGK198

SCHMITT

TRIGGER

RESET

CIRCUITRY

RRST

overflow timer T3

RSTOUT

8 k

+

10

µ

F

VDD

on-chip circuit

RST

POC

GND

1998 Apr 07

33

Philips Semiconductors

Product specification

8-bit Flash microcontrollers

P89C738; P89C739

16 MULTIPLE PROGRAMMING ROM (MTP-ROM)

16.1

Features

∑

64 kbytes electrically erasable internal program memory

∑

Up to 64 kbytes external program memory if the internal

program memory is switched off (EA = 0)

∑

Programming and erasing voltage 12 V

±

5%

∑

Command register architecture

≠ Byte Programming (10

µ

s typical)

≠ Auto chip erase: 5 seconds (typical; including

pre-programming time)

∑

Auto-erase and auto-program

≠ DATA polling

≠ Toggle bit

∑

Minimum 100 erase/program cycles

∑

Advanced CMOS MTP memory technology.

16.2

General description

The P89C738's MTP memories augment EPROM

functionality with in-circuit electrical erasure and

programming. The P89C738 uses a command register to

manage this functionality.

P89C738's MTP reliably stores memory contents even

after 100 erase and program cycles. The cell is designed

to optimize the erase and programming mechanisms. In

addition, the combination of advanced tunnel oxide

processing and low internal electric fields for erase and

programming operations produces reliable cycling.

The P89C738 uses a V

PP

= 12.0 V

±

5% supply to perform

the auto-erase and auto-program algorithms.

16.3

Automatic programming and Automatic chip

erase

The P89C738 is byte programmable using the Automatic

programming algorithm. The Automatic programming

algorithm does not require the system to time out or verify

the data programmed. At typical room temperature the

chip programming time of the P89C738 is less than

5 seconds.

The device may be erased using the Automatic erase

algorithm. The Automatic erase algorithm automatically

programs the entire array prior to electrical erase.

The timing and verification of the electrical erase are