| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: TZA1032UK | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- CONTENTS

- 1 FEATURES

- 2 GENERAL DESCRIPTION

- 3 ORDERING INFORMATION

- 4 QUICK REFERENCE DATA

- 5 BLOCK DIAGRAM

- 6 PINNING

- 7 FUNCTIONAL DESCRIPTION

- 7.1 The I

- 7.2 Interrupt request

- 7.3 Soft reset and power-down

- 7.4 The Phase Locked Loop

- 7.5 The differential receiver

- 7.6 The RLC decoder

- 7.7 Write strategy generator

- 7.8 Laser Power Control

- 8 FUNCTIONAL DIAGRAM

- 9 CHARACTERISTICS

- 10 APPLICATION INFORMATION

- 11 BONDING PAD LOCATIONS

- 12 DATA SHEET STATUS

- 13 DEFINITIONS

- 14 DISCLAIMERS

- 15 PURCHASE OF PHILIPS I

DATA SHEET

Preliminary specification

2002 May 06

INTEGRATED CIRCUITS

TZA1032

Laser driver and controller circuit

2002 May 06

2

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

CONTENTS

1

FEATURES

2

GENERAL DESCRIPTION

3

ORDERING INFORMATION

4

QUICK REFERENCE DATA

5

BLOCK DIAGRAM

6

PINNING

7

FUNCTIONAL DESCRIPTION

7.1

The I

2

C-bus interface

7.2

Interrupt request

7.3

Soft reset and power-down

7.4

The Phase Locked Loop

7.5

The differential receiver

7.6

The RLC decoder

7.7

Write strategy generator

7.8

Laser Power Control

8

FUNCTIONAL DIAGRAM

9

CHARACTERISTICS

10

APPLICATION INFORMATION

11

BONDING PAD LOCATIONS

12

DATA SHEET STATUS

13

DEFINITIONS

14

DISCLAIMERS

15

PURCHASE OF PHILIPS I

2

C COMPONENTS

2002 May 06

3

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

1

FEATURES

∑

Separate 3.3 V digital, analog and output driver power

supplies

∑

Selective power-down of internal functions via I

2

C-bus

for power saving

∑

Low voltage-swing of the differential Run Length Limited

Code (RLC) inputs for high speed transmission and

good electromagnetic compatibility

∑

High-impedance input switching to control two or more

TZA1032 ICs in parallel for double writer applications

∑

Supports I

2

C-bus interface up to 400 kbits/s with block

transfer feature in slave mode only

∑

3.3 and 5 V tolerant input logic

∑

Supports any RLC code with run lengths from 1 to 15

∑

Automatic write-read switching for run lengths

16

∑

Channel decoding rate up to 105 Mbits/s, according to

DVD 4

◊

∑

Look back function to enable write pre-compensation by

data dependent write strategy with a land-pit

compensation up to five

∑

Supports Forced Erase (FE) mode for quick initialisation

of disc

∑

Fixed propagation delay within RLC clock periods to

allow accurate data linking on disc

∑

Supports CD-R, CD-RW, DVD+RW, DVD-R, DVD-RW

and DVR formats or any comparable existing or future

format

∑

Programmable write strategy via I

2

C-bus; completely

flexible up to a maximum of two output level transitions

per RLC clock period

∑

Pulse timing resolution of 2 ns at 500 MHz internal clock

∑

Minimum pulse width of 4 ns at 500 MHz internal clock

∑

Four programmable threshold current levels with an

8-bit resolution, and eight programmable delta levels

with an 8-bit resolution

∑

Independent laser threshold and laser delta current

control

∑

Programmable modulation unit

∑

Pointer memory mapping to allow compact write

strategy coding

∑

PLL oscillator features a self-learning oscillator mode for

non-locked operation during read

∑

Wide frequency range: PLL locking factor

2.5

∑

Two output channels, delta and threshold current levels,

each capable of delivering 240 mA delta and 200 mA

threshold peak current to the output

∑

Rise and fall times of 1 to 2 ns, depending on package

and laser

∑

Typical output resistance of 120

∑

Programmable current step size for a threshold level of

0 to 1 mA at a 16-bit resolution, and a delta level of

0 to 1.2 mA at an 8-bit resolution

∑

Internal modulator up to 565 MHz

∑

Forward Sense (FS) Laser Power Control (LPC) loop to

compensate laser drift due to temperature and aging

∑

Internal set point generation to allow read-write

switching without any transient effects

∑

Digital LPC algorithm based on FS feedback

∑

Single forward sense diode connection

∑

Programmable FS input current gain to allow for spread

in FS efficiency

∑

Supports running Optimum Power Control (OPC) loop,

so called alpha loop, to monitor and control the quality of

writing

∑

Programmable loop bandwidths: up to 1 kHz for the

LPC, and up to 50 kHz for the alpha loop

∑

Programmable minimum and maximum limiting of laser

currents and running OPC range

∑

Programmable OPC stepper.

2

GENERAL DESCRIPTION

The TZA1032 is a laser driver circuit which is intended for

a wide range of recordable and re-writable optical drives.

Figure 3 shows a function diagram of TZA1032 in relation

to a disc recording system. The TZA1032 is intended to be

located close to the laser diode on the Optical Pick-up

Unit (OPU). It can be used in CD-R/RW systems

with 1

◊

, 2

◊

, 4

◊

, 8

◊

, 12

◊

, 16

◊

and 24

◊

(24

◊

is not

guaranteed yet: evaluation pending) speed and in

DVD-R/RW systems with 1

◊

, 2

◊

and 4

◊

speed (4

◊

is not

guaranteed yet). Furthermore, it is suitable for future

standards like DVR.

2002 May 06

4

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

The TZA1032 fulfils three main functions:

∑

Drives the laser with a sequence of programmable write

strategy pulses with high timing accuracy and high peak

current levels

∑

Encodes the input modulated data to a sequence of

write strategy pulses. This encoding is flexible with

respect to input modulation code (EFM, EFMplus,

17 pp, etc.). Any RLC with run lengths in the range from

1 to 15 is possible. The write strategy is programmable

with high flexibility for CD-R/RW, DVD-R/RW, DVR or

other optical recording systems using comparable write

strategies. For this purpose the TZA1032 includes two

Random Access Memories (RAMs) which can be

loaded (non real-time) via an I

2

C-bus from a PC or

microcontroller

∑

Controls the exact light power levels coming from the

laser and controls the exact power absorbed by the disc

during recording. This is not trivial since the laser

characteristics (both threshold and gain) are strongly

temperature dependent. A first control loop controls the

laser power levels based on the signal from a forward

sense diode (FS control). This will make the laser

virtually temperature and aging independent. The loop is

fully self-contained, only an external forward sense

diode must be connected. A second control loop

controls the laser power based on an alpha signal,

generated by additional electronics based on signals

from the diode during writing. It is primarily intended to

compensate for writing performance variations due to

imperfections in the optical path and/or disc (e.g. finger

prints). The alpha signal is a measure of the power

absorption of the disc material during the writing process

or in general of the writing quality on the disc. For this

second loop, a method of stepping the set point under

external control is provided. The TZA1032 contains a

programmable counter that can be clocked via the

external OPC-strobe (pin OPC). This function is

typically used during OPC in order to calibrate the

optimum laser writing power.

When required, non-real time control is possible via an

interrupt feedback signal at pin IRQ.

The TZA1032 can supply the analog, digital and driver part

separately to obtain maximum performance.

The TZA1032 features three independent power supplies.

These are the analog and digital power supplies and a

local power supply for the laser driver function. The

supplies can be delivered separately to obtain maximum

output performance of the TZA1032 in environments with

large and highly dynamic current flows. The driver supply

has no accompanying ground because the laser driver

block only sources current to the laser. Ensure that all

power supply pins are connected to the appropriate

voltage rails.

For evaluation purposes only (by special request) the

TZA1032 can be delivered in a LQFP64 package.

3

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

TZA1032UK

-

bare die with solder bumps

-

2002 May 06

5

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

4

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITION

MIN.

TYP.

MAX.

UNIT

V

DD[1 to 3]

output supply voltage

3.0

3.3

3.6

V

I

OUT[1 to 3]

output current (threshold)

1

-

200

mA

output current (delta)

0

-

240

mA

R

OUT[1 to 3]

output resistance

-

120

-

t

r

, t

f

rise and fall time

depends on package

and load

-

-

1 to 2

ns

rl

min

decodable run length

1

-

15

B

LPC(

-

3dB)

-

3dB LPC bandwidth

-

1

-

kHz

B

alpha(

-

3dB)

-

3dB alpha bandwidth

-

50

-

kHz

f

mod

modulator frequency

PLL locked to

external clock

250

-

565

MHz

PLL in Current

Controlled Oscillator

(CCO) mode

240

-

440

MHz

t

W(min)

minimum pulse width

4

-

-

ns

t

res

timing resolution

2

-

-

ns

2002 May 06

6

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

5

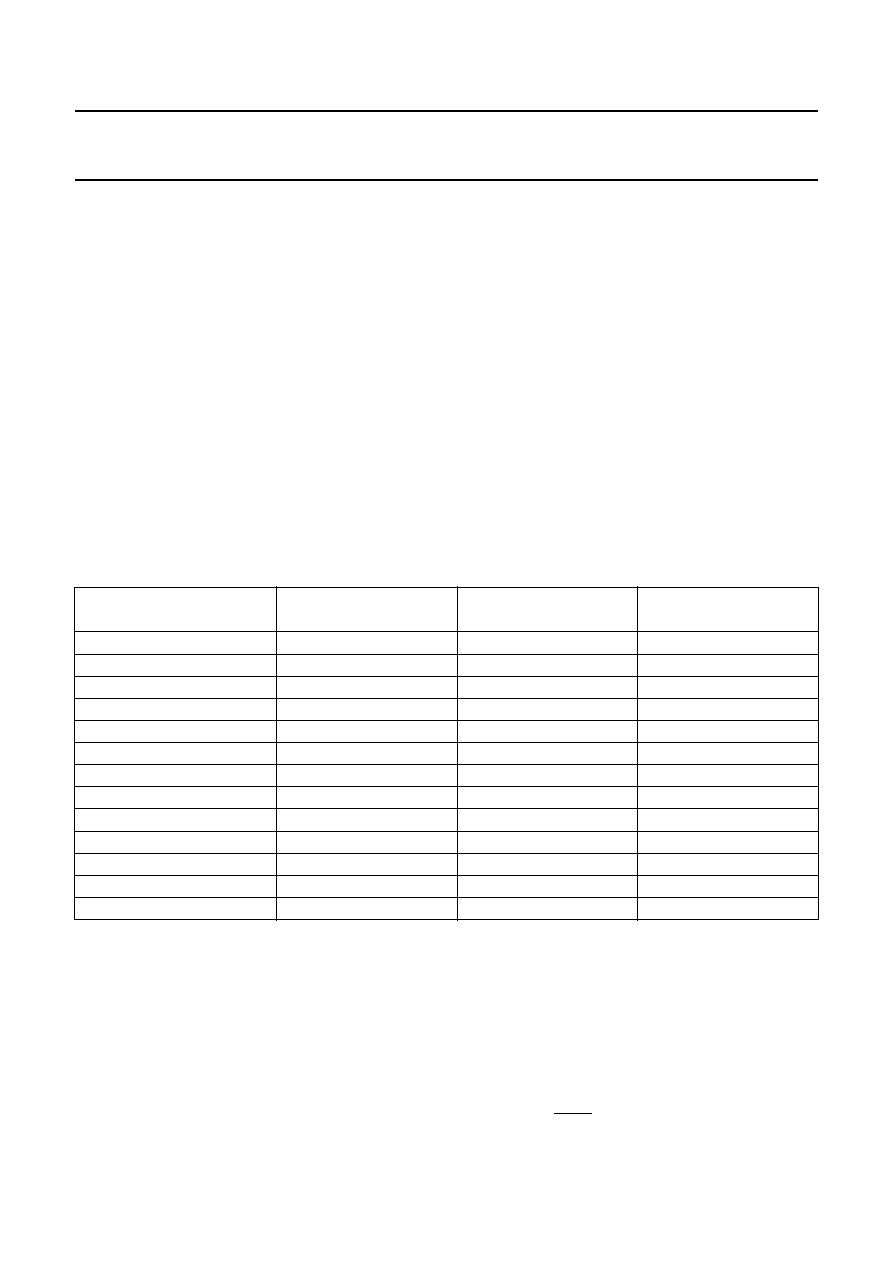

BLOCK DIAGRAM

MGW501

handbook, full pagewidth

AMEAS

RLC

DECODER

I

2

C-BUS

INTERFACE

AEZ

SAMPLE

TIMING

GENERATOR

SCL

LPC LOOP;

ALPHA LOOP

AND OPC

FS_ADC

Alpha_ADC

LasP_DAC

I_delta_DAC_ref

I_threshold_DAC_ref

P_writeSet

RDWR

P_readSet

LCD clock

LASER

CONTROL

ANALOG

FS

LASP

OPC

SDA

I2C_A0

IRQ

RLC

DIFFERENTIAL

RECEIVER

DATAP

DATAN

CLKP

CLKN

Data

delta

(8 bits)

threshold

Clk

RLC to WS

& SETPOINT

POWER

CONVERTER

REFERENCE

DACs

threshold (16 bits)

delta (8 bits)

MULTIPLYING

CURRENT

DACs

OUT[1 to 3]

RDWR

ES

to all blocks

Supply

TEST

INTERFACE

REFH

VDD

DIGITAL

POWER

VDDA VSSA

VDDD VSSD

LCA clock

Analog Ref

Analog Ref

Reference_clock

Feedback_clock

Lock_clock

Strategy_clock

Output_clock

LCD clock

REFL

ES

TEST_IN[1 to 0]

TEST[2 to 0]

TEST_CLK

TEST_OUT[1 to 0]

FSPLUS

FSMIN

IVREFCON

IVCON

POWER-ON

RESET

VSS

CFS

TZA1032UK

n.c.

4

3

ANALOG

POWER

3

3

2

2

3

3

3

8, 17,

21, 38

3, 18,

47

22, 27,

46

19, 30,

48

16

41

14

15

40

37

35

34

33

45

32

31

23

24

26

25

43

44

42

1, 2, 49

50, 51,

52

5, 6, 7

9, 10

13

11, 12

36

39

29

28

20

4

ANALOG

REFERENCE

LASER

CONTROL

DIGITAL

PLL

Fig.1 Block diagram.

2002 May 06

7

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

6

PINNING

SYMBOL

PAD

TYPE

DESCRIPTION

V

DD2

1

P

laser driver power supply

V

DD3

2

P

laser driver power supply

V

SSD3

3

P

IC digital ground

V

SS

4

P

laser driver ground

V

DDD3

8

P

IC digital power supply

IRQ

14

O

interrupt request; digital output (open drain sink). IRQ is an active LOW

interrupt service request output line to the microprocessor. This line is set

(made LOW) by internal laser driver events and is cleared (made HIGH) when

a register in the laser driver is read via I

2

C-bus.

OPC

15

I

OPC strobe; digital input with pull-down resistor. The system controller during

OPC issues the OPC (strobe) signal. This signal tells the laser driver that a

step in a set point value should be made during OPC mode.

I2C_A0

16

I

digital input pin with pull-down resistor whose function is to select which

I

2

C-bus address range applies to the IC. This allows two laser drivers to be

used in parallel on one I

2

C-bus. This pin is also used as test mode selection

pin for test mode.

V

DDD1

17

P

IC digital power supply

V

SSD1

18

P

IC digital ground

V

SSA1

19

P

IC analog ground

V

SSD4

20

P

not connected

V

DDD4

21

P

IC digital power supply

V

DDA1

22

P

IC analog power supply

CLKN

23

I

clock pulse; analog current input. The anti-phase clock signal is used together

with CLKP to allow balanced transmission.

CLKP

24

I

clock pulse; analog current input. Provides clock reference for EFMplus data

plus the clock reference for the internal PLL.

DATAP

25

I

data input; analog current input. This is the input for the run length variable

code (in non-return to zero form) from which the laser driver knows which laser

pulses to generate.

DATAN

26

I

data input; analog current input. The anti-phase data signal (CLKN) used

together with DATAN to allow balanced transmission.

V

DDA2

27

P

IC analog power supply

V

SSA2

30

P

IC analog ground

REFH

31

O

band-gap reference output (for external smoothing capacitor)

REFL

32

O

band-gap ground connection (for external smoothing capacitor)

CFS

33

O

capacitor forward sense; analog connection for external smoothing capacitor.

An external capacitor of 560 pF combined with an internal resistor of 70 k

can be used to create a RC filter for the FS input before the ADC unit in order

to prevent slew-rate effects. This capacitor is placed between this pin and

REFL.

2002 May 06

8

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

AMEAS

34

I

alpha measure; analog current sink input. AMEAS (alpha measure) is the

value of the measured disk writing quality. This is used in the alpha control

loop in order to regulate the actual laser power as a function of non-laser

system and medium drift.

LASP

35

O

laser power; analog current source output. Pin LASP indicates the laser power

level. The read power is constant and the write power level (which is added

during laser driver write mode) is alpha corrected. This signal is used in order

to normalise signals with respect to laser power.

AEZ

37

I

alpha error zero; digital input with pull-down resistor. Depending on the

programming of an internal mode bit one of two effects occurs when this input

is asserted.

alpha error zero (AEZ): the output of the alpha error adder is forced to zero.

alpha set zero (ASZ): the alpha error adder positive input (i.e. the alpha set

point) is forced to zero.

V

DDD2

38

P

IC digital power supply

SCL

40

I

digital input for I

2

C-clock (the laser driver is a slave device)

SDA

41

I/O

digital bi-directional port with open-drain sink output for I

2

C-bus data

RDWR

42

O

read-write; digital output line. This signal indicates whether the laser driver is

in read mode (HIGH) or write mode (LOW).

ES

43

O

analog output line. This signal indicates when valid signals from the

photo-detector can be expected for sampling purposes (used in CD-R

applications).

ES

44

O

analog output line. The ES anti-phase signal used together with ES to allow

balanced transmission.

FS

45

I

forward sense; analog current sink input. This is the value of the measured

laser power (e.g. measured by a photodiode which receives a set fraction of

laser output directly). This is used in the laser power control loop in order to

regulate the actual laser power to a given set of values as a function of laser

temperature drift.

V

DDA3

46

P

IC analog power supply

V

SSD2

47

P

IC digital ground

V

SSA3

48

P

IC analog ground

V

DD1

49

P

laser driver power supply

OUT1

50

O

analog current output to the laser

OUT2

51

O

analog current output to the laser

OUT3

52

O

analog current output to the laser

Laser driver IC test pads

TEST2

5

I

digital input bus for test mode control. Normal functional mode (normal

application use) is: all pins with an internal pull-down resistor and code = 0.

TEST1

6

I

digital input bus for test mode control. Normal functional mode (normal

application use) is: all pins with an internal pull-down resistor and code = 0.

TEST0

7

I

digital input bus for test mode control. Normal functional mode (normal

application use) is: all pins with an internal pull-down resistor and code = 0.

SYMBOL

PAD

TYPE

DESCRIPTION

2002 May 06

9

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

TEST_IN1

9

I

digital input bus with internal pull-down resistors for test data input.

High-impedance state in functional mode.

TEST_IN0

10

I

digital input bus with internal pull-down resistors for test data input.

High-impedance state in functional mode.

TEST_OUT1

11

O

digital output bus for test data output. High-impedance state in functional

mode.

TEST_OUT0

12

O

digital output bus for test data output. High-impedance state in functional

mode.

TEST_CLK

13

I

digital input pin with internal pull-down resistor for test data clock.

High-impedance state in functional mode.

IVCON

28

O

analog current output related to the PLL loop-filter. High-impedance state in

functional mode.

IVREFCON

29

O

analog current output related to the PLL loop-filter. High-impedance state in

functional mode.

FSPLUS

36

O

analog voltage output from LCA FS/alpha pre-amp circuit. High-impedance

state in functional mode.

FSMIN

39

O

analog voltage output from LCA FS/alpha pre-amp circuit. High-impedance

state in functional mode.

SYMBOL

PAD

TYPE

DESCRIPTION

2002 May 06

10

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

handbook, full pagewidth

TZA1032UK

MGW503

43

44

45

46

40

41

42

47

48

49

50

51

52

23

22

21

20

26

25

24

19

18

17

16

15

14

1

2

3

4

5

6

7

8

9

10 11 12 13

39 38 37 36 35 34 33 32 31 30 29 28 27

SCL

SDA

RDWR

ES

DATAP

DATAN

ES

FS

CLKP

CLKN

I2C_A0

AEZ

VDDA1

V

DDA2

VDDA3

VDDD4

V

DDD3

TEST2

TEST0

TEST_IN1

TEST_IN0

TEST_OUT0

TEST_OUT1

TEST1

TEST_CLK

V

DDD2

VDDD1

OPC

REFL

IVREFCON

IVCON

REFH

LASP

V

SS

VSSA3

VSSD2

V

SSA2

VSSA1

IRQ

V

SSD3

VSSD1

OUT1

OUT2

OUT3

V

DD3

V

DD2

VDD1

AMEAS

FSMIN

FSPLUS

CFS

Fig.2 Bare die with solder bumps (flip-chip).

Pad number 20 is not connected.

2002 May 06

11

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

7

FUNCTIONAL DESCRIPTION

7.1

The I

2

C-bus interface

The TZA1032 has two possible I

2

C-bus addresses that can be selected via pin I2C_A0, an active HIGH digital CMOS

input. This allows two TZA1032 ICs to be independently applied using the same I

2

C-bus (e.g. for double write

applications), one with pin I2C_A0 HIGH and the other with pin I2C_A0 LOW. The TZA1032 operates as a slave only

I

2

C-bus device.

Table 1

TZA1032 I

2

C-bus addresses

Each I

2

C-bus register has an 8-bit register address bus. The various modes in which an external controller can use the

I

2

C-bus interface are shown in Table 2. The special RAM Write mode allows fast block transfer of data via one single

I

2

C-bus register address.

Table 2

I

2

C-bus communication modes supported by TZA1032

7.2

Interrupt request

The IRQ is built as an active LOW open-drain output pin so it can be linked to the system controller together with similar

signals in a wired-or approach. An IRQ register is present to select the conditions which can cause the IRQ line to be

active. Possible conditions for an interrupt can be overrun or under-run of threshold or delta laser current or several other

selectable conditions.

The status register allows extra signals to be monitored in non-interrupt mode (e.g. by polling). The IRQ and status

registers in combination with the IRQ line allow a very efficient way of controlling TZA1032.

In addition, the IRQ_enable register allows selectable masking of most of the IRQ conditions to the IRQ line.

I2C_A0

I

2

C-BUS WRITE ADDRESS

I

2

C-BUS READ ADDRESS

0 = LOW

1101 1100 (DCH)

1101 1101 (DDH)

1 = HIGH

1101 1110 (DEH)

1101 1111 (DFH)

I

2

C-BUS MODE

I

2

C-BUS INFORMATION

Write

start; TZA1032_write_address; acknowledge; register_address (n); acknowledge;

data_to_register_address (n); acknowledge; stop

Incremental write

start; TZA1032_write_address; acknowledge; register_address (n); acknowledge;

data_to_register_address (n); acknowledge; data_to_register_address (n + 1);

acknowledge; .... ; data_to_register_address (n + r); acknowledge; stop

RAM write

start; TZA1032_write_address; acknowledge; register_address (= RAM x), acknowledge;

data_to_RAM x (0), acknowledge; data_to_RAM x (1), acknowledge; .... ;

data_to_RAM x (m); acknowledge; stop

Read

start; TZA1032_write_address; acknowledge; register_address (n); acknowledge; stop

start; TZA1032_read_address; acknowledge; data_from_register_address (n);

acknowledge; stop

Successive read

start; TZA1032_write_address; acknowledge; register_address (n); acknowledge; start;

TZA1032_read_address; acknowledge; data_from_register_address (n), acknowledge;

data_from_register_address (n); acknowledge; .... ; data_from_register_address (n);

acknowledge; stop

2002 May 06

12

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

7.3

Soft reset and power-down

TZA1032 has a soft reset register that can reset most of

the internal blocks, and is automatically synchronized with

the I

2

C-bus SCL input.

Most of the blocks in the TZA1032 are provided with a

power-down input. The IC features a special power-down

register which can be programmed via I

2

C-bus. An active

bit in the register causes a block to go into a low dissipation

standby mode. This offers the user the possibility to save

power when TZA1032 operates in a register mode (e.g.

during read).

7.4

The Phase Locked Loop

The PLL is phase locked to the incoming RLC clock signal.

A single external clock signal is sufficient for a complete

task of TZA1032. The PLL unit provides all internal

clocking with the exception of the I

2

C-bus interface that

can run on its own SCL clock.

The PLL can be used in closed loop or as a stable

open-loop oscillator (in read mode for example) when no

input clock is present. For this purpose the PLL features a

self-learning oscillator mode for non-locked operation.

Furthermore, the PLL is designed for wide range

frequency locking (factor

2.5). The frequency

multiplication factor is programmable for flexible selection

of write strategy timing resolution for different standards

(CD 1

◊

to 24

◊

, DVD 1

◊

, 2

◊

, 4

◊

and DVR).

For PLL characteristics see Table 3 for the possible PLL

frequencies and write strategy resolutions with respect to

the incoming RLC clock. The TZA1032 features are much

more flexible than shown in Table 3. The PLL frequency

and write strategy resolution can be programmed

according to the specific requirements of the user.

Table 3

Examples of PLL clock ratio programming

Note

1. The write strategy resolution is defined as the number of bits per RLC clock period.

7.5

The differential receiver

A differential RLC receiver (DRX) with low voltage-swing is present to allow high data rates in combination with low

electromagnetic interference. The receiver features impedance matching with typical flex foils. Furthermore, single side

operation is optionally possible by connecting additional external resistors.

High-impedance input switching allows two or more TZA1032 ICs to operate in parallel. The high-impedance input switch

is controlled by a single I

2

C-bus control register that can individually select DRX clock and/or data lines for

high-impedance mode. A high-impedance input mode is also entered during Reset or power-down.

STANDARD

RLC FREQUENCY

f

rlc

(MHz)

PLL FREQUENCY

f

o

(MHz)

WRITE STRATEGY

RESOLUTION

(1)

CD

◊

1

4.3218

518.616

8

CD

◊

2

8.6436

518.616

8

CD

◊

4

17.2872

553.1904

8

CD

◊

8

34.5744

553.1904

8

CD

◊

12

51.8616

414.8928

8

CD

◊

16

69.1488

553.1904

8

CD

◊

24

103.7232

414.8928

4

DVD

◊

1

26.16

523.2

20

DVD

◊

2

52.32

523.2

10

DVD

◊

2.5

65.4

392.4

6

DVD

◊

4

104.64

418.56

4

DVR-1

65.625

525

8

DVR-2

93.75

562.5

6

2002 May 06

13

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

Table 4

Truth table for RLC differential receiver; note 1

Note

1. X = don't care; L = LOW; H = HIGH.

7.6

The RLC decoder

The RLC decoder and write strategy generator feature a look back function to enable write pre-compensation by data

dependent write strategies. The write strategy for the current received run length (rlc

n

) depends on the previous received

run length (rlc

n

-

1

). Table 5 shows that TZA1032 is capable of decoding 64 possible combinations of rlc

n

and rlc

n

-

1

including a read state.

The read state is entered after detecting run lengths

16. The decoder automatically toggles between the status write

and erase in normal writing mode, and the RLC data inputs can be made edge sensitive only, or edge and level sensitive.

It should be noticed that erase strategies are possible. A forced erase mode can be entered via I

2

C-bus for quick disc

initialisation. The RLC decoder (and the complete TZA1032) have a fixed propagation delay of 28 RLC clock periods to

allow accurate data linking on disc.

Table 5

List of possible RLC decoder combinations; note 1

Note

1. X = don't care; E = erase; W = write.

CLOCK

INPUT

POWER-DOWN

High_Z

High_Z_clk

Reset

OUT

BIAS

INPUT SWITCH

CLKP

L

L

L

H

H

on

closed

CLKN

L

L

L

H

L

on

closed

X

H

X

X

X

H

off

open (high impedance)

X

L

H

X

X

H

on

open (high impedance)

X

L

X

H

X

H

on

open (high impedance)

X

L

X

X

H

H

on

open (high impedance)

rlc

n

rlc

n

-

1

EFFECT

rlc

n

rlc

n

-

1

EFFECT

rlc

n

rlc

n

-

1

EFFECT

rlc

n

rlc

n

-

1

EFFECT

Read

X

0

E8

X

16

W2

E3

32

W5

E1

48

E1

X

1

E9

X

17

W2

E4

33

W5

E2

49

E2

X

2

E10

X

18

W2

E5

34

W5

E3

50

E3

W3

3

E11

X

19

W2

X

35

W5

E4

51

E3

W4

4

E12

X

20

W3

E1

36

W5

E5

52

E3

W5

5

E13

X

21

W3

E2

37

W5

X

53

E3

X

6

E14

X

22

W3

E3

38

W6

X

54

E4

W3

7

E15

X

23

W3

E4

39

W7

X

55

E4

W4

8

W1

E1

24

W3

E5

40

W8

X

56

E4

W5

9

W1

E2

25

W3

X

41

W9

X

57

E4

X

10

W1

E3

26

W4

E1

42

W10

X

58

E5

W3

11

W1

E4

27

W4

E2

43

W11

X

59

E5

W4

12

W1

E5

28

W4

E3

44

W12

X

60

E5

X

13

W1

X

29

W4

E4

45

W13

X

61

E6

X

14

W2

E1

30

W4

E5

46

W14

X

62

E7

X

15

W2

E2

31

W4

X

47

W15

X

63

2002 May 06

14

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

7.7

Write strategy generator

The write strategy generator makes use of pointer memory

mapping to allow compact write strategy coding. Only

1600 bytes have to be transferred to TZA1032 to load the

most complex write strategy including write

pre-compensation. Due to the pointer memory structure

common strategies can be loaded in an even more

compact manner (e.g. CD strategies). Loading can be

done efficiently via I

2

C-bus block transfer mode.

The write strategy code includes:

∑

Data for selection of output power levels from 4

threshold and 8 delta values (these 8-bit values can be

programmed asynchronously via I

2

C-bus)

∑

Pulse timing information

∑

Modulation information.

The modulation information enables the user to switch on

modulation in pre-selected parts of the write strategy on

a real time basis. The modulation amplitude can be

programmed asynchronously via I

2

C-bus.

7.8

Laser Power Control

The Forward Sense Diode (FSD) is a reversed biased

diode that receives a small percentage of the laser output

light and converts it into a current. The FSD can be

connected directly to the TZA1032 without additional

components. The TZA1032 features a current input with

programmable gain (6-bit resolution). Furthermore a 12-bit

ADC is used.

Internal set point generation is present to allow read-write

switching without any transient effects. A digital loop filter

with programmable loop gain is used. This allows tailoring

of loop bandwidth according to the requirements of the

application. A unique laser power control algorithm is

used. This algorithm ensures not only average power

control but it really makes the laser virtual temperature and

aging independent for any possible write strategy. This

loop operates with or without the alpha (running OPC)

loop.

The TZA1032 supports a full running optimum power

control loop when required by the user. The loop is also

referred to as the alpha loop. The input signal is based on

disc Absorption MEASurements (AMEAS). This signal is

processed in a similar way as the FS input current.

A current input is provided with programmable gain (4-bit)

and an 8-bit ADC is used.

Again a digital loop filter with programmable loop gain is

used. This allows tailoring of loop bandwidth according to

the requirements of the application. The alpha loop does

not interfere with the FS laser power control loop.

Therefore, both control loops can be used simultaneously.

The set point is programmable via I

2

C-bus or is under

control of a programmable OPC stepper.

2002

May

06

15

Philips Semiconductors

Preliminar

y specification

Laser dr

iv

er and controller circuit

TZA1032

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

8

FUNCTIONAL DIA

GRAM

MGW500

u

ll pagewidth

I

2

C-BUS

INTERFACE

PLL

POR

ALPHA LOOP

TIMING &

CONTROL

LASER

POWER

SETPOINT

GENERATOR

DIGITAL

LOOP

FILTERING

LPC

DIGITAL

LOOP

FILTERING

ALPHA

PHOTO

DETECTOR

& PREAMPS

DISK

EFM(P)

DATA SOURCE

(ENCODER)

OPC,

AEZ

SCL, SDA, IRQ,

I2C_A0

Alpha MEASURE

(AMEAS)

RLC TO WS

CONVERTER

THRESHOLD

CURRENT

REFERENCE

MULTIPLYING

CURRENT DACs

Threshold

Delta

Delta_REF

RLC

DECODER

ALPHA

SETPOINT

& OPC

STEPPER

DELTA

CURRENT

REFERENCE

ALPHA

MEASURE

PROCESSING

+

+

+

+

+

+

+

-

-

+

TZA1032

FS

ES, ES, RDWR, LASP

clock and data (CLKP, CLKN, DATAP, DATAN)

OUT

laser

forward

sense

laser light

laser

light

VFS

Fig.3 Functional diagram of TZA1032 in relation to a disc recording system.

2002 May 06

16

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

9

CHARACTERISTICS

Note

1. Use low range CCO mode only.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Current driver

V

DD[1 to 3]

output supply voltage

3.0

3.3

3.6

V

I

OUT[1 to 3]

output current (threshold)

1

-

200

mA

output current (delta)

0

-

240

mA

R

OUT[1 to 3]

output resistance

-

120

-

t

r

, t

f

rise and fall times

depends on package and

load

-

-

1 to 2

ns

PLL

f

o(R)

PLL output frequency

(1)

read mode

240

375

440

MHz

f

o(W)

PLL output frequency

write mode

320

523.2

565

MHz

f

i(rlc)

PLL input frequency

0

26.16

105

MHz

FS buffer and ADC combination

V

FS

voltage at pin FS

virtual ground

1.220

1.225

1.230

V

I

FS

current at pin FS

0

1000

4000

µ

A

DC input current

code

-

2048

-

0

-

µ

A

code 2047; nominal gain

-

1000

-

µ

A

N

resolution

signed

-

12

-

bit

B

-

3dB

analog bandwidth

3.08

4.06

5.64

kHz

Reg_FS

programmable gain register 6 bits

0

-

63

Alpha buffer and ADC

I

alpha

input current

into pin AMEAS

0

100

400

µ

A

V

alpha

input voltage

virtual ground

1.3

1.4

1.5

V

N

resolution

signed

-

8

-

bit

I_alpha

DC input current

code

-

128

-

0

-

µ

A

code 127; nominal gain

-

100

-

µ

A

B

-

3dB

analog bandwidth

520

650

850

kHz

Alpha_Reg

programmable gain register 4 bits

0

-

15

DRX input

I

DRXD(HIZ)

DRX data input current

high-impedance mode

0

0

100

µ

A

I

DRXC(HIZ)

DRX clock input current

high-impedance mode

0

0

100

µ

A

V

DATA

DRX data input voltage

low-impedance mode

-

120

-

mV

V

CLK

DRX clock input voltage

low-impedance mode

-

120

-

mV

I

2

C-bus interface

R

ON(SDA)

on resistance SDA line

100

150

250

R

ON(SCL)

on resistance SCL line

100

150

250

2002 May 06

17

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

10 APPLICATION INFORMATION

A typical application diagram of the TZA1032 is shown in

Fig.4. As can be seen from this figure the CLKP, CLKN,

DATAP and DATAN inputs allow differential data transfer

for electromagnetic compatibility issues. Input series

resistors can be connected to obtain low voltage swing

when using standard 3.3 or 5 V drivers. This will further

reduce electromagnetic interference.

This application diagram shows separated 3.3 V supplies

to obtain maximum output performance. Only few

decoupling capacitors are needed for the total application.

The forward sense loop is fully self-contained. Only a

forward sense diode has to be connected, which can be

biased with an external voltage.

The TZA1032 can be mounted with `flip-chip' technology

as a bare die on the flex foils. For this purpose the bond

pads of the silicon die can be bumped with solder dots.

In this configuration parasitic components (e.g. inductors)

can be further reduced leading to even better performance

of the TZA1032.

2002

May

06

18

Philips Semiconductors

Preliminar

y specification

Laser dr

iv

er and controller circuit

TZA1032

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

handbook, full pagewidth

FSMIN

SCL

3.3

SDA

RDWR

ES

ES

FS

SCL

3.3 V

3.3 / 5 V

SDA

26

25

24

23

22

21

20

19

18

17

16

15

14

40

41

42

43

44

45

46

47

48

49

laser

(1, 2)

50

MGW504

51

52

39

38

VFS

37

36

35

34

33

32

31

30

29

28

27

1

choke

FLEX-V3

MAIN PCB

choke

C(bias)

100 nF

C(laser)

220 nF

220

µ

F

Vbias

2

3

4

5

6

7

8

TZA1032UK

(bare die)

9

10

11

12

13

FSPLUS

LASP

AMEAS

CFS

REFL

REFH

AEZ

IVREFCON

IVCON

V

DDD2

V

DDA2

V

SSA2

VSSD

VSSA

VDDA1

VDDD4

VSSD4

pad not

bumped

VSSA1

VSSD1

100 nF

560 nF

1.8 k

ALPHA-

PROCESSING

V

SS

V

SSD3

TEST0

TEST1

TEST2

V

DDD3

V

DD3

V

DD2

TEST_CLK

TEST_OUT0

TEST_OUT1

TEST_IN0

TEST_IN1

VDDD1

VDDD

VDDA3

VDD1

OUT1

OUT2

OUT3

VDDD

VFS

VDDA

VDD

VSSD2

VSSD

VSSA3

VSSA

I2C_A0

OPC

CLKN

CLKP

DATAP

DATAN

IRQ

I

2

C-bus

1.8 k

1.8 k

1.8 k

10 k

ENCODER

SYSTEM

CONTROLLER

PRE-

PROCESSOR

forward

sense

220

µ

F

100 nF

100 nF

100 nF

Fig.4 Typical application diagram for TZA1032UK on flex foil.

(1) The loop format by OUT1, OUT2 and OUT3, laser anode, laser cathode, C(laser) and V

DDD

must be kept as small as possible.

(2) The ground pad of C(bias) must be placed as close to V

SS

as possible.

2002 May 06

19

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

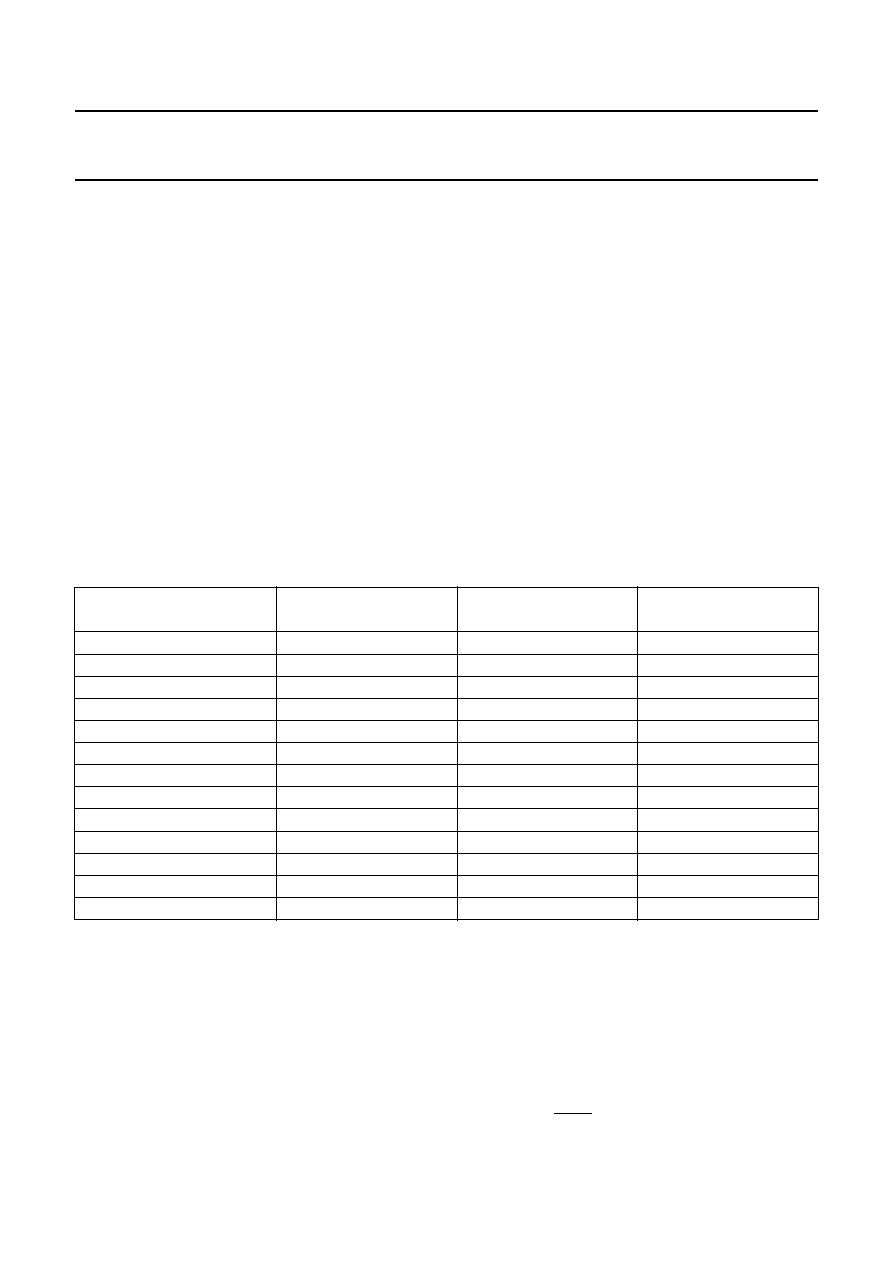

11 BONDING PAD LOCATIONS

Note

1. All x and y coordinates represent the position of the

centre of the pad in mm with respect to the centre of

the die (see Fig.5).

SYMBOL

PAD

COORDINATES

(1)

x

y

V

DD2

1

-

1.469

-

1.758

V

DD3

2

-

1.2215

-

1.758

V

SSD3

3

-

0.974

-

1.758

V

SS

4

-

0.7265

-

1.758

TEST2

5

-

0.4775

-

1.758

TEST1

6

-

0.230

-

1.758

TEST0

7

+

0.019

-

1.758

V

DDD3

8

+0.2665

-

1.758

TEST_IN1

9

+0.5155

-

1.758

TEST_IN0

10

+0.763

-

1.758

TEST_OUT1

11

+1.012

-

1.758

TEST_OUT0

12

+1.2595

-

1.758

TEST_CLK

13

+1.5085

-

1.758

IRQ

14

+1.758

-

1.469

OPC

15

+1.758

-

1.2215

I2C_A0

16

+1.758

-

0.974

V

DDD1

17

+1.758

-

0.7265

V

SSD1

18

+1.758

-

0.4775

V

SSA1

19

+1.758

-

0.230

V

SSD4

20

+1.758

+

0.019

V

DDD4

21

+1.758

+0.2665

V

DDA1

22

+1.758

+0.5155

CLKN

23

+1.758

+0.763

CLKP

24

+1.758

+1.012

DATAP

25

+1.758

+1.2595

DATAN

26

+1.758

+1.5085

V

DDA2

27

+1.5085

+1.758

IVCON

28

+1.2595

+1.758

IVREFCON

29

+1.012

+1.758

V

SSA2

30

+0.763

+1.758

REFH

31

+0.5155

+1.758

REFL

32

+0.2665

+1.758

CFS

33

+0.019

+1.758

AMEAS

34

-

0.230

+1.758

LASP

35

-

0.4775

+1.758

FSPLUS

36

-

0.7265

+1.758

AEZ

37

-

0.974

+1.758

V

DDD2

38

-

1.2215

+1.758

FSMIN

39

-

1.469

+1.758

SCL

40

-

1.758

+1.5085

SDA

41

-

1.758

+1.2595

RDWR

42

-

1.758

+1.012

ES

43

-

1.758

+0.763

ES

44

-

1.758

+0.5155

FS

45

-

1.758

+0.2665

V

DDA3

46

-

1.758

+0.019

V

SSD2

47

-

1.758

-

0.230

V

SSA3

48

-

1.758

-

0.4775

V

DD1

49

-

1.758

-

0.7265

OUT1

50

-

1.758

-

0.974

OUT2

51

-

1.758

-

1.2215

OUT3

52

-

1.758

-

1.469

SYMBOL

PAD

COORDINATES

(1)

x

y

2002 May 06

20

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

handbook, full pagewidth

TZA1032UK

MBL538

43

44

45

46

40

41

42

47

48

49

50

51

52

23

22

21

20

26

25

24

19

18

17

16

15

14

1

2

3

4

5

6

7

8

9

10 11 12 13

39 38 37 36 35 34 33 32 31 30 29 28 27

SCL

SDA

RDWR

ES

DATAP

DATAN

ES

FS

CLKP

CLKN

I2C_A0

AEZ

VDDA1

V

DDA2

VDDA3

VDDD4

n.c.

V

DDD3

TEST2

TEST0

TEST_IN1

TEST_IN0

TEST_OUT0

TEST_OUT1

TEST1

TEST_CLK

V

DDD2

VDDD1

OPC

REFL

IVREFCON

IVCON

REFH

LASP

V

SS

VSSA3

VSSD2

V

SSA2

VSSA1

IRQ

V

SSD3

VSSD1

OUT1

OUT2

OUT3

V

DD3

V

DD2

VDD1

AMEAS

FSMIN

FSPLUS

CFS

x

y

0

0

Fig.5 Bonding pad locations.

2002 May 06

21

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

12 DATA SHEET STATUS

Notes

1. Please consult the most recently issued data sheet before initiating or completing a design.

2. The product status of the device(s) described in this data sheet may have changed since this data sheet was

published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

DATA SHEET STATUS

(1)

PRODUCT

STATUS

(2)

DEFINITIONS

Objective data

Development

This data sheet contains data from the objective specification for product

development. Philips Semiconductors reserves the right to change the

specification in any manner without notice.

Preliminary data

Qualification

This data sheet contains data from the preliminary specification.

Supplementary data will be published at a later date. Philips

Semiconductors reserves the right to change the specification without

notice, in order to improve the design and supply the best possible

product.

Product data

Production

This data sheet contains data from the product specification. Philips

Semiconductors reserves the right to make changes at any time in order

to improve the design, manufacturing and supply. Changes will be

communicated according to the Customer Product/Process Change

Notification (CPCN) procedure SNW-SQ-650A.

13 DEFINITIONS

Short-form specification

The data in a short-form

specification is extracted from a full data sheet with the

same type number and title. For detailed information see

the relevant data sheet or data handbook.

Limiting values definition

Limiting values given are in

accordance with the Absolute Maximum Rating System

(IEC 60134). Stress above one or more of the limiting

values may cause permanent damage to the device.

These are stress ratings only and operation of the device

at these or at any other conditions above those given in the

Characteristics sections of the specification is not implied.

Exposure to limiting values for extended periods may

affect device reliability.

Application information

Applications that are

described herein for any of these products are for

illustrative purposes only. Philips Semiconductors make

no representation or warranty that such applications will be

suitable for the specified use without further testing or

modification.

14 DISCLAIMERS

Life support applications

These products are not

designed for use in life support appliances, devices, or

systems where malfunction of these products can

reasonably be expected to result in personal injury. Philips

Semiconductors customers using or selling these products

for use in such applications do so at their own risk and

agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes

Philips Semiconductors

reserves the right to make changes, without notice, in the

products, including circuits, standard cells, and/or

software, described or contained herein in order to

improve design and/or performance. Philips

Semiconductors assumes no responsibility or liability for

the use of any of these products, conveys no licence or title

under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that

these products are free from patent, copyright, or mask

work right infringement, unless otherwise specified.

2002 May 06

22

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

Bare die

All die are tested and are guaranteed to comply with all data sheet limits up to the point of wafer sawing for

a period of ninety (90) days from the date of Philips' delivery. If there are data sheet limits not guaranteed, these will be

separately indicated in the data sheet. There are no post packing tests performed on individual die or wafer. Philips

Semiconductors has no control of third party procedures in the sawing, handling, packing or assembly of the die.

Accordingly, Philips Semiconductors assumes no liability for device functionality or performance of the die or systems

after third party sawing, handling, packing or assembly of the die. It is the responsibility of the customer to test and qualify

their application in which the die is used.

15 PURCHASE OF PHILIPS I

2

C COMPONENTS

Purchase of Philips I

2

C components conveys a license under the Philips' I

2

C patent to use the

components in the I

2

C system provided the system conforms to the I

2

C specification defined by

Philips. This specification can be ordered using the code 9398 393 40011.

2002 May 06

23

Philips Semiconductors

Preliminary specification

Laser driver and controller circuit

TZA1032

NOTES

© Koninklijke Philips Electronics N.V. 2002

SCA74

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed

without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license

under patent- or other industrial or intellectual property rights.

Philips Semiconductors ≠ a worldwide company

Contact information

For additional information please visit http://www.semiconductors.philips.com.

Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com.

Printed in The Netherlands

753503/01/pp

24

Date of release:

2002 May 06

Document order number:

9397 750 08652