Universal Serial Bus (USB) CODEC

DATA SHEET

Preliminary specification

File under Integrated Circuits, IC01

1999 May 10

INTEGRATED CIRCUITS

UDA1325

Universal Serial Bus (USB) CODEC

1999 May 10

2

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) CODEC

UDA1325

FEATURES

General

·

High Quality USB-compliant Audio/HID device

·

Supports 12 Mbits/s serial data transmission

·

Fully USB Plug and Play operation

·

Supports `Bus-powered' and `Self-powered' operation

·

3.3 V power supply

·

Low power consumption with optional efficient power

control

·

On-chip clock oscillator, only an external crystal is

required.

Audio playback channel

·

One isochronous output endpoint

·

Supports multiple audio data formats (8, 16 and 24 bits)

·

Adaptive sample frequency support from 5 to 55 kHz

·

One master 20-bit I

2

S digital stereo playback output,

I

2

S and LSB justified serial formats

·

One slave 20-bit I

2

S digital stereo playback input,

I

2

S and LSB justified serial formats

·

Selectable volume control for left and right channel

·

Soft mute control

·

Digital bass and treble tone control

·

Selectable on-chip digital de-emphasis

·

Low total harmonic distortion (typical 90 dB)

·

High signal-to-noise ratio (typical 95 dB)

·

One stereo Line output.

Audio recording channel

·

One isochronous input endpoint

·

Supports multiple audio data formats (8, 16 and 24 bits)

·

Twelve selectable sample rates (4, 8, 16 or 32 kHz;

5.5125, 11.025, 22.05 or 44.1 kHz; 6, 12, 24 or 48 kHz)

via analog PLL (APLL).

·

Selectable sample rate between 5 to 55 kHz via a

second oscillator (optional)

·

One slave 20-bit I

2

S digital stereo recording input,

I

2

S and LSB justified serial formats

·

Programmable Gain Amplifier for left and right channel

·

Low total harmonic distortion (typical 85 dB)

·

High signal-to-noise ratio (typical 90 dB)

·

One stereo Line/Microphone input.

USB endpoints

·

2 control endpoints

·

2 interrupt endpoints

·

1 isochronous data sink endpoint

·

1 isochronous data source endpoint.

Document references

·

"USB Specification"

·

"USB Device Class Definition for Audio Devices"

·

"Device Class Definition for Human Interface Devices

(HID)"

·

"USB HID Usage Table".

·

"USB Common Class Specification".

1999 May 10

3

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) CODEC

UDA1325

APPLICATIONS

·

USB monitors

·

USB speakers

·

USB microphones

·

USB headsets

·

USB telephone/answering machines

·

USB links in consumer audio devices.

GENERAL DESCRIPTION

The UDA1325 is a single chip stereo USB codec

incorporating bitstream converters designed for

implementation in USB-compliant audio peripherals and

multimedia audio applications. It contains a USB interface,

an embedded microcontroller, an Analog-to-Digital

Interface (ADIF) and an Asynchronous Digital-to-Analog

Converter (ADAC).

The USB interface consists of an analog front-end and a

USB processor. The analog front-end transforms the

differential USB data into a digital data stream. The USB

processor buffers the incoming and outgoing data from the

analog front-end and handles all low-level USB protocols.

The USB processor selects the relevant data from the

universal serial bus, performs an extensive error detection

and separates control information and audio information.

The control information is made accessible to the

microcontroller. At playback, the audio information

becomes available at the digital I

2

S output of the digital I/O

module or is fed directly to the ADAC. At recording, the

audio information is delivered by the ADIF or by the digital

I

2

S input of the I

2

S-bus interface.

All I

2

S inputs and I

2

S outputs support standard I

2

S-bus

format and the LSB justified serial data format with word

lengths of 16, 18 and 20 bits.

Via the digital I/O module with its I

2

S input and output, an

external DSP can be used for adding extra sound

processing features for the audio playback channel.

The microcontroller is responsible for handling the

high-level USB protocols, translating the incoming control

requests and managing the user interface via general

purpose pins and an I

2

C-bus.

The ADAC enables the wide and continuous range of

playback sampling frequencies. By means of a Sample

Frequency Generator (SFG), the ADAC is able to

reconstruct the average sample frequency from the

incoming audio samples. The ADAC also performs the

playback sound processing. The ADAC consists of a

FIFO, an unique audio feature processing DSP, the SFG,

digital filters, a variable hold register, a Noise Shaper (NS)

and a Filter Stream DAC (FSDAC) with line output drivers.

The audio information is applied to the ADAC via the USB

processor or via the digital I

2

S input of the digital I/O

module.

The ADIF consists of an Programmable Gain Amplifier

(PGA), an Analog-to-Digital Converter (ADC) and a

Decimator Filter (DF). An Analog Phase Lock Loop (APLL)

or oscillator is used for creating the clock signal of the

ADIF. The clock frequency for the ADIF can be controlled

via the microcontroller. Several clock frequencies are

possible for sampling the analog input signal at different

sampling rates.

The wide dynamic range of the bitstream conversion

technique used in the UDA1325 for both the playback and

recording channel guarantees a high audio sound quality.

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME

DESCRIPTION

VERSION

UDA1325PS

SDIP42

plastic shrink dual in-line package; 42 leads (600 mil)

SOT270-1

UDA1325H

QFP64

plastic quad flat package; 64 leads (lead length 1.95 mm);

body 14

×

20

×

2.8 mm

SOT319-2

1999 May 10

4

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) CODEC

UDA1325

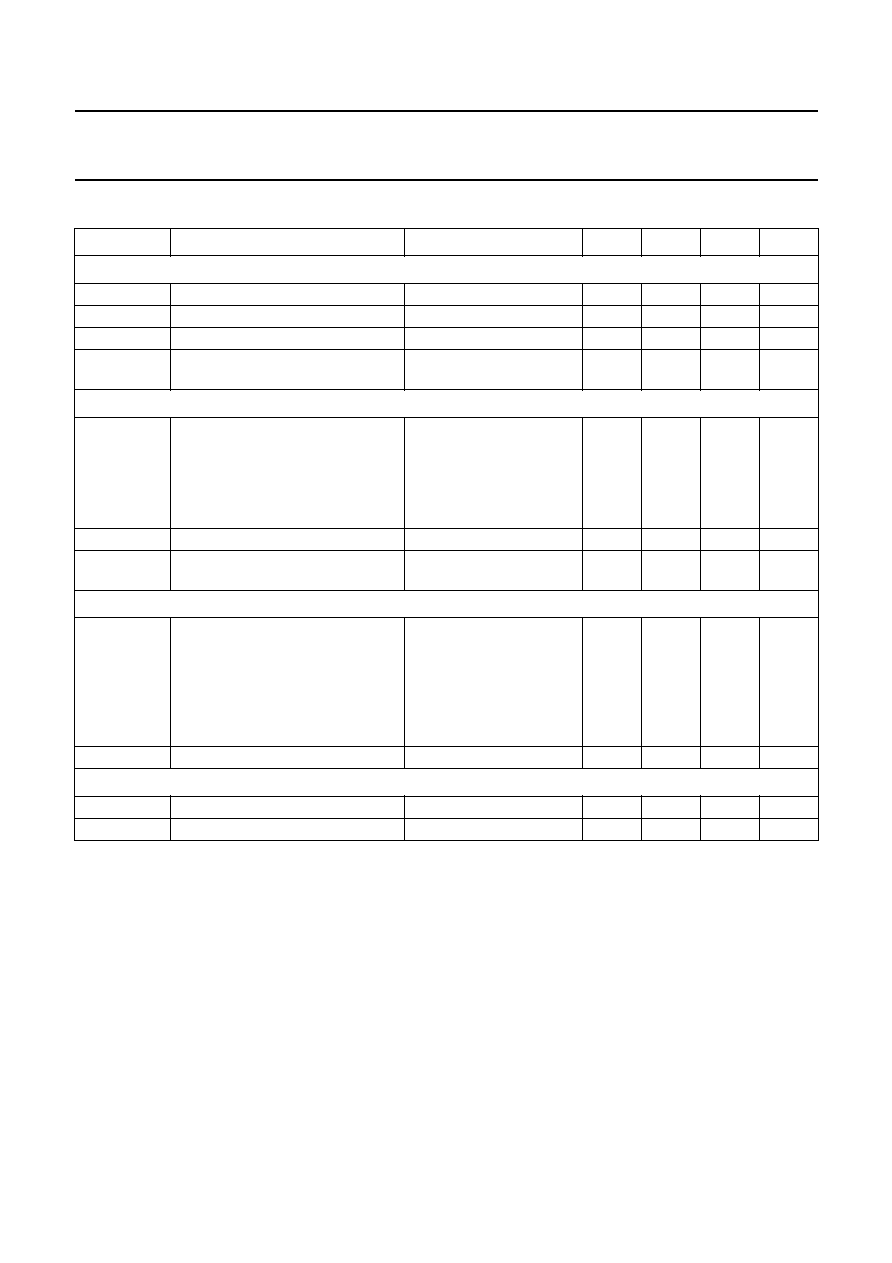

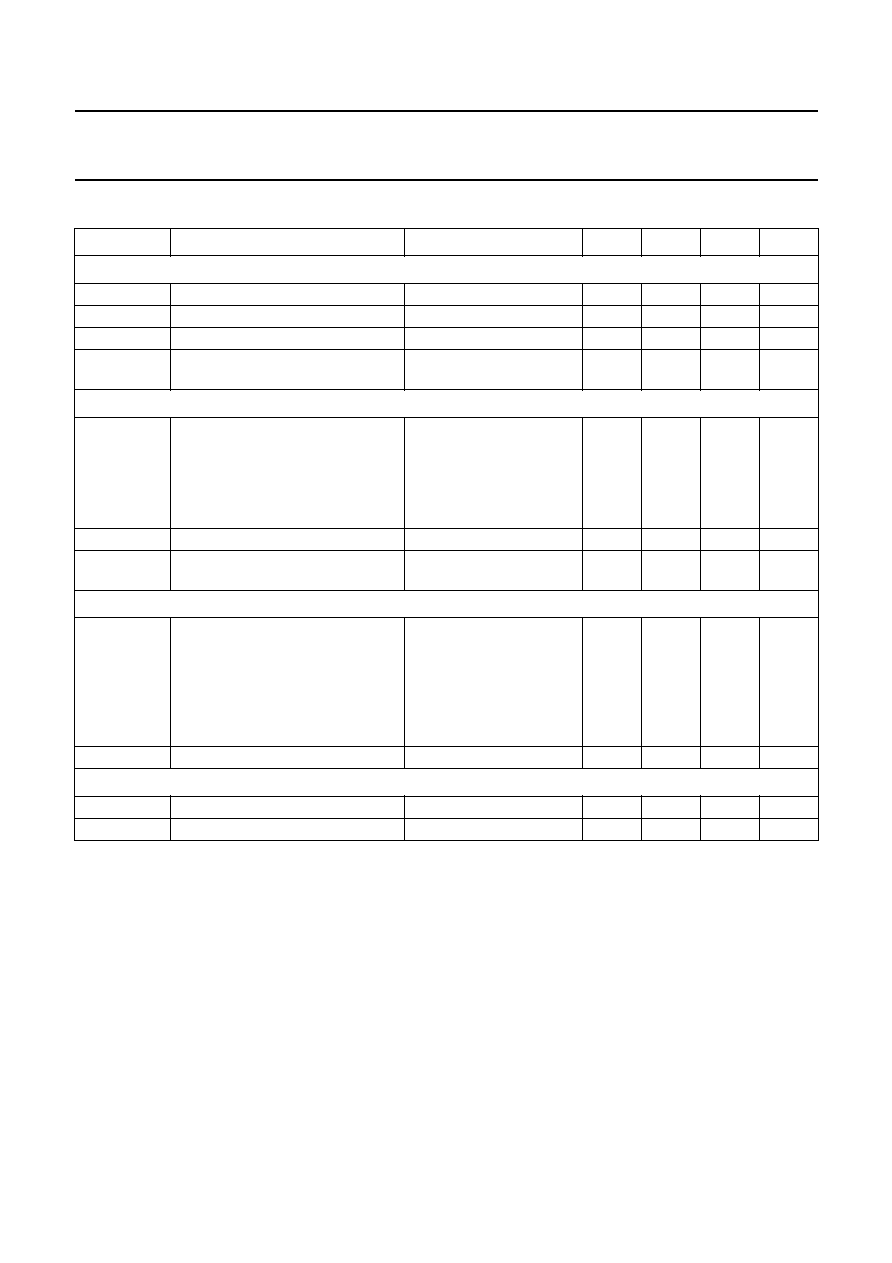

QUICK REFERENCE DATA

Note

1. Exclusive the IDDE current which depends on the components connected to the I/O pins.

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

Supplies

V

DDE

supply voltage periphery

4.75

5.0

5.25

V

V

DDI

supply voltage core

3.0

3.3

3.6

V

I

DD(tot)

total supply current

-

60

tbf

mA

I

DD(tot)(ps)

total supply current in power-saving

mode

note 1

-

360

-

µ

A

Dynamic performance DAC

(THD + N)/S

total harmonic distortion plus

noise-to-signal ratio

f

s

= 44.1 kHz; R

L

= 5 k

f

i

= 1 kHz (0 dB)

-

-

90

-

80

dB

-

0.0032

0.01

%

f

i

= 1 kHz (

-

60 dB)

-

-

30

-

20

dB

-

3.2

10

%

S/N

signal-to-noise ratio at bipolar zero

A-weighted at code 0000H 90

95

-

dBA

V

o(FS)(rms)

full-scale output voltage

(RMS value)

V

DD

= 3.3 V

-

0.66

-

V

Dynamic performance PGA and ADC

(THD + N)/S

total harmonic distortion plus

noise-to-signal ratio

f

s

= 44.1 kHz;

PGA gain = 0 dB

f

i

= 1 kHz; (0 dB);

V

i

= 1.0 V (RMS)

-

-

85

-

80

dB

-

0.0056

0.01

%

f

i

= 1 kHz (

-

60 dB)

-

-

30

-

20

dB

-

3.2

10.0

%

S/N

signal-to-noise ratio

V

i

= 0.0 V

90

95

-

dBA

General characteristics

f

i(s)

audio input sample frequency

5

-

55

kHz

T

amb

operating ambient temperature

0

25

70

°

C

1999 May 10

5

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) CODEC

UDA1325

BLOCK DIAGRAM

Fig.1 Block diagram (QFP64 package).

handbook, full pagewidth

MGM108

TIMING

ANALOG

PLL

OSC

48 MHz

OSC

ADC

24 (19)

27

25 (20)

26 (21)

28 (22)

52 (39)

53 (40)

54 (41)

55 (42)

63 (4)

1 (5)

2 (6)

13 (14)

17 (16)

15 (15)

(12) 11

(13) 12

(10) 9

(11) 10

(23) 32

(24) 33

(29) 38

(30) 39

(33) 42

(35) 44

ANALOG FRONT-END

USB-PROCESSOR

DIGITAL I/O

FIFO

AUDIO FEATURE

PROCESSING DSP

UPSAMPLE FILTERS

VARIABLE HOLD REGISTER

3rd-ORDER NOISE SHAPER

REFERENCE VOLTAGE

57 (1)

59 (2)

61 (3)

43 (34)

47 (36)

8 (9)

6 (8)

MICRO-

CONTROLLER

TEST

CONTROL

BLOCK

SAMPLE

FREQUENCY

GENERATOR

MUX

I

2

S-BUS

INTERFACE

DECIMATOR

FILTER

PGA

LEFT

ADC

PGA

RIGHT

ADC

LEFT

DAC

RIGHT

DAC

49 (37)

51 (38)

45, 46

41 (32)

40 (31)

Vref(AD)

Vref(DA)

(28) 37

(25) 34

(27) 36

(26) 35

(7) 4

(18) 21

(17) 19

n.c.

UDA1325

+

-

-

+

VRN

VINR

VSSA2

VINL

VSSA1

VDDA1

VOUTR

RTCB

GP4/BCKO

SHTCB

D

-

7, 5, 3, 64,

62, 60, 58, 56

P0.7 to P0.0

14, 16, 18, 20,

22, 23, 29, 30

P2.0 to P2.7

D

+

VDDI

VSSI

VDDE

GP1/DI

GP0/BCKI

VDDA2

BCK

48

EA

50

ALE

WS

DA

31

PSEN

VSSA3

XTAL2a

VDDA3

VRP

GP2/DO

GP3/WSO

XTAL1a

SDA

VSSX

XTAL1b

XTAL2b

CLK

VDDX

VSSO

VOUTL

TC

SCL

VDDO

VSSE

GP5/WSI

The pin numbers given in parenthesis refer to the SDIP42 version.

Document Outline

- FEATURES

- General

- Audio playback channel

- Audio recording channel

- USB endpoints

- Document references

- APPLICATIONS

- GENERAL DESCRIPTION

- ORDERING INFORMATION

- QUICK REFERENCE DATA

- BLOCK DIAGRAM

- PINNING

- FUNCTIONAL DESCRIPTION

- The Universal Serial Bus (USB)

- The analog front-end

- The USB processor

- Bit clock recovery

- Philips Serial Interface Engine (PSIE)

- Memory Management Unit (MMU) and integrated RAM

- Audio Sample Redistribution (ASR)

- The 80C51 microcontroller

- The Analog-to-Digital Interface (ADIF)

- Programmable Gain Amplifier circuit (PGA)

- The Analog-to-Digital Converter (ADC)

- The Decimation Filter (DF)

- The clock source of the analog-to-digital interface

- The Asynchronous Digital-to-Analog Converter (ADAC)

- The Sample Frequency Generator (SFG)

- First-In First-Out (FIFO) registers

- The sound processing DSP

- The upsampling filters and variable hold function

- The noise shaper

- The Filter Stream DAC (FSDAC)

- USB ENDPOINT DESCRIPTION

- CONTROLLING THE PLAYBACK FEATURES

- Controlling the playback features of the ADAC

- Soft mute control

- Volume control

- Treble control

- Bass control

- De-emphasis

- Filter characteristics playback channel

- DSP extension port for enhanced playback audio processing

- PORT DEFINITION 80C51

- MEMORY AND REGISTER SPACE 80C51

- Overview registers

- Interrupts

- Internal registers

- START-UP BEHAVIOUR AND POWER MANAGEMENT

- Start-up of the UDA1325

- Power Management

- COMMAND SUMMARY

- COMMAND DESCRIPTIONS

- Command procedure

- Initialization commands

- Data flow commands

- General commands

- I 2 C MASTER/SLAVE INTERFACE

- Characteristics of the I 2 C-bus

- Programmers view

- S1CON register

- LIMITING VALUES

- THERMAL CHARACTERISTICS

- RECOMMENDED OPERATING CONDITIONS

- DC CHARACTERISTICS

- AC CHARACTERISTICS

- APPLICATION INFORMATION

- PACKAGE OUTLINES

- SOLDERING

- DEFINITIONS

- LIFE SUPPORT APPLICATIONS

- PURCHASE OF PHILIPS I 2 C COMPONENTS