UDA1431T 16-bit, 48 kHz, low-cost stereo current DAC

1.

General description

The UDA1431T is a 16-bit, 48 kHz, single-chip stereo DAC employing bitstream

conversion techniques.

The UDA1431T supports the I

2

S-bus data format with word lengths of up to 24 bits,

MSB justified and can be operated with a 256f

s

master clock mode.

The audio outputs meet the IEC 61938 specification.

2.

Features

s

Low power consumption

s

Analog power supply voltage from 10.8 V to 13.2 V

s

Digital power supply voltage from 3.1 V to 3.5 V

s

Master clock frequencies of 256f

s

s

Supports sampling frequencies up to 48 kHz

s

Integrated digital filter

s

No analog post filtering required for DAC

s

Slave mode only applications

s

I

2

S-bus input interface: 16-bit, 18-bit, 20-bit and 24-bit format compatible

s

CMOS levels compatible digital inputs and outputs

s

Very easy application

s

Advanced audio configuration:

x

Stereo line output

x

High linearity, wide dynamic range and low distortion

s

Small package size (SO14)

3.

Applications

s

PC audio applications

s

Car radio applications

s

DVD players

s

Digital set-top boxes

UDA1431T

16-bit, 48 kHz, low-cost stereo current DAC

Rev. 02 -- 20 February 2006

Product data sheet

UDA1431T_2

� Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Product data sheet

Rev. 02 -- 20 February 2006

2 of 17

Philips Semiconductors

UDA1431T

16-bit, 48 kHz, low-cost stereo current DAC

4.

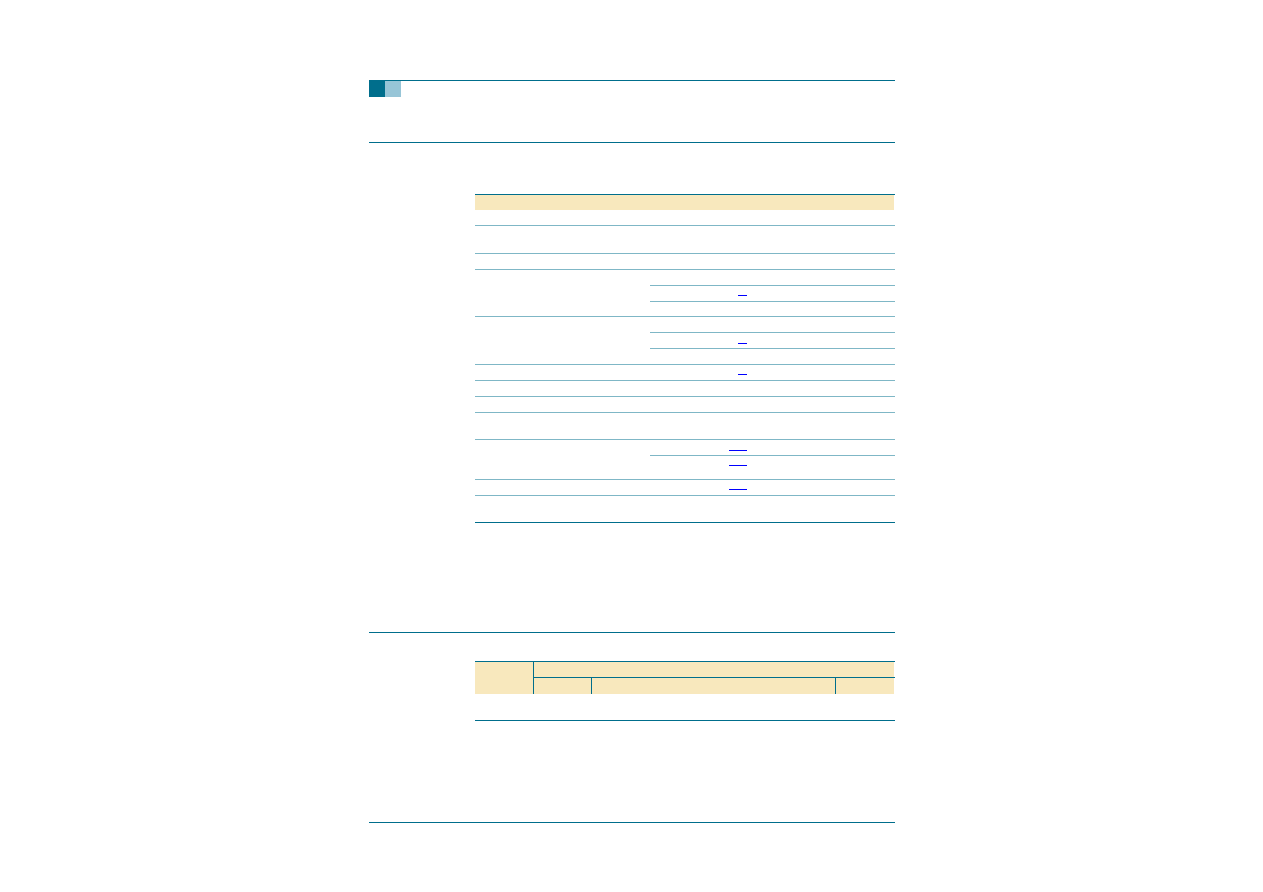

Quick reference data

[1]

A 1 kHz at 0 dB sine wave input is applied.

[2]

(THD + N)/S is the power ratio between the sum of noise and distortion and the output signal.

[3]

Measurement is performed with a 22 kHz low-pass filter and is unweighted.

[4]

Measurement is performed with a ITU-R-2K filter and is unweighted.

[5]

S/N is the power ratio between the output signal and the noise measured with no signal applied.

5.

Ordering information

Table 1:

Quick reference data

V

DDA

= 12.0 V; V

DDD

= 3.3 V; T

amb

= 25

�

C; f

s

= 48 kHz; f

i

= 1 kHz; all voltages referenced to ground

(pins V

SSA

and V

SSD

); unless otherwise specified.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

Supplies

V

DDA

analog supply voltage

(for DAC)

10.8

12.0

13.2

V

V

DDD

digital supply voltage

3.1

3.3

3.5

V

I

DDA

analog supply current

(for DAC)

V

DDA

= 12.0 V

operating

[1]

-

6.6

-

mA

power-down

-

0.8

-

mA

I

DDD

digital supply current

V

DDD

= 3.3 V

operating

[1]

-

7.0

-

mA

power-down

-

6.8

-

mA

P

tot

total power dissipation

operating

[1]

-

102

-

mW

T

amb

ambient temperature

5

-

65

�

C

Digital-to-analog converter

V

o(rms)

output voltage

(RMS value)

1.575

1.880

1.925

V

(THD + N)/S

total harmonic

distortion-plus-noise to

signal ratio

at 0 dB

[2] [3]

-

62

-

66

-

dB

at

-

60 dB

[2] [4]

-

-

32.5

-

dB

S/N

signal-to-noise ratio

[3] [5]

89

94

-

dB

cs

channel separation

at 0 dB; from

1 kHz to 20 kHz

85

98

-

dB

Table 2:

Ordering information

Type

number

Package

Name

Description

Version

UDA1431T

SO14

plastic small outline package; 14 leads; body width

3.9 mm

SOT108-1

UDA1431T_2

� Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Product data sheet

Rev. 02 -- 20 February 2006

3 of 17

Philips Semiconductors

UDA1431T

16-bit, 48 kHz, low-cost stereo current DAC

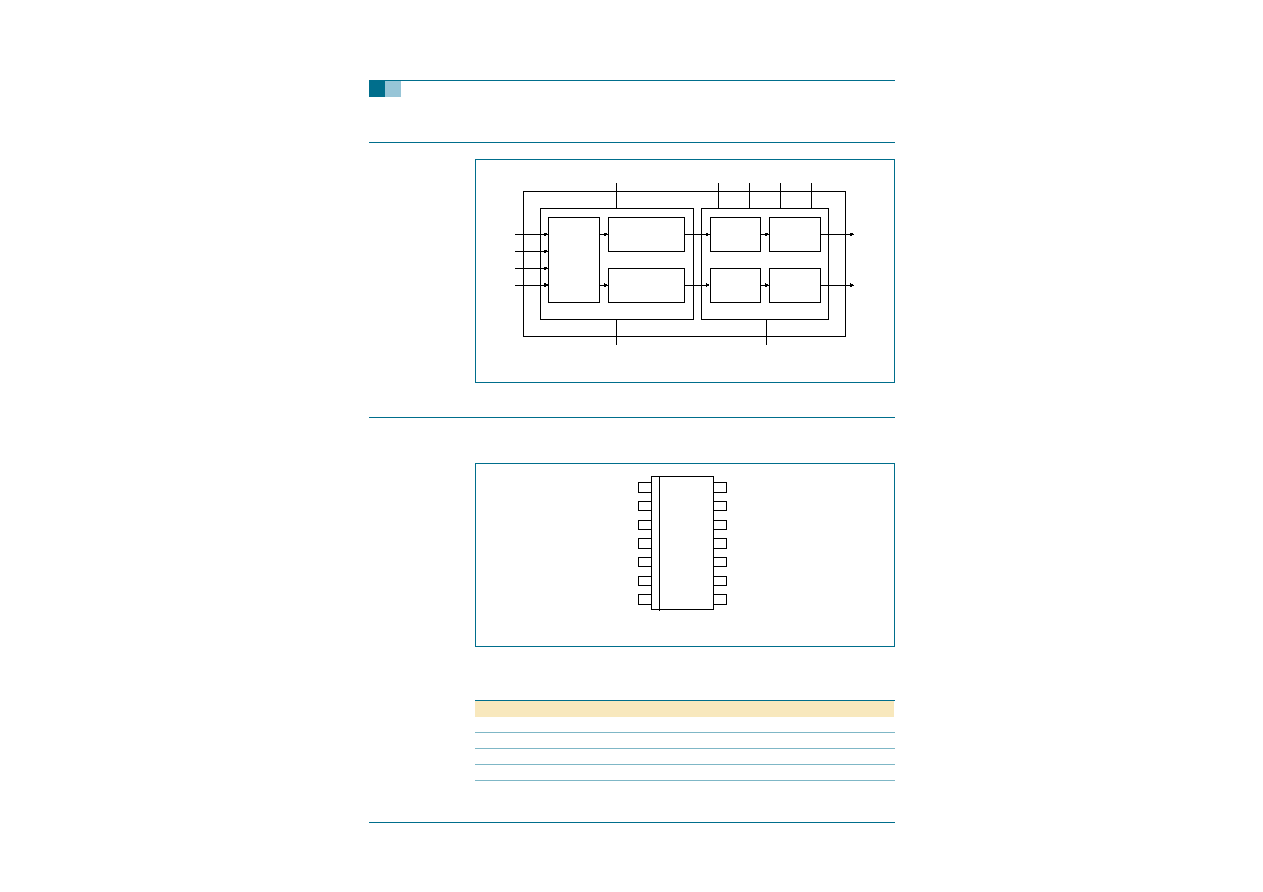

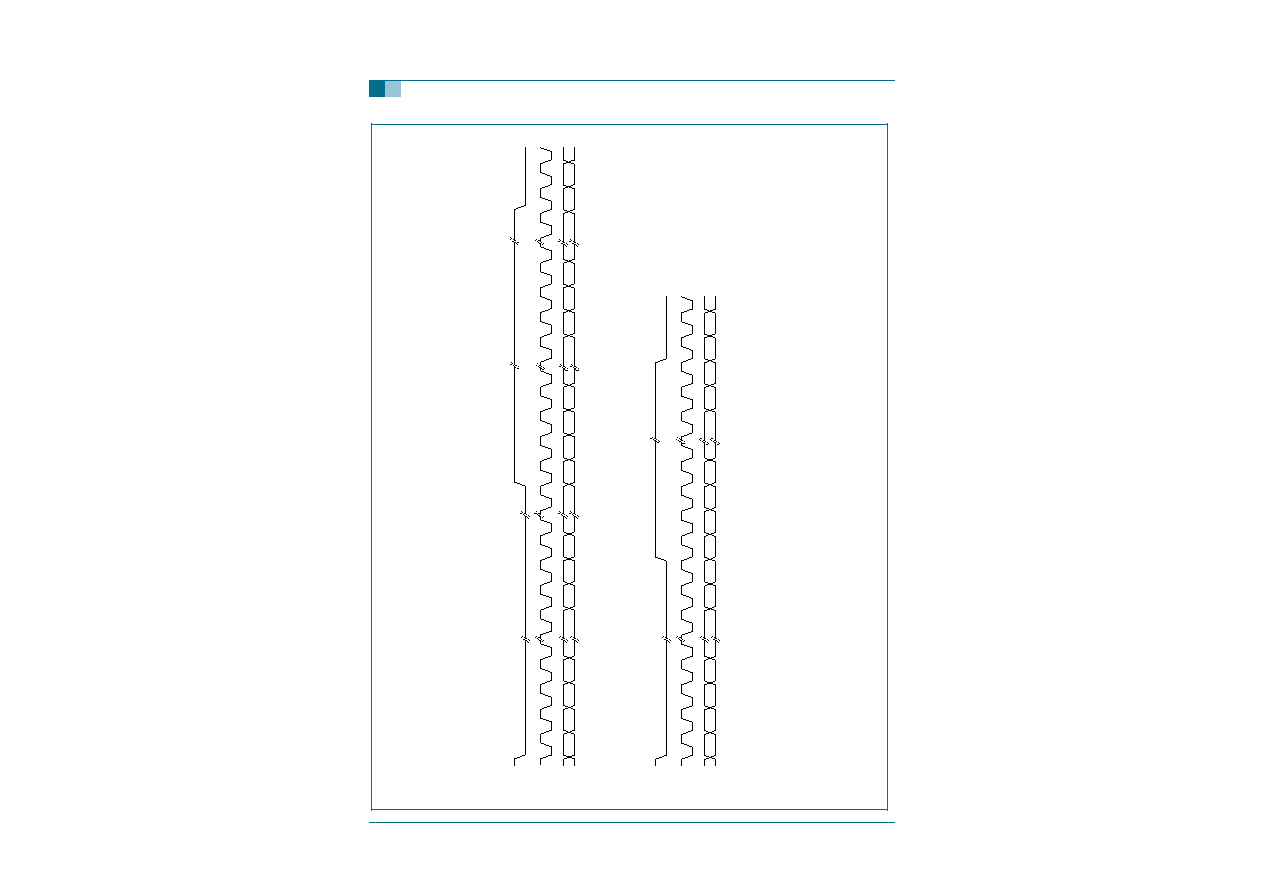

6.

Block diagram

7.

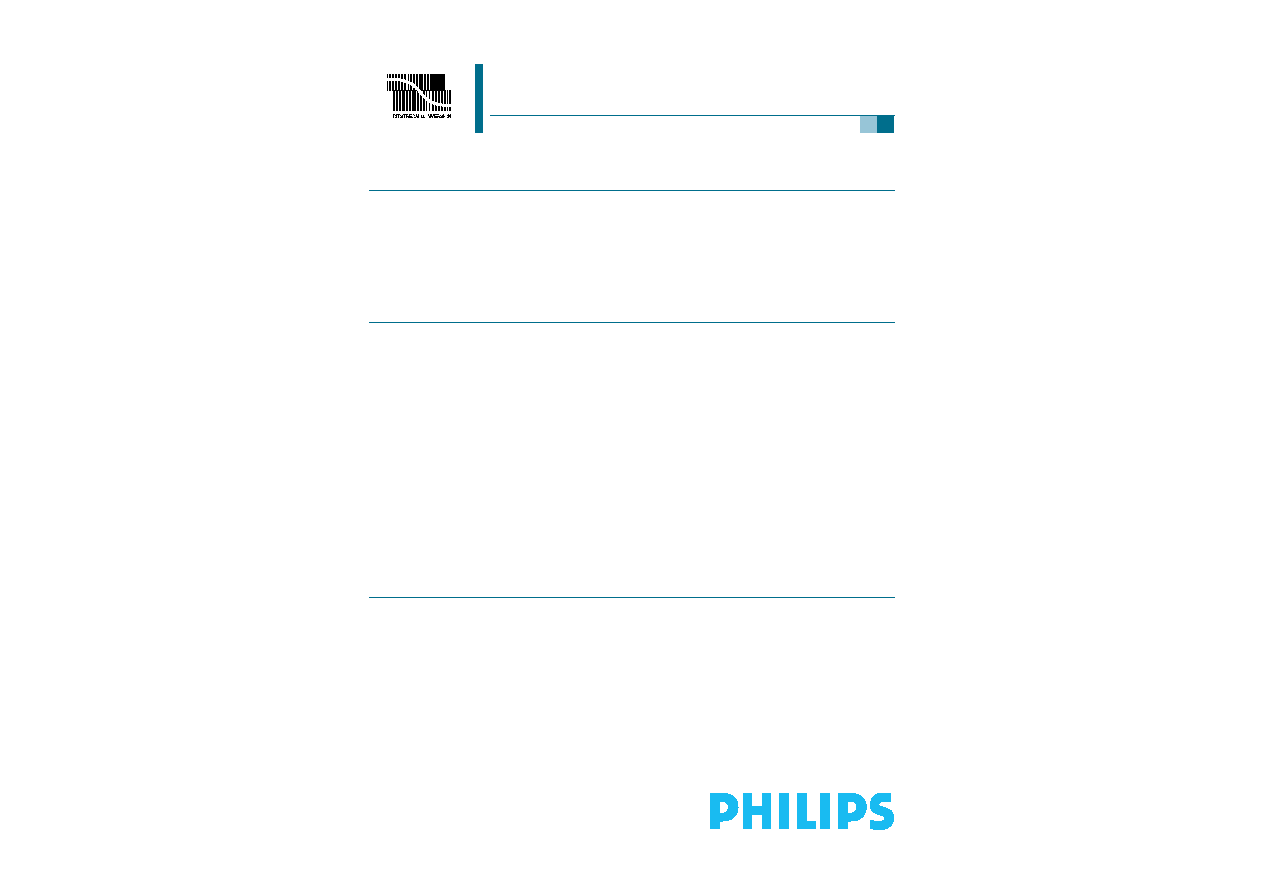

Pinning information

7.1 Pinning

7.2 Pin description

Fig 1.

Block diagram

001aac962

ANALOG

DIGITAL

6

10

ROUT

LOUT

14

11

8

9

12

V

DDD

DVREF AVREF

V

DDA

PD_N

7

1

V

SSA

V

SSD

4

13

2

3

BCLK

MCLK

WS

SDI

UDA1431T

AMPLIFIER

AMPLIFIER

CURRENT

DAC

I

2

S-BUS

INTERFACE

CURRENT

DAC

UPSAMPLING

FILTERING

NOISE SHAPING

UPSAMPLING

FILTERING

NOISE SHAPING

Fig 2.

Pin configuration

UDA1431T

V

SSD

V

DDD

WS

MCLK

SDI

PD_N

BCLK

DVREF

i.c.

LOUT

ROUT

V

DDA

V

SSA

AVREF

001aac963

1

2

3

4

5

6

7

8

10

9

12

11

14

13

Table 3:

Pin description

Symbol

Pin

Description

V

SSD

1

digital ground

WS

2

word select input

SDI

3

serial audio data input

BCLK

4

bit clock input

i.c.

5

internally connected; do not connect or connect to V

DDD

UDA1431T_2

� Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Product data sheet

Rev. 02 -- 20 February 2006

4 of 17

Philips Semiconductors

UDA1431T

16-bit, 48 kHz, low-cost stereo current DAC

8.

Functional description

8.1 Master clock

The UDA1431T operates in slave mode only. Therefore, in all applications the system

devices must provide a master clock (pin MCLK) at 256f

s

for correct operation. The master

clock must be locked in frequency to the digital interface input signals.

The UDA1431T supports sampling frequencies up to 48 kHz.

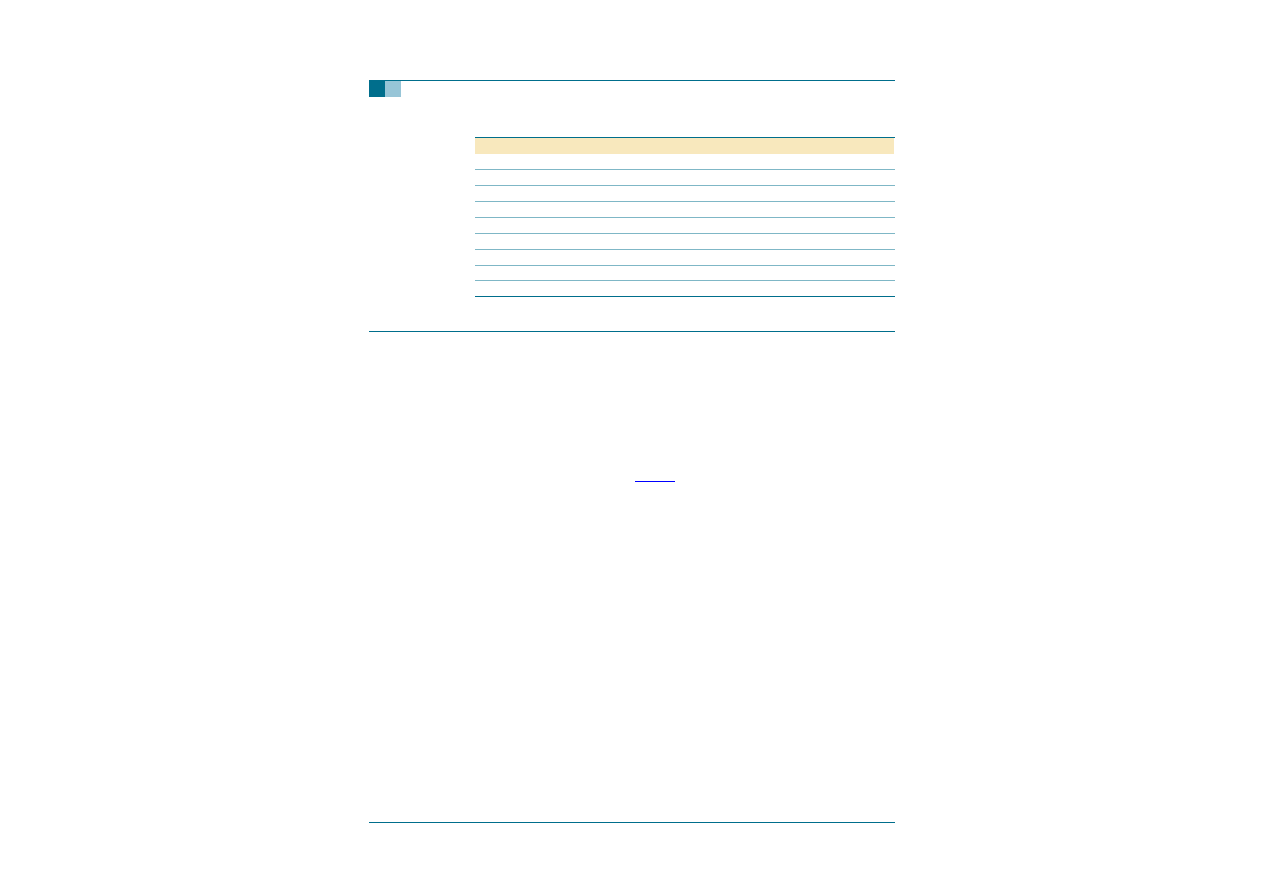

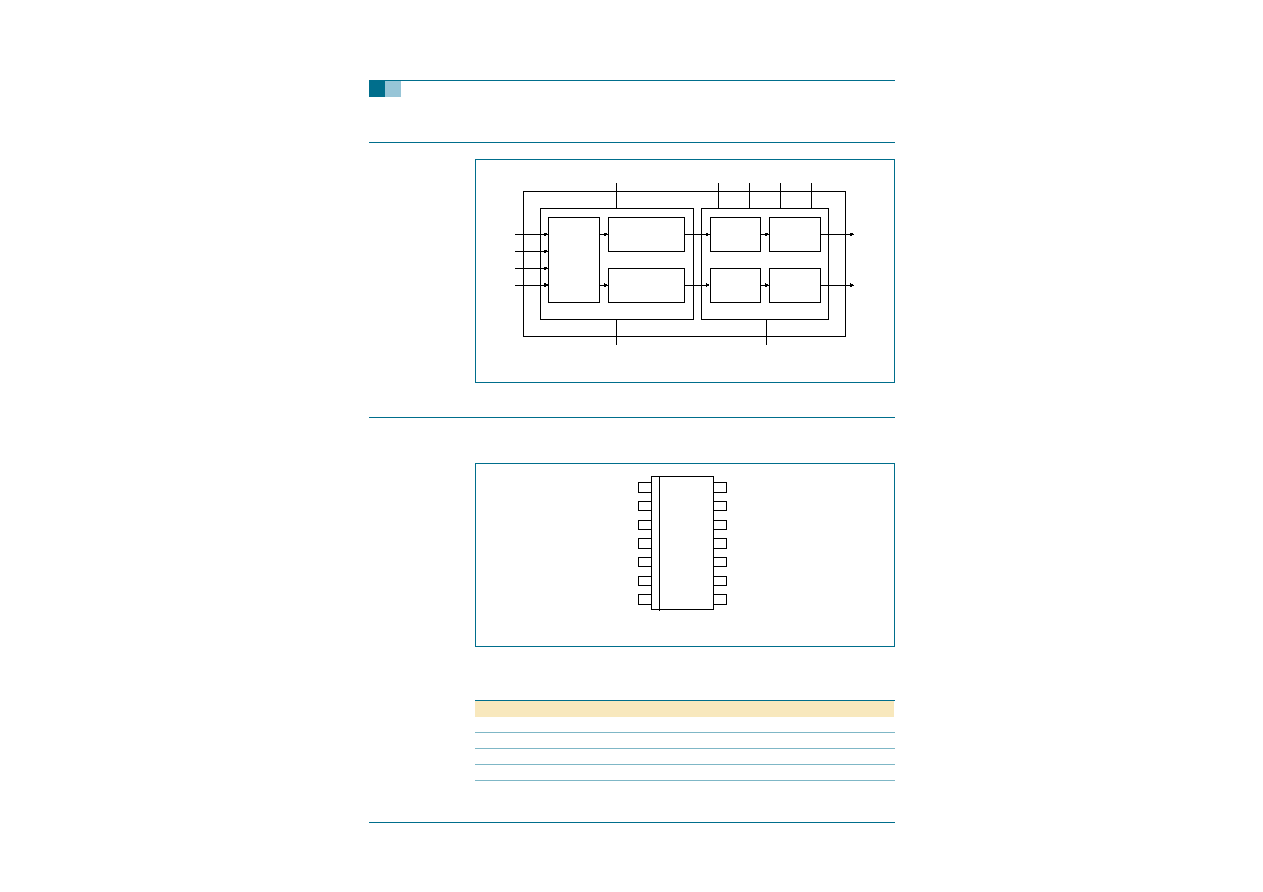

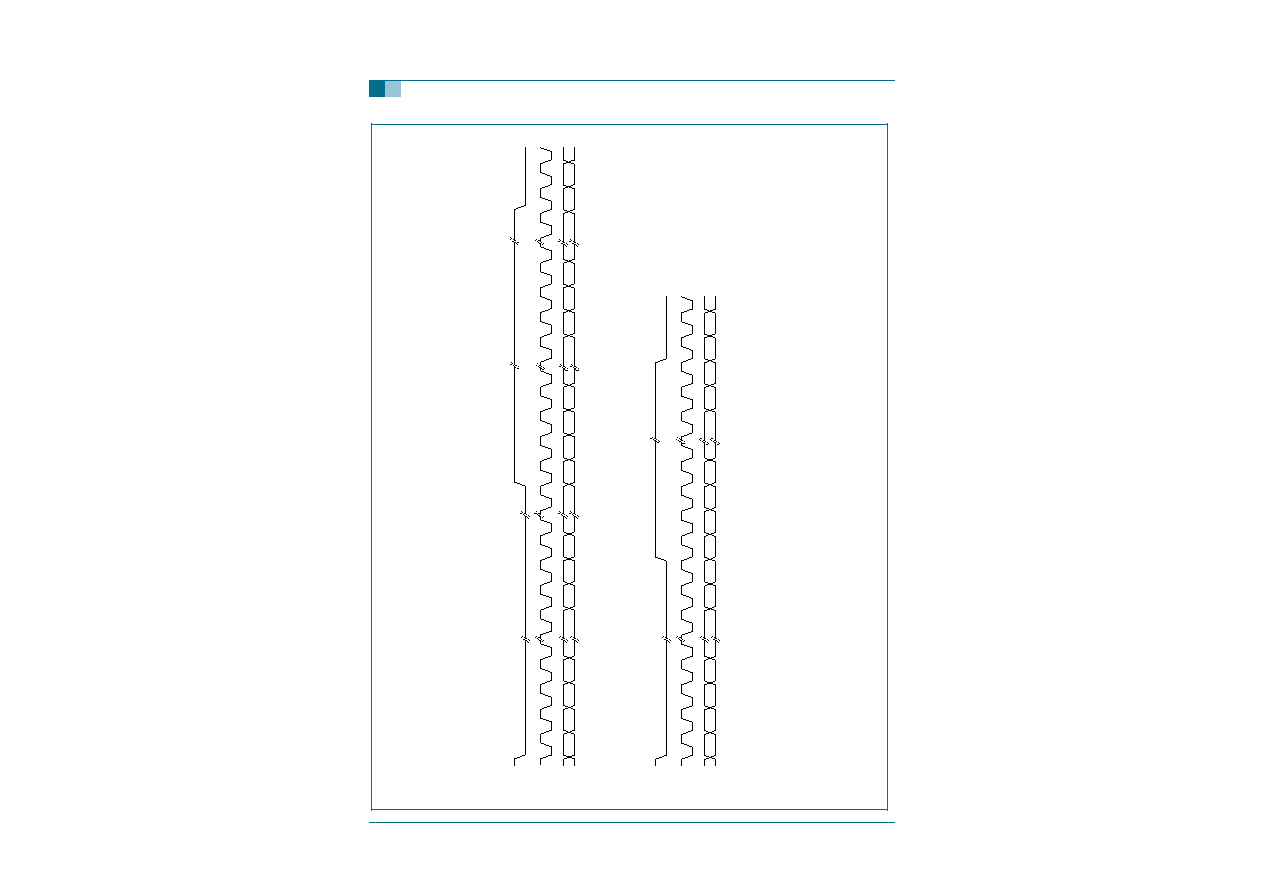

8.2 Data formats

The I

2

S-bus formats are shown in

Figure 3

.

Left and right data channel words are time multiplexed.

The UDA1431T supports I

2

S-bus formats with data word length up to 24 bits.

The BCLK clock can be up to 48f

s

, or in other words the BCLK frequency is 48 times or

less the word select frequency (pin WS): f

BCLK

48

�

f

WS

.

Important: The WS edge MUST fall on the negative edge of the BCLK at all times for

proper operation of the digital interface.

8.3 Noise shaper

The 1st-order noise shaper operates at 32f

s

. It shifts in-band quantization noise to

frequencies well above the audio band. This noise shaping technique enables high

signal-to-noise ratios to be achieved. The noise shaper output is converted into an analog

signal using a current DAC.

ROUT

6

right channel output

V

SSA

7

analog ground (for DAC)

AVREF

8

regulator decoupling

V

DDA

9

analog supply voltage (for DAC)

LOUT

10

left channel output

DVREF

11

internal reference voltage (digital part)

PD_N

12

power-down input (active LOW)

MCLK

13

master clock input (256f

s

)

V

DDD

14

digital supply voltage

Table 3:

Pin description

...continued

Symbol

Pin

Description

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx

xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

UD

A1431T_2

� K

oninklijk

e Philips Electronics N.V

. 2006. All r

ights reser

v

ed.

Pr

oduct data sheet

Re

v

.

02 -- 20 Februar

y 2006

5 of 17

Philips Semiconductor

s

UD

A1431T

16-bit, 48 kHz, lo

w-cost stereo current D

A

C

Fig 3.

I

2

S-bus data formats

001aac967

LEFT CHANNEL

I

2

S-BUS FORMAT

I

2

S-BUS FORMAT IN 16-BIT MODE

WS

BCLK

SDI

RIGHT CHANNEL

MSB

L

B2

L

B3

L

B14

L

B15

L

LSB

L

B3

R

B14

R

B15

R

LSB

R

MSB

R

B2

R

MSB

L

WS

BCLK

SDI

LEFT CHANNEL

RIGHT CHANNEL

MSB

L

LSB

R

B2

L

B3

L

B14

L

B15

L

LSB

L

LSB

R

MSB

L

MSB

R

B2

R

B3

R

B14

R

B15

R

Document Outline