| ÐлекÑÑоннÑй компоненÑ: UJA1065TW | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

1.

General description

The UJA1065 System Basis Chip (SBC) replaces basic discrete components which are

common in every Electronic Control Unit (ECU) with a Controller Area Network (CAN) and

a Local Interconnect Network (LIN) interface. The SBC supports all networking

applications which control various power and sensor peripherals by using high-speed

CAN as the main network interface and LIN as a local sub-bus. The SBC contains the

following integrated devices:

·

High-speed CAN transceiver, inter-operable and downwards compatible with CAN

transceiver TJA1041 and TJA1041A, and compatible with the ISO11898-2 standard

and the ISO11898-5 standard (in preparation)

·

LIN transceiver compliant with LIN 2.0 and SAE J2602, and compatible with LIN 1.3

·

Advanced independant watchdog

·

Dedicated voltage regulators for microcontroller and CAN transceiver

·

Serial peripheral interface (full duplex)

·

Local wake-up input port

·

Inhibit / limp home output port

In addition to the advantages of integrating these common ECU functions in a single

package, the SBC offers an intelligent combination of system-specific functions such as:

·

Advanced low power concept

·

Safe and controlled system start-up behavior

·

Advanced fail-safe system behavior that prevents any conceivable deadlock

·

Detailed status reporting on system and sub-system levels

The UJA1065 is designed to be used in combination with a microcontroller with a CAN

controller. The SBC ensures that the microcontroller is always started up in a defined

manner. In failure situations the SBC will maintain the microcontroller function for as long

as possible, to provide full monitoring and software driven fall-back operation.

The UJA1065 is designed for 14 V single power supply architectures and for 14 V and

42 V dual power supply architectures.

UJA1065

High-speed CAN/LIN fail-safe system basis chip

Rev. 01 -- 10 August 2005

Objective data sheet

9397 750 14409

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Objective data sheet

Rev. 01 -- 10 August 2005

2 of 67

Philips Semiconductors

UJA1065

High-speed CAN/LIN fail-safe system basis chip

2.

Features

2.1 General

s

Contains a full set of CAN and LIN ECU functions:

x

CAN transceiver and LIN transceiver

x

Voltage regulator for the microcontroller (3.0 V, 3.3 V or 5.0 V)

x

Separate voltage regulator for the CAN transceiver (5 V)

x

Enhanced window watchdog with on-chip oscillator

x

Serial Peripheral Interface (SPI) for the microcontroller

x

ECU power management system

x

Fully integrated autonomous fail-safe system

s

Designed for automotive applications:

x

Supports 14 V, 24 V and 42 V architectures

x

Excellent ElectroMagnetic Compatibility (EMC) performance

x

±

8 kV ElectroStatic Discharge (ESD) protection Human Body Model (HBM) for off

board pins

x

±

60 V short-circuit proof CAN / LIN-bus pins

x

Battery and CAN / LIN-bus pins are protected against transients in accordance with

ISO 7637

x

Very low Sleep current

s

Supports remote flash programming via the CAN-bus

s

Small 8 mm

×

11 mm HTSSOP32 package with low thermal resistance

2.2 CAN transceiver

s

ISO 11898-2 and ISO 11898-5 compliant high-speed CAN transceiver

s

Enhanced error signalling and reporting

s

Dedicated low dropout voltage regulator for the CAN-bus:

x

Independent from microcontroller supply

x

Guarded by CAN-bus failure management

x

Significantly improves EMC performance

s

Partial networking option with global wake-up feature, allows selective CAN-bus

communication without waking up sleeping nodes

s

Bus connections are truly floating when power is off

s

SPLIT output pin for stabilizing the recessive bus level

2.3 LIN transceiver

s

LIN 2.0 compliant LIN transceiver

s

Enhanced error signalling and reporting

s

Downward compatible with LIN 1.3 and the TJA1020

9397 750 14409

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Objective data sheet

Rev. 01 -- 10 August 2005

3 of 67

Philips Semiconductors

UJA1065

High-speed CAN/LIN fail-safe system basis chip

2.4 Power management

s

Smart operating modes and power management modes

s

Cyclic wake-up capability in Standby and Sleep mode

s

Local wake-up input with cyclic supply feature

s

Remote wake-up capability via the CAN-bus and LIN-bus

s

External voltage regulators can easily be incorporated in the power supply system

(flexible and fail-safe)

s

42 V battery related high-side switch for driving external loads such as relays and

wake-up switches

s

Intelligent maskable interrupt output

2.5 Fail-safe features

s

Safe and predictable behavior under all conditions

s

Programmable fail-safe coded window and time-out watchdog with on-chip oscillator,

guaranteeing autonomous fail-safe system supervision

s

Fail-safe coded 16-bit SPI interface for the microcontroller

s

Global enable pin for the control of safety critical hardware

s

Detection and detailed reporting of failures:

x

On-chip oscillator failure and watchdog alerts

x

Battery and voltage regulator undervoltages

x

CAN and LIN-bus failures (short-circuits and open-circuit bus wires)

x

TXD and RXD clamping situations and short-circuits

x

Clamped or open reset line

x

SPI message errors

x

Overtemperature warning

x

ECU ground shift (two selectable thresholds)

s

Rigorous error handling based on diagnostics

s

Supply failure early warning allows critical data to be stored

s

23 bits of access-protected RAM is available e.g. for logging of cyclic problems

s

Reporting in a single SPI message; no assembly of multiple SPI frames needed

s

Limp home output signal for activating application hardware in case system enters

Fail-safe mode (e.g. for switching on warning lights)

s

Fail-safe coded activation of Software development mode and Flash mode

s

Unique SPI readable device type identification

s

Software initiated system reset

3.

Ordering information

Table 1:

Ordering information

Type number

Package

Name

Description

Version

UJA1065TW

HTSSOP32

plastic thermal enhanced thin shrink small outline package; 32 leads;

body width 6.1 mm; lead pitch 0.65 mm; exposed die pad

SOT549-1

9397 750 14409

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Objective data sheet

Rev. 01 -- 10 August 2005

4 of 67

Philips Semiconductors

UJA1065

High-speed CAN/LIN fail-safe system basis chip

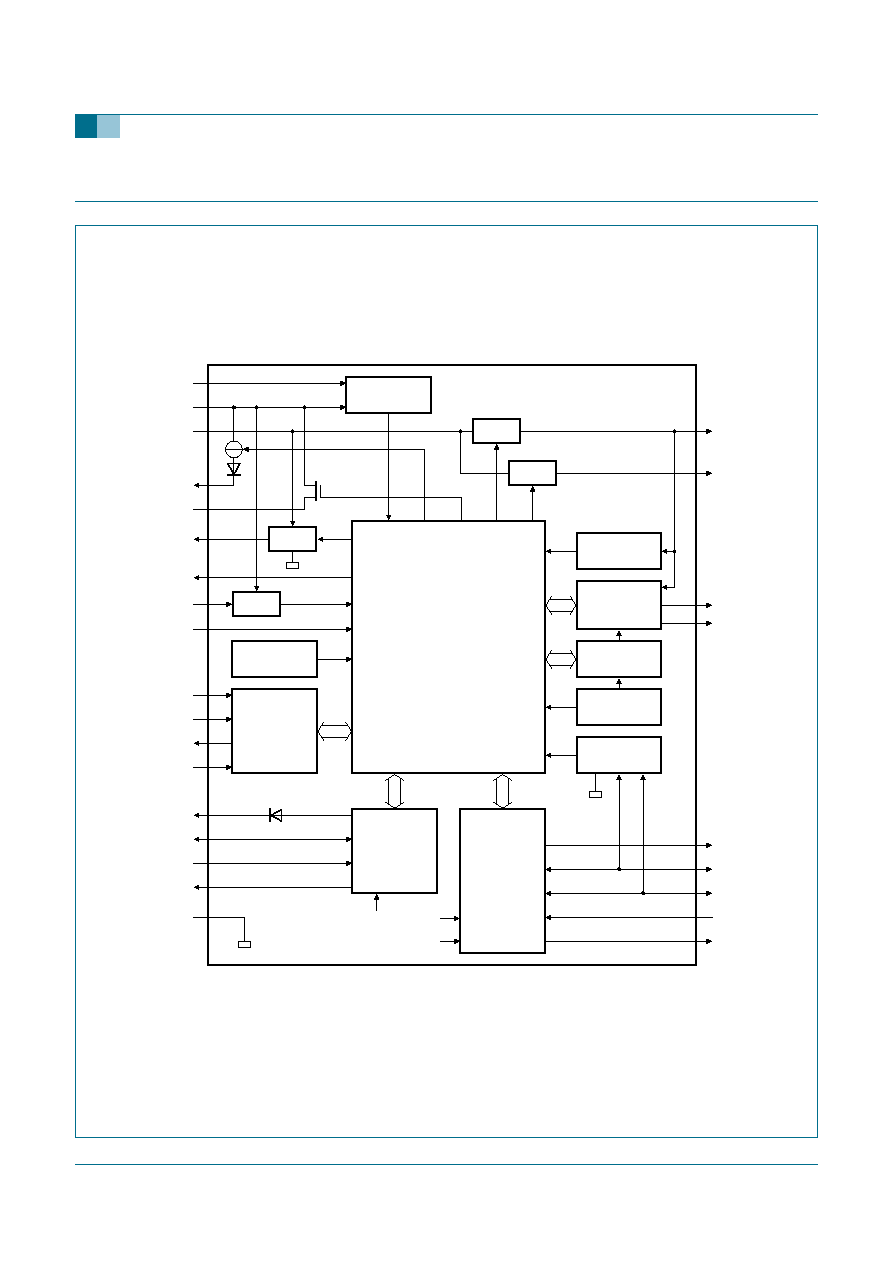

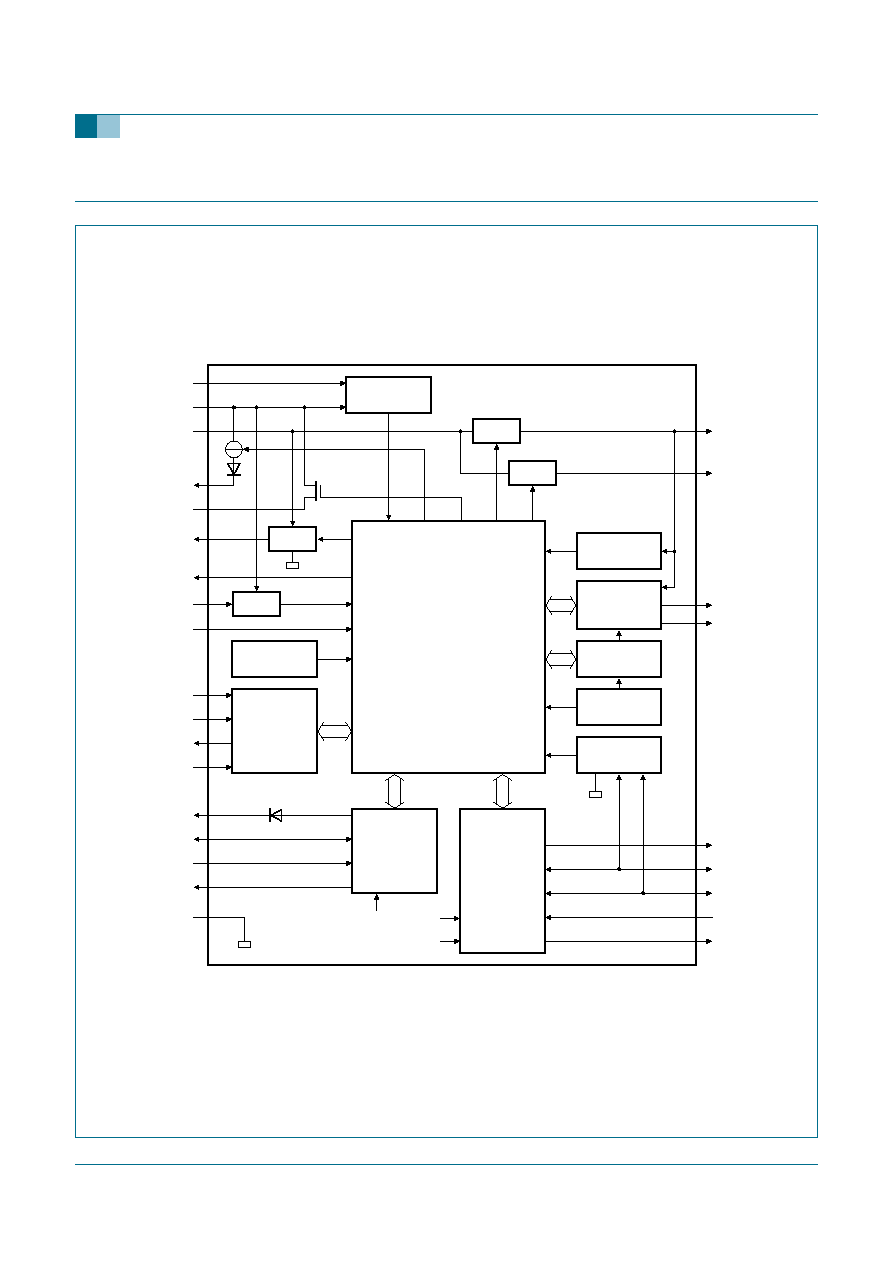

4.

Block diagram

Fig 1.

Block diagram

BAT42

BAT14

SYSINH

V3

INH/LIMP

INTN

TEST

SCK

SDI

SDO

SCS

RTLIN

LIN

TXDL

RXDL

GND

WAKE

SENSE

32

27

29

30

17

7

16

11

9

10

12

26

25

3

5

23

18

31

V1

V2

RSTN

EN

SPLIT

CANH

CANL

TXDC

RXDC

4

20

6

8

24

21

22

13

14

SBC

FAIL-SAFE

SYSTEM

V1 MONITOR

RESET/EN

WATCHDOG

OSCILLATOR

GND SHIFT

DETECTOR

BAT

MONITOR

V1

V2

HIGH

SPEED

CAN

LIN

SPI

CHIP

TEMPERATURE

WAKE

INH

BAT42

BAT42

V2

001aac305

UJA1065

9397 750 14409

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Objective data sheet

Rev. 01 -- 10 August 2005

5 of 67

Philips Semiconductors

UJA1065

High-speed CAN/LIN fail-safe system basis chip

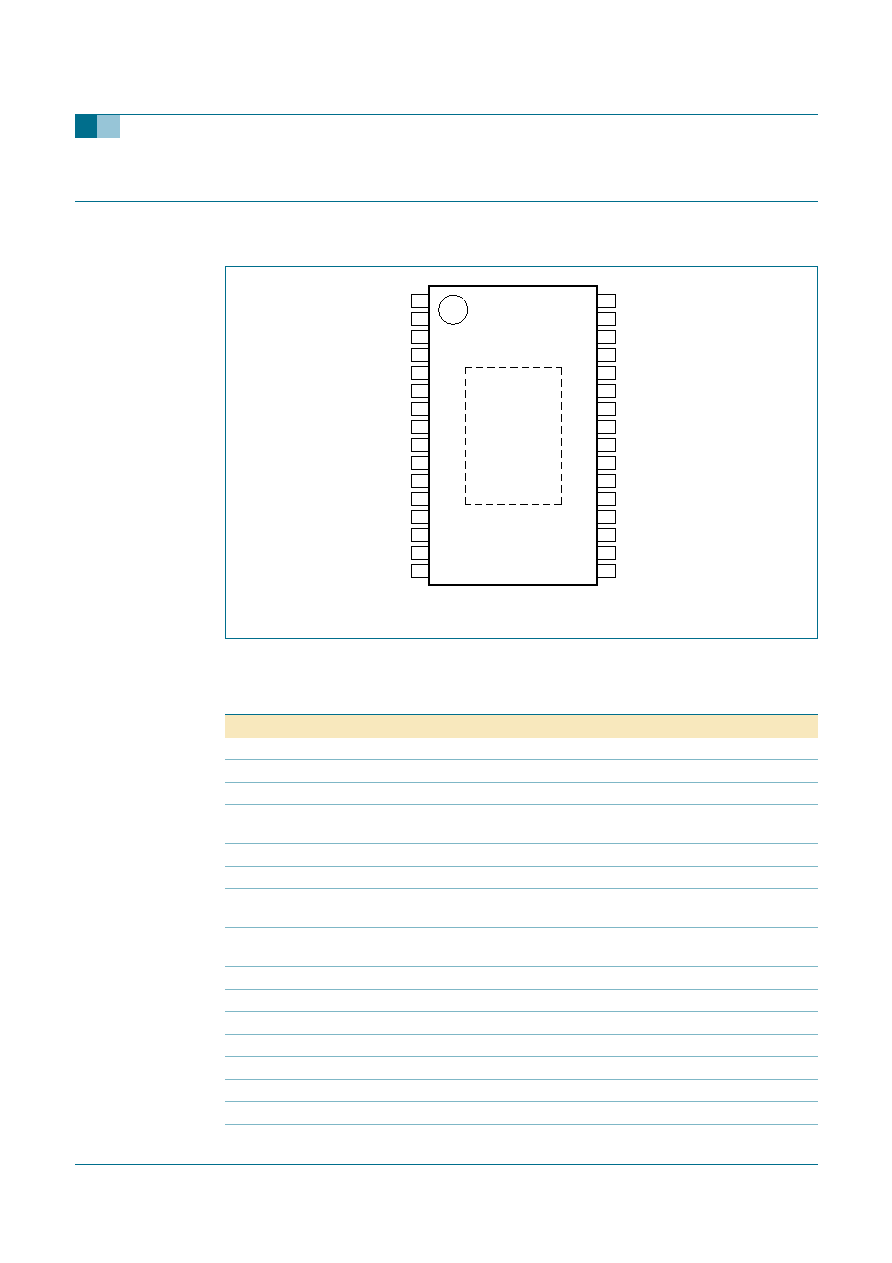

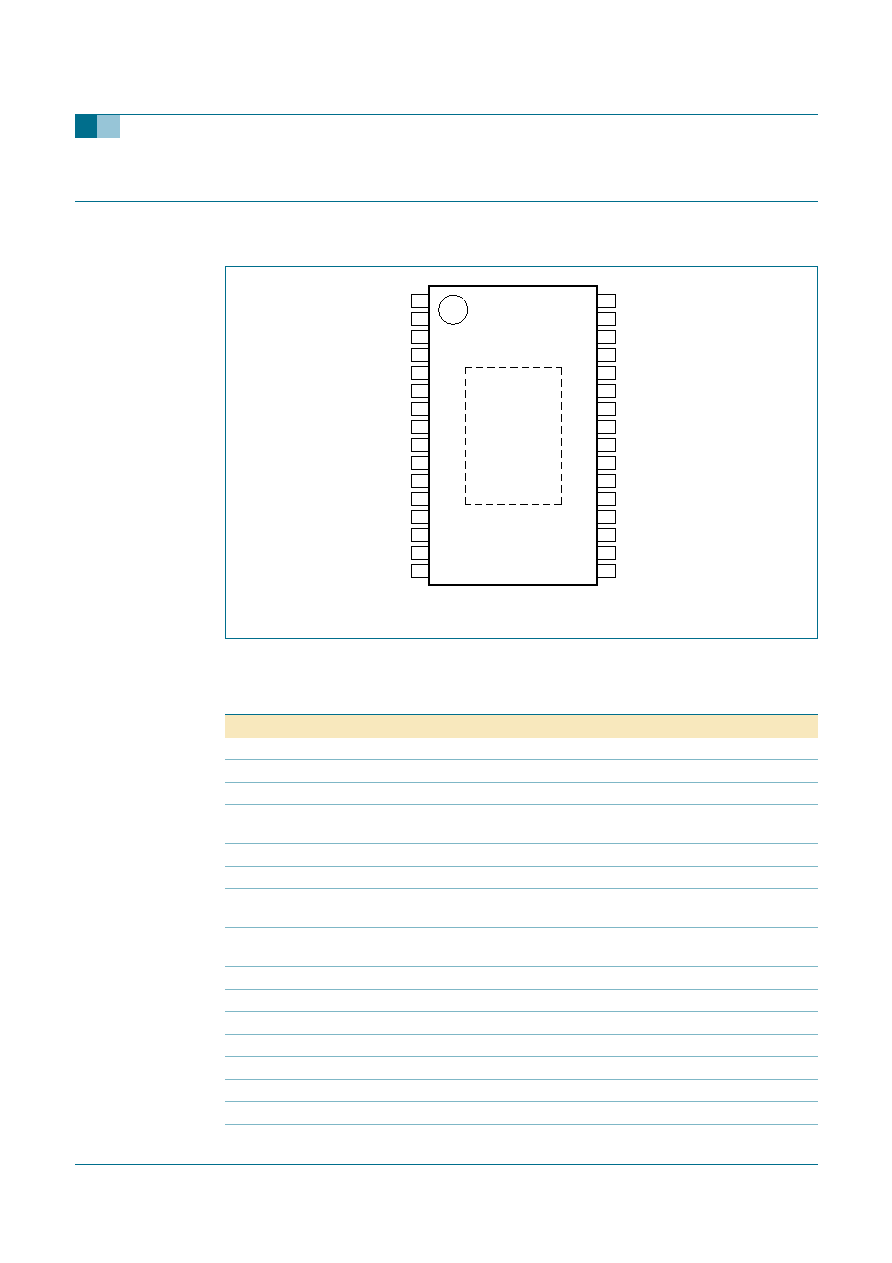

5.

Pinning information

5.1 Pinning

5.2 Pin description

Fig 2.

Pin configuration

UJA1065TW

n.c.

BAT42

n.c.

SENSE

TXDL

V3

V1

SYSINH

RXDL

n.c.

RSTN

BAT14

INTN

RTLIN

EN

LIN

SDI

SPLIT

SDO

GND

SCK

CANL

SCS

CANH

TXDC

V2

RXDC

n.c.

n.c.

WAKE

TEST

INH/LIMP

001aac306

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

18

17

20

19

22

21

24

23

26

25

32

31

30

29

28

27

Table 2:

Pin description

Symbol

Pin

Description

n.c.

1

not connected

n.c.

2

not connected

TXDL

3

LIN transmit data input (LOW for dominant, HIGH for recessive)

V1

4

voltage regulator output for the microcontroller (3 V, 3.3 V or 5 V depending on

the SBC version)

RXDL

5

LIN receive data output (LOW when dominant, HIGH when recessive)

RSTN

6

reset output to microcontroller (active LOW; will detect clamping situations)

INTN

7

interrupt output to microcontroller (active LOW; open-drain, wire-AND this pin to

other ECU interrupt outputs)

EN

8

enable output (active HIGH; push-pull, LOW with every reset / watchdog

overflow)

SDI

9

SPI data input

SDO

10

SPI data output (floating when pin SCS is HIGH)

SCK

11

SPI clock input

SCS

12

SPI chip select input (active LOW)

TXDC

13

CAN transmit data input (LOW for dominant; HIGH for recessive)

RXDC

14

CAN receive data output (LOW when dominant; HIGH when recessive)

n.c.

15

not connected

TEST

16

test pin (should be connected to ground in application)

Document Outline