| ÐлекÑÑоннÑй компоненÑ: PJ393CS | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

þÿ

PJ393

Dual Voltage Comparator

1-6 2001/10 VER.A

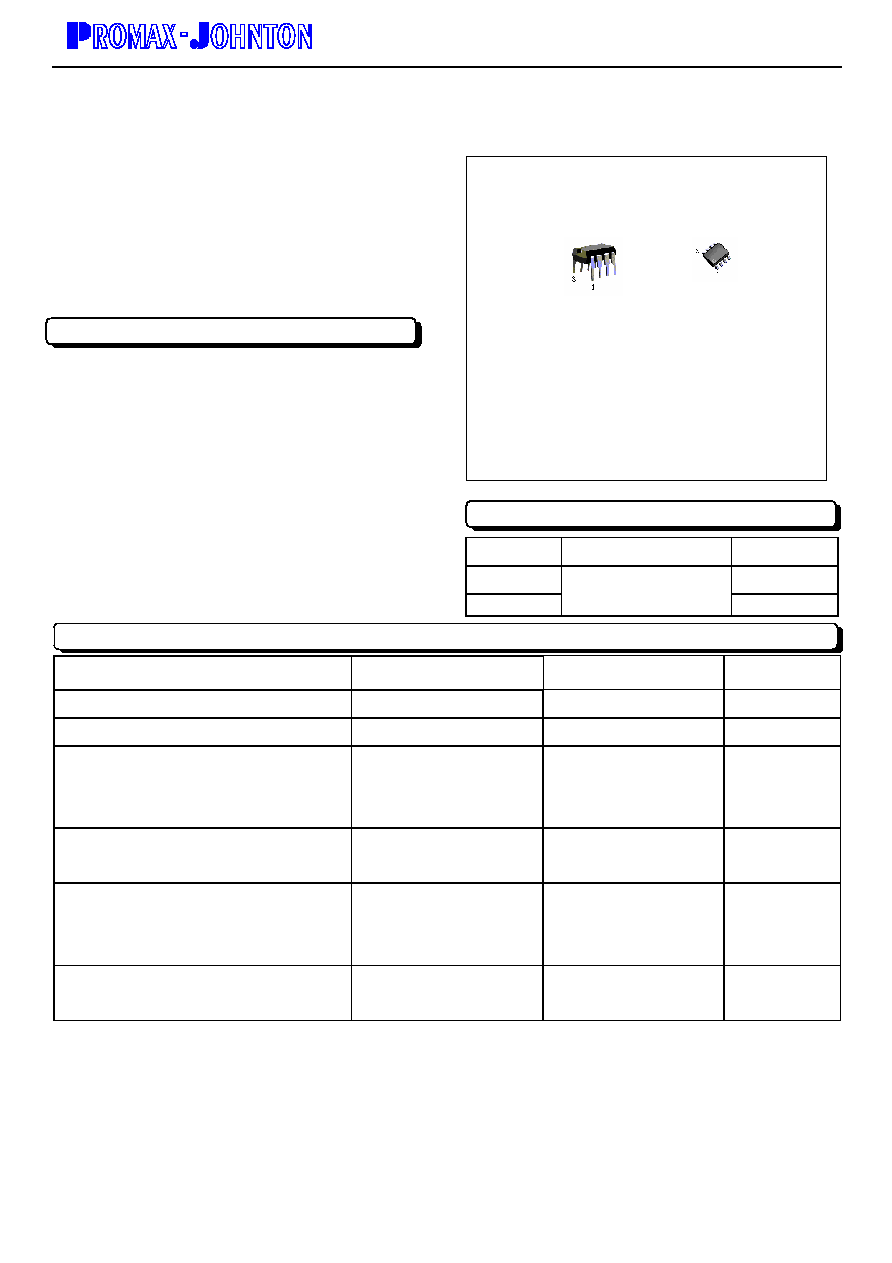

DIP-8 SOP-8

Pin : 1. Output 5. Input B

2. Input A 6. Input B

3. Input A 7. Output B

4. Gnd 8. Vcc

he PJ393 is dual independent precision voltage

comparators capable of single- or split-supply

operation.

specifications as low as 2.0 mV make this device an

excellentground level with single-supply operation. Input

offset-voltage selection for many applications in consumer

automotive, and It is designed to permit a common mode

range-to- industrial electronics.

· Output voltage compatible with DTL, ECL, TTL, MOS

and CMOS Logic Levels

· Low input bias current -25 nA

· Low input offset current -5.0 nA

· Low input offset voltage --5.0 mV(max)

· Input common mode range to ground level

· Differential lnput voltage range equal to power supply

voltage

· Very low current drain independent of supply voltage -

0.4 mA

· Wide single-supply range - 2.0 Vdc to 36 Vdc

· Split-supply range - ±1.0 Vdc to ±18 Vdc

Device

Operating Temperature

Package

PJ393CD DIP-8

PJ393CS

-20 +85

SOP-8

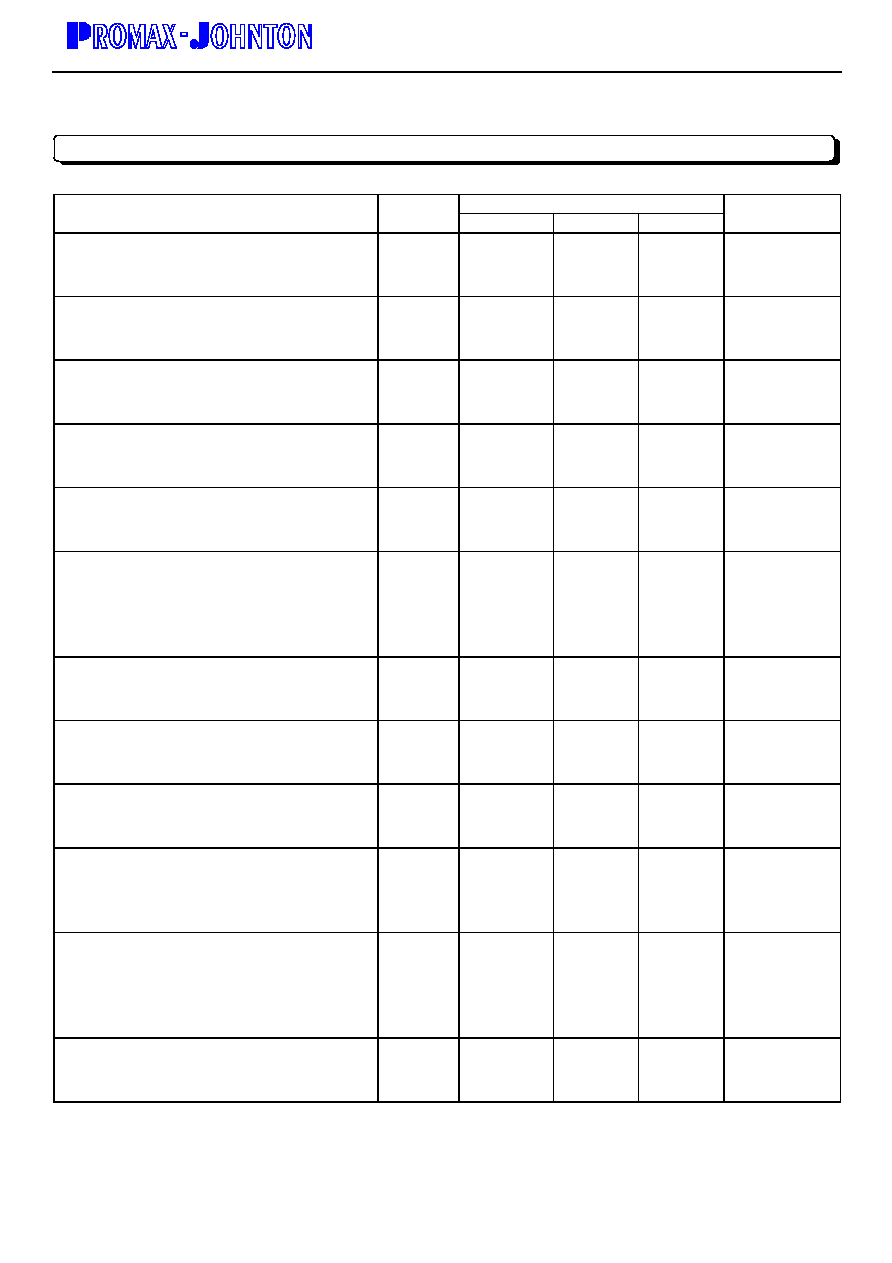

Rating Symbol

Value

Unit

Power Supply Voltage

V

CC

+36

or

±18

Vdc

Input Differential Voltage Range

V

IDR

36

Vdc

Input Common Mode Voltage Range

Input Current (2)

(Vin -0.3 Vdc)

V

ICR

I

in

-0.3 to 36

50

Vdc

mA

Output Short Circuit Duration

Output Sink Current (1)

I

SC

I

sink

Continuous

20

mA

Power Dissipation@T

A

=25

Plastic DIP

Derate above 25

P

D

1/R

JA

570

5.7

mW

mW/

Maximum Operating Junction Temperature

PJ393

T

J(max)

T

stg

125

-65 to 150

T

ORDERING INFORMATION

FEATURES

MAXIMUM RATINGS

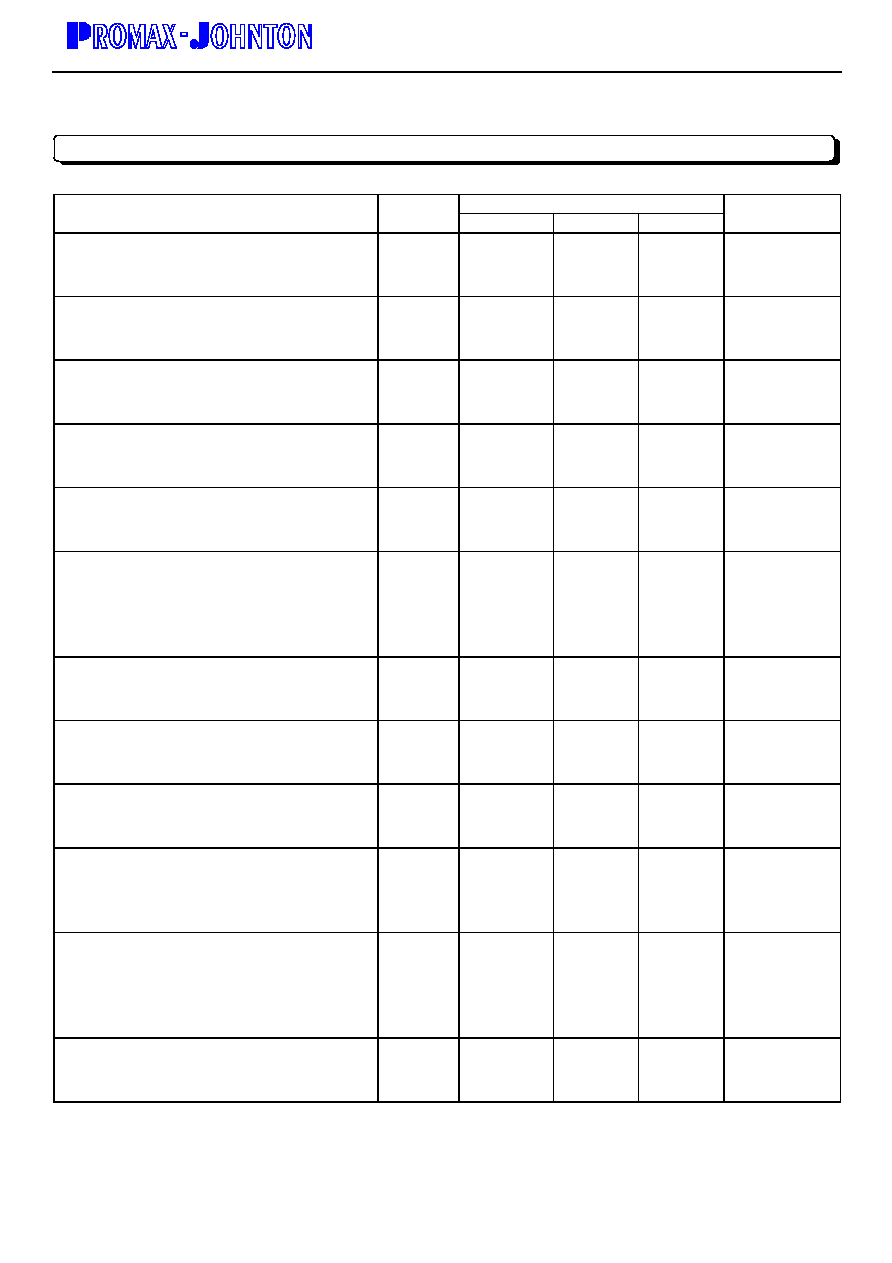

PJ393

Dual Voltage Comparator

2-6 2001/10 VER.A

(V

CC

= 50Vdc, 0

T

A

70 unless otherwise stated)

PJ393

Characteristics Symbol

Min

Typ

Max

Unit

Input Offset Voltage (3)

T

A

=25

-20

T

A

85

V

IO

--

--

±1.0

--

±5.0

9.0

mV

Input Offset Current

T

A

=25

-20

T

A

85

I

IO

--

--

±5.0

--

±50

±150

nA

Input Offset Current (4)

T

A

=25

-20

T

A

85

I

IB

--

--

25

--

250

400

nA

Input Common Mode Voltage Range (4)

T

A

=25

-20

T

A

85

V

ICR

0

0

--

--

V

CC

-1.5

V

CC

-2.0

Volts

Voltage Gain

R

L

15K , V

CC

= 15 Vdc.

T

A

=25

A

VOL

50

200

--

V/mV

Large Signal Response Time

Vin = TTL Logic Swing.

Vref = 1.4 Vdc

VRL = 5.0 Vdc. RL 5.1 K

T

A

=25

-- -- 300 -- ns

Response Time (6)

VRL = 5.0 Vdc RK = 5.1 K

T

A

=25

t

TLH

--

1.3 --

µs

Input Differentral Voltage (7)

All Vin

Gnd or V-Supply

(if used)

V

ID

-- -- V

CC

V

Output Sink Current

V

in-

1.0 Vdc V

in+

= 0 Vdc

V

O-

15 Vdc T

A

=25

L

sink

60 16 --

mA

Output Saturation Voltage

V

in-

1.0 Vdc. V

in+

= 0

I

sink

4.0 mA, T

A

= 25

-20

T

A

85

V

OL

--

--

150

--

400

700

mV

Output Leakage Current

V

in-

= 0V, V

in+

1.0Vdc

VP = 50 Vdc. T

A

=25

V

in-

= 0V, V

in+

1.0 Vdc

V

O

=30 Vdc -20

T

A

85

I

OL

--

--

0.1

--

--

1000

nA

Supply Current

R

L

=

T

A

=25

R

L

=

V

CC

=30 V

L

CC

--

--

0.4

--

1.0

2.5

mA

ELECTRICAL CHARACTERISTICS

PJ393

Dual Voltage Comparator

3-6 2001/10 VER.A

Notes:

1. The max. Output current may be as high as 20 mA, independent of the magnitude of V

CC

, output short circuits to V

CC

can cause excessive heating and eventual destruction.

2. This magnitude of input current will only occur if the input leads are driven more negative than guound or the negative

supply voltage. This is due to the input PNP collector base junction becoming forward biased acting as an input clamp

diode. There is also a lateral PNP parasitic transistor action on the IC chip. This phenomena can cause the output

voltage of the comparators to go to the V

CC

voltage level (or ground if overdrive is large) during the time the input is

driven negative.This will not destroy the device and normal output states will recover when the inputs become -0.3 V of

ground or negative supply.

3. At output switch point, V

O

= 1.4 Vdc, R

S

= 0

with V

CC

from 5.0 Vdc to 30 Vdc, and over the full input common-mode

4. Due to the PNP transistor inputs, bias current will flow out of the inputs, this current is essentially constant independent

of the output state, therefore, no loading changes will exist on the input lines.

5. Input common mode of either input should not be permitted to go more than 0.3 V negative of ground or minus supply.

The upper limit of common mode range is V

CC

- 1.5 V but either or both inputs can betaken to as high as 30 volts

without damage.

6. Response time is specified with a 100 mV step and 5.0 mV of overdrive. With larger magnitudes of overdrive faster

response times are obtainable.

7. The comparator will inhibit proper output state if one of the inputs become greater than V

CC,

the other input must remain

within the common mode range. The low input state must not be less than -0.3 volts of ground of minus supply.

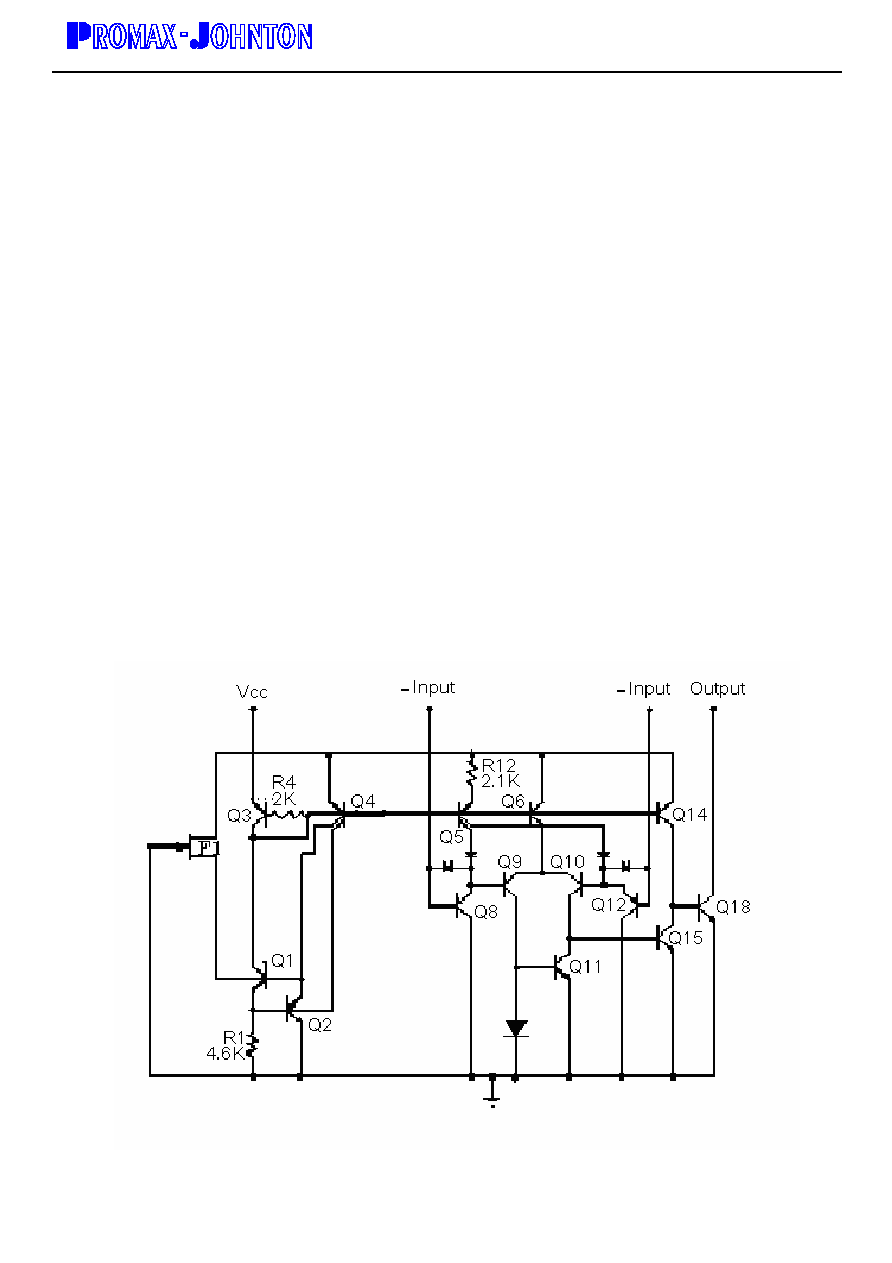

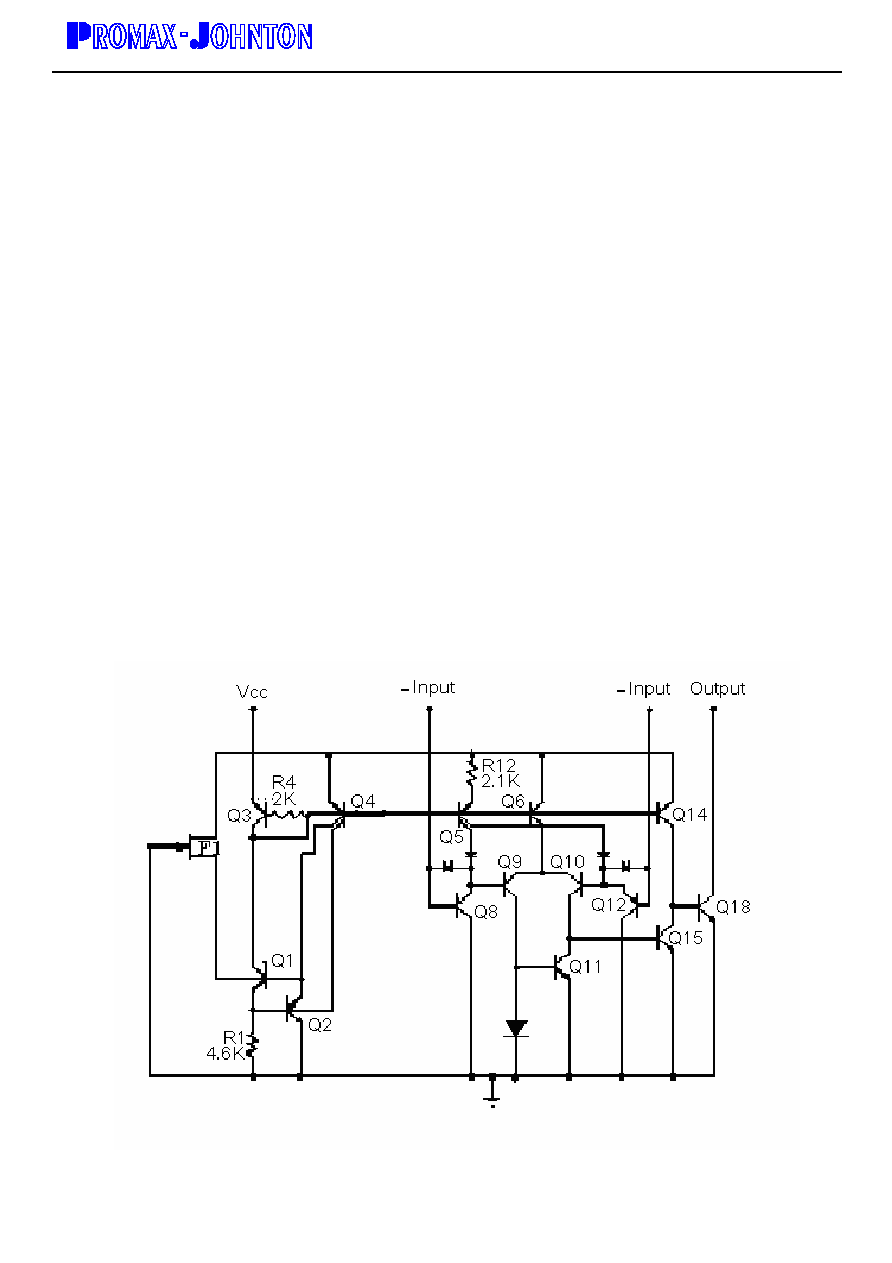

FIGURE 1- CIRCUIT SCHEMATIC

(Diagram shown is for 1 comparator)

PJ393

Dual Voltage Comparator

4-6 2001/10 VER.A

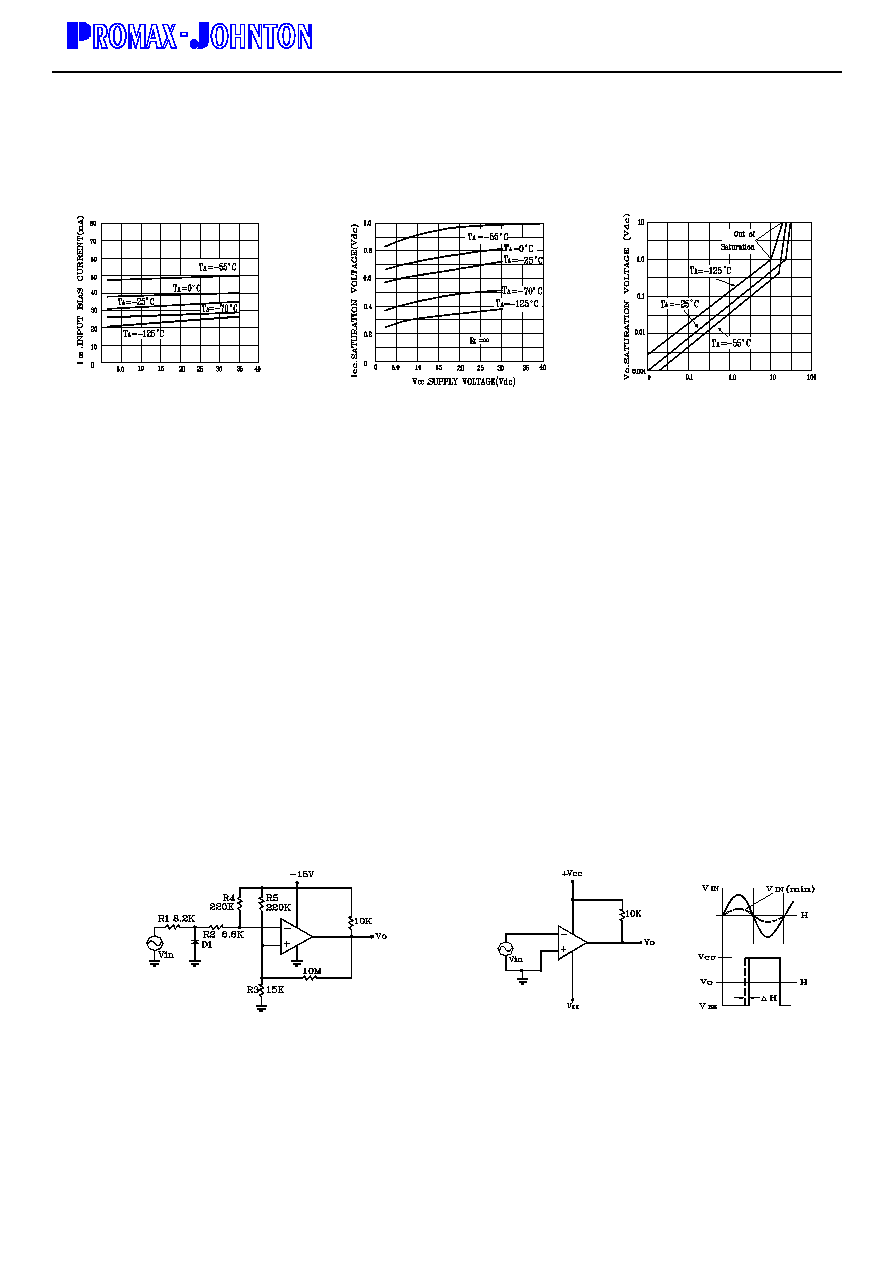

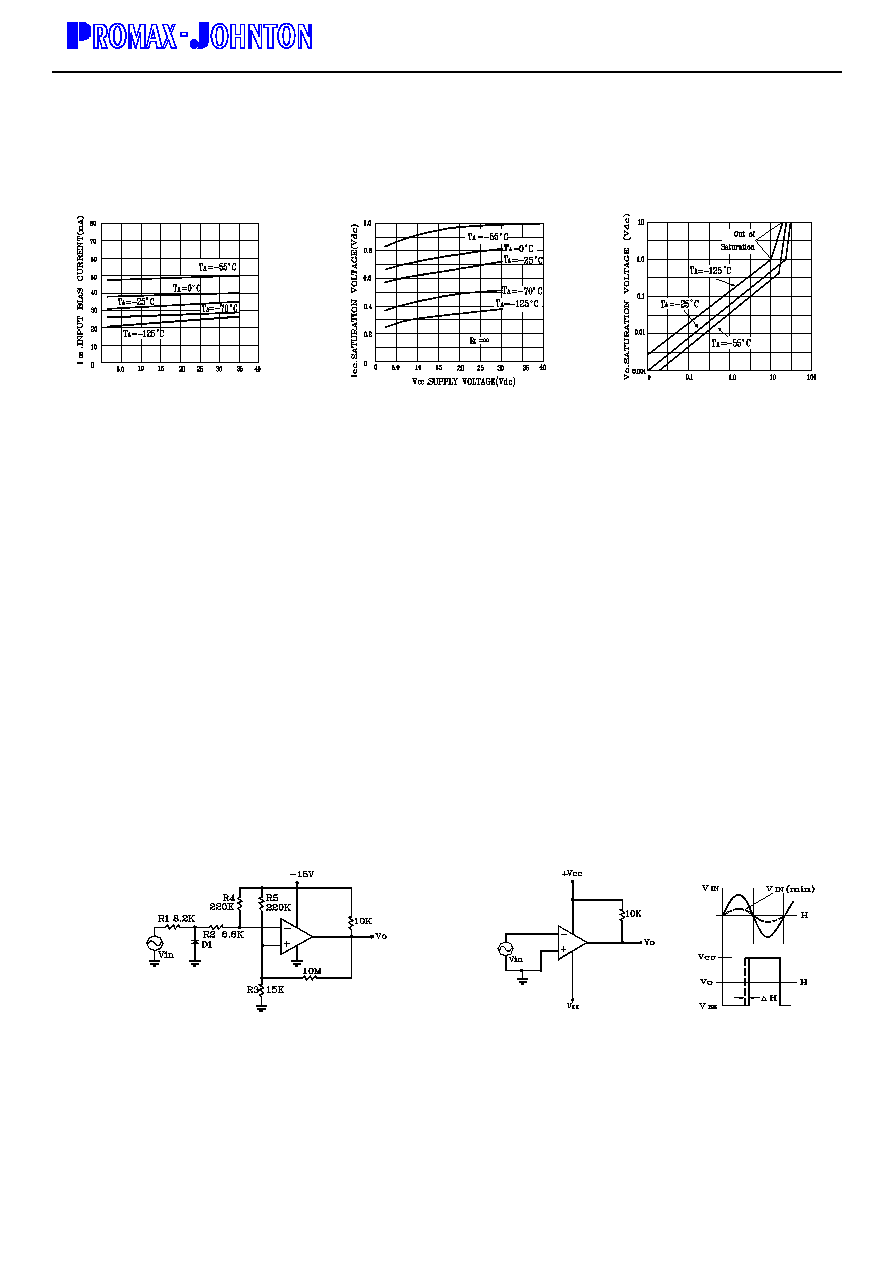

FIGURE 2 - INPUT BIAS

CURRENT versus

POWER SUPPLY VOLTAGE

FIGURE 4 - POWER SUPPLY

CURRENT versus

POWER SUPPLY VOLTAGE

FIGURE 3 - OUTPUT

SATURATION VOLTAGE

versus OUTPUT SINK CURRENT

APPLICATIONS INFORMATION

This dual comparator feature high gain, wide bandwidth characteristics. This gives the device oscillation

tendencies if the outputs are capactively coupled to the inputs via stray capacitance. This oscillation manifests itself

during output transitions (V

OL

to V

OH

). To alleviate this situation input resistors <10K

should be used. The addition

of positive feedback (<10 mV) is also recommended.

It is good design practice to ground all unused pins.

Differential input voltages may be larger than supply voltage without damaging the comparator's inputs. Voltages

more negative than -0.3 V should not be used.

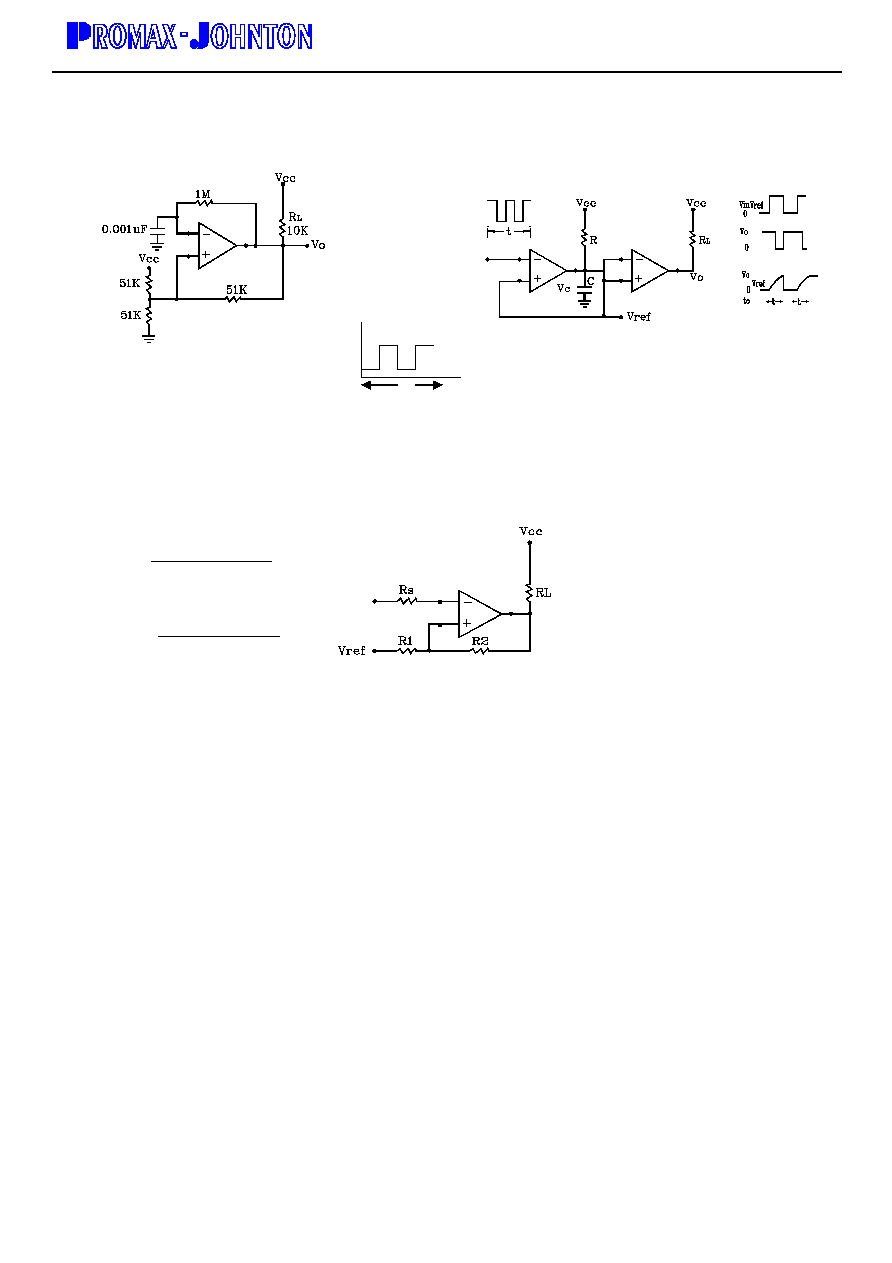

FIGURE 5 - ZERO CROSSING DETECTOR FIGURE 6 - ZERO CROSSING DETECTOR

( Single Supply ) ( Split Supplies )

PJ393

Dual Voltage Comparator

5-6 2001/10 VER.A

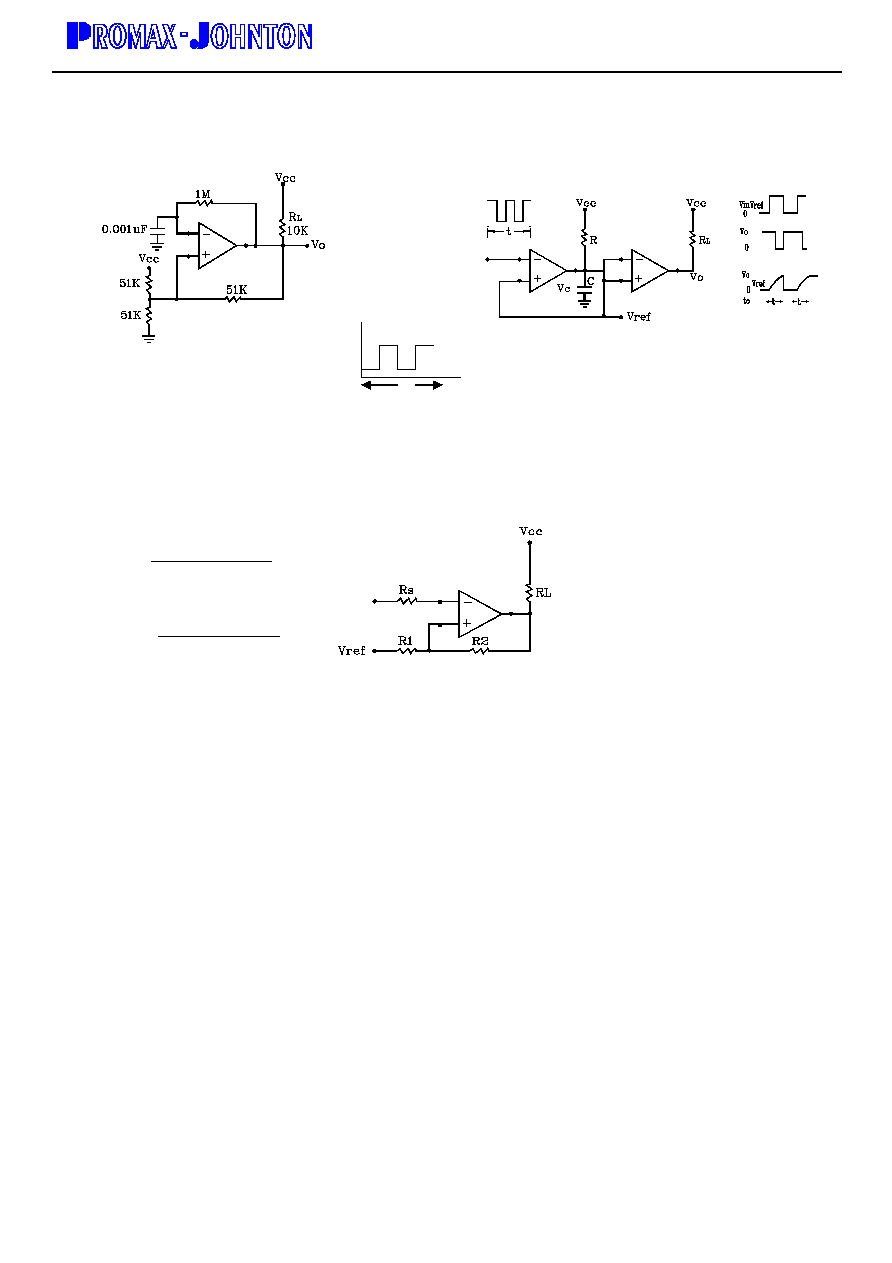

FIGURE 7 - ZERO CROSSING DETECTOR FIGURE 8 - TIME DELAY GENERATOR

Vcc

Vo

0

t

FIGURE 9 - COMPARATOR WITH HYSTERESIS

R

S

= R1 = R2

(Vcc * Vref) * R1

Vth1 = Vref *

R1 * R2 * R

L

(Vref * VoLow) * R1

Vth2 = Vref *

R1 * R2 * R

L