PTSC ∑ 10989 Via Frontera ∑ San Diego, CA 92127 ∑ Tel: (858) 674-5000 ∑ Fax: (858) 674-5005 ∑

info@ptsc.com ∑ www.ptsc.com

PTSC's IGNITETM family of microprocessors enables manufacturers to differentiate their products, re-

place less efficient control devices, add functionality and reduce cost. The unique dual stack architecture

coupled with the lowest gate count and memory footprint in the industry, enables IGNITE to be the indus-

try's price/performance leader. PTSC has successfully integrated the industry's smallest and most power-

ful RISC 32-bit microprocessor. It also has a full Java application environment including Personal Java

and VxWorks, as well as Linux, ensuring real-time system response for time-critical system tasks. The

speed, flexibility, efficiency and low cost of this technology package are what make it the most attractive

advanced microprocessor on the market today.

IGNITE

TM

Family of Microprocessors

Half the Size, Consumes Half the Power &

Delivers Twice the Performance

IGNITE I ≠ Silicon Microprocessor ≠ Floating Point

Product

IGNITE Ia - 0.35 micron (Available now)

Silicon feature list

IGNITE Ib -0 .18 micron (Available Q4 2002)

∑

Patented Zero-operand, dual-stack architecture

∑

4 Gigabyte of physical address space

∑

8-level interrupt controller

∑

Dedicated 8 input and 8 output bits

∑

32-bit System Bus

∑

Multi-instruction fetch with overlap execution

∑

Automatic Stack fills and refills in hardware

∑

Posted Writes

∑

Hardware assist to single/double precision IEEE

Floating point instructions

∑

Fully Static Design

∑

JTAG support

∑

Low-cost, high-performance, low-power 32 bit RISC

processor

∑

Up to 200MHz operating frequency (worst case)

∑

Memory efficient, eight-bit instruction op codes

IGNITE II ≠ Silicon Microprocessors ≠ Integer Product

IGNITE IIb - 0.18 micron (Available Q4 2002)

∑

Patented Zero-operand, dual-stack architecture

∑

4 Gigabyte of physical address space

∑

8-level interrupt controller

∑

Dedicated 8 input and 8 output bits

∑

32-bit System Bus

∑

Multi-instruction fetch with overlap execution

∑

Automatic Stack fills and refills in hardware

∑

Posted Writes

∑

Fully Static Design

∑

JTAG support

∑

Low-cost, high-performance, low-power 32 bit RISC

processor

∑

Up to 225MHz operating frequency (worst case)

∑

Memory efficient, eight-bit instruction op codes

IGNITE III ≠ Floating Point Core Microprocessors

IGNITE IIIb ≠ Generic reference to FP 0.18 micron soft-

core (Available now)

IGNITE IIIb.d - FP 0.18 micron hardcore

(Available Q4 2002)

IGNITE IV ≠ Integer Core Microprocessors

IGNITE IVb ≠ Generic reference to Integer 0.18 micron

softcore (Available now)

IGNITE IVb.d ≠ Integer 0.18 micron hardcore

(Available Q4 2002)

IGNITE Microprocessor Family

©Copyright 2002, PTSC, all rights reserved. IGNITE and IGNITE I are trademarks of PTSC. All other trademarks are the property of their respective owners.

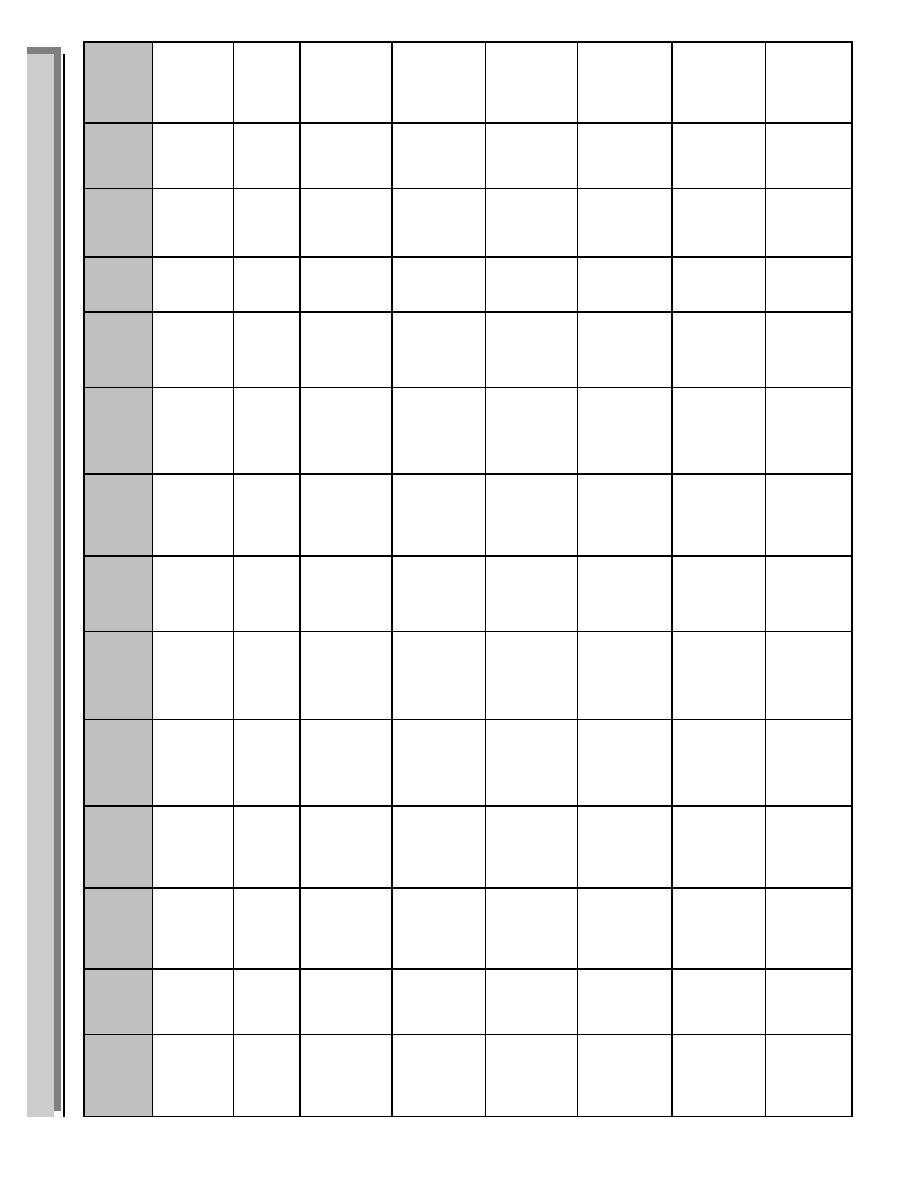

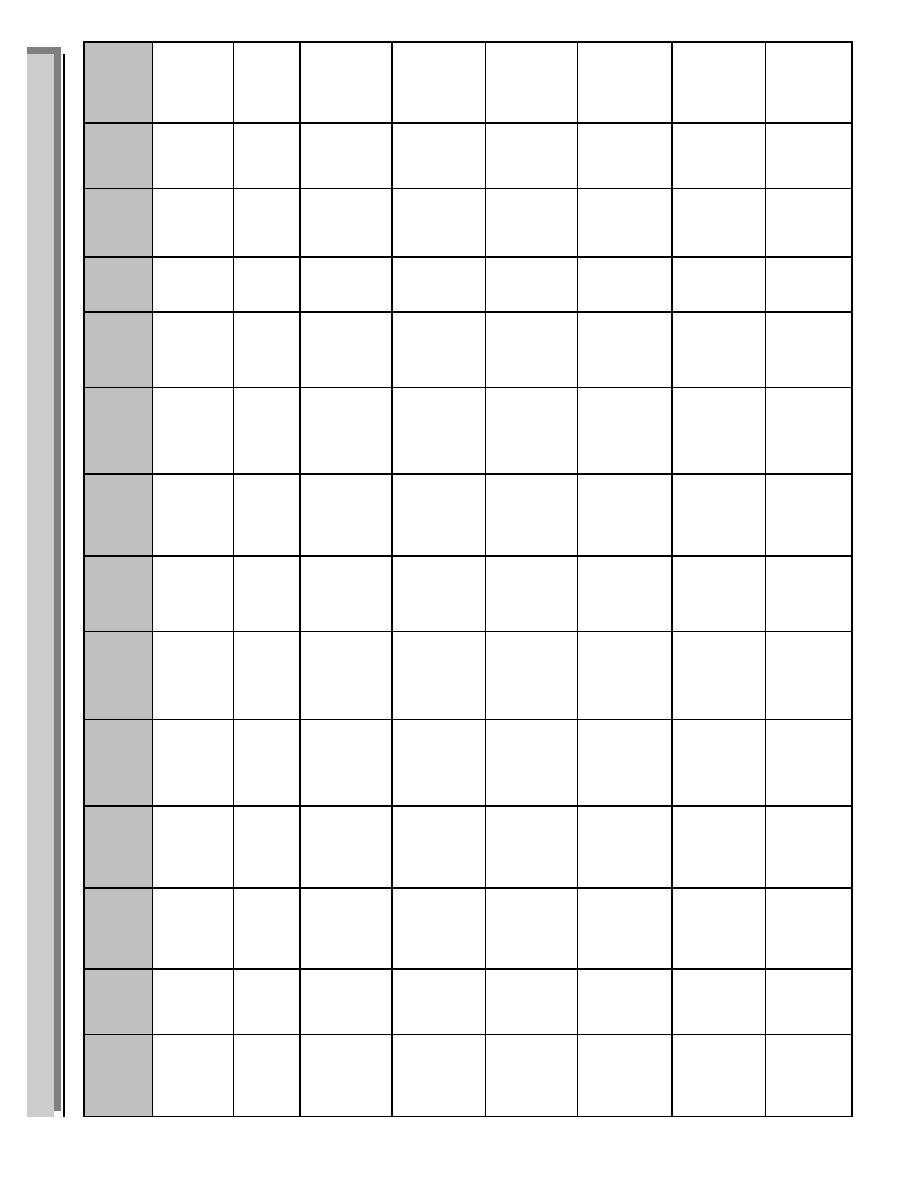

DEVICE

CPU

frequency

(MHz)

Bus interface

(address/ data) (bits)

Instruction width (bits)

Operating voltages (V)

Typical power at maximum

frequency

Power down

modes

Caching

Memory

Memory co

n

troller

Timers

Serial,

Parallel I/O

Interrupts

Additional features

IGNITE I

100

32

(multiplexed)

8

5

350 mW

Stop, halt

not required (single cycle

random access

supported)

yes

VPU

Hardware baud rate generation

Eight

IGNITE Ia

100

32

(multiplexed)

8

3.5

165 mW

Stop, halt

not required (single cycle

random access

supported)

yes

VPU

Hardware baud rate generation

Eight

IGNITE Ib

200

32/8, 16, 32

8

1.8

100 mW

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE IIb

220

32/8, 16, 32

8

1.8

110 mW

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE IIIb

365

32/8, 16, 32

8

1.8

81mW or 0.22

mW/MHz

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE IIIb.a

365

32/8, 16, 32

8

1.8

84mW or 0.23

mW/MHz

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE IVb

400

32/8, 16, 32

8

1.8

88mW or 0.22

mW/MHz

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE IVb.a

400

32/8, 16, 32

8

1.8

92mW or 0.23

mW/MHz

Stop, halt, sleep and dynamically variable fr

e-

quency clock

(0

-

max)

not required (single cycle

random access

supported)

Configurable

Optional

Fully

configurable

Eight

Fully

synthesizable

core

IGNITE

TM

Product Specifications

S

pecifications subject to change without notice.